Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                   |

| Number of I/O              | 46                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

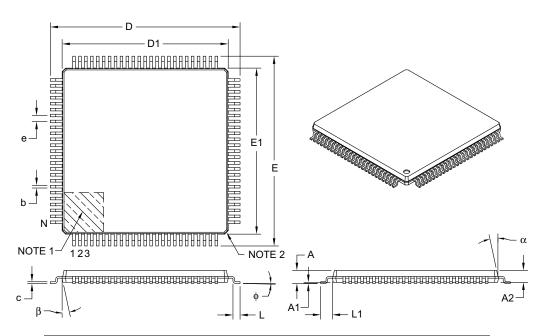

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024eff064t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1: **PIC32MZ EF FAMILY FEATURES**

|                   |                        |                     |      |               |                           |                 | Remap                                         | pable l | Periph               | erals                                 |          |        |     |                                              |                | ors                | 4              |                  |     |     |                |      |          |          |      |              |

|-------------------|------------------------|---------------------|------|---------------|---------------------------|-----------------|-----------------------------------------------|---------|----------------------|---------------------------------------|----------|--------|-----|----------------------------------------------|----------------|--------------------|----------------|------------------|-----|-----|----------------|------|----------|----------|------|--------------|

| Device            | Program<br>Memory (KB) | Data<br>Memory (KB) | Pins | Packages      | Boot Flash<br>Memory (KB) | Remappable Pins | Timers/<br>Capture/<br>Compare <sup>(1)</sup> | UART    | SPI/I <sup>2</sup> S | External<br>Interrupts <sup>(2)</sup> | CAN 2.0B | Crypto | RNG | DMA Channels<br>(Programmable/<br>Dedicated) | ADC (Channels) | Analog Comparators | USB 2.0 HS OTG | 1 <sup>2</sup> C | PMP | EBI | SQI            | RTCC | Ethernet | I/O Pins | JTAG | Trace        |

| PIC32MZ0512EFE064 |                        |                     |      |               |                           |                 |                                               |         |                      |                                       | 0        | N      | Υ   | 8/12                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFF064 | 512                    | 128                 |      |               |                           |                 |                                               |         |                      |                                       | 2        | Ν      | Υ   | 8/16                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFK064 |                        |                     | 64   | TQFP,         | 160                       | 34              | 9/9/9                                         | 6       | 4                    | 5                                     | 2        | Υ      | Υ   | 8/18                                         | 24             | 2                  | Y              | 4                | Y   | N   | l <sub>Y</sub> | Y    | Υ        | 46       | Υ    | <sub>Y</sub> |

| PIC32MZ1024EFE064 |                        |                     | 04   | QFN           | 100                       | 34              | 3/3/3                                         | 0       | -                    |                                       | 0        | N      | Υ   | 8/12                                         | 24             | _                  | '              | "                | '   | "   | '              | '    | '        | 40       | '    | l '          |

| PIC32MZ1024EFF064 | 1024                   | 256                 |      |               |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ1024EFK064 |                        |                     |      |               |                           |                 |                                               |         |                      |                                       | 2        | Υ      | Υ   | 8/18                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFE100 |                        |                     |      |               |                           |                 |                                               |         |                      |                                       | 0        | Ν      | Υ   | 8/12                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFF100 | 512                    | 128                 |      |               |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFK100 |                        |                     | 100  | TQFP          | 160                       | 51              | 9/9/9                                         | 6       | 6                    | 5                                     | 2        | Υ      | Υ   | 8/18                                         | 40             | 2                  | Y              | 5                | Y   | Y   | Ι <sub>Υ</sub> | Y    | Υ        | 78       | Y    | Y            |

| PIC32MZ1024EFE100 |                        |                     | 100  | 1 3.1         | 100                       |                 | 0,0,0                                         |         |                      |                                       | 0        | N      | Υ   | 8/12                                         | "              | _                  |                |                  | i i | l . | l .            | ·    | ·        | '        | •    | '            |

| PIC32MZ1024EFF100 | 1024                   | 256                 |      |               |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ1024EFK100 |                        |                     |      |               |                           |                 |                                               |         |                      |                                       | 2        | Υ      | Υ   | 8/18                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFE124 | _                      |                     |      |               |                           |                 |                                               |         |                      |                                       | 0        | N      | Υ   | 8/12                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFF124 | 512                    | 128                 |      |               |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFK124 |                        |                     | 124  | VTLA          | 160                       | 53              | 9/9/9                                         | 6       | 6                    | 5                                     | 2        | Υ      | Υ   | 8/18                                         | 48             | 2                  | Y              | 5                | Y   | Ιγ  | Ιγ             | Y    | Υ        | 97       | Y    | Y            |

| PIC32MZ1024EFE124 | 4                      |                     |      |               |                           |                 |                                               |         |                      |                                       | 0        | N      | Υ   | 8/12                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ1024EFF124 | 1024                   | 256                 |      |               |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ1024EFK124 |                        |                     |      |               |                           |                 |                                               |         |                      |                                       | 2        | Υ      | Υ   | 8/18                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFE144 | 4                      |                     |      |               |                           |                 |                                               |         |                      |                                       | 0        | N      | Υ   | 8/12                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFF144 | 512                    | 128                 |      |               |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ0512EFK144 |                        |                     | 144  | LQFP,<br>TQFP | 160                       | 53              | 9/9/9                                         | 6       | 6                    | 5                                     | 2        | Υ      | Y   | 8/18                                         | 48             | 2                  | Υ              | 5                | Υ   | Y   | Y              | Υ    | Υ        | 120      | Υ    | Υ            |

| PIC32MZ1024EFE144 | 4                      |                     |      | TUFP          |                           |                 |                                               |         |                      |                                       | 0        | N      | Υ   | 8/12                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ1024EFF144 | 1024                   | 256                 |      |               |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |                  |     |     |                |      |          |          |      |              |

| PIC32MZ1024EFK144 |                        |                     |      |               |                           |                 |                                               |         |                      |                                       | 2        | Υ      | Υ   | 8/18                                         |                |                    | 1              |                  |     |     |                |      |          |          |      |              |

Note

Eight out of nine timers are remappable. Four out of five external interrupts are remappable. This device is available with a 252 MHz speed rating. 2: 3:

| TABLE 1: | PIC32MZ EF FAMILY FEATURES (CONTINUED) |

|----------|----------------------------------------|

|----------|----------------------------------------|

|                                  |                        |                     |      |          |                           |                 | Remap                                         | pable I | Periph               | erals                                 |          |        |     |                                              |                | ıs                 | _              |     |     |     |     |      |          |          |      |       |

|----------------------------------|------------------------|---------------------|------|----------|---------------------------|-----------------|-----------------------------------------------|---------|----------------------|---------------------------------------|----------|--------|-----|----------------------------------------------|----------------|--------------------|----------------|-----|-----|-----|-----|------|----------|----------|------|-------|

| Device                           | Program<br>Memory (KB) | Data<br>Memory (KB) | Pins | Packages | Boot Flash<br>Memory (KB) | Remappable Pins | Timers/<br>Capture/<br>Compare <sup>(1)</sup> | UART    | SPI/I <sup>2</sup> S | External<br>Interrupts <sup>(2)</sup> | CAN 2.0B | Crypto | RNG | DMA Channels<br>(Programmable/<br>Dedicated) | ADC (Channels) | Analog Comparators | USB 2.0 HS OTG | l²C | PMP | EBI | SQI | RTCC | Ethernet | I/O Pins | JTAG | Trace |

| PIC32MZ1024EFG064                |                        |                     |      |          |                           |                 |                                               |         |                      |                                       | 0        | Ν      | Υ   | 8/12                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFH064                | 1024                   |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | Ν      | Υ   | 8/16                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFM064                |                        | 512                 | 64   | TQFP,    | 160                       | 34              | 9/9/9                                         | 6       | 4                    | 5                                     | 2        | Υ      | Υ   | 8/18                                         | 24             | 2                  | Υ              | 4   | Y   | N   | Υ   | Υ    | Υ        | 46       | Υ    | Y     |

| PIC32MZ2048EFG064                |                        | 312                 | 04   | QFN      | 100                       | 34              | 9/9/9                                         | O       | 4                    | 5                                     | 0        | Ν      | Υ   | 8/12                                         | 24             | 2                  | ı              | 4   | ı   | IN  | ı   | 1    | ı        | 40       | ī    | 1     |

| PIC32MZ2048EFH064 <sup>(3)</sup> | 2048                   |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | Ν      | Υ   | 8/16                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ2048EFM064                |                        |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | Υ      | Υ   | 8/18                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFG100                |                        |                     |      |          |                           |                 |                                               |         |                      |                                       | 0        | N      | Υ   | 8/12                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFH100                | 1024                   |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFM100                |                        | 512                 | 100  | TQFP     | 160                       | 51              | 9/9/9                                         | 6       | 6                    | 5                                     | 2        | Υ      | Υ   | 8/18                                         | 40             | 2                  | Y              | 5   | Υ   | Y   | Y   | Υ    | Υ        | 78       | Υ    | Y     |

| PIC32MZ2048EFG100                |                        | 312                 | 100  | IQIF     | 100                       | 31              | 3/3/3                                         | O       | O                    | 3                                     | 0        | Ν      | Υ   | 8/12                                         | 40             | 2                  | '              | 3   | '   | '   | '   | '    | '        | 70       | '    | '     |

| PIC32MZ2048EFH100 <sup>(3)</sup> | 2048                   |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ2048EFM100                |                        |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | Υ      | Υ   | 8/18                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFG124                |                        |                     |      |          |                           |                 |                                               |         |                      |                                       | 0        | N      | Υ   | 8/12                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFH124                | 1024                   |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFM124                |                        | 512                 | 124  | VTLA     | 160                       | 53              | 9/9/9                                         | 6       | 6                    | 5                                     | 2        | Υ      | Υ   | 8/18                                         | 48             | 2                  | Υ              | 5   | Υ   | Y   | Y   | Υ    | Υ        | 97       | Υ    | Y     |

| PIC32MZ2048EFG124                |                        | 012                 |      |          | 100                       | 00              | 0,0,0                                         | ŭ       | Ü                    |                                       | 0        | N      | Υ   | 8/12                                         | 10             | -                  | i i            |     | ·   |     |     | Ċ    | ·        | 01       | ·    |       |

| PIC32MZ2048EFH124                | 2048                   |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ2048EFM124                |                        |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | Υ      | Υ   | 8/18                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFG144                |                        |                     |      |          |                           |                 |                                               |         |                      |                                       | 0        | N      | Υ   | 8/12                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFH144                | 1024                   |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFM144                |                        | 512                 | 144  | LQFP,    | 160                       | 53              | 9/9/9                                         | 6       | 6                    | 5                                     | 2        | Υ      | Υ   | 8/18                                         | 48             | 2                  | Υ              | 5   | Υ   | Y   | Y   | Υ    | Υ        | 120      | Υ    | Y     |

| PIC32MZ2048EFG144                |                        | 0.2                 |      | TQFP     | 100                       |                 | 3,0,0                                         | Ĭ       |                      |                                       | 0        | N      | Υ   | 8/12                                         |                | -                  |                |     |     |     |     | •    |          | .20      | •    | '     |

| PIC32MZ2048EFH144 <sup>(3)</sup> | 2048                   |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | N      | Υ   | 8/16                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

| PIC32MZ2048EFM144                |                        |                     |      |          |                           |                 |                                               |         |                      |                                       | 2        | Υ      | Υ   | 8/18                                         |                |                    |                |     |     |     |     |      |          |          |      |       |

1: 2: 3: Note

Eight out of nine timers are remappable. Four out of five external interrupts are remappable. This device is available with a 252 MHz speed rating.

#### 1.0 DEVICE OVERVIEW

Note:

This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This data sheet contains device-specific information for PIC32MZ EF devices.

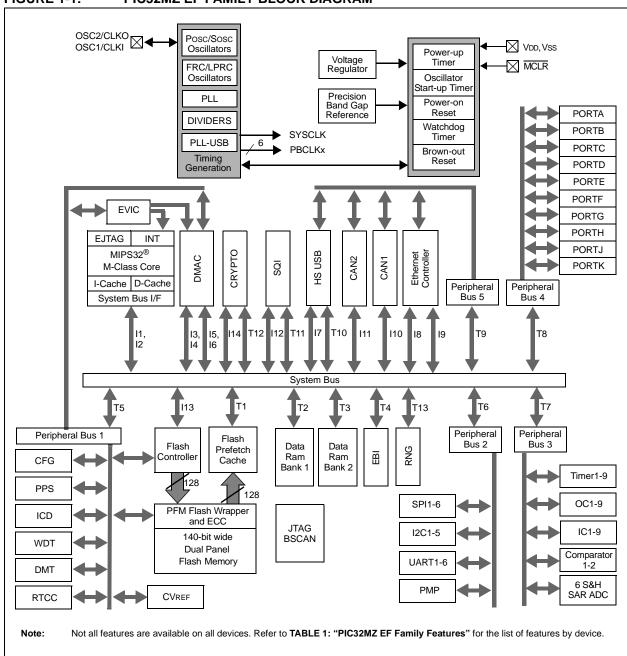

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MZ EF family of devices.

Table 1-21 through Table 1-22 list the pinout I/O descriptions for the pins shown in the device pin tables (see Table 2 through Table 5).

FIGURE 1-1: PIC32MZ EF FAMILY BLOCK DIAGRAM

TABLE 1-22: JTAG, TRACE, AND PROGRAMMING/DEBUGGING PINOUT I/O DESCRIPTIONS

|          |                        | Pin Nu          | mber            |                          |             |                |                                                                            |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|----------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                                                |

|          |                        |                 |                 |                          | J٦          | ΓAG            |                                                                            |

| TCK      | 27                     | 38              | B21             | 56                       | I           | ST             | JTAG Test Clock Input Pin                                                  |

| TDI      | 28                     | 39              | A26             | 57                       | I           | ST             | JTAG Test Data Input Pin                                                   |

| TDO      | 24                     | 40              | B22             | 58                       | 0           | _              | JTAG Test Data Output Pin                                                  |

| TMS      | 23                     | 17              | A11             | 22                       | I           | ST             | JTAG Test Mode Select Pin                                                  |

|          |                        |                 |                 |                          | Tr          | ace            |                                                                            |

| TRCLK    | 57                     | 89              | A61             | 129                      | 0           | _              | Trace Clock                                                                |

| TRD0     | 58                     | 97              | B55             | 141                      | 0           | _              | Trace Data bits 0-3                                                        |

| TRD1     | 61                     | 96              | A65             | 140                      | 0           | _              |                                                                            |

| TRD2     | 62                     | 95              | B54             | 139                      | 0           | _              |                                                                            |

| TRD3     | 63                     | 90              | B51             | 130                      | 0           | _              |                                                                            |

|          |                        |                 |                 | Pro                      | grammir     | ng/Debuggi     | ing                                                                        |

| PGED1    | 16                     | 25              | A18             | 36                       | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1             |

| PGEC1    | 15                     | 24              | A17             | 35                       | I           | ST             | Clock input pin for Programming/Debugging Communication Channel 1          |

| PGED2    | 18                     | 27              | A19             | 38                       | I/O         | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 2          |

| PGEC2    | 17                     | 26              | B14             | 37                       | I           | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 2       |

| MCLR     | 9                      | 15              | A10             | 20                       | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device. |

egend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input

O = Output

P = Power I = Input

PPS = Peripheral Pin Select

| <b>TABLE 7-3:</b> | INTERRUPT | REGISTER | MAP | (CONTINUED) |

|-------------------|-----------|----------|-----|-------------|

|                   |           |          |     |             |

| ress<br>t)                  | <b>L</b> _                      | ø         |       |       |       |           |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | s,         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-----------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12     | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

| 0010                        | OFF183                          | 31:16     | _     | _     | _     | _         | -     | _     | ı    | _          | _    | _    | _    |      | _    |      | VOFF< | 17:16> | 0000       |

| 0610                        | OFF 103                         | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0830                        | OFF184                          | 31:16     | _     | _     | _     | _         | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0020                        | 011104                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0824                        | OFF185 <sup>(2)</sup>           | 31:16     | _     | _     | _     | _         | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0024                        | 011100                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0828                        | OFF186 <sup>(2)</sup>           | 31:16     | _     |       | _     | _         |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0020                        | OI 1 100·                       | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0820                        | OFF187 <sup>(2)</sup>           | 31:16     | _     |       | _     | _         | _     | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0020                        | 011107                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0830                        | OFF188                          | 31:16     | _     | _     | _     | _         | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0030                        | 011100                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0834                        | OFF189                          | 31:16     | _     |       | _     | _         |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0004                        | 011103                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0838                        | OFF190                          | 31:16     | _     |       | _     | _         | _     | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0030                        | 011130                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0840                        | OFF192                          | 31:16     | _     | _     | _     | _         | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0040                        | 011132                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0844                        | OFF193                          | 31:16     | _     |       | _     | _         | _     | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0044                        | 011133                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0848                        | OFF194                          | 31:16     | _     |       | _     | _         | _     | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0040                        | 011134                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0850                        | OFF196                          | 31:16     | _     |       | _     | _         | _     | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0030                        | 011130                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0858                        | OFF198                          | 31:16     | _     |       | _     | _         |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0000                        | 011130                          | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 0850                        | OFF199                          | 31:16     | _     |       | _     | _         | _     | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 3030                        | 017 100                         | 15:0      |       |       |       |           |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0860                        | OFF200                          | 31:16     | _     |       | _     | _         | _     | _     | -    | _          |      |      | _    | -    | _    | _    | VOFF< | 17:16> | 0000       |

| 0000                        | O1 F200                         | 15:0      |       |       |       | · · · · · |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

- Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV

- Registers" for more information.

This bit or register is not available on 64-pin devices.

- This bit or register is not available on devices without a CAN module.

- 4:

- This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

- 6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

- This bit or register is not available on devices without a Crypto module. This bit or register is not available on 124-pin devices. 7:

#### REGISTER 11-18: USBEXTXA: USB ENDPOINT 'x' TRANSMIT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 |                   |                   | T                 | (HUBPRT<6:        | 0>                |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | MULTTRAN          |                   |                   | TΣ                | (HUBADD<6:        | 0>                |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | -                 | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 |                   |                   | Т                 | XFADDR<6:0        | >                 |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 Unimplemented: Read as '0'

bit 30-24 **TXHUBPRT<6:0>:** TX Hub Port bits (*Host mode*)

When a Low-Speed or Full-Speed device is connected to this endpoint through a Hi-Speed USB 2.0 hub, this field records the port number of that USB 2.0 hub.

bit 23 MULTTRAN: TX Hub Multiple Translators bit (Host mode)

1 = The USB 2.0 hub has multiple transaction translators

0 = The USB 2.0 hub has a single transaction translator

bit 22-16 **TXHUBADD<6:0>:** TX Hub Address bits (*Host mode*)

When a Low-Speed or Full-Speed device is connected to this endpoint through a Hi-Speed USB 2.0 hub, these bits record the address of the USB 2.0 hub.

bit 15-7 Unimplemented: Read as '0'

bit 6-0 **TXFADDR<6:0>:** TX Functional Address bits (*Host mode*)

Specifies the address for the target function that is be accessed through the associated endpoint. It needs to be defined for each TX endpoint that is used.

#### REGISTER 15-3: DMTCLR: DEADMAN TIMER CLEAR REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | _                 | _                 | _                 | _                 |                   | _                 | _                | _                |

| 22.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     |                   | _                 | _                 |                   | _                 |                   | -                | _                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      |                   | _                 | _                 |                   | _                 |                   | -                | _                |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       |                   |                   |                   | STEP2             | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 **Unimplemented:** Read as '0' bit 7-0 **STEP2<7:0>:** Clear Timer bits

00001000 = Clears STEP1<7:0>, STEP2<7:0> and the Deadman Timer if, and only if, preceded by correct loading of STEP1<7:0> bits in the correct sequence. The write to these bits may be verified by reading DMTCNT and observing the counter being reset.

All other write patterns = Set BAD2 bit, the value of STEP1<7:0> will remain unchanged, and the new value being written STEP2<7:0> will be captured. These bits are also cleared when a DMT reset event occurs.

REGISTER 20-8: SQI1INTEN: SQI INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | _                 | DMAEIE            | PKTCOMPIE         | BDDONEIE         | CONTHRIE         |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CONEMPTYIE        | CONFULLIE         | RXTHRIE           | RXFULLIE          | RXEMPTYIE         | TXTHRIE           | TXFULLIE         | TXEMPTYIE        |

**Legend:** HS = Hardware Set

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-12 Unimplemented: Read as '0'

bit 11 DMAEIE: DMA Bus Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 10 PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 9 BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 8 **CONTHRIE:** Control Buffer Threshold Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 7 CONEMPTYIE: Control Buffer Empty Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 6 CONFULLIE: Control Buffer Full Interrupt Enable bit

This bit enables an interrupt when the receive FIFO buffer is full.

1 = Interrupt is enabled0 = Interrupt is disabled

bit 5 RXTHRIE: Receive Buffer Threshold Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 4 RXFULLIE: Receive Buffer Full Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 3 RXEMPTYIE: Receive Buffer Empty Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 2 **TXTHRIE:** Transmit Threshold Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 1 TXFULLIE: Transmit Buffer Full Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 0 TXEMPTYIE: Transmit Buffer Empty Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

#### REGISTER 20-10: SQI1TXDATA: SQI TRANSMIT DATA BUFFER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | TXDATA<           | :31:24>           |                   |                  |                  |

| 22.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | TXDATA<           | :23:16>           |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | TXDATA            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | TXDATA            | ·<7:0>            |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 TXDATA<31:0>: Transmit Command Data bits

Data is loaded into this register before being transmitted. Prior to the data transfer, the data in TXDATA is loaded into the shift register (SFDR).

Multiple writes to TXDATA can occur while a transfer is in progress. There can be a maximum of eight commands that can be queued.

### REGISTER 20-11: SQI1RXDATA: SQI RECEIVE DATA BUFFER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        |                   |                   |                   | RXDATA<           | <31:24>           |                   |                  |                  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   |                   |                   | RXDATA<           | <23:16>           |                   |                  |                  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | RXDATA            | <15:8>            |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | RXDATA            | N<7:0>            |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 RXDATA<31:0>: Receive Data Buffer bits

At the end of a data transfer, the data in the shift register is loaded into the RXDATA register. This register works like a FIFO. The depth of the receive buffer is eight words.

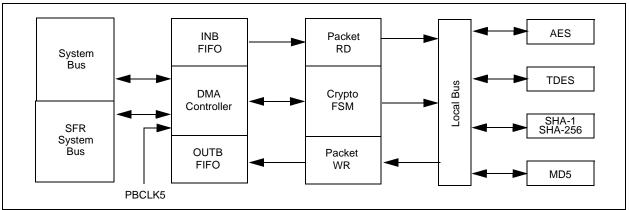

#### 26.0 CRYPTO ENGINE

Note:

This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Crypto Engine is intended to accelerate applications that need cryptographic functions. By executing these functions in the hardware module, software overhead is reduced and actions, such as encryption, decryption, and authentication can execute much more quickly.

The Crypto Engine uses an internal descriptor-based DMA for efficient programming of the security association data and packet pointers (allowing scatter/gather data fetching). An intelligent state machine schedules the Crypto Engines based on the protocol selection and packet boundaries. The hardware engines can perform the encryption and authentication in sequence or in parallel.

The following are key features of the Crypto Engine:

- · Bulk ciphers and hash engines

- Integrated DMA to off-load processing:

- Buffer descriptor-based

- Secure association per buffer descriptor

- Some functions can execute in parallel

Bulk ciphers that are handled by the Crypto Engine include:

- AES:

- 128-bit, 192-bit, and 256-bit key sizes

- CBC, ECB, CTR, CFB, and OFB modes

- DES/TDES:

- CBC, ECB, CFB, and OFB modes

Authentication engines that are available through the Crypto Engine include:

- SHA-1

- SHA-256

- MD-5

- AES-GCM

- HMAC operation (for all authentication engines)

The rate of data that can be processed by the Crypto Engine depends on these factors:

- · Which engine is in use

- Whether the engines are used in parallel or in series

- The demands on source and destination memories by other parts of the system (i.e., CPU, DMA, etc.)

- The speed of PBCLK5, which drives the Crypto Engine

Table 26-1 shows typical performance for various engines.

TABLE 26-1: CRYPTO ENGINE PERFORMANCE

| Engine/<br>Algorithm | Performance<br>Factor<br>(Mbps/MHz) | Maximum Mbps<br>(PBCLK5 = 100 MHz) |

|----------------------|-------------------------------------|------------------------------------|

| DES                  | 14.4                                | 1440                               |

| TDES                 | 6.6                                 | 660                                |

| AES-128              | 9.0                                 | 900                                |

| AES-192              | 7.9                                 | 790                                |

| AES-256              | 7.2                                 | 720                                |

| MD5                  | 15.6                                | 1560                               |

| SHA-1                | 13.2                                | 1320                               |

| SHA-256              | 9.3                                 | 930                                |

## REGISTER 28-30: ADCEISTAT1: ADC EARLY INTERRUPT STATUS REGISTER 1

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 04.04        | R-0, HS, HC            |

| 31:24        | EIRDY31 <sup>(1)</sup> | EIRDY30 <sup>(1)</sup> | EIRDY29 <sup>(1)</sup> | EIRDY28 <sup>(1)</sup> | EIRDY27 <sup>(1)</sup> | EIRDY26 <sup>(1)</sup> | EIRDY25 <sup>(1)</sup> | EIRDY24 <sup>(1)</sup> |

|              | R-0, HS, HC            |

| 23:16        | EIRDY23 <sup>(1)</sup> | EIRDY22 <sup>(1)</sup> | EIRDY21 <sup>(1)</sup> | EIRDY20 <sup>(1)</sup> | EIRDY19 <sup>(1)</sup> | EIRDY18                | EIRDY17                | EIRDY16                |

| 45.0         | R-0, HS, HC            |

| 15:8         | EIRDY15                | EIRDY14                | EIRDY13                | EIRDY12                | EIRDY11                | EIRDY10                | EIRDY9                 | EIRDY8                 |

| 7.0          | R-0, HS, HC            |

| 7:0          | EIRDY7                 | EIRDY6                 | EIRDY5                 | EIRDY4                 | EIRDY3                 | EIRDY2                 | EIRDY1                 | EIRDY0                 |

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                     |

|-------------------|-------------------|-------------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared $x = Bit$ is unknown |

## bit 31-0 EIRDY31:EIRDY0: Early Interrupt for Corresponding Analog Input Ready bits

- 1 = This bit is set when the early interrupt event occurs for the specified analog input. An interrupt will be generated if early interrupts are enabled in the ADCEIEN1 register. For the Class 1 analog inputs, this bit will set as per the configuration of the ADCEIS<2:0> bits in the ADCXTIME register. For the shared ADC module, this bit will be set as per the configuration of the ADCEIS<2:0> bits in the ADCCON2 register.

- 0 = Interrupts are disabled

Note 1: This bit is not available on 64-pin devices.

| IC32MZ Embe | <br>nectivity w | illi Fioalii | ig Politi Oi | iii (Er) rai |  |

|-------------|-----------------|--------------|--------------|--------------|--|

| OTES:       |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

|             |                 |              |              |              |  |

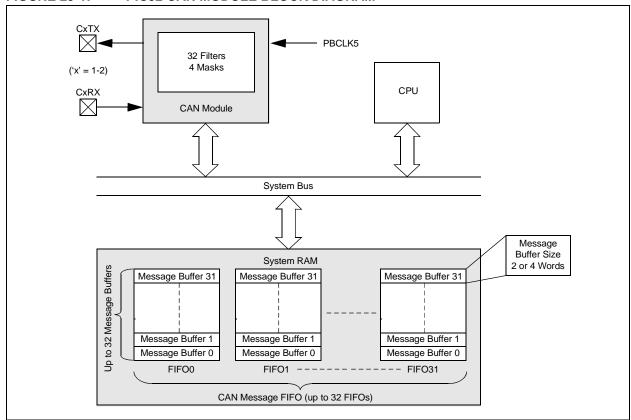

# 29.0 CONTROLLER AREA NETWORK (CAN)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Controller Area Network (CAN)" (DS60001154) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Controller Area Network (CAN) module supports the following key features:

- Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- Message Reception and Transmission:

- 32 message FIFOs

- Each FIFO can have up to 32 messages for a total of 1024 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 32 acceptance filters for message filtering

- Four acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

- DeviceNet<sup>™</sup> addressing support

- · Additional Features:

- Loopback, Listen All Messages and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32 System Bus

- Use of DMA is not required

- Dedicated time-stamp timer

- Dedicated DMA channels

- Data-only Message Reception mode

Figure 29-1 illustrates the general structure of the CAN module.

#### FIGURE 29-1: PIC32 CAN MODULE BLOCK DIAGRAM

| 0          |

|------------|

| 201        |

| 5-201      |

| <u></u>    |

| Microchip  |

| Technology |

| nc.        |

| ess                         |                                 |           |               |               |               |         |               |         |         | Bi            | its        |         |               |               |            |         |           |          |            |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------|---------------|---------|---------|---------------|------------|---------|---------------|---------------|------------|---------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12   | 27/11         | 26/10   | 25/9    | 24/8          | 23/7       | 22/6    | 21/5          | 20/4          | 19/3       | 18/2    | 17/1      | 16/0     | All Resets |

|                             | ETH                             | 31:16     | _             |               | _             | _       | _             |         | _       | _             | _          | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2110                        | FRMTXOK                         | 15:0      |               |               |               | •       |               |         |         | FRMTXOK       | CNT<15:0>  | •       |               |               | •          | •       | •         | •        | 0000       |

| 2120                        | ETH                             | 31:16     | _             |               | _             | _       | -             |         | _       | -             | _          | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2120                        | SCOLFRM                         | 15:0      |               |               |               | 1       |               |         |         | SCOLFRM       | CNT<15:0>  | 1       |               |               | 1          | 1       | ı         | 1        | 0000       |

| 2130                        | ETH                             | 31:16     | _             | _             | _             | _       | _             | _       | _       | _             | _          | _       | _             | _             | _          | _       | _         | _        | 0000       |

|                             | MCOLFRM                         | 15:0      |               |               |               |         |               |         |         | MCOLFRM       | CNT<15:0>  |         |               |               |            |         |           |          | 0000       |

| 2140                        | ETH                             | 31:16     | _             | _             | _             | _       | _             | _       | _       |               |            | _       | _             | _             | _          | _       | _         | _        | 0000       |

|                             | FRMRXOK                         | 15:0      |               |               | 1             | 1       |               |         | 1       | FRMRXOK       | CNT<15:0>  | I       |               |               |            |         | l         | l        | 0000       |

| 2150                        | ETH<br>FCSERR                   | 31:16     | _             |               | _             | _       |               |         | _       |               |            | _       | _             | _             | _          | _       | _         | _        | 0000       |

|                             |                                 | 15:0      |               |               |               |         |               |         |         | FCSERRO       |            |         |               |               |            |         |           |          | 0000       |

| 2160                        | ETH<br>ALGNERR                  | 31:16     | _             | _             | _             | _       | _             | _       | _       |               | — ONT 45:0 | _       | _             | _             | _          | _       | _         | _        | 0000       |

|                             | ALGINLIKIK                      | 15:0      |               |               |               |         |               |         |         | ALGNERR       |            |         |               |               |            |         |           |          | 0000       |

| 2200                        | EMAC1                           | 31:16     | -<br>SOFT     | —<br>SIM      | _             | _       | —<br>RESET    | RESET   | RESET   | —<br>RESET    | _          | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2200                        | CFG1                            | 15:0      | RESET         | RESET         | _             | _       | RMCS          | RESET   | TMCS    | TFUN          |            | _       | _             | LOOPBACK      | TXPAUSE    | RXPAUSE | PASSALL   | RXENABLE | 800D       |

|                             | EMAC1                           | 31:16     | _             | _             | _             | _       | _             | _       | _       | _             | _          | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2210                        | CFG2                            | 15:0      | _             | EXCESS<br>DFR | BP<br>NOBKOFF | NOBKOFF | _             | _       | LONGPRE | PUREPRE       | AUTOPAD    | VLANPAD | PAD<br>ENABLE | CRC<br>ENABLE | DELAYCRC   | HUGEFRM | LENGTHCK  | FULLDPLX | 4082       |

| 0000                        | EMAC1                           | 31:16     | _             | -             | _             | _       | _             | -       | _       | _             | -          | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2220                        | IPGT                            | 15:0      | _             | I             | _             | _       | _             |         | _       | _             |            |         |               | B2            | 2BIPKTGP<6 | :0>     |           |          | 0012       |

| 2230                        | EMAC1                           | 31:16     | _             | -             | _             | _       | _             | ı       | _       | _             | -          | _       | -             | _             | _          | _       | _         | _        | 0000       |

| 2230                        | IPGR                            | 15:0      | _             |               |               | NB2     | BIPKTGP1<6    | 6:0>    |         |               | _          |         |               | NB:           | 2BIPKTGP2< | 6:0>    |           |          | 0C12       |

| 2240                        | EMAC1                           | 31:16     | _             | _             | _             | _       | _             | _       | _       | _             | _          | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2240                        | CLRT                            | 15:0      | _             | _             |               |         | CWINDO        | )W<5:0> |         |               | _          | _       | _             | _             |            | RET     | <<3:0>    |          | 370F       |

| 2250                        | EMAC1                           | 31:16     | _             | _             | _             | _       | _             | _       | _       | _             | _          | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2200                        | MAXF                            | 15:0      |               |               | ı             |         |               |         |         | MACMA)        | KF<15:0>   | ı       |               | ı             | I          | ı       | ı         | ı        | 05EE       |

|                             | EMAC1                           | 31:16     | _             |               | _             | _       | _             |         | _       | _             | _          | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2260                        | SUPP                            | 15:0      | _             | _             | _             | _       | RESET<br>RMII | _       | _       | SPEED<br>RMII | _          | _       | _             | _             | _          | _       | _         | _        | 1000       |

| 2270                        | EMAC1                           | 31:16     | _             | _             | _             | _       | _             | _       | _       | _             | _          | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2270                        | TEST                            | 15:0      | _             | -             | _             | _       | _             | ı       | _       | _             | _          | _       | _             | _             | _          | TESTBP  | TESTPAUSE | SHRTQNTA | 0000       |

|                             | EMAC1                           | 31:16     | _             |               | _             | _       | _             | _       | _       | _             | _          | _       | _             | _             |            | _       | _         |          | 0000       |

| 2280                        | MCFG                            | 15:0      | RESET<br>MGMT | ı             | _             | _       | -             | ı       | -       |               | -          | _       |               | CLKSE         | :L<3:0>    |         | NOPRE     | SCANINC  | 0020       |

| 2200                        | EMAC1                           | 31:16     | _             | _             | _             | _       | _             | _       | _       | _             |            | _       | _             | _             | _          | _       | _         | _        | 0000       |

| 2290                        | MCMD                            | 15:0      | _             | _             | _             | _       | _             | _       | _       | _             | _          | _       | _             | _             | _          | _       | SCAN      | READ     | 0000       |

|                             | EMAC1                           | 31:16     | _             |               | _             | _       |               |         | _       | _             |            | _       | _             | _             | _          |         |           | _        | 0000       |

| 22A0                        |                                 |           |               |               |               |         |               |         |         |               |            |         |               |               |            |         |           |          |            |

Legend: Note 1:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and **INV Registers"** for more information.

<sup>2:</sup> Reset values default to the factory programmed value.

#### REGISTER 30-2: ETHCON2: ETHERNET CONTROLLER CONTROL REGISTER 2

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|