Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

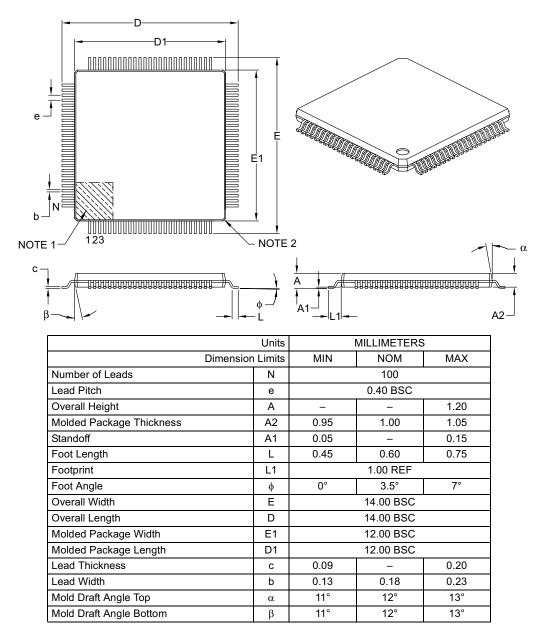

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024eff100-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-6: SYSTEM BUS TARGETS AND ASSOCIATED PROTECTION REGISTERS

|                  |                                                                        |          |                                             | SBTxREC                      | Gy Register                                |                  |                   |                   | SBTxRD  | y Register                                                      | SBTxWRy Register |                                                                  |

|------------------|------------------------------------------------------------------------|----------|---------------------------------------------|------------------------------|--------------------------------------------|------------------|-------------------|-------------------|---------|-----------------------------------------------------------------|------------------|------------------------------------------------------------------|

| Target<br>Number | Target Description <sup>(5)</sup>                                      | Name     | Region Base<br>(BASE<21:0>)<br>(see Note 2) | Physical<br>Start<br>Address | Region Size<br>(SIZE<4:0>)<br>(see Note 3) | Region<br>Size   | Priority<br>(PRI) | Priority<br>Level | Name    | Read<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) | Name             | Write<br>Permissior<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) |

| <u>^</u>         | System Bus                                                             | SBT0REG0 | R                                           | 0x1F8F0000                   | R                                          | 64 KB            | —                 | 0                 | SBT0RD0 | R/W <sup>(1)</sup>                                              | SBT0WR0          | R/W <sup>(1)</sup>                                               |

| 0                |                                                                        | SBT0REG1 | R                                           | 0x1F8F8000                   | R                                          | 32 KB            | —                 | 3                 | SBT0RD1 | R/W <sup>(1)</sup>                                              | SBT0WR1          | R/W <sup>(1)</sup>                                               |

|                  | Flash Memory <sup>(6)</sup> :                                          | SBT1REG0 | R                                           | 0x1D000000                   | R <sup>(4)</sup>                           | R <sup>(4)</sup> | —                 | 0                 | SBT1RD0 | R/W <sup>(1)</sup>                                              | SBT1WR0          | 0, 0, 0, 0                                                       |

|                  | Program Flash<br>Boot Flash                                            | SBT1REG2 | R                                           | 0x1F8E0000                   | R                                          | 4 KB             | 1                 | 2                 | SBT1RD2 | R/W <sup>(1)</sup>                                              | SBT1WR2          | R/W <sup>(1)</sup>                                               |

|                  | Prefetch Module                                                        | SBT1REG3 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD3 | R/W <sup>(1)</sup>                                              | SBT1WR3          | 0, 0, 0, 0                                                       |

| 4                |                                                                        | SBT1REG4 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD4 | R/W <sup>(1)</sup>                                              | SBT1WR4          | 0, 0, 0, 0                                                       |

| 1                |                                                                        | SBT1REG5 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD5 | R/W <sup>(1)</sup>                                              | SBT1WR5          | 0, 0, 0, 0                                                       |

|                  |                                                                        | SBT1REG6 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD6 | R/W <sup>(1)</sup>                                              | SBT1WR6          | 0, 0, 0, 0                                                       |

|                  |                                                                        | SBT1REG7 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT1RD7 | R/W <sup>(1)</sup>                                              | SBT1WR7          | 0, 0, 0, 0                                                       |

|                  |                                                                        | SBT1REG8 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT1RD8 | R/W <sup>(1)</sup>                                              | SBT1WR8          | 0, 0, 0, 0                                                       |

|                  | RAM Bank 1 Memory                                                      | SBT2REG0 | R                                           | 0x00000000                   | R <sup>(4)</sup>                           | R <sup>(4)</sup> | _                 | 0                 | SBT2RD0 | R/W <sup>(1)</sup>                                              | SBT2WR0          | R/W <sup>(1)</sup>                                               |

| 2                |                                                                        | SBT2REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | —                 | 3                 | SBT2RD1 | R/W <sup>(1)</sup>                                              | SBT2WR1          | R/W <sup>(1)</sup>                                               |

|                  |                                                                        | SBT2REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT2RD2 | R/W <sup>(1)</sup>                                              | SBT2WR2          | R/W <sup>(1)</sup>                                               |

|                  | RAM Bank 2 Memory                                                      | SBT3REG0 | R <sup>(4)</sup>                            | R <sup>(4)</sup>             | R <sup>(4)</sup>                           | R <sup>(4)</sup> | —                 | 0                 | SBT3RD0 | R/W <sup>(1)</sup>                                              | SBT3WR0          | R/W <sup>(1)</sup>                                               |

| 3                |                                                                        | SBT3REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | —                 | 3                 | SBT3RD1 | R/W <sup>(1)</sup>                                              | SBT3WR1          | R/W <sup>(1)</sup>                                               |

|                  |                                                                        | SBT3REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT3RD2 | R/W <sup>(1)</sup>                                              | SBT3WR2          | R/W <sup>(1)</sup>                                               |

| 4                | External Memory via EBI and EBI Module <sup>(6)</sup>                  | SBT4REG0 | R                                           | 0x20000000                   | R                                          | 64 MB            | —                 | 0                 | SBT4RD0 | R/W <sup>(1)</sup>                                              | SBT4WR0          | R/W <sup>(1)</sup>                                               |

| 4                | Module                                                                 | SBT4REG2 | R                                           | 0x1F8E1000                   | R                                          | 4 KB             | 0                 | 1                 | SBT4RD2 | R/W <sup>(1)</sup>                                              | SBT4WR2          | R/W <sup>(1)</sup>                                               |

|                  | Peripheral Set 1:<br>System Control                                    | SBT5REG0 | R                                           | 0x1F800000                   | R                                          | 128 KB           | _                 | 0                 | SBT5RD0 | R/W <sup>(1)</sup>                                              | SBT5WR0          | R/W <sup>(1)</sup>                                               |

|                  | Flash Control                                                          | SBT5REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | —                 | 3                 | SBT5RD1 | R/W <sup>(1)</sup>                                              | SBT5WR1          | R/W <sup>(1)</sup>                                               |

| 5                | DMT/WDT<br>RTCC<br>CVR<br>PPS Input<br>PPS Output<br>Interrupts<br>DMA | SBT5REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT5RD2 | R/W <sup>(1)</sup>                                              | SBT5WR2          | R/W <sup>(1)</sup>                                               |

**Note** 1: Reset values for these bits are '0', '1', '1', '1', respectively.

2: The BASE<21:0> bits must be set to the corresponding Physical Address and right shifted by 10 bits. For Read-only bits, this value is set by hardware on Reset.

3: The SIZE<4:0> bits must be set to the corresponding Region Size, based on the following formula: Region Size = 2<sup>(SIZE-1)</sup> x 1024 bytes. For read-only bits, this value is set by hardware on Reset.

4: Refer to the Device Memory Maps (Figure 4-1 through Figure 4-4) for specific device memory sizes and start addresses.

5: See Table 4-1for information on specific target memory size and start addresses.

6: The SBTxREG1 SFRs are reserved, and therefore, are not listed in this table for this target.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0                  | U-0                  | U-0                  | U-0                  | U-0                  |

| 31:24        | —                 | —                 | _                 | —                    | —                    | —                    | _                    | —                    |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0                  | U-0                  | U-0                  | U-0                  |

| 23:16        | —                 | —                 | _                 | —                    | _                    |                      | _                    | _                    |

| 45.0         | R/W-1             | U-0               | U-0               | R/W-1                | R/W-1                | R/W-1                | R/W-1                | R/W-1                |

| 15:8         | LBWPULOCK         | —                 | _                 | LBWP4 <sup>(1)</sup> | LBWP3 <sup>(1)</sup> | LBWP2 <sup>(1)</sup> | LBWP1 <sup>(1)</sup> | LBWP0 <sup>(1)</sup> |

| 7.0          | R/W-1             | r-1               | U-0               | R/W-1                | R/W-1                | R/W-1                | R/W-1                | R/W-1                |

| 7:0          | UBWPULOCK         | _                 |                   | UBWP4 <sup>(1)</sup> | UBWP3 <sup>(1)</sup> | UBWP2 <sup>(1)</sup> | UBWP1 <sup>(1)</sup> | UBWP0 <sup>(1)</sup> |

# REGISTER 5-8: NVMBWP: FLASH BOOT (PAGE) WRITE-PROTECT REGISTER

| Legend:           |                  | r = Reserved             |                    |  |  |  |

|-------------------|------------------|--------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

| bit 15  |     | LBWPULOCK: Lower Boot Alias Write-protect Unlock bit                                                                                                                                                            |

|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |     | 1 = LBWPx bits are not locked and can be modified                                                                                                                                                               |

|         |     | 0 = LBWPx bits are locked and cannot be modified                                                                                                                                                                |

|         |     | This bit is only clearable and cannot be set except by any reset.                                                                                                                                               |

| bit 14- | -13 | Unimplemented: Read as '0'                                                                                                                                                                                      |

| bit 12  |     | LBWP4: Lower Boot Alias Page 4 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC10000 through 0x1FC13FFF enabled</li> <li>0 = Write protection for physical address 0x01FC10000 through 0x1FC13FFF disabled</li> </ul>                 |

| bit 11  |     | LBWP3: Lower Boot Alias Page 3 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC0C000 through 0x1FC0FFFF enabled</li> <li>0 = Write protection for physical address 0x01FC0C000 through 0x1FC0FFFF disabled</li> </ul>                 |

| bit 10  |     | LBWP2: Lower Boot Alias Page 2 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC08000 through 0x1FC0BFFF enabled</li> <li>0 = Write protection for physical address 0x01FC08000 through 0x1FC0BFFF disabled</li> </ul>                 |

| bit 9   |     | LBWP1: Lower Boot Alias Page 1 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC04000 through 0x1FC07FFF enabled</li> <li>0 = Write protection for physical address 0x01FC04000 through 0x1FC07FFF disabled</li> </ul>                 |

| bit 8   |     | LBWP0: Lower Boot Alias Page 0 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC00000 through 0x1FC03FFF enabled</li> <li>0 = Write protection for physical address 0x01FC00000 through 0x1FC03FFF disabled</li> </ul>                 |

| bit 7   |     | UBWPULOCK: Upper Boot Alias Write-protect Unlock bit                                                                                                                                                            |

|         |     | <ul> <li>1 = UBWPx bits are not locked and can be modified</li> <li>0 = UBWPx bits are locked and cannot be modified</li> <li>This bit is only user-clearable and cannot be set except by any reset.</li> </ul> |

| bit 6   |     | Reserved: This bit is reserved for use by development tools                                                                                                                                                     |

| bit 5   |     | Unimplemented: Read as '0'                                                                                                                                                                                      |

|         |     |                                                                                                                                                                                                                 |

| Note    | 1:  | These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (LBWPULOCK or UBWPULOCK) is set.                                                                         |

Note: The bits in this register are only writable when the NVMKEY unlock sequence is followed.

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>)                   |                                 | ø           |       |       |       |       | -                                                           |         |            | Bi                    | ts   |              |      |                              |              |               |                   |                       | s          |

|-----------------------------|---------------------------------|-------------|-------|-------|-------|-------|-------------------------------------------------------------|---------|------------|-----------------------|------|--------------|------|------------------------------|--------------|---------------|-------------------|-----------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range   | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                                                       | 26/10   | 25/9       | 24/8                  | 23/7 | 22/6         | 21/5 | 20/4                         | 19/3         | 18/2          | 17/1              | 16/0                  | All Resets |

| 0050                        | 100.44                          | 31:16       | _     | —     | —     |       | FCEIP<2:0>                                                  |         | FCEIS      | <1:0>                 | _    | _            | —    |                              | RTCCIP<2:0   | )>            | RTCCI             | S<1:0>                | 0000       |

| 03D0                        | IPC41                           | 15:0        | _     | _     | _     |       | SPI4TXIP<2:0                                                | )>      | SPI4TXI    | S<1:0>                | -    | _            | -    | SPI4RXIP<2:0>                |              | SPI4RXIS<1:0> |                   | 0000                  |            |

| 0250                        | IPC42                           | 31:16       |       | _     | _     |       | U4RXIP<2:0:                                                 | >       | U4RXIS     | S<1:0>                | _    | _            | _    |                              | U4EIP<2:0:   | >             | U4EIS             | S<1:0>                | 0000       |

| 03E0                        | IPC42                           | 15:0 -      |       | _     | —     |       | SQI1IP<2:0>                                                 |         | SQI1IS     | 5<1:0>                | _    | _            | _    |                              | PREIP<2:0    | >             | PREIS             | S<1:0>                | 0000       |

| 0250                        | IPC43                           | 31:16       | _     | _     | —     |       | I2C4MIP<2:0>                                                |         | I2C4MI     | S<1:0>                | _    | _            | _    |                              | I2C4SIP<2:0  | )>            | I2C4SI            | S<1:0>                | 0000       |

| 03F0                        | IPC43                           | 15:0        |       | _     | _     |       | I2C4BIP<2:0:                                                | I2C4BIS | S<1:0>     | _                     | _    | -            |      | U4TXIP<2:0                   | >            | U4TXI         | S<1:0>            | 0000                  |            |

| 0.400                       | 10044                           | 31:16       | _     | _     | —     |       | U5EIP<2:0>                                                  |         | U5EIS      | <1:0>                 | _    | _            | _    | SPI5TXIP<2:0> <sup>(2)</sup> |              | SPI5TXIS      | S<1:0> <b>(2)</b> | 0000                  |            |

| 0400                        | IPC44                           | 15:0        | -     | _     | —     | 5     | SPI5RXIP<2:0>(2)                                            |         | SPI5RXIS   | S<1:0> <b>(2)</b>     | —    | _            | -    | 5                            | SPI5EIP<2:0: | >(2)          | SPI5EIS           | S<1:0> <b>(2)</b>     | 0000       |

| 0410                        | IPC45                           | 31:16       | _     | _     | _     |       | I2C5SIP<2:0>                                                |         | 12C5S1     | S<1:0>                |      | _            | —    |                              | I2C5BIP<2:0  | )>            | I2C5BI            | S<1:0>                | 0000       |

| 0410                        | IPC45                           | 15:0        |       | _     | _     |       | U5TXIP<2:0:                                                 | >       | U5TXIS     | 6<1:0>                | _    | _            | _    |                              | U5RXIP<2:0   | )>            | U5RXI             | S<1:0>                | 0000       |

| 0420                        | IPC46                           | 31:16       | _     | _     | _     | S     | SPI6TXIP<2:0> <sup>(2)</sup><br>SPI6EIP<2:0> <sup>(2)</sup> |         | SPI6TXIS   | 6<1:0> <sup>(2)</sup> | -    | _            | —    | SPI6RXIP<2:0> <sup>(2)</sup> |              |               | SPI6RXI           | S<1:0> <sup>(2)</sup> | 0000       |

| 0420                        |                                 | 15:0        | _     | _     | _     |       |                                                             |         | SPI6EIS    | <1:0> <sup>(2)</sup>  |      | _            | —    | I2C5MIP<2:0>                 |              |               | I2C5MI            | S<1:0>                | 0000       |

| 0420                        | IPC47                           | 31:16       | _     | —     | —     | —     |                                                             |         | -          |                       |      | _            | _    | U6TXIP<2:0>                  |              | U6TXI         | S<1:0>            | 0000                  |            |

| 0430                        | IFC47                           | 15:0        | _     | -     | —     |       | U6RXIP<2:0:                                                 | >       | U6RXIS     | S<1:0>                |      | _            | —    | U6EIP<2:0>                   |              |               | U6EIS             | 6<1:0>                | 0000       |

| 0440                        | IPC48                           | 31:16       | _     | _     | _     | _     | _                                                           |         | _          |                       |      | _            | —    | ADCURDYIP<2:0>               |              | ADCURD        | YIS<1:0>          | 0000                  |            |

| 0440                        | IF U40                          | 15:0        | _     | —     | —     | A     | DCARDYIP<2                                                  | :0>     | ADCARD     | YIS<1:0>              |      | _            | _    | ADCEOSIP<2:0>                |              | ADCEOSIS<1:0> |                   | 0000                  |            |

| 0450                        | IPC49                           | 31:16       | _     | -     | —     |       | ADC1EIP<2:0                                                 | >       | ADC1EI     | ADC1EIS<1:0> A        |      | ADC0EIP<2:0> |      | ADC0E                        | IS<1:0>      | 0000          |                   |                       |            |

| 0430                        | 1FC49                           | 15:0        | _     | —     | —     | _     | _                                                           | _       | _          | _                     |      |              |      | A                            | DCGRPIP<2    | 2:0>          | ADCGRPIS<1:0>     |                       | 0000       |

| 0460                        | IPC50                           | 31:16       | _     | _     | _     | _     | _                                                           |         | _          |                       |      |              |      |                              | ADC4EIP<2:   | 0>            | ADC4E             | IS<1:0>               | 0000       |

| 0400                        | 1FC30                           | 15:0        | _     | _     | _     |       | ADC3EIP<2:0                                                 | >       | ADC3EI     | S<1:0>                |      |              |      |                              | ADC2EIP<2:   | 0>            | ADC2E             | IS<1:0>               | 0000       |

| 0470                        | IPC51                           | 31:16       | _     | _     | _     |       | ADC1WIP<2:0                                                 | )>      | ADC1W      | IS<1:0>               |      |              |      |                              | ADC0WIP<2:   | :0>           | ADC0W             | 'IS<1:0>              | 0000       |

| 0470                        | IPC51                           | 15:0        |       | _     | _     |       | ADC7EIP<2:0                                                 | >       | ADC7EI     | S<1:0>                |      |              |      | _                            | _            | _             | -                 | _                     | 0000       |

| 0490                        | IPC52                           | 31:16       | _     | _     | _     | _     | _                                                           | -       | _          |                       |      |              |      |                              | ADC4WIP<2:   | :0>           | ADC4W             | 'IS<1:0>              | 0000       |

| 0460                        | IPC52                           | 15:0        |       | —     | _     |       | ADC3WIP<2:0                                                 | )>      | ADC3W      | IS<1:0>               |      |              |      |                              | ADC2WIP<2:   | :0>           | ADC2W             | 'IS<1:0>              | 0000       |

| 0400                        | IPC53                           | 31:16       | -     | _     | _     | —     | -                                                           | —       | -          | _                     |      |              |      | —                            | —            | —             | —                 | —                     | 0000       |

| 0490                        | IPC53                           | 15:0        | _     | _     | —     |       | ADC7WIP<2:0>                                                |         | ADC7W      | IS<1:0>               |      |              |      | _                            | _            | —             | _                 | _                     | 0000       |

| 0540                        | 055000                          | 31:16       | _     | —     | —     | _     |                                                             |         | _          | —                     | _    | —            | -    | _                            | —            | —             | VOFF<             | :17:16>               | 0000       |

| 0540                        | OFF000                          | 15:0        |       |       |       |       |                                                             |         |            | VOFF<15:1>            |      |              |      |                              |              |               |                   | —                     | 0000       |

| 0544                        | 055004                          | 31:16       | _     | —     | —     | _     | —                                                           | —       | —          | —                     | —    | _            | —    | —                            | —            | _             | VOFF<             | :17:16>               | 0000       |

| 0544                        | 0FF001                          | OFF001 15:0 |       |       |       |       |                                                             |         | VOFF<15:1> |                       |      |              |      |                              |              |               |                   | 0000                  |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

3: This bit or register is not available on devices without a CAN module.

4: This bit or register is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

# TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| ss                          |                  |               | Bits                                                                                                                 |                                          |       |       |       |        |              |          |                 |          |             |      |           |             |        |       |            |

|-----------------------------|------------------|---------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------|-------|-------|--------|--------------|----------|-----------------|----------|-------------|------|-----------|-------------|--------|-------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15                                                                                                                | 30/14                                    | 29/13 | 28/12 | 27/11 | 26/10  | 25/9         | 24/8     | 23/7            | 22/6     | 21/5        | 20/4 | 19/3      | 18/2        | 17/1   | 16/0  | All Resets |

| 3248                        | USB              | 31:16         |                                                                                                                      |                                          |       |       |       |        |              | DMA      | ADDR<31:16      | >        |             |      |           |             |        |       | 0000       |

| 3248                        | DMA5A            | 15:0          |                                                                                                                      |                                          |       |       |       |        |              | DM       | ADDR<15:0       | •        |             |      |           |             |        |       | 0000       |

| 324C                        | USB              | 31:16         |                                                                                                                      |                                          |       |       |       |        |              | DMA      | COUNT<31:10     | i>       |             |      |           |             |        |       | 0000       |

| 0240                        | DMA5N            | 15:0          |                                                                                                                      |                                          |       | -     |       |        |              | DMA      | COUNT<15:0      | >        |             |      |           |             |        |       | 0000       |

| 3254                        | USB              | 31:16         | _                                                                                                                    | _                                        | —     | —     |       | _      | —            | -        | _               | —        | —           | -    | -         | -           | _      | -     | 0000       |

|                             | DMA6C            | 15:0          | —                                                                                                                    | —                                        | —     |       | -     | DMABR  | STM<1:0>     | DMAERR   |                 |          | EP<3:0>     |      | DMAIE     | DMAMODE     | DMADIR | DMAEN |            |

| 3258                        | USB<br>DMA6A     | 31:16         |                                                                                                                      |                                          |       |       |       |        |              |          | ADDR<31:16      |          |             |      |           |             |        |       | 0000       |

|                             |                  | 15:0          |                                                                                                                      |                                          |       |       |       |        |              |          | ADDR<15:0       |          |             |      |           |             |        |       | 0000       |

| 325C                        | USB<br>DMA6N     | 31:16         |                                                                                                                      | DMACOUNT<31:16> 0000 DMACOUNT<15:0> 0000 |       |       |       |        |              |          |                 |          |             |      |           |             |        |       |            |

| $\vdash$                    |                  | 15:0          |                                                                                                                      |                                          |       |       |       |        |              |          |                 |          |             |      |           |             |        |       |            |

| 3264                        | USB<br>DMA7C     | 31:16<br>15:0 |                                                                                                                      |                                          | _     |       | _     |        | <br>STM<1:0> |          | —               |          | <br>EP<3:0> | _    | <br>DMAIE | <br>DMAMODE |        |       |            |

|                             |                  | 31:16         | —                                                                                                                    | _                                        | —     |       | _     | DIMABR | 51M<1:0>     | DMAERR   | ADDR<31:16      |          | EP<3:0>     |      | DIVIAIE   | DMAMODE     | DMADIR | DMAEN | 0000       |

| 3268                        | USB<br>DMA7A     | 15:0          |                                                                                                                      |                                          |       |       |       |        |              |          | ADDR<15:0:      |          |             |      |           |             |        |       | 0000       |

|                             | USB              | 31:16         |                                                                                                                      |                                          |       |       |       |        |              |          | COUNT<31:10     |          |             |      |           |             |        |       | 0000       |

| 326C                        | DMA7N            | 15:0          |                                                                                                                      |                                          |       |       |       |        |              |          | COUNT<15:0      |          |             |      |           |             |        |       | 0000       |

|                             | USB              | 31:16         | _                                                                                                                    | _                                        |       | _     | _     | _      | _            | _        | _               | _        | _           | _    | _         | _           | _      | _     | 0000       |

| 3274                        | DMA8C            | 15:0          | _                                                                                                                    | _                                        | _     | _     | _     | DMABR  | STM<1:0>     | DMAERR   |                 | DMA      | EP<3:0>     |      | DMAIE     | DMAMODE     | DMADIR | DMAEN | 0000       |

| 0070                        | USB              | 31:16         |                                                                                                                      |                                          |       |       |       | 1      |              | DMA      | ADDR<31:16      | >        |             |      | 1         |             | 1      | J     | 0000       |

| 3278                        | DMA8A            | 15:0          |                                                                                                                      |                                          |       |       |       |        |              | DM       | ADDR<15:0       | •        |             |      |           |             |        |       | 0000       |

| 327C                        | USB              | 31:16         |                                                                                                                      |                                          |       |       |       |        |              | DMA      | COUNT<31:10     | i>       |             |      |           |             |        |       | 0000       |

| 3270                        | DMA8N            | 15:0          |                                                                                                                      |                                          |       |       |       |        |              | DMA      | COUNT<15:0      | >        |             |      |           |             |        |       | 0000       |

| 3304                        | USB              | 31:16         | —                                                                                                                    |                                          | —     | _     | —     | _      | —            | —        | _               | —        | _           | -    | —         | _           | _      | —     | 0000       |

| 5504                        | E1RPC            | 15:0          |                                                                                                                      |                                          |       | -     |       | -      |              | RQP      | KTCNT<15:0      | >        |             | -    |           |             |        |       | 0000       |

| 3308                        | USB              | 31:16         | —                                                                                                                    | —                                        | —     | —     | -     | —      | —            | —        | —               | —        | -           | -    | —         | -           | —      | —     | 0000       |

|                             | E2RPC            | 15:0          |                                                                                                                      |                                          |       |       |       |        |              | RQP      | KTCNT<15:0      | >        | 1           |      |           |             |        |       | 0000       |

| 330C                        | USB              | 31:16         | _                                                                                                                    | _                                        | —     |       | —     |        | —            | —        |                 |          | _           | _    | _         | _           | _      | —     | 0000       |

|                             | E3RPC            | 15:0          |                                                                                                                      |                                          |       |       | 1     |        |              |          | KTCNT<15:0      |          |             |      |           |             |        |       | 0000       |

| 3310                        | USB<br>E4RPC     | 31:16         | _                                                                                                                    | _                                        | —     |       | -     | _      | —            | <u> </u> | -               | _        | _           | -    | _         | _           | _      |       | 0000       |

| $\vdash$                    |                  | 15:0          |                                                                                                                      |                                          |       |       |       |        |              |          | KTCNT<15:0      |          |             |      |           |             |        |       | 0000       |

| 3314                        | USB<br>E5RPC     | 31:16<br>15:0 | —                                                                                                                    | _                                        | —     | _     | —     | _      | —            |          |                 | _        | —           | —    | _         | —           | —      | —     | 0000       |

| $\vdash$                    |                  |               |                                                                                                                      |                                          |       |       |       |        |              |          | KTCNT<15:0      |          |             |      |           |             |        |       | 0000       |

| 3318                        | USB<br>E6RPC     | 31:16<br>15:0 | —                                                                                                                    | _                                        | —     | _     | _     | _      | _            |          | —<br>KTCNT<15:0 | _        | _           | _    | _         | _           | _      | —     | 0000       |

| $\vdash$                    |                  | 31:16         | _                                                                                                                    | _                                        | _     |       |       | _      |              |          |                 | <u> </u> |             | _    | _         | _           |        | _     | 0000       |

| 331C                        | USB<br>E7RPC     | 15:0          | _                                                                                                                    | _                                        |       |       | _     |        |              | ROP      |                 |          | _           | _    |           | _           |        |       |            |

| 1                           |                  | 10.0          | 0000 RQPKTCNT<15:0> 0000 nown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |                                          |       |       |       |        |              |          |                 |          |             |      |           |             |        |       |            |

Legend: Note x = unknownDevice mode.

Host mode.

1: 2: 3: 4: Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

# REGISTER 11-5: USBIE0CSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 0) (CONTINUED)

### bit 21 SENDSTALL: Send Stall Control bit (Device mode)

- 1 = Terminate the current transaction and transmit a STALL handshake. This bit is automatically cleared.

- 0 = Do not send STALL handshake.

**REQPKT:** IN transaction Request Control bit (Host mode)

- 1 = Request an IN transaction. This bit is cleared when the RXPKTRDY bit is set.

- 0 = Do not request an IN transaction

- bit 20 SETUPEND: Early Control Transaction End Status bit (Device mode)

- 1 = A control transaction ended before the DATAEND bit has been set. An interrupt will be generated and the FIFO flushed at this time.

- 0 = Normal operation

This bit is cleared by writing a '1' to the SVCSETEND bit in this register.

#### ERROR: No Response Error Status bit (Host mode)

- 1 = Three attempts have been made to perform a transaction with no response from the peripheral. An interrupt is generated.

- 0 = Clear this flag. Software must write a '0' to this bit to clear it.

#### DATAEND: End of Data Control bit (Device mode)

The software sets this bit when:

bit 19

- Setting TXPKTRDY for the last data packet

- Clearing RXPKTRDY after unloading the last data packet

- Setting TXPKTRDY for a zero length data packet

Hardware clears this bit.

**SETUPPKT:** Send a SETUP token Control bit (*Host mode*)

- 1 = When set at the same time as the TXPKTRDY bit is set, the module sends a SETUP token instead of an OUT token for the transaction

- 0 = Normal OUT token operation

Setting this bit also clears the Data Toggle.

- bit 18 SENTSTALL: STALL sent status bit (Device mode)

- 1 = STALL handshake has been transmitted

- 0 = Software clear of bit

RXSTALL: STALL handshake received Status bit (Host mode)

- 1 = STALL handshake was received

- 0 = Software clear of bit

- bit 17 **TXPKTRDY:** TX Packet Ready Control bit

- 1 = Data packet has been loaded into the FIFO. It is cleared automatically.

- 0 = No data packet is ready for transmit

- bit 16 **RXPKTRDY:** RX Packet Ready Status bit

- 1 = Data packet has been received. Interrupt is generated (when enabled) when this bit is set.

- 0 = No data packet has been received

This bit is cleared by setting the SVCRPR bit.

bit 15-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | -                 | —                 | -                 | _                 | _                | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 |                   | —                 |                   | -                 |                  |                  |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-1               | R-0               | R-0              | R-0              |

| 10.0         | RC                |                   | VE                | RMAJOR<4:         | 0>                |                   | VERMIN           | OR<9:8>          |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | VERMIN            | OR<7:0>           |                   |                  |                  |

# REGISTER 11-15: USBHWVER: USB HARDWARE VERSION REGISTER

# Legend:

| 3                 |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 RC: Release Candidate bit

- 1 = USB module was created using a release candidate

- 0 = USB module was created using a full release

- bit 14-10 VERMAJOR<4:0>: USB Module Major Version number bits This read-only number is the Major version number for the USB module.

- bit 9-0 VERMINOR<9:0>: USB Module Minor Version number bits This read-only number is the Minor version number for the USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 |                   |                   |                   | —                 | —                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 |                   |                   |                   | —                 | —                 |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | —                 | —                 | —                 | —                 | —                 | DMABRS            | TM<1:0>          | DMAERR           |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | DMAE              | P<3:0>            |                   | DMAIE             | DMAMODE           | DMADIR           | DMAEN            |

# REGISTER 11-21: USBDMAxC: USB DMA CHANNEL 'x' CONTROL REGISTER ('x' = 1-8)

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-11 Unimplemented: Read as '0'

- bit 10-9 DMABRSTM<1:0>: DMA Burst Mode Selection bit

- 11 = Burst Mode 3: INCR16, INCR8, INCR4 or unspecified length

- 10 = Burst Mode 2: INCR8, INCR4 or unspecified length

- 01 = Burst Mode 1: INCR4 or unspecified length

- 00 = Burst Mode 0: Bursts of unspecified length

### bit 8 DMAERR: Bus Error bit

- 1 = A bus error has been observed on the input

- 0 = The software writes this to clear the error

- bit 7-4 DMAEP<3:0>: DMA Endpoint Assignment bits

- These bits hold the endpoint that the DMA channel is assigned to. Valid values are 0-7.

# bit 3 DMAIE: DMA Interrupt Enable bit

- 1 = Interrupt is enabled for this channel

- 0 = Interrupt is disabled for this channel

# bit 2 DMAMODE: DMA Transfer Mode bit

- 1 = DMA Mode1 Transfers

- 0 = DMA Mode0 Transfers

- bit 1 DMADIR: DMA Transfer Direction bit

- 1 = DMA Read (TX endpoint)

- 0 = DMA Write (RX endpoint)

# bit 0 DMAEN: DMA Enable bit

- 1 = Enable the DMA transfer and start the transfer

- 0 = Disable the DMA transfer

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   | —                 | _                 | —                 | —                 | -                 | _                | —                |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                   | —                 |                   |                   |                   |                   |                  | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | POLLCON           | N<15:8>           |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | POLLCON<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

# REGISTER 20-18: SQI1BDPOLLCON: SQI BUFFER DESCRIPTOR POLL CONTROL REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **POLLCON<15:0>:** Buffer Descriptor Processor Poll Status bits These bits indicate the number of cycles the BDP would wait before refetching the descriptor control word if the previous descriptor fetched was disabled.

# REGISTER 20-19: SQI1BDTXDSTAT: SQI BUFFER DESCRIPTOR DMA TRANSMIT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | U-0              |

| 31:24        |                   | —                 | _                 |                   | TXSTAT            | ΓE<3:0>           |                  | _                |

| 00.40        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | R-x              |

| 23:16        | —                 | —                 | _                 |                   |                   |                   |                  |                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |

| 7:0          |                   |                   |                   | TXCURBUF          | LEN<7:0>          |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

bit 28-25 **TXSTATE<3:0>:** Current DMA Transmit State Status bits These bits provide information on the current DMA receive states.

bit 24-21 Unimplemented: Read as '0'

bit 20-16 **TXBUFCNT<4:0>:** DMA Buffer Byte Count Status bits

These bits provide information on the internal FIFO space.

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **TXCURBUFLEN<7:0>:** Current DMA Transmit Buffer Length Status bits These bits provide the length of the current DMA transmit buffer.

# 21.1 I<sup>2</sup>C Control Registers

# TABLE 21-1: I2C1 THROUGH I2C5 REGISTER MAP

| ess                         |                                 |               |             |            |        |        |        |           |             | Bi         | ts         |               |               |               |               |              |              |             |            |

|-----------------------------|---------------------------------|---------------|-------------|------------|--------|--------|--------|-----------|-------------|------------|------------|---------------|---------------|---------------|---------------|--------------|--------------|-------------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14      | 29/13  | 28/12  | 27/11  | 26/10     | 25/9        | 24/8       | 23/7       | 22/6          | 21/5          | 20/4          | 19/3          | 18/2         | 17/1         | 16/0        | All Resets |

| 0000                        | I2C1CON                         | 31:16         | _           | _          | —      | —      | —      |           | —           |            |            | PCIE          | SCIE          | BOEN          | SDAHT         | SBCDE        | AHEN         | DHEN        | 0000       |

| 0000                        | 12010011                        | 15:0          | ON          |            | SIDL   | SCLREL | STRICT | A10M      | DISSLW      | SMEN       | GCEN       | STREN         | ACKDT         | ACKEN         | RCEN          | PEN          | RSEN         | SEN         | 1000       |

| 0010                        | I2C1STAT                        | 31:16         |             | —          | —      | —      |        | -         | —           | _          | —          | —             | -             | _             | _             | —            | —            | -           | 0000       |

|                             |                                 | 15:0          | ACKSTAT     | TRSTAT     | ACKTIM | _      |        | BCL       | GCSTAT      | ADD10      | IWCOL      | I2COV         | D/A           | Р             | S             | R/W          | RBF          | TBF         | 0000       |

| 0020                        | I2C1ADD                         | 31:16         | _           | _          |        |        | _      |           |             | _          | _          | —             |               |               | —             | —            |              | —           | 0000       |

|                             |                                 | 15:0          | _           |            |        |        | _      |           |             |            |            |               | Address       | Register      |               |              |              |             | 0000       |

| 0030                        | I2C1MSK                         | 31:16<br>15:0 |             |            | —      |        |        |           | —           | _          | _          | _             | - Address Mr  | ask Registe   |               | _            | —            | —           | 0000       |

|                             |                                 | 31:16         | _           |            |        |        |        |           |             |            |            |               | Address Ma    | ask Registe   |               |              |              | _           | 0000       |

| 0040                        | I2C1BRG                         | 15:0          |             |            | _      | _      | _      |           | Bau         | d Rate Gen | erator Reg | ister         | _             | _             | _             | _            | _            |             | 0000       |

|                             |                                 | 31:16         |             | _          | _      | _      |        | _         |             |            |            |               | _             | _             | _             | _            | _            | _           | 0000       |

| 0050                        | I2C1TRN                         | 15:0          | _           | _          | _      | _      |        | _         | _           | _          |            |               |               | Transmit      | Register      |              |              |             | 0000       |

|                             |                                 | 31:16         | _           | _          | _      | _      | _      | _         | _           | _          | _          | _             | _             |               | —             | _            | _            | _           | 0000       |

| 0060                        | I2C1RCV                         | 15:0          | _           | _          | _      | _      |        | _         | _           | _          |            |               |               | Receive       | Register      |              |              |             | 0000       |

|                             |                                 | 31:16         | _           | _          | _      | _      | _      | _         | _           | _          | _          | PCIE          | SCIE          | BOEN          | SDAHT         | SBCDE        | AHEN         | DHEN        | 0000       |

| 0200                        | 12C2CON <sup>(2)</sup>          | 15:0          | ON          | _          | SIDL   | SCLREL | STRICT | A10M      | DISSLW      | SMEN       | GCEN       | STREN         | ACKDT         | ACKEN         | RCEN          | PEN          | RSEN         | SEN         | 1000       |

| 0040                        | 12C2STAT <sup>(2)</sup>         | 31:16         | _           |            | _      | —      | —      |           | _           | _          |            | _             | —             | —             | _             | _            | —            |             | 0000       |

| 0210                        | 12025TAT-                       | 15:0          | ACKSTAT     | TRSTAT     | ACKTIM | _      | —      | BCL       | GCSTAT      | ADD10      | IWCOL      | I2COV         | D/A           | Р             | S             | R/W          | RBF          | TBF         | 0000       |

| 0220                        | 12C2ADD(2)                      | 31:16         | _           |            | —      | _      | _      |           | —           | _          | -          | _             | -             | _             | _             | —            | -            |             | 0000       |

| 0220                        | IZCZADD.                        | 15:0          | _           | _          | _      | —      | _      | _         |             |            |            |               | Address       | Register      |               |              | -            |             | 0000       |

| 0230                        | 12C2MSK(2)                      | 31:16         | —           | —          | —      | —      | —      | -         | —           | —          | —          | —             | —             | —             | —             | —            | —            | —           | 0000       |

| 0200                        |                                 | 15:0          | _           |            |        | —      | _      |           |             |            |            |               | Address Ma    | ask Registe   | r             |              |              |             | 0000       |

| 0240                        | 12C2BRG(2)                      | 31:16         | —           | —          | —      | —      | _      | —         | —           | —          | _          | —             | —             | —             | —             | —            | —            | —           | 0000       |

|                             |                                 | 15:0          |             |            |        |        |        |           | Bau         | d Rate Gen | erator Reg | ister         |               |               |               |              |              |             | 0000       |

| 0250                        | 12C2TRN(2)                      | 31:16         | _           |            |        | _      | _      |           | _           | _          | _          | —             |               |               |               | _            |              | _           | 0000       |

|                             |                                 | 15:0          | _           |            |        |        | _      |           |             | _          |            |               |               | Transmit      | Register      |              |              |             | 0000       |

| 0260                        | I2C2RCV(2)                      | 31:16         | _           | _          | _      | _      |        | _         | _           | _          | -          |               | —             | -             | —             | —            | —            | —           | 0000       |

|                             |                                 | 15:0          | _           |            |        |        |        |           |             | _          |            | DOIE          | 0015          | Receive       |               | 00005        |              | DUCH        | 0000       |

| 0400                        | I2C3CON                         | 31:16<br>15:0 | ON          |            |        |        |        | —<br>A10M | —<br>DISSLW | <br>SMEN   | —<br>GCEN  | PCIE<br>STREN | SCIE<br>ACKDT | BOEN<br>ACKEN | SDAHT<br>RCEN | SBCDE<br>PEN | AHEN<br>RSEN | DHEN<br>SEN | 0000       |

|                             |                                 | 31:16         |             |            | SIDL   | SULREL |        | A10M      | DISSLW      | SIMEIN     | GCEN       | STREN         | ACKDI         | ACKEN         | RCEN          | PEN          | KSEN         | SEN<br>—    | 1000       |

| 0410                        | I2C3STAT                        | 15:0          | <br>ACKSTAT | <br>TRSTAT | ACKTIM | _      |        | BCL       | GCSTAT      | ADD10      |            | I2COV         | <br>D/A       | <br>P         |               | R/W          | <br>RBF      | <br>TBF     | 0000       |

|                             |                                 | 31:16         | -           |            |        |        | _      | BCL       | GCSTAT      |            |            | 12000         |               | г<br>         | 3             | R/W          |              |             | 0000       |

| 0420                        | I2C3ADD                         | 15:0          |             |            |        |        |        |           |             |            |            |               | Address       | <br>Register  |               |              |              |             | 0000       |

| Logon                       |                                 |               |             |            |        |        |        |           | chown in h  |            |            |               | /1001033      | register      |               |              |              |             | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

2: This register is not available on 64-pin devices.

# REGISTER 22-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bit<br>11 = Reserved                                                                                                                                                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full</li> <li>01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full</li> <li>00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)</li> </ul> |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                  |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                         |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                      |