Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-TFBGA                                                                         |

| Supplier Device Package    | 144-TFBGA (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024eff144-i-jwx |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                       |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description           |

| AN36     | _                      |                 | B4              | 8                        | Ι           | Analog         | Analog Input Channels |

| AN37     | _                      | _               | B12             | 27                       | I           | Analog         |                       |

| AN38     | _                      | _               | B17             | 43                       | I           | Analog         |                       |

| AN39     | —                      | —               | A22             | 44                       | I           | Analog         |                       |

| AN40     | _                      | _               | A30             | 65                       | I           | Analog         |                       |

| AN41     | _                      | _               | B26             | 66                       | I           | Analog         |                       |

| AN42     | _                      | _               | A31             | 67                       | I           | Analog         |                       |

| AN45     | 11                     | 20              | B11             | 25                       | I           | Analog         |                       |

| AN46     | 17                     | 26              | B14             | 37                       | I           | Analog         |                       |

| AN47     | 18                     | 27              | A19             | 38                       | I           | Analog         | 1                     |

| AN48     | 21                     | 32              | B18             | 47                       | I           | Analog         |                       |

| AN49     | 22                     | 33              | A23             | 48                       | Ι           | Analog         |                       |

#### **TABLE 1-1:** ADC PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS-compatible input or output TTL = Transistor-transistor Logic input buffer

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output PPS = Peripheral Pin Select P = Power I = Input

© 2015-2016 Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

| 31:24        |                   |                   |                   | CSEQ<             | 15:8>             |                   |                  |                  |  |  |

| 00.40        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

| 23:16        | CSEQ<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

| 15:8         | TSEQ<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

| 7:0          |                   |                   |                   | TSEQ<             | <7:0>             |                   |                  |                  |  |  |

# **REGISTER 4-1: BFxSEQ3: BOOT FLASH 'x' SEQUENCE WORD 3 REGISTER ('x' = 1 AND 2)**

| Legend:           |                  | P = Programmable bit | P = Programmable bit |  |  |  |  |

|-------------------|------------------|----------------------|----------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown   |  |  |  |  |

bit 31-16 CSEQ<15:0>: Boot Flash Complement Sequence Number bits

bit 15-0 **TSEQ<15:0>:** Boot Flash True Sequence Number bits

**Note:** The BFxSEQ0, BFxSEQ1, and BFxSEQ2 registers are used for Quad Word programming operation when programming the BFxSEQ3 registers, and do not contain any valid information.

# TABLE 7-2: INTERRUPT IRQ, VECTOR, AND BIT LOCATION (CONTINUED)

|                                                 | XO20 Ve ster News             | IRQ | Maatan #     |          | Interru  | upt Bit Location | n            | Persistent |

|-------------------------------------------------|-------------------------------|-----|--------------|----------|----------|------------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>                 | XC32 Vector Name              | #   | Vector #     | Flag     | Enable   | Priority         | Sub-priority | Interrupt  |

| System Bus Protection Violation                 | _SYSTEM_BUS_PROTECTION_VECTOR | 106 | OFF106<17:1> | IFS3<10> | IEC3<10> | IPC26<20:18>     | IPC26<17:16> | Yes        |

| Crypto Engine Event                             | _CRYPTO_VECTOR                | 107 | OFF107<17:1> | IFS3<11> | IEC3<11> | IPC26<28:26>     | IPC26<25:24> | Yes        |

| Reserved                                        |                               | 108 | —            |          |          | —                |              |            |

| SPI1 Fault                                      | _SPI1_FAULT_VECTOR            | 109 | OFF109<17:1> | IFS3<13> | IEC3<13> | IPC27<12:10>     | IPC27<9:8>   | Yes        |

| SPI1 Receive Done                               | _SPI1_RX_VECTOR               | 110 | OFF110<17:1> | IFS3<14> | IEC3<14> | IPC27<20:18>     | IPC27<17:16> | Yes        |

| SPI1 Transfer Done                              | _SPI1_TX_VECTOR               | 111 | OFF111<17:1> | IFS3<15> | IEC3<15> | IPC27<28:26>     | IPC27<25:24> | Yes        |

| UART1 Fault                                     | _UART1_FAULT_VECTOR           | 112 | OFF112<17:1> | IFS3<16> | IEC3<16> | IPC28<4:2>       | IPC28<1:0>   | Yes        |

| UART1 Receive Done                              | _UART1_RX_VECTOR              | 113 | OFF113<17:1> | IFS3<17> | IEC3<17> | IPC28<12:10>     | IPC28<9:8>   | Yes        |

| UART1 Transfer Done                             | _UART1_TX_VECTOR              | 114 | OFF114<17:1> | IFS3<18> | IEC3<18> | IPC28<20:18>     | IPC28<17:16> | Yes        |

| I2C1 Bus Collision Event                        | _I2C1_BUS_VECTOR              | 115 | OFF115<17:1> | IFS3<19> | IEC3<19> | IPC28<28:26>     | IPC28<25:24> | Yes        |

| I2C1 Slave Event                                | _I2C1_SLAVE_VECTOR            | 116 | OFF116<17:1> | IFS3<20> | IEC3<20> | IPC29<4:2>       | IPC29<1:0>   | Yes        |

| I2C1 Master Event                               | _I2C1_MASTER_VECTOR           | 117 | OFF117<17:1> | IFS3<21> | IEC3<21> | IPC29<12:10>     | IPC29<9:8>   | Yes        |

| PORTA Input Change Interrupt <sup>(2)</sup>     | _CHANGE_NOTICE_A_VECTOR       | 118 | OFF118<17:1> | IFS3<22> | IEC3<22> | IPC29<20:18>     | IPC29<17:16> | Yes        |

| PORTB Input Change Interrupt                    | _CHANGE_NOTICE_B_VECTOR       | 119 | OFF119<17:1> | IFS3<23> | IEC3<23> | IPC29<28:26>     | IPC29<25:24> | Yes        |

| PORTC Input Change Interrupt                    | _CHANGE_NOTICE_C_VECTOR       | 120 | OFF120<17:1> | IFS3<24> | IEC3<24> | IPC30<4:2>       | IPC30<1:0>   | Yes        |

| PORTD Input Change Interrupt                    | _CHANGE_NOTICE_D_VECTOR       | 121 | OFF121<17:1> | IFS3<25> | IEC3<25> | IPC30<12:10>     | IPC30<9:8>   | Yes        |

| PORTE Input Change Interrupt                    | _CHANGE_NOTICE_E_VECTOR       | 122 | OFF122<17:1> | IFS3<26> | IEC3<26> | IPC30<20:18>     | IPC30<17:16> | Yes        |

| PORTF Input Change Interrupt                    | _CHANGE_NOTICE_F_VECTOR       | 123 | OFF123<17:1> | IFS3<27> | IEC3<27> | IPC30<28:26>     | IPC30<25:24> | Yes        |

| PORTG Input Change Interrupt                    | _CHANGE_NOTICE_G_VECTOR       | 124 | OFF124<17:1> | IFS3<28> | IEC3<28> | IPC31<4:2>       | IPC31<1:0>   | Yes        |

| PORTH Input Change Interrupt <sup>(2,3)</sup>   | _CHANGE_NOTICE_H_VECTOR       | 125 | OFF125<17:1> | IFS3<29> | IEC3<29> | IPC31<12:10>     | IPC31<9:8>   | Yes        |

| PORTJ Input Change Interrupt <sup>(2,3)</sup>   | _CHANGE_NOTICE_J_VECTOR       | 126 | OFF126<17:1> | IFS3<30> | IEC3<30> | IPC31<20:18>     | IPC31<17:16> | Yes        |

| PORTK Input Change Interrupt <sup>(2,3,4)</sup> | _CHANGE_NOTICE_K_VECTOR       | 127 | OFF127<17:1> | IFS3<31> | IEC3<31> | IPC31<28:26>     | IPC31<25:24> | Yes        |

| Parallel Master Port                            | _PMP_VECTOR                   | 128 | OFF128<17:1> | IFS4<0>  | IEC4<0>  | IPC32<4:2>       | IPC32<1:0>   | Yes        |

| Parallel Master Port Error                      | _PMP_ERROR_VECTOR             | 129 | OFF129<17:1> | IFS4<1>  | IEC4<1>  | IPC32<12:10>     | IPC32<9:8>   | Yes        |

| Comparator 1 Interrupt                          | _COMPARATOR_1_VECTOR          | 130 | OFF130<17:1> | IFS4<2>  | IEC4<2>  | IPC32<20:18>     | IPC32<17:16> | No         |

| Comparator 2 Interrupt                          | _COMPARATOR_2_VECTOR          | 131 | OFF131<17:1> | IFS4<3>  | IEC4<3>  | IPC32<28:26>     | IPC32<25:24> | No         |

| USB General Event                               | _USB1_VECTOR                  | 132 | OFF132<17:1> | IFS4<4>  | IEC4<4>  | IPC33<4:2>       | IPC33<1:0>   | Yes        |

| USB DMA Event                                   | _USB1_DMA_VECTOR              | 133 | OFF133<17:1> | IFS4<5>  | IEC4<5>  | IPC33<12:10>     | IPC33<9:8>   | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the list of available peripherals.

**2:** This interrupt source is not available on 64-pin devices.

3: This interrupt source is not available on 100-pin devices.

4: This interrupt source is not available on 124-pin devices.

# TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

| ss                          |                                 |                             |       |             | / ///////////////////////////////////// |       |        | -     |      | Bit    |        | ,      |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-----------------------------|-------|-------------|-----------------------------------------|-------|--------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range                   | 31/15 | 30/14       | 29/13                                   | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 15B0                        | DCH7ECON                        | 31:16                       | —     | —           | —                                       | —     | —      | -     | —    | —      |        |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 1300                        | DOINECON                        | 15:0                        |       |             |                                         | CHSIR | Q<7:0> |       | -    | -      | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | _      |        |        | FF00       |

| 15C0                        | DCH7INT                         | 31:16                       | —     | —           | —                                       | —     | —      | —     | —    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 1000                        |                                 | 15:0                        | —     | —           | —                                       | —     | —      | —     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 15D0                        | DCH7SSA                         | 31:16                       |       | CHSSA<31:0> |                                         |       |        |       |      |        |        |        |        |        |        |        |        |        |            |

|                             |                                 | 15:0                        |       |             |                                         |       |        |       |      |        |        |        |        |        |        |        |        |        | 0000       |

| 15E0                        | DCH7DSA                         | 31:16<br>15:0               |       |             |                                         |       |        |       |      | CHDSA- | <31:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16                       | _     | _           | _                                       | _     | _      | _     | _    | _      | _      | _      | _      | _      | _      | _      | _      |        | 0000       |

| 15F0                        | DCH7SSIZ                        | 15:0                        |       |             |                                         |       |        |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16                       |       |             |                                         |       |        | _     |      |        |        |        |        |        | _      |        | _      |        | 0000       |

| 1600                        | DCH7DSIZ                        | 15:0                        |       |             |                                         |       |        |       |      | CHDSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1010                        | DCH7SPTR                        | 31:16                       | —     | _           | —                                       | _     | —      | —     | —    | —      | —      | —      | —      | —      | _      | —      | —      | _      | 0000       |

| 1010                        | DCHISPIR                        | 15:0                        |       |             |                                         |       |        |       |      | CHSPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1620                        | DCH7DPTR                        | 31:16                       | _     | -           |                                         | _     |        |       | _    | _      |        | _      | _      |        |        |        |        | _      | 0000       |

| 1020                        | DOINDEIR                        | 15:0                        |       |             |                                         |       |        |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1630                        | DCH7CSIZ                        | 31:16                       | —     | _           |                                         | _     |        |       | _    | -      |        | _      | —      |        |        |        |        | _      | 0000       |

| 1030                        | DOINCOIL                        | 17/C3/2 15:0 CHCSIZ<15:0> 0 |       |             |                                         |       |        |       | 0000 |        |        |        |        |        |        |        |        |        |            |

| 1640                        | DCH7CPTR                        | 31:16                       | —     | —           | —                                       | _     | —      | —     | —    | _      | _      | _      | _      | _      | _      | —      | -      | _      | 0000       |

| 1010                        |                                 | 15:0                        |       |             |                                         |       |        |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1650                        | DCH7DAT                         | 31:16                       |       | —           | —                                       | —     | —      | —     | —    | —      | —      | —      | _      | —      | —      | —      | —      |        | 0000       |

|                             |                                 | 15:0                        |       |             |                                         |       |        |       |      | CHPDAT | <15:0> |        |        |        |        |        |        |        | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 |                   |                   |                   | —                 | —                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 |                   |                   |                   | —                 | —                 |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | —                 | —                 | —                 | —                 | —                 | DMABRS            | TM<1:0>          | DMAERR           |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | DMAE              | P<3:0>            |                   | DMAIE             | DMAMODE           | DMADIR           | DMAEN            |

# REGISTER 11-21: USBDMAxC: USB DMA CHANNEL 'x' CONTROL REGISTER ('x' = 1-8)

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-11 Unimplemented: Read as '0'

- bit 10-9 DMABRSTM<1:0>: DMA Burst Mode Selection bit

- 11 = Burst Mode 3: INCR16, INCR8, INCR4 or unspecified length

- 10 = Burst Mode 2: INCR8, INCR4 or unspecified length

- 01 = Burst Mode 1: INCR4 or unspecified length

- 00 = Burst Mode 0: Bursts of unspecified length

### bit 8 DMAERR: Bus Error bit

- 1 = A bus error has been observed on the input

- 0 = The software writes this to clear the error

- bit 7-4 DMAEP<3:0>: DMA Endpoint Assignment bits

- These bits hold the endpoint that the DMA channel is assigned to. Valid values are 0-7.

# bit 3 DMAIE: DMA Interrupt Enable bit

- 1 = Interrupt is enabled for this channel

- 0 = Interrupt is disabled for this channel

# bit 2 DMAMODE: DMA Transfer Mode bit

- 1 = DMA Mode1 Transfers

- 0 = DMA Mode0 Transfers

- bit 1 DMADIR: DMA Transfer Direction bit

- 1 = DMA Read (TX endpoint)

- 0 = DMA Write (RX endpoint)

# bit 0 DMAEN: DMA Enable bit

- 1 = Enable the DMA transfer and start the transfer

- 0 = Disable the DMA transfer

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24     | —                 | —                 | —                 | _                 | —                 | _                 | _                | -                |  |  |

| 00.10     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | —                 | —                 | —                 | _                 | —                 | _                 |                  |                  |  |  |

| 45.0      | R/W-y             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8      | ON <sup>(1)</sup> | —                 | —                 | _                 | —                 | _                 | _                | -                |  |  |

| 7:0       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0       |                   | _                 |                   | _                 | _                 | _                 |                  | _                |  |  |

# REGISTER 15-1: DMTCON: DEADMAN TIMER CONTROL REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Deadman Timer Module Enable bit<sup>(1)</sup>

1 = Deadman Timer module is enabled

0 = Deadman Timer module is disabled

The reset value of this bit is determined by the setting of the FDMTEN bit (DEVCFG1<3>).

bit 13-0 Unimplemented: Read as '0'

**Note 1:** This bit only has control when FDMTEN (DEVCFG1<3>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     |                   | —                 | _                 | _                 | _                 |                   | —                | _                |  |  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     |                   | -                 |                   |                   | _                 |                   |                  |                  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | STEP1<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0       |                   | _                 |                   |                   | _                 | _                 |                  | _                |  |  |

### **REGISTER 15-2: DMTPRECLR: DEADMAN TIMER PRECLEAR REGISTER**

| Legend:                                                              |                  |                      |                    |  |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 31-16 Unimplemented: Read as '0'

| bit 15-8 | STEP1<7:0>: Preclear Enable bits                                                        |

|----------|-----------------------------------------------------------------------------------------|

|          | 01000000 = Enables the Deadman Timer Preclear (Step 1)                                  |

|          | All other write patterns = Set BAD1 flag.                                               |

|          | These bits are cleared when a DMT reset event occurs. STEP1<7:0> is also cleared if the |

|          | STEP2<7:0> bits are loaded with the correct value in the correct sequence.              |

| bit 7-0  | Unimplemented: Read as '0'                                                              |

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                     | —                     | _                 | —                 | —                 | _                 | —                | —                |  |

| 22.46        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                     | —                     | _                 | —                 | —                 | —                 | _                | —                |  |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    |                   |                   |                   | .4.2.0            |                  |                  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   | ADDR<13:8>        |                   |                   |                  |                  |  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                       |                       |                   | ADDR              | <7:0>             |                   |                  |                  |  |

# REGISTER 23-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

# Legend:

bit 15

| 3                 |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- ADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- 3: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

**Note:** If the DUALBUF bit (PMCON<17>) = 0, the bits in this register control both read and write target addressing. If the DUALBUF bit = 1, the bits in this register are not used. In this instance, use the PMRADDR register for Read operations and the PMWADDR register for Write operations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4           | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                         | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                           | —                 | —                 | —                | —                |

| 22.46        | U-0               | U-0               | U-0               | U-0                         | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 |                   |                   |                             | —                 | —                 |                  | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0                         | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | _                 | _                 | _                           | —                 | REGSEL<2:0>       |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-1             | R/W-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | MEMTYPE<2:0>      |                   |                   | MEMSIZE<4:0> <sup>(1)</sup> |                   |                   |                  |                  |

# **REGISTER 24-2:** EBIMSKx: EXTERNAL BUS INTERFACE ADDRESS MASK REGISTER ('x' = 0-3)

# Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-11 Unimplemented: Read as '0'

|          | Ommplemented. Read as 0                                                               |

|----------|---------------------------------------------------------------------------------------|

| bit 10-8 | REGSEL<2:0>: Timing Register Set for Chip Select 'x' bits                             |

|          | 111 = Reserved                                                                        |

|          | •                                                                                     |

|          | •                                                                                     |

|          | 011 = Reserved                                                                        |

|          | 010 = Use EBISMT2                                                                     |

|          | 001 = Use EBISMT1                                                                     |

|          | 000 = Use EBISMT0                                                                     |

| bit 7-5  | <b>MEMTYPE&lt;2:0&gt;:</b> Select Memory Type for Chip Select 'x' bits                |

|          | 111 = Reserved                                                                        |

|          | •                                                                                     |

|          | •                                                                                     |

|          | 011 = Reserved                                                                        |

|          | 010 = NOR-Flash                                                                       |

|          | 001 = SRAM                                                                            |

|          | 000 = Reserved                                                                        |

| bit 4-0  | <b>MEMSIZE&lt;4:0&gt;:</b> Select Memory Size for Chip Select 'x' bits <sup>(1)</sup> |

|          | 11111 = Reserved                                                                      |

|          | •                                                                                     |

|          | •                                                                                     |

|          | 01010 = Reserved                                                                      |

|          | 01001 = 16 MB                                                                         |

|          | 01000 = 8 MB                                                                          |

|          | 00111 = 4 MB                                                                          |

|          | 00110 = 2 MB                                                                          |

|          | 00101 = 1 MB<br>00100 = 512 KB                                                        |

|          | 00100 = 312  KB<br>00011 = 256  KB                                                    |

|          | 00010 = 128 KB                                                                        |

|          | 00001 = 64 KB (smaller memories alias within this range)                              |

|          | 00000 = Chip Select is not used                                                       |

|          |                                                                                       |

|          |                                                                                       |

# **Note 1:** The specified value for these bits depends on the number of available address lines. Refer to the specific device pin table (Table 2 through Table 5) for the available address lines.

NOTES:

| REGISTER 28-6: | ADCIMCON2: ADC INPUT MODE CONTROL REGISTER 2 (CONTINUED) |

|----------------|----------------------------------------------------------|

|----------------|----------------------------------------------------------|

| bit 6 | SIGN19: AN19 Signed Data Mode bit <sup>(1)</sup> |

|-------|--------------------------------------------------|

|       | 1 = AN19 is using Signed Data mode               |

|       | 0 = AN19 is using Unsigned Data mode             |

| bit 5 | DIFF18: AN18 Mode bit                            |

|       | 1 = AN18 is using Differential mode              |

|       | 0 = AN18 is using Single-ended mode              |

| bit 4 | SIGN18: AN18 Signed Data Mode bit                |

|       | 1 = AN18 is using Signed Data mode               |

|       | 0 = AN18 is using Unsigned Data mode             |

| bit 3 | DIFF17: AN17 Mode bit                            |

|       | 1 = AN17 is using Differential mode              |

|       | 0 = AN17 is using Single-ended mode              |

| bit 2 | SIGN17: AN17 Signed Data Mode bit                |

|       | 1 = AN17 is using Signed Data mode               |

|       | 0 = AN17 is using Unsigned Data mode             |

| bit 1 | DIFF16: AN16 Mode bit                            |

|       | 1 = AN16 is using Differential mode              |

|       | 0 = AN16 is using Single-ended mode              |

| bit 0 | SIGN16: AN16 Signed Data Mode bit                |

|       | 1 = AN16 is using Signed Data mode               |

|       | 0 = AN16 is using Unsigned Data mode             |

|       |                                                  |

Note 1: This bit is not available on 64-pin devices.

NOTES:

|           | RE                | GISTER            |                   |                   |                   |                   |                  |                  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10     | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.6      |                   | PMCS<15:8>        |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0       |                   |                   |                   | PMCS              | S<7:0>            |                   |                  |                  |  |

### REGISTER 30-9: ETHPMCS: ETHERNET CONTROLLER PATTERN MATCH CHECKSUM REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-8 PMCS<15:8>: Pattern Match Checksum 1 bits

bit 7-0 PMCS<7:0>: Pattern Match Checksum 0 bits

**Note 1:** This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

# REGISTER 30-10: ETHPMO: ETHERNET CONTROLLER PATTERN MATCH OFFSET REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 51.24        | —                 | —                 | _                 |                   |                   | _                 |                  | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | —                 | _                 | —                 | —                 | —                | —                |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.6         | PMO<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                   |                   |                   | PMO               | <7:0>             |                   |                  |                  |  |

| Le | gend:              |  |

|----|--------------------|--|

|    | Deside to the test |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **PMO<15:0>:** Pattern Match Offset 1 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

# REGISTER 30-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER (CONTINUED)

- bit 6 **TXBUSY:** Transmit Busy bit<sup>(2,6)</sup>

- 1 = TX logic is receiving data

0 = TX logic is idle

This bit indicates that a packet is currently being transmitted. A change in this status bit is not necessarily reflected by the TXDONE interrupt, as TX packets may be aborted or rejected by the MAC.

bit 5 **RXBUSY:** Receive Busy bit<sup>(3,6)</sup>

1 = RX logic is receiving data 0 = RX logic is idle

This bit indicates that a packet is currently being received. A change in this status bit is not necessarily reflected by the RXDONE interrupt, as RX packets may be aborted or rejected by the RX filter.

- bit 4-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for RX operations.

- **2:** This bit is only affected by TX operations.

- **3:** This bit is only affected by RX operations.

- 4: This bit is affected by TX and RX operations.

- 5: This bit will be set when the ON bit (ETHCON1 < 15 >) = 1.

- 6: This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

# 34.3 On-Chip Voltage Regulator

The core and digital logic for all PIC32MZ EF devices is designed to operate at a nominal 1.8V. To simplify system designs, devices in the PIC32MZ EF family incorporate an on-chip regulator providing the required core logic voltage from VDD.

# 34.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

# 34.3.2 ON-CHIP REGULATOR AND BOR

PIC32MZ EF devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 37.1** "**DC Characteristics**".

# 34.4 On-chip Temperature Sensor

PIC32MZ EF devices include a temperature sensor that provides accurate measurement of a device's junction temperature (see Section 37.2 "AC Characteristics and Timing Parameters" for more information).

The temperature sensor is connected to the ADC module and can be measured using the shared S&H circuit (see Section 28.0 "12-bit High-Speed Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC)" for more information).

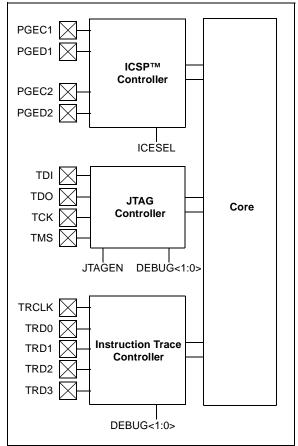

# 34.5 Programming and Diagnostics

PIC32MZ EF devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

# FIGURE 34-1:

# BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE PORTS

| DC CHARACTERISTICS |      | Standard Operating Conditions: 2.1V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended                                                                                                                                                                                                                                                                           |            |   |   |        |                                                                                                              |

|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|---|--------|--------------------------------------------------------------------------------------------------------------|

| Param.             | Sym. | n. Characteristic Min. Typ. Max. Units Cond                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |   |   |        | Conditions <sup>(1)</sup>                                                                                    |

| DO20a Voh1         |      | Output High Voltage<br>I/O Pins:                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5<br>2.0 |   | _ | V<br>V | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$<br>$IOH \ge -12 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |

|                    |      | 4x Source Driver Pins -<br>RA3, RA9, RA10, RA14, RA15<br>RB0-RB2, RB4, RB6-RB7, RB11, RB13<br>RC12-RC15<br>RD0, RD6-RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8<br>RG15<br>RH0, RH1, RH4-RH6, RH8-RH13<br>RJ0-RJ2, RJ8, RJ9, RJ11                                                                                                                                                                                                                                                    |            |   |   | v      | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{ VD}$                                                        |

|                    |      | Output High Voltage           I/O Pins:           8x Source Driver Pins -           RA0-RA2, RA4, RA5           RB3, RB5, RB8-RB10, RB12, RB14, RB15           RC1-RC4           RD1-RD5, RD9, RD10, RD12, RD13, RD15           RE4-RE7           RF0, RF4, RF5, RF12, RF13           RG0, RG1, RG6-RG9           RH2, RH3, RH7, RH14, RH15           RJ3-RJ7, RJ10, RJ12-RJ15           RK0-RK7           Output High Voltage           I/O Pins:           12x Source Driver Pins - | 1.5        | _ | — | V      | Ioh $\geq$ -22 mA, Vdd = 3.3V                                                                                |

|                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.0        | _ | _ | V      | $\text{IOH} \geq \text{-18 mA},  \text{VDD} = 3.3 \text{V}$                                                  |

|                    | Voh1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.0        |   |   | V      | IOH ≥ -10 mA, VDD = 3.3V                                                                                     |

|                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.5        | _ | — | V      | $\text{IOH} \geq \text{-32 mA},  \text{VDD} = 3.3 \text{V}$                                                  |

|                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.0        | _ | — | V      | $\text{IOH} \geq \text{-25 mA},  \text{VDD} = 3.3 \text{V}$                                                  |

|                    | Dor  | RA6, RA7<br>RE0-RE3<br>RF1<br>RG12-RG14                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | _ | _ | V      | IOH $\ge$ -14 mA, VDD = 3.3V                                                                                 |

# TABLE 37-11: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

Note 1: Parameters are characterized, but not tested.

|                                                                                                                                   |        |                                                                                                                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |                     |               |               |               |

|-----------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|---------------|---------------|---------------|

| Param.<br>No.                                                                                                                     | Symbol | Characteris                                                                                                                               | stics <sup>(2)</sup>                                                                                                                                                                                                                                                                | Min. | Тур. <sup>(1)</sup> | Max.          | Units         | Conditions    |

| DO31 TIOR <b>Port Output Rise Tim</b><br>I/O Pins:<br>4x Source Driver Pins<br>RA3, RA9, RA10, RA1<br>RB0-RB2, RB4, RB6-F<br>RB13 |        | -<br>14, RA15                                                                                                                             | _                                                                                                                                                                                                                                                                                   | _    | 9.5                 | ns            | Cload = 50 pF |               |

|                                                                                                                                   |        | RC12-RC15<br>RD0, RD6-RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8<br>RG15<br>RH0, RH1, RH4-RH6, RH8-RH13<br>RJ0-RJ2, RJ8, RJ9, RJ11      |                                                                                                                                                                                                                                                                                     | _    | _                   | 6             | ns            | Cload = 20 pF |

|                                                                                                                                   |        | Port Output Rise Tin<br>I/O Pins:<br>8x Source Driver Pins<br>RA0-RA2, RA4, RA5<br>RB3, RB5, RB8-RB10<br>RB15<br>RC1-RC4                  | -                                                                                                                                                                                                                                                                                   | _    |                     | 8             | ns            | Cload = 50 pF |

|                                                                                                                                   |        | RD1-RD5, RD9, RD10<br>RD15<br>RE4-RE7<br>RF0, RF4, RF5, RF12<br>RG0, RG1, RG6-RG9<br>RH2, RH3, RH7, RH1<br>RJ3-RJ7, RJ10, RJ12<br>RK0-RK7 | 2, RF13<br>4, RH15                                                                                                                                                                                                                                                                  | _    | _                   | 6             | ns            | Cload = 20 pF |

| Port Output Rise Time<br>I/O Pins:<br>12x Source Driver Pins -<br>RA6, RA7<br>RE0-RE3<br>RF1<br>RG12-RG14                         |        | I/O Pins:<br>12x Source Driver Pins                                                                                                       |                                                                                                                                                                                                                                                                                     | _    | _                   | 3.5           | ns            | CLOAD = 50 pF |

|                                                                                                                                   |        | _                                                                                                                                         | _                                                                                                                                                                                                                                                                                   | 2    | ns                  | CLOAD = 20 pF |               |               |

# TABLE 37-23: I/O TIMING REQUIREMENTS

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

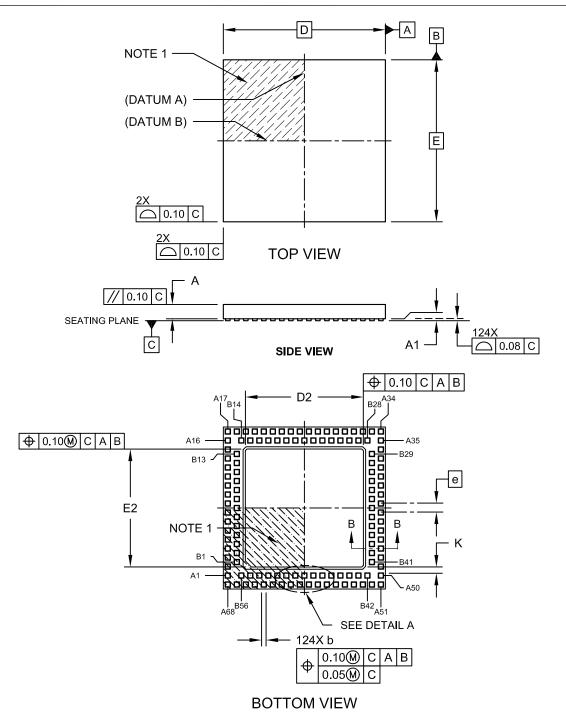

# 124-Terminal Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-193A Sheet 1 of 2

# APPENDIX A: MIGRATING FROM PIC32MX5XX/6XX/7XX TO PIC32MZ EF

This appendix provides an overview of considerations for migrating from PIC32MX5XX/6XX/7XX devices to the PIC32MZ EF family of devices. The code developed for PIC32MX5XX/6XX/7XX devices can be ported to PIC32MZ EF devices after making the appropriate changes outlined in the following sections.

The PIC32MZ EF devices are based on a new architecture, and feature many improvements and new capabilities over PIC32MX5XX/6XX/7XX devices.

# A.1 Oscillator and PLL Configuration

Because the maximum speed of the PIC32MZ EF family is greater, the configuration of the oscillator is different from prior PIC32MX5XX/6XX/7XX devices.

Table A-1 summarizes the differences (indicated by **Bold** type) between the family devices for the oscillator.

# TABLE A-1: OSCILLATOR CONFIGURATION DIFFERENCES

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                                                                 | PIC32MZ EF Feature                                                                                                                                            |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Primary Oscillator Configuration                                                                                                                                                                                           |                                                                                                                                                               |  |  |  |  |

| On PIC32MX devices, XT mode had to be selected if the input fre-<br>quency was in the 3 MHz to 10 MHz range (4-10 for PLL), and HS<br>mode had to be selected if the input frequency was in the 10 MHz<br>to 20 MHz range. | On PIC32MZ EF devices, HS mode has a wider input frequency range (4 MHz to 12 MHz). The bit setting of '01' is Reserved.                                      |  |  |  |  |

| POSCMOD<1:0> (DEVCFG1<9:8>)<br>11 = Primary Oscillator disabled                                                                                                                                                            | POSCMOD<1:0> (DEVCFG1<9:8>)<br>11 = Primary Oscillator disabled                                                                                               |  |  |  |  |

| 10 = HS Oscillator mode selected<br>01 = XT Oscillator mode selected                                                                                                                                                       | 10 = HS Oscillator mode selected<br>01 = Reserved                                                                                                             |  |  |  |  |

| 00 = External Clock mode selected                                                                                                                                                                                          | 00 = External Clock mode selected                                                                                                                             |  |  |  |  |

| On PIC32MX devices, crystal mode could be selected with the HS or XT POSC setting, but an external oscillator could be fed into the OSC1/CLKI pin and the part would operate normally.                                     | On PIC32MZ devices, this option is not available. External oscil-<br>lator signals should only be fed into the OSC1/CLKI pin with the<br>POSC set to EC mode. |  |  |  |  |

| Oscillator                                                                                                                                                                                                                 | Selection                                                                                                                                                     |  |  |  |  |

| On PIC32MX devices, clock selection choices are as follows:                                                                                                                                                                | On PIC32MZ EF devices, clock selection choices are as follows:                                                                                                |  |  |  |  |

| FNOSC<2:0> (DEVCFG1<2:0>)<br>NOSC<2:0> (OSCCON<10:8>)                                                                                                                                                                      | FNOSC<2:0> (DEVCFG1<2:0>)<br>NOSC<2:0> (OSCCON<10:8>)                                                                                                         |  |  |  |  |

| 111 = FRCDIV                                                                                                                                                                                                               | 111 = FRCDIV                                                                                                                                                  |  |  |  |  |

| 110 = FRCDIV16                                                                                                                                                                                                             | 110 = Reserved                                                                                                                                                |  |  |  |  |

| 101 = LPRC                                                                                                                                                                                                                 | 101 = LPRC                                                                                                                                                    |  |  |  |  |

| 100 = SOSC<br>011 = POSC with PLL module                                                                                                                                                                                   | 100 = SOSC<br>011 = Reserved                                                                                                                                  |  |  |  |  |

| 010 = POSC (XT, HS, EC)                                                                                                                                                                                                    | 011 = POSC (HS or EC)                                                                                                                                         |  |  |  |  |

| 0.01 = FRCDIV+PLL                                                                                                                                                                                                          | 001 = System PLL (SPLL)                                                                                                                                       |  |  |  |  |

| 000 = FRC                                                                                                                                                                                                                  | 000 = FRCDIV                                                                                                                                                  |  |  |  |  |

| COSC<2:0> (OSCCON<14:12>)<br>111 = FRC divided by FRCDIV                                                                                                                                                                   | COSC<2:0> (OSCCON<14:12>)<br>111 = FRC divided by FRCDIV                                                                                                      |  |  |  |  |

| 110 = FRC divided by FRCDIV                                                                                                                                                                                                | $110 = \mathbf{BFRC}$                                                                                                                                         |  |  |  |  |

| 101 = LPRC                                                                                                                                                                                                                 | 101 = LPRC                                                                                                                                                    |  |  |  |  |

| 100 = SOSC                                                                                                                                                                                                                 | 100 = SOSC                                                                                                                                                    |  |  |  |  |

| 011 = POSC + PLL module                                                                                                                                                                                                    | 011 = Reserved                                                                                                                                                |  |  |  |  |

| 010 = POSC                                                                                                                                                                                                                 | 010 = POSC                                                                                                                                                    |  |  |  |  |

| 001 = FRCPLL                                                                                                                                                                                                               | 001 = System PLL                                                                                                                                              |  |  |  |  |

| 000 = FRC                                                                                                                                                                                                                  | 000 = FRC divided by FRCDIV                                                                                                                                   |  |  |  |  |

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                                                                                                                | PIC32MZ EF Feature                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Scan Trigg                                                                                                                                                                                                                                                                | ger Source                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| On PIC32MX devices, there are four sources that can trigger a scan conversion in the ADC module: Auto, Timer3, INT0, and clearing the SAMP bit.<br>SSRC<2:0> (AD1CON1<7:5>)<br>111 = Auto convert<br>110 = Reserved<br>101 = Reserved<br>100 = Reserved<br>011 = Reserved | On PIC32MZ EF devices, the list of sources for triggering a scan<br>conversion has been expanded to include the comparators,<br>Output Compare, and two additional Timers. In addition, trigger<br>sources can be simulated by setting the RQCNVRT<br>(ADCCON3<8>) bit.<br>STRGSRC<4:0> (ADCCON1<20:16>)<br>11111 = Reserved<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |  |  |  |  |