Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256K × 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

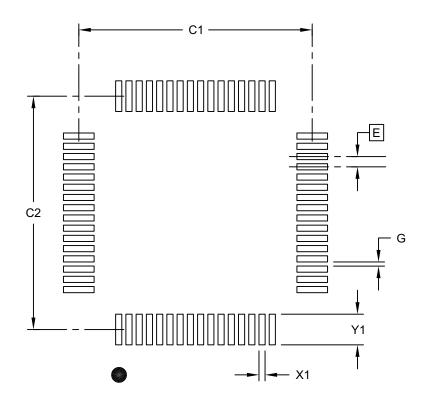

| Package / Case             | 144-TQFP                                                                         |

| Supplier Device Package    | 144-TQFP (16x16)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024eff144-i-ph |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1: **PIC32MZ EF FAMILY FEATURES**

|                   |                        |                     |      |          |                           |                 | Remap                                         | pable | Periph               | erals                                 |          |        |     |                                              |                | IS                 |                |                  |     |     |     |      |          |          |      |       |

|-------------------|------------------------|---------------------|------|----------|---------------------------|-----------------|-----------------------------------------------|-------|----------------------|---------------------------------------|----------|--------|-----|----------------------------------------------|----------------|--------------------|----------------|------------------|-----|-----|-----|------|----------|----------|------|-------|

| Device            | Program<br>Memory (KB) | Data<br>Memory (KB) | Pins | Packages | Boot Flash<br>Memory (KB) | Remappable Pins | Timers/<br>Capture/<br>Compare <sup>(1)</sup> | UART  | SPI/I <sup>2</sup> S | External<br>Interrupts <sup>(2)</sup> | CAN 2.0B | Crypto | RNG | DMA Channels<br>(Programmable/<br>Dedicated) | ADC (Channels) | Analog Comparators | USB 2.0 HS OTG | 1 <sup>2</sup> C | AMP | EBI | sai | RTCC | Ethernet | I/O Pins | JTAG | Trace |

| PIC32MZ0512EFE064 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 0        | N      | Y   | 8/12                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFF064 | 512                    | 128                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      | 1     |

| PIC32MZ0512EFK064 |                        |                     | 64   | TQFP,    | 160                       | 34              | 9/9/9                                         | 6     | 4                    | 5                                     | 2        | Y      | Υ   | 8/18                                         | 24             | 2                  | Y              | 4                | Y   | N   | Y   | Y    | Υ        | 46       | Y    | Y     |

| PIC32MZ1024EFE064 |                        |                     | 04   | QFN      | 100                       | 34              | 9/9/9                                         | 0     | 4                    | 5                                     | 0        | Ν      | Υ   | 8/12                                         | 24             | 2                  | T              | 4                | T   |     | ľ   |      |          | 40       | T    |       |

| PIC32MZ1024EFF064 | 1024                   | 256                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Υ   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      | 1     |

| PIC32MZ1024EFK064 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 2        | Y      | Y   | 8/18                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFE100 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 0        | Ν      | Y   | 8/12                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFF100 | 512                    | 128                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      | 1     |

| PIC32MZ0512EFK100 |                        |                     | 100  | TQFP     | 160                       | 51              | 9/9/9                                         | 6     | 6                    | 5                                     | 2        | Y      | Y   | 8/18                                         | 40             | 2                  | Y              | 5                | Y   | Υ   | Y   | Υ    | Υ        | 78       | Y    | Y     |

| PIC32MZ1024EFE100 |                        |                     |      | I GI I   | 100                       | 51              | 3/3/3                                         | 0     |                      | 5                                     | 0        | Ν      | Y   | 8/12                                         | 40             | 2                  |                |                  |     | '   | '   |      | '        | 10       |      |       |

| PIC32MZ1024EFF100 | 1024                   | 256                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFK100 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 2        | Y      | Y   | 8/18                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFE124 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 0        | Ν      | Y   | 8/12                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFF124 | 512                    | 128                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFK124 |                        |                     | 124  | VTLA     | 160                       | 53              | 9/9/9                                         | 6     | 6                    | 5                                     | 2        | Y      | Y   | 8/18                                         | 48             | 2                  | Y              | 5                | Y   | Υ   | Υ   | Υ    | Y        | 97       | Y    | Y     |

| PIC32MZ1024EFE124 |                        |                     | 124  |          |                           |                 | 5/5/5                                         | Ū     |                      | Ŭ                                     | 0        | Ν      | Y   | 8/12                                         | -10            | 2                  |                |                  |     | '   | '   | '    | '        |          |      | '     |

| PIC32MZ1024EFF124 | 1024                   | 256                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFK124 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 2        | Y      | Y   | 8/18                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFE144 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 0        | Ν      | Y   | 8/12                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFF144 | 512                    | 128                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFK144 |                        |                     | 144  | LQFP,    | 160                       | 53              | 9/9/9                                         | 6     | 6                    | 5                                     | 2        | Y      | Y   | 8/18                                         | 48             | 2                  | Y              | 5                | Y   | Υ   | Y   | Υ    | Υ        | 120      | Y    | Y     |

| PIC32MZ1024EFE144 |                        |                     |      | TQFP     |                           |                 | 31313                                         | 0     |                      |                                       | 0        | Ν      | Y   | 8/12                                         | 40             | -                  |                |                  |     | '   | '   | '    | '        | 120      |      | '     |

| PIC32MZ1024EFF144 | 1024                   | 256                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFK144 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 2        | Y      | Y   | 8/18                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

Note 1:

Eight out of nine timers are remappable. Four out of five external interrupts are remappable. This device is available with a 252 MHz speed rating. 2: 3:

|          |                        | Pin Nu          | mber            |                          |             |                |                                     |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                         |

| EBIA0    | _                      | 44              | B24             | 30                       | 0           | —              | External Bus Interface Address Bus  |

| EBIA1    | _                      | 43              | A28             | 51                       | 0           | _              | 7                                   |

| EBIA2    |                        | 16              | B9              | 21                       | 0           |                | 1                                   |

| EBIA3    |                        | 12              | B7              | 52                       | 0           |                | 1                                   |

| EBIA4    |                        | 11              | A8              | 68                       | 0           |                | 1                                   |

| EBIA5    |                        | 2               | B1              | 2                        | 0           |                | 1                                   |

| EBIA6    |                        | 6               | B3              | 6                        | 0           |                | 1                                   |

| EBIA7    |                        | 33              | A23             | 48                       | 0           |                | 1                                   |

| EBIA8    |                        | 65              | A44             | 91                       | 0           |                | 1                                   |

| EBIA9    |                        | 64              | B36             | 90                       | 0           |                | 1                                   |

| EBIA10   | _                      | 32              | B18             | 47                       | 0           | _              | 1                                   |

| EBIA11   | _                      | 41              | A27             | 29                       | 0           | —              | 1                                   |

| EBIA12   | _                      | 7               | A6              | 11                       | 0           | _              | 1                                   |

| EBIA13   | _                      | 34              | B19             | 28                       | 0           | —              | 1                                   |

| EBIA14   | _                      | 61              | A42             | 87                       | 0           | —              | 1                                   |

| EBIA15   | _                      | 68              | B38             | 97                       | 0           | —              | 1                                   |

| EBIA16   | _                      | 17              | A11             | 19                       | 0           | —              | 1                                   |

| EBIA17   | _                      | 40              | B22             | 53                       | 0           |                | 1                                   |

| EBIA18   | -                      | 39              | A26             | 92                       | 0           | _              |                                     |

| EBIA19   | -                      | 38              | B21             | 93                       | 0           | _              |                                     |

| EBIA20   | -                      | _               | _               | 94                       | 0           | _              |                                     |

| EBIA21   | _                      | _               | _               | 126                      | 0           | _              | 1                                   |

| EBIA22   | _                      | _               | _               | 117                      | 0           | _              | -                                   |

| EBIA23   | _                      | _               | _               | 103                      | 0           | _              | 1                                   |

| EBID0    | _                      | 91              | B52             | 135                      | I/O         | ST             | External Bus Interface Data I/O Bus |

| EBID1    | _                      | 94              | A64             | 138                      | I/O         | ST             |                                     |

| EBID2    | _                      | 98              | A66             | 142                      | I/O         | ST             | -                                   |

| EBID3    | _                      | 99              | B56             | 143                      | I/O         | ST             | -                                   |

| EBID4    | _                      | 100             | A67             | 144                      | I/O         | ST             | 1                                   |

| EBID5    | _                      | 3               | A3              | 3                        | I/O         | ST             | -                                   |

| EBID6    | _                      | 4               | B2              | 4                        | I/O         | ST             | 1                                   |

| EBID7    | _                      | 5               | A4              | 5                        | I/O         | ST             | 1                                   |

| EBID8    | _                      | 88              | B50             | 128                      | I/O         | ST             | 1                                   |

| EBID9    | _                      | 87              | A60             | 127                      | I/O         | ST             | 1                                   |

| EBID10   | _                      | 86              | B49             | 125                      | I/O         | ST             | 1                                   |

| EBID11   | _                      | 85              | A59             | 124                      | I/O         | ST             | 1                                   |

| EBID12   | _                      | 79              | B43             | 112                      | I/O         | ST             | 1                                   |

| EBID13   | _                      | 80              | A54             | 113                      | I/O         | ST             | 4                                   |

| EBID14   |                        | 77              | B42             | 110                      | I/O         | ST             | 4                                   |

| EBID15   |                        | 78              | A53             | 110                      | I/O         | ST             | 4                                   |

| EBIBS0   |                        |                 |                 | 9                        | 0           |                | External Bus Interface Byte Select  |

| EBIBS1   |                        | <u> </u>        | <u> </u>        | 10                       | 0           |                |                                     |

| EBICS0   |                        | 59              | A41             | 131                      | 0           |                | External Bus Interface Chip Select  |

| EBICS1   |                        |                 |                 | 131                      | 0           |                |                                     |

| EBICS2   |                        |                 |                 | 132                      | 0           |                | 4                                   |

| EBICS2   |                        |                 |                 | 133                      | 0           |                | 4                                   |

#### TABLE 1-13: **EBI PINOUT I/O DESCRIPTIONS**

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

PPS = Peripheral Pin Select

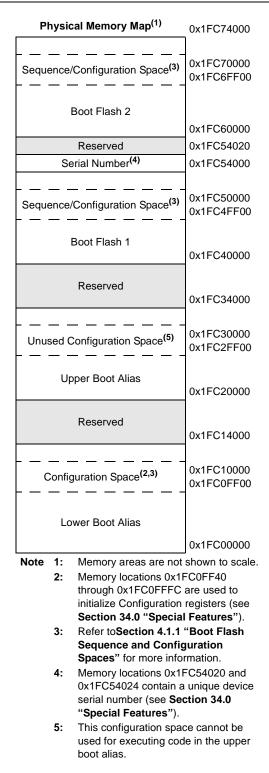

# FIGURE 4-5: BOOT AND ALIAS MEMORY MAP

### TABLE 4-1: SFR MEMORY MAP

|                           | Virtual Ad | dress           |

|---------------------------|------------|-----------------|

| Peripheral                | Base       | Offset<br>Start |

| System Bus <sup>(1)</sup> | 0xBF8F0000 | 0x0000          |

| Prefetch                  |            | 0x0000          |

| EBI                       |            | 0x1000          |

| SQI1                      |            | 0x2000          |

| USB                       | 0xBF8E0000 | 0x3000          |

| Crypto                    |            | 0x5000          |

| RNG                       |            | 0x6000          |

| CAN1 and CAN2             |            | 0x0000          |

| Ethernet                  | 0xBF880000 | 0x2000          |

| USBCR                     |            | 0x4000          |

| PORTA-PORTK               | 0xBF860000 | 0x0000          |

| Timer1-Timer9             |            | 0x0000          |

| IC1-IC9                   |            | 0x2000          |

| OC1-OC9                   | 0xBF840000 | 0x4000          |

| ADC                       |            | 0xB000          |

| Comparator 1, 2           |            | 0xC000          |

| I2C1-I2C5                 |            | 0x0000          |

| SPI1-SPI6                 | 0,000000   | 0x1000          |

| UART1-UART6               | 0xBF820000 | 0x2000          |

| PMP                       |            | 0xE000          |

| Interrupt Controller      | 0xBF810000 | 0x0000          |

| DMA                       | 00000      | 0x1000          |

| Configuration             |            | 0x0000          |

| Flash Controller          |            | 0x0600          |

| Watchdog Timer            |            | 0x0800          |

| Deadman Timer             | 0vPE800000 | 0x0A00          |

| RTCC                      | 0xBF800000 | 0x0C00          |

| CVREF                     |            | 0x0E00          |

| Oscillator                |            | 0x1200          |

| PPS                       |            | 0x1400          |

Note 1: Refer to 4.2 "System Bus Arbitration" for important legal information.

|              |                   | ('x' = 0-13)      |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | R/W-0, C          | U-0               | U-0               | U-0               | R/W-0, C          | R/W-0, C          | R/W-0, C         | R/W-0, C         |

| 31:24        | MULTI             | —                 | —                 | —                 |                   | CODE              | <3:0>            |                  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   | —                 | —                 |                   | —                 |                  | _                |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | INITIE            | 0<7:0>            |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          |                   | REGIO             | N<3:0>            |                   |                   |                   | CMD<2:0>         |                  |

### REGISTER 4-3: SBTxELOG1: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 1

| Legend:           | C = Clearable bit |                                    |

|-------------------|-------------------|------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               |

bit 31 MULTI: Multiple Permission Violations Status bit

This bit is cleared by writing a '1'.

1 = Multiple errors have been detected

0 = No multiple errors have been detected

bit 30-28 Unimplemented: Read as '0'

bit 27-24 CODE<3:0>: Error Code bits

Indicates the type of error that was detected. These bits are cleared by writing a '1'.

- 1111 = Reserved

- 1101 = Reserved

- •

- •

- 0011 = Permission violation

- 0010 = Reserved

- 0001 = Reserved

- 0000 = No error

- bit 23-16 Unimplemented: Read as '0'

- bit 15-8 INITID<7:0>: Initiator ID of Requester bits

- 11111111 = Reserved

- 00001111 = Reserved 00001110 = Crypto Engine 00001101 = Flash Controller 00001100 = SQI1 00001011 = CAN2 00001010 = CAN1 00001001 = Ethernet Write 00001000 = Ethernet Read 00000111 = USB 00000110 = DMA Write (DMAPRI (CFGCON<25>) = 1) 00000101 = DMA Write (DMAPRI (CFGCON<25>) = 0) 00000100 = DMA Read (DMAPRI (CFGCON<25>) = 1) 00000011 = DMA Read (DMAPRI (CFGCON<25>) = 0) 00000010 = CPU (CPUPRI (CFGCON<24>) = 1) 00000001 = CPU (CPUPRI (CFGCON<25>) = 0) 00000000 = Reserved

#### Note: Refer to Table 4-6 for the list of available targets and their descriptions.

### TABLE 12-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SSS                         |                      |               |       |       |       |       |       |       |      | E    | Bits |      |      |      |      |       |             |      |            |

|-----------------------------|----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|-------------|------|------------|

| Virtual Address<br>(BF80_#) |                      |               | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1        | 16/0 | All Resets |

| 4.400                       |                      | 31:16         | -     | —     | _     | —     | —     | —     | —    | _    | -    | —    | —    | —    | —    | —     | —           | —    | 000        |

| 1488                        | U5RXR                | 15:0          | _     | —     | —     | —     | —     | —     | —    | —    |      | —    | —    | —    |      | U5RXI | R<3:0>      | •    | 000        |

| 148C                        | U5CTSR               | 31:16         |       | —     | —     | —     | —     | —     | _    | —    | 1    | —    | —    | —    | —    | —     | —           | —    | 000        |

| 1400                        | USCISK               | 15:0          |       | _     | —     | _     | _     | —     | —    | —    |      | _    | _    | _    |      | U5CTS | R<3:0>      |      | 000        |

| 1490                        | U6RXR                | 31:16         |       | _     | —     | _     | _     | —     | —    | —    |      | _    | _    | _    | _    | _     | _           | _    | 000        |

| 1490                        | UUKAK                | 15:0          | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | U6RXI | R<3:0>      |      | 000        |

| 1494                        | U6CTSR               | 31:16         | _     | —     | —     | —     | —     | —     | _    | —    | _    | —    | —    | _    | _    | —     | —           | —    | 000        |

| 1404                        | 000101               | 15:0          | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | U6CTS | R<3:0>      |      | 000        |

| 149C                        | SDI1R                | 31:16         | _     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | —    | —     | —           | —    | 000        |

|                             | 00                   | 15:0          | _     |       | —     |       |       | —     | _    | —    | _    |      | —    | —    |      | SDI1F | R<3:0>      |      | 000        |

| 14A0                        | SS1R                 | 31:16         | _     | _     | —     | _     | _     | _     | _    | —    | _    | _    | —    | _    |      | —     | —           |      | 000        |

|                             |                      | 15:0          | _     |       | —     |       |       |       |      | —    | _    |      | —    | —    |      | SS1R  | <3:0>       |      | 000        |

| 14A8                        | SDI2R                | 31:16         | _     | —     | —     | —     | —     | _     | —    | —    | _    | —    |      | —    | —    | —     | —           | —    | 000        |

|                             |                      | 15:0          | _     | —     | —     |       |       |       |      | —    | _    |      | —    | —    |      | SDI2F | R<3:0>      |      | 000        |

| 14AC                        | SS2R                 | 31:16         | _     | —     | —     | —     | —     | _     | —    | —    | _    | —    |      | —    | —    | —     | —           | —    | 000        |

|                             |                      | 15:0          | _     | —     | —     | —     | _     |       | —    | —    | _    | —    | —    | —    |      | SS2R  |             |      | 000        |

| 14B4                        | SDI3R                | 31:16         | _     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | —    | _     | —           | —    | 000        |

|                             |                      | 15:0          | _     |       | _     |       |       | —     | _    | _    | _    | _    | _    | _    |      | SDI3F | R<3:0>      |      | 000        |

| 14B8                        | SS3R                 | 31:16         | —     | _     | _     | _     | _     | _     | _    | _    | _    | —    | _    | _    | —    |       | —           | _    | 000        |

|                             |                      | 15:0          | _     |       |       |       |       |       | _    | _    |      |      |      |      |      | SS3R  |             |      | 000        |

| 14C0                        | SDI4R                | 31:16         |       | _     | _     | _     | _     | _     | _    | _    |      | _    |      |      |      |       | —           |      | 000        |

|                             |                      | 15:0          |       | _     | _     | _     | _     | _     | _    | _    |      | _    |      |      |      | SDI4F | R<3:0>      |      | 000        |

| 14C4                        | SS4R                 | 31:16         |       | _     | _     | _     | _     |       |      | —    |      |      |      |      |      |       | —           | —    | 000        |

|                             |                      | 15:0          |       | _     | _     | _     | _     |       |      | —    |      |      |      |      |      | SS4R  |             |      | 000        |

| 14CC                        | SDI5R <sup>(1)</sup> | 31:16         |       | _     | —     |       | _     |       | —    | —    |      |      | —    | —    | —    | -     | —           | —    | 000        |

|                             |                      | 15:0          |       | _     | _     | _     |       |       | —    | —    |      |      | —    | —    |      |       | R<3:0>      |      | 0000       |

| 14D0                        | SS5R <sup>(1)</sup>  | 31:16         |       | _     | _     |       |       |       | —    | —    |      |      | _    | —    | —    |       | -           | —    | 0000       |

|                             |                      | 15:0          |       |       | _     |       |       |       | —    | —    |      |      | _    |      |      | SS5R  | <3:0>       |      | 0000       |

| 14D8                        | SDI6R <sup>(1)</sup> | 31:16<br>15:0 |       | —     | _     | —     | _     | —     | _    | _    |      | —    | _    |      | —    |       | —<br>R<3:0> |      | 0000       |

| Logon                       |                      |               |       |       |       |       |       | —     |      | _    | —    | —    | _    | —    |      | 20101 | <3.0>       |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

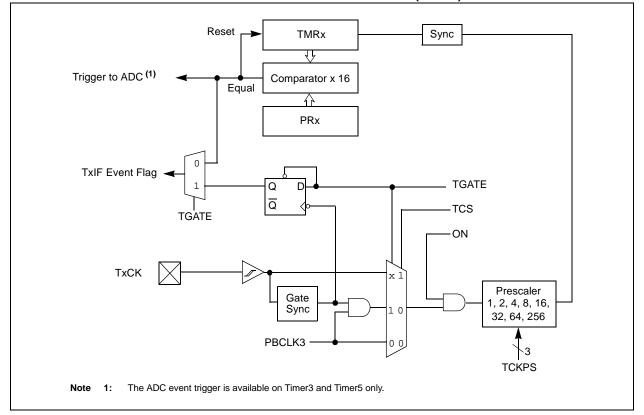

### 14.0 TIMER2/3, TIMER4/5, TIMER6/7, AND TIMER8/9

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14.** "**Timers**" (DS60001105) of the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32MZ EF family of devices features eight synchronous 16-bit timers (default) that can operate as a free-running interval timer for various timing applications and counting external events.

The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- Synchronous external 16-bit timer

Four 32-bit synchronous timers are available by combining Timer2 with Timer3, Timer4 with Timer5, Timer6 with Timer7, and Timer8 with Timer9.

The 32-bit timers can operate in one of three modes:

- · Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

### 14.1 Additional Supported Features

- Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 through Timer7 only)

- ADC event trigger (Timer3 and Timer5 only)

- Fast bit manipulation using CLR, SET, and INV registers

#### FIGURE 14-1: TIMER2 THROUGH TIMER9 BLOCK DIAGRAM (16-BIT)

|           | -                 |                   |                   |                   |                   |                   |                  |                  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | —                 | _                 | —                 | _                 | _                | -                |

| 00.10     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | —                 | _                 | —                 | _                 |                  |                  |

| 45.0      | R/W-y             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | ON <sup>(1)</sup> | —                 | —                 | _                 | —                 | _                 | _                | -                |

| 7:0       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0       |                   | _                 |                   | _                 | _                 | _                 |                  | _                |

### REGISTER 15-1: DMTCON: DEADMAN TIMER CONTROL REGISTER

| Legend:           |                  | y = Value set from Conf | iguration bits on POR |

|-------------------|------------------|-------------------------|-----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit,  | read as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared    | x = Bit is unknown    |

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Deadman Timer Module Enable bit<sup>(1)</sup>

1 = Deadman Timer module is enabled

0 = Deadman Timer module is disabled

The reset value of this bit is determined by the setting of the FDMTEN bit (DEVCFG1<3>).

bit 13-0 Unimplemented: Read as '0'

**Note 1:** This bit only has control when FDMTEN (DEVCFG1<3>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     |                   | —                 | _                 | _                 | _                 |                   | —                | _                |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     |                   | -                 |                   |                   | _                 |                   |                  |                  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      |                   |                   |                   | STEP1             | <7:0>             |                   |                  |                  |

| 7:0       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0       |                   | _                 |                   |                   | _                 | _                 |                  | _                |

#### **REGISTER 15-2: DMTPRECLR: DEADMAN TIMER PRECLEAR REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| bit 15-8 | STEP1<7:0>: Preclear Enable bits                                                        |

|----------|-----------------------------------------------------------------------------------------|

|          | 01000000 = Enables the Deadman Timer Preclear (Step 1)                                  |

|          | All other write patterns = Set BAD1 flag.                                               |

|          | These bits are cleared when a DMT reset event occurs. STEP1<7:0> is also cleared if the |

|          | STEP2<7:0> bits are loaded with the correct value in the correct sequence.              |

| bit 7-0  | Unimplemented: Read as '0'                                                              |

#### 17.1 Input Capture Control Registers

# TABLE 17-2: INPUT CAPTURE 1 THROUGH INPUT CAPTURE 9 REGISTER MAP

| ÷ ŧ                         |                       |               |       |       |       |       |       |       |       | Bit    | S      |      |       |      |       |      |          |      |              |

|-----------------------------|-----------------------|---------------|-------|-------|-------|-------|-------|-------|-------|--------|--------|------|-------|------|-------|------|----------|------|--------------|

| Virtual Address<br>(BF84_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8   | 23/7   | 22/6 | 21/5  | 20/4 | 19/3  | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | IC1CON <sup>(1)</sup> | 31:16         |       | —     |       | —     | —     |       | —     |        |        | _    |       |      | —     |      | —        | _    | 0000         |

| 2000                        |                       | 15:0          | ON    | _     | SIDL  | _     |       |       | FEDGE | C32    | ICTMR  | ICI< | :1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000         |

| 2010                        | IC1BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC1BUF | <31:0> |      |       |      |       |      |          |      | XXXX         |

| 0000                        | 10000N(1)             | 31:16         | _     | —     | —     | —     | —     | —     | —     | —      | _      | —    | —     | —    | —     | —    | _        | —    | 0000         |

| 2200                        | IC2CON <sup>(1)</sup> | 15:0          | ON    | —     | SIDL  | -     | —     | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0>  | ICOV | ICBNE |      | ICM<2:0> |      | 0000         |

| 2210                        | IC2BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC2BUF | <31:0> |      |       |      |       |      |          |      | XXXX         |

| 2400                        | IC3CON <sup>(1)</sup> | 31:16         | _     |       | _     |       | —     | —     | —     | _      | _      | _    | _     | _    | —     | _    | —        | _    | 0000         |

| 2400                        | IC3CON*               | 15:0          | ON    | —     | SIDL  | —     |       |       | FEDGE | C32    | ICTMR  | ICI< | 1:0>  | ICOV | ICBNE |      | ICM<2:0> |      | 0000         |

| 2410                        | IC3BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC3BUF | <31:0> |      |       |      |       |      |          |      | XXXX<br>XXXX |

| 2600                        | IC4CON <sup>(1)</sup> | 31:16         | _     | _     | _     | _     | _     | _     | _     | _      | _      | _    | _     | _    | _     | _    | _        | _    | 0000         |

| 2000                        | 1040011               | 15:0          | ON    | _     | SIDL  | _     | _     | -     | FEDGE | C32    | ICTMR  | ICI< | :1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000         |

| 2610                        | IC4BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC4BUF | <31:0> |      |       |      |       |      |          |      | XXXX         |

| 2800                        | IC5CON <sup>(1)</sup> | 31:16         | _     |       |       |       | _     | _     |       |        |        | _    |       | _    | _     |      | _        |      | 0000         |

| 2000                        | ICSCON.               | 15:0          | ON    |       | SIDL  |       | _     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0>  | ICOV | ICBNE |      | ICM<2:0> |      | 0000         |

| 2810                        | IC5BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC5BUF | <31:0> |      |       |      |       |      |          |      | XXXX<br>XXXX |

| 2A00                        | IC6CON <sup>(1)</sup> | 31:16         | _     | —     | —     | —     | —     | —     | —     | _      | _      | —    | —     | —    | - 1   | —    | —        | _    | 0000         |

| 2400                        |                       | 15:0          | ON    | —     | SIDL  | -     |       |       | FEDGE | C32    | ICTMR  | ICI< | :1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000         |

| 2A10                        | IC6BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC6BUF | <31:0> |      |       |      |       |      |          |      | XXXX         |

| 2C00                        | IC7CON <sup>(1)</sup> | 31:16         | _     | —     | —     | —     | —     | —     | —     | —      | —      | —    | —     | —    | —     | —    | —        | —    | 0000         |

| 2000                        |                       | 15:0          | ON    | —     | SIDL  | -     |       |       | FEDGE | C32    | ICTMR  | ICI< | :1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000         |

| 2C10                        | IC7BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC7BUF | <31:0> |      |       |      |       |      |          |      | XXXX         |

| 2500                        | IC8CON <sup>(1)</sup> | 31:16         | _     |       | _     |       | _     | —     | —     | _      | _      | _    | _     |      | —     | _    | —        | _    | 0000         |

| 2E00                        |                       | 15:0          | ON    | _     | SIDL  | _     | -     |       | FEDGE | C32    | ICTMR  | ICI< | 1:0>  | ICOV | ICBNE |      | ICM<2:0> |      | 0000         |

| 2E10                        | IC8BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC8BUF | <31:0> |      |       |      |       |      |          |      | XXXX<br>XXXX |

| 2000                        | IC9CON <sup>(1)</sup> | 31:16         | —     | —     | _     | —     |       |       | _     | _      | —      | _    | —     | —    |       |      | _        | _    | 0000         |

| 3000                        |                       | 15:0          | ON    | _     | SIDL  | —     | _     | —     | FEDGE | C32    | ICTMR  | ICI< | 1:0>  | ICOV | ICBNE |      | ICM<2:0> |      | 0000         |

| 3010                        | IC9BUF                | 31:16<br>15:0 |       |       |       |       |       |       |       | IC9BUF | <31:0> |      |       |      |       |      |          |      | xxxx<br>xxxx |

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more Note 1: information.

|              |                       |                   |                   | <b>BOILINGE</b>   |                   |                   |                  |                  |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 04.04        | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                     | _                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 00.40        | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | DUN                   | /MYBYTES<         | <2:0>             | AI                | DDRBYTES<2:       | READOPCODE<7:6>   |                  |                  |  |

| 45-0         | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | READOPCODE<5:0>       |                   |                   |                   |                   |                   |                  | TYPEDATA<1:0>    |  |

| 7 0          | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | TYPEDUMMY<1:0> TYPEMO |                   |                   | DE<1:0>           | TYPEAD            | TYPEADDR<1:0>     |                  | TYPECMD<1:0>     |  |

### REGISTER 20-1: SQI1XCON1: SQI XIP CONTROL REGISTER 1

### Legend:

| Logona.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 31-24 Unimplemented: Read as '0'

### bit 23-21 DUMMYBYTES<2:0>: Transmit Dummy Bytes bits

- 111 = Transmit seven dummy bytes after the address bytes

- •

- 011 = Transmit three dummy bytes after the address bytes

- 010 = Transmit two dummy bytes after the address bytes

- 001 = Transmit one dummy bytes after the address bytes

- 000 = Transmit zero dummy bytes after the address bytes

### bit 20-18 ADDRBYTES<2:0>: Address Cycle bits

- 111 = Reserved

- •

- •

- 101 = Reserved

- 100 = Four address bytes

- 011 = Three address bytes

- 010 = Two address bytes

- 001 = One address bytes

- 000 = Zero address bytes

### bit 17-10 READOPCODE<7:0>: Op code Value for Read Operation bits

### These bits contain the 8-bit op code value for read operation.

### bit 9-8 TYPEDATA<1:0>: SQI Type Data Enable bits

The boot controller will receive the data in Single Lane, Dual Lane, or Quad Lane.

- 11 = Reserved

- 10 = Quad Lane mode data is enabled

- 01 = Dual Lane mode data is enabled

- 00 = Single Lane mode data is enabled

## bit 7-6 **TYPEDUMMY<1:0>:** SQI Type Dummy Enable bits

- The boot controller will send the dummy in Single Lane, Dual Lane, or Quad Lane.

- 11 = Reserved

- 10 = Quad Lane mode dummy is enabled

- 01 = Dual Lane mode dummy is enabled

- 00 = Single Lane mode dummy is enabled

### REGISTER 22-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bit<br>11 = Reserved                                                                                                                                                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full</li> <li>01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full</li> <li>00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)</li> </ul> |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                  |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                         |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                      |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit.                                                                                                                                                                                                                                                              |

|         | This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.                                                                                                                                                |

|         | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed</li> </ul>                                                                                                                                                                                                        |

| bit 0   | <ul> <li>URXDA: Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                 |

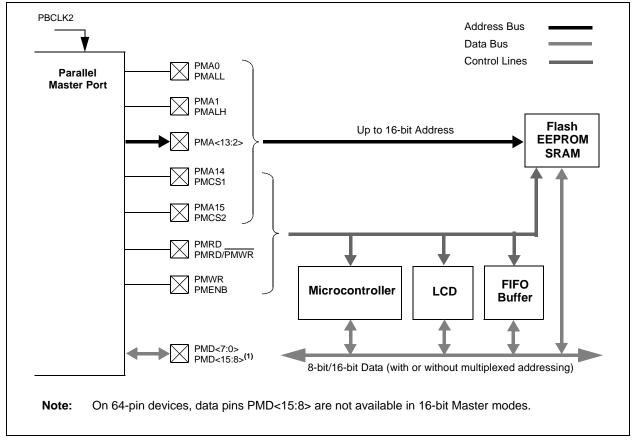

## 23.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features<br>of the PIC32MZ EF family of devices. It is<br>not intended to be a comprehensive refer-<br>ence source. To complement the informa-<br>tion in this data sheet, refer to <b>Section 13</b> . |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | "Parallel Master Port (PMP)"                                                                                                                                                                                                           |

|       | (DS60001128) in the "PIC32 Family Ref-                                                                                                                                                                                                 |

|       | erence Manual", which is available from                                                                                                                                                                                                |

|       | the Microchip web site (www.micro-<br>chip.com/PIC32).                                                                                                                                                                                 |

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. The following are key features of the PMP module:

- 8-bit,16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options:

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- Parallel Slave Port support:

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait states

- Operate during Sleep and Idle modes

- Separate configurable read/write registers or dual buffers for Master mode

- Fast bit manipulation using CLR, SET, and INV registers

Note: On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

### REGISTER 28-6: ADCIMCON2: ADC INPUT MODE CONTROL REGISTER 2 (CONTINUED)

| REGISTER | 20-0. ADCINICONZ. ADC INFUT IN                          |

|----------|---------------------------------------------------------|

| bit 21   | DIFF26: AN26 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN26 is using Differential mode                     |

|          | 0 = AN26 is using Single-ended mode                     |

| bit 20   | <b>SIGN26:</b> AN26 Signed Data Mode bit <sup>(1)</sup> |

|          | 1 = AN26 is using Signed Data mode                      |

|          | 0 = AN26 is using Unsigned Data mode                    |

| bit 19   | DIFF25: AN25 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN25 is using Differential mode                     |

|          | 0 = AN25 is using Single-ended mode                     |

| bit 18   | SIGN25: AN25 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN25 is using Signed Data mode                      |

|          | 0 = AN25 is using Unsigned Data mode                    |

| bit 17   | DIFF24: AN24 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN24 is using Differential mode                     |

|          | 0 = AN24 is using Single-ended mode                     |

| bit 16   | SIGN24: AN24 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN24 is using Signed Data mode                      |

|          | 0 = AN24 is using Unsigned Data mode                    |

| bit 15   | DIFF23: AN23 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN23 is using Differential mode                     |

|          | 0 = AN23 is using Single-ended mode                     |

| bit 14   | SIGN23: AN23 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN23 is using Signed Data mode                      |

|          | 0 = AN23 is using Unsigned Data mode                    |

| bit 13   | DIFF22: AN22 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN22 is using Differential mode                     |

|          | 0 = AN22 is using Single-ended mode                     |

| bit 12   | SIGN22: AN22 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN22 is using Signed Data mode                      |

|          | 0 = AN22 is using Unsigned Data mode                    |

| bit 11   | DIFF21: AN21 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN21 is using Differential mode                     |

|          | 0 = AN21 is using Single-ended mode                     |

| bit 10   | SIGN21: AN21 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN21 is using Signed Data mode                      |

|          | 0 = AN21 is using Unsigned Data mode                    |

| bit 9    | DIFF20: AN20 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN20 is using Differential mode                     |

|          | 0 = AN20 is using Single-ended mode                     |

| bit 8    | SIGN20: AN20 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN20 is using Signed Data mode                      |

|          | 0 = AN20 is using Unsigned Data mode                    |

| bit 7    | DIFF19: AN19 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN19 is using Differential mode                     |

|          | 0 = AN19 is using Single-ended mode                     |

|          |                                                         |

Note 1: This bit is not available on 64-pin devices.

# PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

|              |                        |                        |                        |                        |                        |                        | • • = • • •            |                        |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|              | R/W-0                  |

| 31:24        | AGIEN31 <sup>(1)</sup> | AGIEN30 <sup>(1)</sup> | AGIEN29 <sup>(1)</sup> | AGIEN28 <sup>(1)</sup> | AGIEN27 <sup>(1)</sup> | AGIEN26 <sup>(1)</sup> | AGIEN25 <sup>(1)</sup> | AGIEN24 <sup>(1)</sup> |

| 00.40        | R/W-0                  |

| 23:16        | AGIEN23 <sup>(1)</sup> | AGIEN22 <sup>(1)</sup> | AGIEN21 <sup>(1)</sup> | AGIEN20 <sup>(1)</sup> | AGIEN19 <sup>(1)</sup> | AGIEN18                | AGIEN17                | AGIEN16                |

| 45.0         | R/W-0                  |

| 15:8         | AGIEN15                | AGIEN14                | AGIEN13                | AGIEN12                | AGIEN11                | AGIEN10                | AGIEN9                 | AGIEN8                 |

| 7.0          | R/W-0                  |

| 7:0          | AGIEN7                 | AGIEN6                 | AGIEN5                 | AGIEN4                 | AGIEN3                 | AGIEN2                 | AGIEN1                 | AGIEN0                 |

### REGISTER 28-8: ADCGIRQEN1: ADC GLOBAL INTERRUPT ENABLE REGISTER 1

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

bit 31-0 AGIEN31:AGIEN0: ADC Global Interrupt Enable bits

- 1 = Interrupts are enabled for the selected analog input. The interrupt is generated after the converted data is ready (indicated by the ARDYx bit ('x' = 31-0) of the ADCDSTAT1 register)

- 0 = Interrupts are disabled

**Note 1:** This bit is not available on 64-pin devices.

### REGISTER 28-9: ADCGIRQEN2: ADC GLOBAL INTERRUPT ENABLE REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 24.24        | U-0                    |

| 31:24        | —                      | —                      | —                      | —                      | —                      | —                      | —                      | —                      |

| 00.40        | U-0                    |

| 23:16        | —                      | -                      | -                      | _                      | —                      | —                      | —                      | _                      |

| 45.0         | U-0                    | U-0                    | U-0                    | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

| 15:8         | —                      | -                      | —                      | AGIEN44                | AGIEN43                | AGIEN42 <sup>(2)</sup> | AGIEN41 <sup>(2)</sup> | AGIEN40 <sup>(2)</sup> |

| 7.0          | R/W-0                  |

| 7:0          | AGIEN39 <sup>(2)</sup> | AGIEN38 <sup>(2)</sup> | AGIEN37 <sup>(2)</sup> | AGIEN36 <sup>(2)</sup> | AGIEN35 <sup>(2)</sup> | AGIEN34 <sup>(1)</sup> | AGIEN33 <sup>(1)</sup> | AGIEN32 <sup>(1)</sup> |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-13 Unimplemented: Read as '0'

bit 12-0 AGIEN44:AGIEN32 ADC Global Interrupt Enable bits

- 1 = Interrupts are enabled for the selected analog input. The interrupt is generated after the converted data is ready (indicated by the ARDY*x* bit ('x' = 44-32) of the ADCDSTAT2 register)

- 0 =Interrupts are disabled

- Note 1: This bit is not available on 64-pin devices.

- 2: This bit is not available on 64-pin and 100-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 04-04        | R-0, HS, HC            |

| 31:24        | EIRDY31 <sup>(1)</sup> | EIRDY30 <sup>(1)</sup> | EIRDY29 <sup>(1)</sup> | EIRDY28 <sup>(1)</sup> | EIRDY27 <sup>(1)</sup> | EIRDY26 <sup>(1)</sup> | EIRDY25 <sup>(1)</sup> | EIRDY24 <sup>(1)</sup> |

| 00.40        | R-0, HS, HC            |

| 23:16        | EIRDY23 <sup>(1)</sup> | EIRDY22 <sup>(1)</sup> | EIRDY21 <sup>(1)</sup> | EIRDY20 <sup>(1)</sup> | EIRDY19 <sup>(1)</sup> | EIRDY18                | EIRDY17                | EIRDY16                |

| 45.0         | R-0, HS, HC            |

| 15:8         | EIRDY15                | EIRDY14                | EIRDY13                | EIRDY12                | EIRDY11                | EIRDY10                | EIRDY9                 | EIRDY8                 |

|              | R-0, HS, HC            |

| 7:0          | EIRDY7                 | EIRDY6                 | EIRDY5                 | EIRDY4                 | EIRDY3                 | EIRDY2                 | EIRDY1                 | EIRDY0                 |

|              |                        |                        |                        |                        |                        |                        |                        |                        |

### REGISTER 28-30: ADCEISTAT1: ADC EARLY INTERRUPT STATUS REGISTER 1

| Legend:           | HS = Hardware Set | HC = Hardware Cleared    |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 EIRDY31:EIRDY0: Early Interrupt for Corresponding Analog Input Ready bits

- 1 = This bit is set when the early interrupt event occurs for the specified analog input. An interrupt will be generated if early interrupts are enabled in the ADCEIEN1 register. For the Class 1 analog inputs, this bit will set as per the configuration of the ADCEIS<2:0> bits in the ADCXTIME register. For the shared ADC module, this bit will be set as per the configuration of the ADCEIS<2:0> bits in the ADCCIS<2:0> bits in the ADCCON2 register.

- 0 = Interrupts are disabled

- Note 1: This bit is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |  |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--|

| 04.04        | U-0                    |  |

| 31:24        |                        | —                      | —                      | —                      | —                      | —                      | —                      | —                      |  |

| 22:46        | U-0                    |  |

| 23:16        | —                      | —                      | _                      | —                      | _                      | —                      | —                      | —                      |  |

| 45.0         | U-0                    | U-0                    | U-0                    | R-0, HS, HC            |  |

| 15:8         | —                      | —                      | _                      | EIRDY44 <sup>(2)</sup> | EIRDY43 <sup>(2)</sup> | EIRDY42 <sup>(2)</sup> | EIRDY41 <sup>(2)</sup> | EIRDY40 <sup>(2)</sup> |  |

| 7.0          | R-0, HS, HC            |  |

| 7:0          | EIRDY39 <sup>(2)</sup> | EIRDY38 <sup>(2)</sup> | EIRDY37 <sup>(2)</sup> | EIRDY36 <sup>(2)</sup> | EIRDY35 <sup>(2)</sup> | EIRDY34 <sup>(1)</sup> | EIRDY33 <sup>(1)</sup> | EIRDY32 <sup>(1)</sup> |  |

### REGISTER 28-31: ADCEISTAT2: ADC EARLY INTERRUPT STATUS REGISTER 2

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                   |  |  |  |  |

|-------------------|-------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

#### bit 31-13 Unimplemented: Read as '0'

bit 31-0 **EIRDY44:EIRDY32:** Early Interrupt for Corresponding Analog Input Ready bits

- 1 = This bit is set when the early interrupt event occurs for the specified analog input. An interrupt will be generated if early interrupts are enabled in the ADCEIEN2 register. For the Class 1 analog inputs, this bit will set as per the configuration of the ADCEIS<2:0> bits in the ADCXTIME register. For the shared ADC module, this bit will be set as per the configuration of the ADCEIS<2:0> bits in the ADCEIS<2:0> bits in the ADCCON2 register.

- 0 = Interrupts are disabled

**Note 1:** This bit is not available on 64-pin devices.

2: This bit is not available on 64-pin and 100-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23.10        | —                 | —                 | ТХВО              | TXBP              | RXBP              | TXWARN            | RXWARN           | EWARN            |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | TERRCI            | NT<7:0>           |                   |                  |                  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          |                   |                   |                   | RERRC             | NT<7:0>           |                   |                  |                  |

### REGISTER 29-5: CITREC: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER

### Legend: