Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32 <sup>®</sup> M-Class                                                      |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024eff144-i-pl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.4 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available from the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.5 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements.

#### 2.6 Trace

The trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

# 2.7 External Oscillator Pins

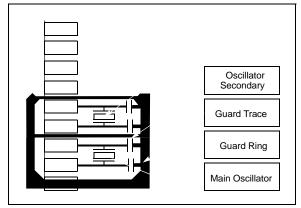

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

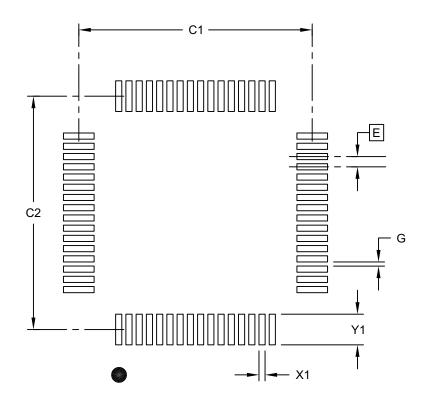

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

#### 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

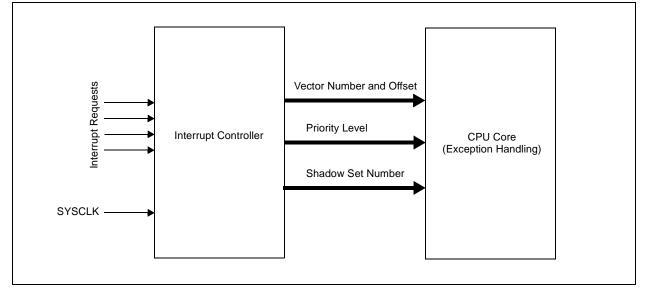

# 7.0 CPU EXCEPTIONS AND INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108) and Section 50. "CPU MIPS32<sup>®</sup> for Devices with microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MZ EF devices generate interrupt requests in response to interrupt events from peripheral modules. The Interrupt Controller module exists outside of the CPU and prioritizes the interrupt events before presenting them to the CPU.

The CPU handles interrupt events as part of the exception handling mechanism, which is described in **Section 7.1 "CPU Exceptions"**.

The Interrupt Controller module includes the following features:

- Up to 213 interrupt sources and vectors with dedicated programmable offsets, eliminating the need for redirection

- · Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Seven shadow register sets that can be used for any priority level, eliminating software context switch and reducing interrupt latency

- Software can generate any interrupt

Figure 7-1 shows the block diagram for the Interrupt Controller and CPU exceptions.

#### FIGURE 7-1: CPU EXCEPTIONS AND INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

| (1)                             | XODO Vester Nerre             | IRQ | Maatan H     |          | IEC0<22> IPC5<20:18> IPC5<17:16>   IEC0<22> IPC5<20:18> IPC5<17:16>   IEC0<23> IPC5<28:26> IPC5<25:24>   IEC0<24> IPC6<4:2> IPC6<1:0>   IEC0<25> IPC6<20:18> IPC6<9:8>   IEC0<26> IPC6<20:18> IPC6<17:16>   IEC0<27> IPC6<28:26> IPC6<25:24>   IEC0<28> IPC6<28:26> IPC6<25:24>   IEC0<28> IPC7<4:2> IPC6<25:24>   IEC0<28> IPC7<4:2> IPC6<25:24>   IEC0<29> IPC7<12:10> IPC7<9:8>   IEC0<30> IPC7<20:18> IPC7<17:16>   IEC1<0> IPC8<4:2> IPC8<1:0>   IEC1<2> IPC8<20:18> IPC8<1:0>   IEC1<2> IPC8<28:26> IPC8<25:24>   IEC1<3> IPC9<4:2> IPC9<1:0>   IEC1<2> IPC9<20:18> IPC9<1:0>   IEC1<4> IPC9<22:18> IPC9<1:0>   IEC1<6> IPC9<28:26> IPC9<25:24>   IEC1<6> IPC9<28:26> IPC9<25:24>   < |              |              | Persistent |

|---------------------------------|-------------------------------|-----|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|------------|

| Interrupt Source <sup>(1)</sup> | XC32 Vector Name              | #   | Vector #     | Flag     | Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Priority     | Sub-priority | Interrupt  |

| Output Compare 4                | _OUTPUT_COMPARE_4_VECTOR      | 22  | OFF022<17:1> | IFS0<22> | IEC0<22>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC5<20:18>  | IPC5<17:16>  | No         |

| External Interrupt 4            | _EXTERNAL_4_VECTOR            | 23  | OFF023<17:1> | IFS0<23> | IEC0<23>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC5<28:26>  | IPC5<25:24>  | No         |

| Timer5                          | _TIMER_5_VECTOR               | 24  | OFF024<17:1> | IFS0<24> | IEC0<24>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC6<4:2>    | IPC6<1:0>    | No         |

| Input Capture 5 Error           | _INPUT_CAPTURE_5_ERROR_VECTOR | 25  | OFF025<17:1> | IFS0<25> | IEC0<25>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC6<12:10>  | IPC6<9:8>    | Yes        |

| Input Capture 5                 | _INPUT_CAPTURE_5_VECTOR       | 26  | OFF026<17:1> | IFS0<26> | IEC0<26>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC6<20:18>  | IPC6<17:16>  | Yes        |

| Output Compare 5                | _OUTPUT_COMPARE_5_VECTOR      | 27  | OFF027<17:1> | IFS0<27> | IEC0<27>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC6<28:26>  | IPC6<25:24>  | No         |

| Timer6                          | _TIMER_6_VECTOR               | 28  | OFF028<17:1> | IFS0<28> | IEC0<28>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC7<4:2>    | IPC7<1:0>    | No         |

| Input Capture 6 Error           | _INPUT_CAPTURE_6_ERROR_VECTOR | 29  | OFF029<17:1> | IFS0<29> | IEC0<29>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC7<12:10>  | IPC7<9:8>    | Yes        |

| Input Capture 6                 | _INPUT_CAPTURE_6_VECTOR       | 30  | OFF030<17:1> | IFS0<30> | IEC0<30>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC7<20:18>  | IPC7<17:16>  | Yes        |

| Output Compare 6                | _OUTPUT_COMPARE_6_VECTOR      | 31  | OFF031<17:1> | IFS0<31> | IEC0<31>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC7<28:26>  | IPC7<25:24>  | No         |

| Timer7                          | _TIMER_7_VECTOR               | 32  | OFF032<17:1> | IFS1<0>  | IEC1<0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC8<4:2>    | IPC8<1:0>    | No         |

| Input Capture 7 Error           | _INPUT_CAPTURE_7_ERROR_VECTOR | 33  | OFF033<17:1> | IFS1<1>  | IEC1<1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC8<12:10>  | IPC8<9:8>    | Yes        |

| Input Capture 7                 | _INPUT_CAPTURE_7_VECTOR       | 34  | OFF034<17:1> | IFS1<2>  | IEC1<2>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC8<20:18>  | IPC8<17:16>  | Yes        |

| Output Compare 7                | _OUTPUT_COMPARE_7_VECTOR      | 35  | OFF035<17:1> | IFS1<3>  | IEC1<3>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC8<28:26>  | IPC8<25:24>  | No         |

| Timer8                          | _TIMER_8_VECTOR               | 36  | OFF036<17:1> | IFS1<4>  | IEC1<4>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC9<4:2>    | IPC9<1:0>    | No         |

| Input Capture 8 Error           | _INPUT_CAPTURE_8_ERROR_VECTOR | 37  | OFF037<17:1> | IFS1<5>  | IEC1<5>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC9<12:10>  | IPC9<9:8>    | Yes        |

| Input Capture 8                 | _INPUT_CAPTURE_8_VECTOR       | 38  | OFF038<17:1> | IFS1<6>  | IEC1<6>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC9<20:18>  | IPC9<17:16>  | Yes        |

| Output Compare 8                | _OUTPUT_COMPARE_8_VECTOR      | 39  | OFF039<17:1> | IFS1<7>  | IEC1<7>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC9<28:26>  | IPC9<25:24>  | No         |

| Timer9                          | _TIMER_9_VECTOR               | 40  | OFF040<17:1> | IFS1<8>  | IEC1<8>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC10<4:2>   | IPC10<1:0>   | No         |

| Input Capture 9 Error           | _INPUT_CAPTURE_9_ERROR_VECTOR | 41  | OFF041<17:1> | IFS1<9>  | IEC1<9>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC10<12:10> | IPC10<9:8>   | Yes        |

| Input Capture 9                 | _INPUT_CAPTURE_9_VECTOR       | 42  | OFF042<17:1> | IFS1<10> | IEC1<10>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC10<20:18> | IPC10<17:16> | Yes        |

| Output Compare 9                | _OUTPUT_COMPARE_9_VECTOR      | 43  | OFF043<17:1> | IFS1<11> | IEC1<11>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC10<28:26> | IPC10<25:24> | No         |

| ADC Global Interrupt            | _ADC_VECTOR                   | 44  | OFF044<17:1> | IFS1<12> | IEC1<12>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC11<4:2>   | IPC11<1:0>   | Yes        |

| ADC FIFO Data Ready Interrupt   | _ADC_FIFO_VECTOR              | 45  | OFF045<17:1> | IFS1<13> | IEC1<13>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC11<12:10> | IPC11<9:8>   | Yes        |

| ADC Digital Comparator 1        | _ADC_DC1_VECTOR               | 46  | OFF046<17:1> | IFS1<14> | IEC1<14>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC11<20:18> | IPC11<17:16> | Yes        |

| ADC Digital Comparator 2        | _ADC_DC2_VECTOR               | 47  | OFF047<17:1> | IFS1<15> | IEC1<15>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC11<28:26> | IPC11<25:24> | Yes        |

| ADC Digital Comparator 3        | _ADC_DC3_VECTOR               | 48  | OFF048<17:1> | IFS1<16> | IEC1<16>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC12<4:2>   | IPC12<1:0>   | Yes        |

| ADC Digital Comparator 4        | _ADC_DC4_VECTOR               | 49  | OFF049<17:1> | IFS1<17> | IEC1<17>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC12<12:10> | IPC12<9:8>   | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

3: This interrupt source is not available on 100-pin devices.

4: This interrupt source is not available on 124-pin devices.

# 11.0 HI-SPEED USB WITH ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 51. "Hi-Speed USB with **On-The-Go** (OTG)" (DS60001326) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 embedded host, device, or OTG implementation with a minimum of external components.

The module supports Hi-Speed, Full-Speed, or Low-Speed in any of the operating modes. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the RAM controller, packet encode/decode, UTM synchronization, end-point control, a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The USB module includes the following features:

- USB Hi-Speed, Full-Speed, and Low-Speed support for host and device

- USB OTG support with one or more Hi-Speed, Full-Speed, or Low-Speed device

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Integrated 8-channel DMA to access system RAM and Flash

- Seven transmit endpoints and seven receive endpoints, in addition to Endpoint 0

- Session Request Protocol (SRP) and Host Negotiation Protocol (HNP) support

- Suspend and resume signaling support

- Dynamic FIFO sizing

- Integrated RAM for the FIFOs, eliminating the need for system RAM for the FIFOs

- Link power management support

- Note 1: The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

- If the USB module is used, the Primary Oscillator (POSC) is limited to either 12 MHz or 24 MHz.

### TABLE 12-19: PORTJ REGISTER MAP FOR 124-PIN DEVICES ONLY

| ess                         |                                 | 0         |       |       |       |       |                |       |              | Bits         |      |      |      |              |      |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|--------------|--------------|------|------|------|--------------|------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9         | 24/8         | 23/7 | 22/6 | 21/5 | 20/4         | 19/3 | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0800                        | ANSELJ                          | 31:16     | —     | -     | —     | -     | —              | —     | —            |              | —    |      |      | —            | —    | —            |              |              | 0000          |

| 0000                        | 7410220                         | 15:0      | —     | _     | —     | —     | ANSJ11         | _     | ANSJ9        | ANSJ8        | —    | _    | _    | —            | _    | —            | _            | _            | 0B00          |

| 0810                        | TRISJ                           | 31:16     | —     | -     | —     | -     | —              | —     | —            | —            | —    | —    | _    | —            | —    | —            | _            | _            | 0000          |

| 00.0                        |                                 | 15:0      | —     | _     | —     | -     | TRISJ11        | _     | TRISJ9       | TRISJ8       | _    | —    | _    | TRISJ4       | _    | TRISJ2       | TRISJ1       | TRISJ0       | 0B17          |

| 0820                        | PORTJ                           | 31:16     | —     | —     | —     | —     | —              | —     | —            |              | —    | —    | —    | —            | _    | -            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | RJ11           | _     | RJ9          | RJ8          | —    | —    | _    | RJ4          | —    | RJ2          | RJ1          | RJ0          | xxxx          |

| 0830                        | LATJ                            | 31:16     | —     | —     | —     | —     | —              | _     |              |              | —    | —    | _    | —            | —    | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     |       | _     | _     | LATJ11         | _     | LATJ9        | LATJ8        |      | _    |      | LATJ4        | _    | LATJ2        | LATJ1        | LATJ0        | XXXX          |

| 0840                        | ODCJ                            | 31:16     | —     |       | —     | _     | —              | _     | —            | —            | —    | —    | _    | —            | _    | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     |       | —     | _     | ODCJ11         | _     | ODCJ9        | ODCJ8        | —    | —    | _    | ODCJ4        | _    | ODCJ2        | ODCJ1        | ODCJ0        | 0000          |

| 0850                        | CNPUJ                           | 31:16     | —     | _     | —     | —     | —              | —     | —            | —            | —    | —    | _    | —            | _    | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | CNPUJ11        | _     | CNPUJ9       | CNPUJ8       | _    | _    | _    | CNPUJ4       | _    | CNPUJ2       | CNPUJ1       | CNPUJ0       | 0000          |

| 0860                        | CNPDJ                           | 31:16     | _     | _     | _     | _     | —              | _     | —            | —            | _    | _    | _    | —            | _    | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | CNPDJ11        | _     | CNPDJ9       | CNPDJ8       | _    | _    | _    | CNPDJ4       | _    | CNPDJ2       | CNPDJ1       | CNPDJ0       | 0000          |

| 0070                        | CNICONU                         | 31:16     | —     |       | _     |       |                |       |              |              |      |      |      | _            |      | _            |              |              | 0000          |

| 0870                        | CNCONJ                          | 15:0      | ON    | _     | —     |       | EDGE<br>DETECT | —     | —            | —            |      | —    | -    | —            | —    | —            | -            | -            | 0000          |

| 0880                        | CNENJ                           | 31:16     | _     | _     | —     | -     | —              | _     | —            | _            | _    | —    | _    | —            | _    | _            | _            | _            | 0000          |

| 0000                        | CINEINJ                         | 15:0      |       |       |       |       | CNENJ11        |       | CNENJ9       | CNENJ8       |      |      |      | CNENJ4       |      | CNENJ2       | CNENJ1       | CNENJ0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | —     | —              | —     | —            | —            | —    | —    | —    | —            | —    | —            | —            | _            | 0000          |

| 0890                        | CNSTATJ                         | 15:0      | -     | —     | -     | —     | CN<br>STATJ11  | -     | CN<br>STATJ9 | CN<br>STATJ8 | —    | —    | —    | CN<br>STATJ4 | —    | CN<br>STATJ2 | CN<br>STATJ1 | CN<br>STATJ0 | 0000          |

| 0040                        |                                 | 31:16     | —     |       | —     |       | —              |       | —            | —            |      | —    |      | —            | —    | —            |              |              | 0000          |

| 08A0                        | CNNEJ                           | 15:0      | —     |       | —     |       | CNNEJ11        |       | CNNEJ9       | CNNEJ8       |      | —    |      | CNNEJ4       | —    | CNNEJ2       | CNNEJ1       | CNNEJ0       | 0000          |

| 08B0                        | CNFJ                            | 31:16     | —     |       | —     |       | —              |       | —            | —            |      | —    |      | —            | _    | —            |              |              | 0000          |

| UOBU                        | CNFJ                            | 15:0      | —     |       | —     |       | CNFJ11         | _     | CNFJ9        | CNFJ8        |      | —    | _    | CNFJ4        |      | CNFJ2        | CNFJ1        | CNFJ0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

| SSS                         |                  |           |       |       |       |       |       |       |      | B    | its  |      |      |      |      |           |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-----------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1   | 16/0 | All Resets |

| 4444                        | IC4R             | 31:16     | —     | —     | -     | —     | -     | —     | —    | —    | —    | -    | —    | —    | —    | —         | -      | —    | 0000       |

| 1444                        | IC4R             | 15:0      |       | _     | —     | _     |       | _     | _    | _    | _    | —    | —    | —    |      | IC4R      | <3:0>  |      | 0000       |

| 1448                        | IC5R             | 31:16     |       | —     | —     | _     |       | —     | —    |      | —    | _    | _    | _    | _    | _         | _      |      | 0000       |

| 1440                        | 10.51            | 15:0      |       | —     | —     | —     |       | —     | —    | —    | _    | _    | —    | —    |      | IC5R      | <3:0>  |      | 0000       |

| 144C                        | IC6R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —         | —      | —    | 0000       |

| 1440                        | ICOIX            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | IC6R      | <3:0>  |      | 0000       |

| 1450                        | IC7R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —         | —      | —    | 0000       |

| 1430                        | 10/10            | 15:0      | _     | _     | —     | —     | _     | _     | —    | _    | _    | —    | _    | —    |      | IC7R      | <3:0>  |      | 0000       |

| 1454                        | IC8R             | 31:16     | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —         | —      | —    | 0000       |

| 1-0-1                       | 10011            | 15:0      | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | IC8R      | <3:0>  |      | 0000       |

| 1458                        | IC9R             | 31:16     | -     | —     | —     | —     | _     | —     | —    | _    | _    | —    | _    | —    | —    | —         | —      | —    | 0000       |

|                             |                  | 15:0      | -     | —     |       | —     | _     | _     | —    | —    | _    |      |      | _    |      | IC9R<3:0> |        |      | 0000       |

| 1460                        | OCFAR            | 31:16     | _     | —     |       | —     | _     | —     | —    | _    | —    | _    | —    | —    | —    | —         | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     |       | —     |       | —     | —    |      | _    | —    | —    | —    |      | OCFA      | R<3:0> |      | 0000       |

| 1468                        | U1RXR            | 31:16     | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |      | —         | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |      | U1RXI     | R<3:0> |      | 0000       |

| 146C                        | U1CTSR           | 31:16     | _     |       |       | —     | _     | —     | —    | —    | _    |      |      | —    | —    | —         | —      | —    | 0000       |

|                             |                  | 15:0      | —     | —     | _     | —     | _     | —     | —    | —    | —    | —    | —    | —    |      | U1CTS     |        |      | 0000       |

| 1470                        | U2RXR            | 31:16     | _     | —     |       | _     | _     | —     | —    | —    | —    | —    | _    | —    | —    | —         | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | -     | —     | —     | —     | —    | _    | _    | —    | —    | —    |      | U2RXI     |        |      | 0000       |

| 1474                        | U2CTSR           | 31:16     | _     | _     |       |       | _     | _     | _    |      | _    |      |      | _    | _    | —         | —      | —    | 0000       |

|                             |                  | 15:0      | _     | _     | -     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2CTS     |        |      | 0000       |

| 1478                        | <b>U3RXR</b>     | 31:16     | _     |       | -     | _     | _     |       | _    | _    | _    | —    |      | _    | —    |           | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     |       | _     |       | _     | _    | _    | _    | _    |      | _    |      | U3RXI     |        |      | 0000       |

| 147C                        | <b>U3CTSR</b>    | 31:16     | _     | _     |       | _     | _     | _     | _    | _    | _    |      |      | _    | —    |           | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     |       | _     |       | _     | _    | _    | _    | _    | _    | _    |      | U3CTS     | R<3:0> |      | 0000       |

| 1480                        | U4RXR            | 31:16     |       | —     | _     | _     | _     | —     | _    |      | _    | _    | _    | _    | _    |           |        | _    | 0000       |

|                             |                  | 15:0      |       | —     |       | _     | _     | —     | —    |      | _    | _    | _    | _    |      | U4RXI     |        |      | 0000       |

| 1484                        | U4CTSR           | 31:16     |       | —     |       | _     | _     | —     | —    |      | _    | _    | _    | _    |      | -         | —      | _    | 0000       |

|                             |                  | 15:0      |       | —     | —     | —     | -     | —     | —    | —    | —    |      | _    | —    |      | U4CTS     | R<3:0> |      | 0000       |

## TABLE 12-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 22:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 7.0       | R-0, HC, HS       | R-0, HC, HS       | R-0, HC, HS       | U-0               | U-0               | U-0               | U-0              | R-0, HC, HS      |

| 7:0       | BAD1              | BAD2              | DMTEVENT          | _                 |                   | _                 | _                | WINOPN           |

#### REGISTER 15-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:           | HC = Hardware Cleared | HS = Hardware Set                |            |

|-------------------|-----------------------|----------------------------------|------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as   | '0'        |

| -n = Value at POR | '1' = Bit is set      | 0' = Bit is cleared $x = Bit is$ | is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP1<7:0> value was not detected                                                                                     |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer even was not detected                                                                                             |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | _                 | -                | —                |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   | MONT              | H10<3:0>          |                   | MONTH01<3:0>      |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   | DAY               | 10<1:0>           |                   |                   | DAY01             | <3:0>            |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   | _                 | _                 | WDAY01<3:0>       |                   |                  |                  |  |  |  |

#### REGISTER 25-6: ALRMDATE: ALARM DATE VALUE REGISTER

# Legend:

| Legenu.           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

٦

Figure 26-10 shows the Security Association control word structure.

The Crypto Engine fetches different structures for different flows and ensures that hardware fetches minimum words from SA required for processing. The structure is ready for hardware optimal data fetches.

| Bit<br>Range | Bit<br>31/23/15/7                                                                                                                                                            | Bit<br>30/22/14/6                                                                                                                              | Bit<br>29/21/13/5              | Bit<br>28/20/12/4                | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 31-24        |                                                                                                                                                                              |                                                                                                                                                | VERIFY                         |                                  | NO_RX             | OR_EN             | ICVONLY          | IRFLAG           |  |  |  |  |  |  |

| 23-16        | LNC                                                                                                                                                                          | LOADIV                                                                                                                                         | FB                             | FLAGS                            | _                 | _                 |                  | ALGO<6>          |  |  |  |  |  |  |

| 15-8         |                                                                                                                                                                              |                                                                                                                                                | ALGO                           | <5:0>                            |                   |                   | ENC              | KEY<br>SIZE<1>   |  |  |  |  |  |  |

| 7-0          | KEY<br>SIZE<0>                                                                                                                                                               | ML                                                                                                                                             | ILTITASK<2:                    | 0>                               | CRYPTOALGO<3:0>   |                   |                  |                  |  |  |  |  |  |  |

| bit 31-30    | Reserved:                                                                                                                                                                    | Do not use                                                                                                                                     |                                |                                  |                   |                   |                  |                  |  |  |  |  |  |  |

| bit 29       | 1 = NIST pr                                                                                                                                                                  | <b>ERIFY:</b> NIST Procedure Verification Setting<br>= NIST procedures are to be used<br>= Do not use NIST procedures                          |                                |                                  |                   |                   |                  |                  |  |  |  |  |  |  |

| bit 28       | Reserved:                                                                                                                                                                    | eserved: Do not use                                                                                                                            |                                |                                  |                   |                   |                  |                  |  |  |  |  |  |  |

| bit 27       | 1 = Only cal                                                                                                                                                                 | IO_RX: Receive DMA Control Setting<br>= Only calculate ICV for authentication calculations<br>= Normal processing                              |                                |                                  |                   |                   |                  |                  |  |  |  |  |  |  |

| bit 26       | 1 = OR the                                                                                                                                                                   | <b>DR_EN:</b> OR Register Bits Enable Setting<br>1 = OR the register bits with the internal value of the CSR register<br>0 = Normal processing |                                |                                  |                   |                   |                  |                  |  |  |  |  |  |  |

| bit 25       | This affects<br>1 = Only thr                                                                                                                                                 | ncomplete Ch<br>the SHA-1 al<br>ee words of th<br>ts from the H                                                                                | gorithm only.<br>ne HMAC res   | It has no eff<br>sult are availa |                   | ES algorithm      |                  |                  |  |  |  |  |  |  |

| bit 24       | This bit is se<br>1 = Save the                                                                                                                                               | nmediate Res<br>et when the in<br>e immediate r<br>save the imme                                                                               | nmediate res<br>result for has | ult for hashir                   | ng is request     | ed.               |                  |                  |  |  |  |  |  |  |

| bit 23       | 1 = Load a i                                                                                                                                                                 | New Keys Se<br>new set of key<br>oad new keys                                                                                                  | ys for encryp                  | tion and auth                    | nentication       |                   |                  |                  |  |  |  |  |  |  |

| bit 22       |                                                                                                                                                                              | oad IV Setting<br>e IV from this<br>next IV                                                                                                    |                                | ociation                         |                   |                   |                  |                  |  |  |  |  |  |  |

| bit 21       | 1 = Indicate                                                                                                                                                                 | ock Setting<br>cates that this<br>s this is the fi<br>s this is not th                                                                         | rst block of d                 | ata                              | o feed the IV     | ′ value.          |                  |                  |  |  |  |  |  |  |

| bit 20       | <b>FLAGS:</b> Incoming/Outgoing Flow Setting<br>1 = Security Association is associated with an outgoing flow<br>0 = Security Association is associated with an incoming flow |                                                                                                                                                |                                |                                  |                   |                   |                  |                  |  |  |  |  |  |  |

|              | Reserved:                                                                                                                                                                    | Do not uso                                                                                                                                     |                                |                                  |                   |                   |                  |                  |  |  |  |  |  |  |

#### FIGURE 26-10: FORMAT OF SA\_CTRL

### TABLE 28-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  | Bits             |   |   |  |   |   |                 |       |      |      |            |  |  |   |  |     |

|-----------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------|---|---|--|---|---|-----------------|-------|------|------|------------|--|--|---|--|-----|

| Virtual Address<br>(BF84_#) | Register<br>Name         | By Figure 2 |  |                  |   |   |  |   |   |                 |       | 17/1 | 16/0 | All Resets |  |  |   |  |     |

|                             | ADCDATA13                | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |                  | • | • |  | • | • | DATA<3          | 1:16> | •    | •    | •          |  |  | • |  | 000 |

|                             |                          | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |                  |   |   |  |   |   | DATA<           | 15:0> |      |      |            |  |  |   |  | 00  |

| B238                        | ADCDATA14                | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  | DATA<31:16> 0000 |   |   |  |   |   |                 |       |      |      |            |  |  |   |  |     |

|                             |                          | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  | DATA<15:0> 0000  |   |   |  |   |   |                 |       |      |      |            |  |  |   |  |     |

| B23C                        | ADCDATA15                | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |                  |   |   |  |   |   | DATA<           | 1:16> |      |      |            |  |  |   |  | 00  |

|                             |                          | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |                  |   |   |  |   |   | DATA<           |       |      |      |            |  |  |   |  | 00  |

| B240                        | ADCDATA16                | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |                  |   |   |  |   |   | DATA<3          |       |      |      |            |  |  |   |  | 00  |

| -                           |                          | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  | DATA<15:0> 0000  |   |   |  |   |   |                 |       |      |      |            |  |  |   |  |     |