Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-TQFP                                                                          |

| Supplier Device Package    | 144-TQFP (16x16)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024eff144t-i-ph |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1: **PIC32MZ EF FAMILY FEATURES**

|                   |                        |                     |      |          |                           |                 | Remap                                         | pable | Periph               | erals                                 |          |        |     |                                              |                | IS                 |                |                  |     |     |     |      |          |          |      |       |

|-------------------|------------------------|---------------------|------|----------|---------------------------|-----------------|-----------------------------------------------|-------|----------------------|---------------------------------------|----------|--------|-----|----------------------------------------------|----------------|--------------------|----------------|------------------|-----|-----|-----|------|----------|----------|------|-------|

| Device            | Program<br>Memory (KB) | Data<br>Memory (KB) | Pins | Packages | Boot Flash<br>Memory (KB) | Remappable Pins | Timers/<br>Capture/<br>Compare <sup>(1)</sup> | UART  | SPI/I <sup>2</sup> S | External<br>Interrupts <sup>(2)</sup> | CAN 2.0B | Crypto | RNG | DMA Channels<br>(Programmable/<br>Dedicated) | ADC (Channels) | Analog Comparators | USB 2.0 HS OTG | 1 <sup>2</sup> C | АМР | EBI | sai | RTCC | Ethernet | I/O Pins | JTAG | Trace |

| PIC32MZ0512EFE064 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 0        | N      | Y   | 8/12                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFF064 | 512                    | 128                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Υ   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      | 1     |

| PIC32MZ0512EFK064 |                        |                     | 64   | TQFP,    | 160                       | 34              | 9/9/9                                         | 6     | 4                    | 5                                     | 2        | Y      | Υ   | 8/18                                         | 24             | 2                  | Y              | 4                | Y   | N   | Y   | Y    | Υ        | 46       | Y    | Y     |

| PIC32MZ1024EFE064 |                        |                     | 04   | QFN      | 100                       | 34              | 9/9/9                                         | 0     | 4                    | 5                                     | 0        | Ν      | Υ   | 8/12                                         | 24             | 2                  | T              | 4                | T   |     | ľ   |      |          | 40       | T    |       |

| PIC32MZ1024EFF064 | 1024                   | 256                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Υ   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      | 1     |

| PIC32MZ1024EFK064 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 2        | Y      | Y   | 8/18                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFE100 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 0        | Ν      | Y   | 8/12                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFF100 | 512                    | 128                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      | 1     |

| PIC32MZ0512EFK100 |                        |                     | 100  | TQFP     | 160                       | 51              | 9/9/9                                         | 6     | 6                    | 5                                     | 2        | Y      | Y   | 8/18                                         | 40             | 2                  | Y              | 5                | Y   | Υ   | Y   | Υ    | Υ        | 78       | Y    | Y     |

| PIC32MZ1024EFE100 |                        |                     |      | I GI I   | 100                       | 51              | 3/3/3                                         | 0     |                      | 5                                     | 0        | Ν      | Y   | 8/12                                         | 40             | 2                  |                |                  |     | '   | '   |      | '        | 10       |      |       |

| PIC32MZ1024EFF100 | 1024                   | 256                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFK100 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 2        | Y      | Y   | 8/18                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFE124 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 0        | Ν      | Y   | 8/12                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFF124 | 512                    | 128                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFK124 |                        |                     | 124  | VTLA     | 160                       | 53              | 9/9/9                                         | 6     | 6                    | 5                                     | 2        | Y      | Y   | 8/18                                         | 48             | 2                  | Y              | 5                | Y   | Υ   | Υ   | Υ    | Y        | 97       | Y    | Y     |

| PIC32MZ1024EFE124 |                        |                     | 124  |          |                           |                 | 5/5/5                                         | Ū     |                      | Ŭ                                     | 0        | Ν      | Y   | 8/12                                         | -10            | 2                  |                | ľ                |     | '   | '   | '    | '        |          |      | '     |

| PIC32MZ1024EFF124 | 1024                   | 256                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFK124 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 2        | Y      | Y   | 8/18                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFE144 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 0        | Ν      | Y   | 8/12                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFF144 | 512                    | 128                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ0512EFK144 |                        |                     | 144  | LQFP,    | 160                       | 53              | 9/9/9                                         | 6     | 6                    | 5                                     | 2        | Y      | Y   | 8/18                                         | 48             | 2                  | Y              | 5                | Y   | Υ   | Y   | Υ    | Υ        | 120      | Y    | Y     |

| PIC32MZ1024EFE144 |                        |                     |      | TQFP     |                           |                 | 31313                                         | 0     |                      |                                       | 0        | Ν      | Y   | 8/12                                         | 40             | -                  |                |                  |     | '   | '   | '    | '        | 120      |      | '     |

| PIC32MZ1024EFF144 | 1024                   | 256                 |      |          |                           |                 |                                               |       |                      |                                       | 2        | Ν      | Y   | 8/16                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

| PIC32MZ1024EFK144 |                        |                     |      |          |                           |                 |                                               |       |                      |                                       | 2        | Y      | Y   | 8/18                                         |                |                    |                |                  |     |     |     |      |          |          |      |       |

Note 1:

Eight out of nine timers are remappable. Four out of five external interrupts are remappable. This device is available with a 252 MHz speed rating. 2: 3:

## TABLE 4-7: SYSTEM BUS REGISTER MAP

| sse                        |                  | a Bits    |       |       |        |        |        |        |       |       |       |       |       |       |       |       |       |       |               |

|----------------------------|------------------|-----------|-------|-------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| Virtual Addre:<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13  | 28/12  | 27/11  | 26/10  | 25/9  | 24/8  | 23/7  | 22/6  | 21/5  | 20/4  | 19/3  | 18/2  | 17/1  | 16/0  | All<br>Resets |

| 0510                       |                  | 31:16     | —     | —     | —      | —      | —      | _      | _     | _     | _     | —     | _     | —     |       | -     | -     | —     | 0000          |

| 0510                       | SBFLAG           | 15:0      | —     | _     | T13PGV | T12PGV | T11PGV | T10PGV | T9PGV | T8PGV | T7PGV | T6PGV | T5PGV | T4PGV | T3PGV | T2PGV | T1PGV | T0PGV | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-8: SYSTEM BUS TARGET 0 REGISTER MAP

| sse                         |                  |           |       |       |       |          |          |       |       |      | Bits     |       |           |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|----------|-------|-----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5      | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| 8020                        | SBT0ELOG1        | 31:16     | MULTI | —     | -     | —        |          | CODE  | <3:0> |      | —        | -     | —         | _    | —      | —      | —       | _      | 0000          |

| 0020                        | SBIULLOGI        | 15:0      |       |       |       | INIT     | TID<7:0> |       |       |      |          | REGIO | N<3:0>    |      | —      | C      | MD<2:0> |        | 0000          |

| 8024                        | SBT0ELOG2        | 31:16     | _     | —     | -     | —        | -        | _     | -     | —    | —        | —     | —         | _    | —      | —      | —       | _      | 0000          |

| 0024                        | SBIULLOGZ        | 15:0      | _     | —     |       | —        | _        | —     | _     | —    | _        | _     | —         |      | —      | _      | GROU    | P<1:0> | 0000          |

| 8028                        | SBT0ECON         | 31:16     | _     | _     | _     | —        | -        | _     | _     | ERRP | _        | _     | _         | _    | —      | _      | —       | -      | 0000          |

| 0020                        | SBIOLOON         | 15:0      | —     | —     |       | —        | _        |       | _     | _    | _        | _     | —         |      | —      | —      |         | _      | 0000          |

| 8030                        | SBT0ECLRS        | 31:16     | _     | —     |       | —        | _        | —     | _     | _    | _        | _     | _         |      | —      | —      |         |        | 0000          |

| 0000                        | SBIULCERG        | 15:0      | —     | —     |       | —        | _        |       | _     | _    | _        | _     | —         |      | —      | —      |         | CLEAR  | 0000          |

| 8038                        | SBT0ECLRM        | 31:16     | _     | —     |       | —        | _        |       | _     | _    | _        | _     | —         |      | —      | _      |         | _      | 0000          |

| 0000                        | OBTOLCER         | 15:0      | —     | —     | _     | —        | —        | —     | —     | _    | —        | —     | —         | —    | —      | —      | —       | CLEAR  | 0000          |

| 8040                        | SBT0REG0         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

| 0040                        | OBTOREGO         | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | —    |          |       | SIZE<4:0: | >    |        | —      | —       | _      | xxxx          |

| 8050                        | SBT0RD0          | 31:16     | _     | —     | -     | —        | -        | —     | _     | —    | _        | —     | —         | —    | —      | —      | —       | _      | xxxx          |

| 0000                        | CETOREO          | 15:0      |       | —     | -     | —        | -        | —     | -     | _    | —        | _     | —         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8058                        | SBT0WR0          | 31:16     | _     | —     | -     | —        | -        | —     | _     | —    | _        | —     | —         | —    | —      | —      | —       | _      | xxxx          |

| 0000                        | <b>OBIONIN</b>   | 15:0      | _     | _     | —     | —        | —        | —     | —     | —    | —        | —     | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8060                        | SBT0REG1         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

| 0000                        |                  | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | _    |          |       | SIZE<4:0: | >    | -      | —      | —       | _      | xxxx          |

| 8070                        | SBT0RD1          | 31:16     | _     | —     | _     | —        | —        | —     | _     | _    | _        | _     |           |      | —      | —      | —       | _      | xxxx          |

| 00.0                        | 5010101          | 15:0      | _     | —     | _     | —        | —        | —     | _     | _    | _        | _     |           |      | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8078                        | SBT0WR1          | 31:16     |       | —     | _     | —        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      |         | —      | xxxx          |

| 00.0                        | 50101111         | 15:0      | _     | —     | —     | —        | —        | —     |       |      | —        | —     | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0   |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|--------------------|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |  |  |  |  |

| 31:24        | —                 | —                 | _                 | _                 | -                 | _                 | —                | _                  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |  |  |  |  |

| 15:8         | —                 | _                 | _                 | _                 | -                 | _                 | _                |                    |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0                |  |  |  |  |

| 7:0          |                   |                   |                   | _                 |                   |                   | GROU             | <sup>D</sup> <1:0> |  |  |  |  |

#### **REGISTER 4-4:** SBTxELOG2: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 2 ('x' = 0-13)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

#### bit 31-3 Unimplemented: Read as '0'

- bit 1-0 GROUP<1:0>: Requested Permissions Group bits

- 11 = Group 3

- 10 = Group 2

- 01 = Group 1

- 00 = Group 0

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

#### REGISTER 4-5: SBTxECON: SYSTEM BUS TARGET 'x' ERROR CONTROL REGISTER ('x' = 0-13)

|              |                   | x = 0 = 13        |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        | —                 | —                 | _                 | _                 | -                 |                   | _                | ERRP             |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | -                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | —                 |                   |                   |                   |                   |                   |                  | —                |

| Legend:           |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-25 Unimplemented: Read as '0'

bit 24 ERRP: Error Control bit

1 = Report protection group violation errors

0 = Do not report protection group violation errors

bit 23-0 Unimplemented: Read as '0'

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

bit 12-10 IP1<2:0>: Interrupt Priority bits

| bit 12-10 | IP1<2:0>: Interrupt Priority bits                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                                                            |

|           | •                                                                                                        |

|           |                                                                                                          |

|           | 010 = Interrupt priority is 2                                                                            |

|           | 001 = Interrupt priority is 1                                                                            |

|           | 000 = Interrupt is disabled                                                                              |

| bit 9-8   | IS1<1:0>: Interrupt Subpriority bits                                                                     |

| DII 3-0   |                                                                                                          |

|           | 11 = Interrupt subpriority is 3<br>10 = Interrupt subpriority is 2                                       |

|           | 01 = Interrupt subpriority is 1                                                                          |

|           | 00 = Interrupt subpriority is 0                                                                          |

| bit 7-5   | Unimplemented: Read as '0'                                                                               |

| bit 4-2   | IPO<2:0>: Interrupt Priority bits                                                                        |

| DIL 4-2   |                                                                                                          |

|           | 111 = Interrupt priority is 7                                                                            |

|           | •                                                                                                        |

|           | •                                                                                                        |

|           | 010 = Interrupt priority is 2                                                                            |

|           | 001 = Interrupt priority is 1                                                                            |

|           | 000 = Interrupt is disabled                                                                              |

| bit 1-0   | IS0<1:0>: Interrupt Subpriority bits                                                                     |

|           | 11 = Interrupt subpriority is 3                                                                          |

|           | 10 = Interrupt subpriority is 2                                                                          |

|           | 01 = Interrupt subpriority is 1                                                                          |

|           | 00 = Interrupt subpriority is 0                                                                          |

| Nut       |                                                                                                          |

| Note:     | This register represents a generic definition of the IPCx register. Refer to Table 7-2 for the exact bit |

|           | definitions.                                                                                             |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 |                   |                   |                   | _                 |                   |                  | —                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHSSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |

#### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL x SOURCE SIZE REGISTER

# Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

#### **REGISTER 10-13: DCHxDSIZ: DMA CHANNEL x DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 |                   | —                 | —                 | _                 | —                 |                  | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-0 **CHDSIZ<15:0>:** Channel Destination Size bits

111111111111111 = 65,535 byte destination size  $\ensuremath{\cdot}$

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | _                 | _                 |                   | —                 |                   |                  | —                |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | _                 | _                 | —                 | —                 | _                 | _                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | CHCSIZ<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 10-16: DCHxCSIZ: DMA CHANNEL x CELL-SIZE REGISTER

# Legend:

| Legenu.                         |                  |                                    |                    |  |  |  |

|---------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR               | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

111111111111111 = 65,535 bytes transferred on an event

#### REGISTER 10-17: DCHxCPTR: DMA CHANNEL x CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 |                   |                   | _                 | —                 | —                | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | CHCPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   |                   |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |

| 7.0          | DMA8IF            | DMA7IF            | DMA6IF            | DMA5IF            | DMA4IF            | DMA3IF            | DMA2IF           | DMA1IF           |

#### REGISTER 11-20: USBDMAINT: USB DMA INTERRUPT REGISTER

#### Legend:

| 3                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **DMAxIF:** DMA Channel 'x' Interrupt bit

1 = The DMA channel has an interrupt event

0 = No interrupt event

All bits are cleared on a read of the register.

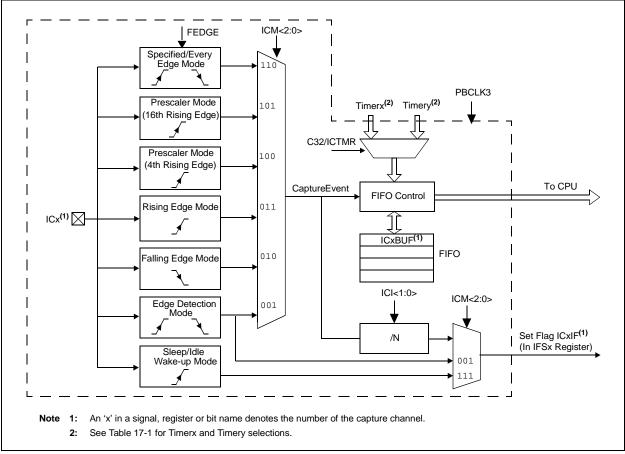

# 17.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin.

Capture events are caused by the following:

• Capture timer value on every edge (rising and falling), specified edge first

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of six 16-bit timers for the time base, or two of six 16-bit timers together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values; Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

# FIGURE 17-1: INPUT CAPTURE BLOCK DIAGRAM

|              | R                 | EGISTER           |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.24        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | U-0              |  |

| 31:24        |                   | _                 | —                 |                   | RXSTATE<3:0>      |                   |                  |                  |  |

| 22:46        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 23:16        |                   |                   | —                 |                   | RXBUFCNT<4:0>     |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         |                   | _                 | —                 | _                 | —                 | _                 | —                | —                |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 7:0          | RXCURBUFLEN<7:0>  |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 20-20: SQI1BDRXDSTAT: SQI BUFFER DESCRIPTOR DMA RECEIVE STATUS REGISTER

## Legend:

| Logonal                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-29 Unimplemented: Read as '0'

- bit 28-25 **RXSTATE<3:0>:** Current DMA Receive State Status bits These bits provide information on the current DMA receive states.

- bit 24-21 Unimplemented: Read as '0'

- bit 20-16 **RXBUFCNT<4:0>:** DMA Buffer Byte Count Status bits These bits provide information on the internal FIFO space.

- bit 15-8 Unimplemented: Read as '0'

- bit 7-0 **RXCURBUFLEN<7:0>:** Current DMA Receive Buffer Length Status bits These bits provide the length of the current DMA receive buffer.

#### REGISTER 20-21: SQI1THR: SQI THRESHOLD CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   |                   | -                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                   |                   | THRES<4:0>        |                  |                  |

| Leaend | : |

|--------|---|

| Logona | • |

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-5 Unimplemented: Read as '0'

bit 4-0 THRES<4:0>: SQI Control Threshold Value bits

The SQI control threshold interrupt is asserted when the amount of space indicated by THRES<4:0> is available in the SQI control buffer.

| REGIST  | TER 23-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)                                                                                     |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6 | CSF<1:0>: Chip Select Function bits <sup>(1)</sup>                                                                                              |

|         | 11 = Reserved                                                                                                                                   |

|         | 10 = PMCS1 and PMCS2 function as Chip Select                                                                                                    |

|         | 01 = PMCS2 functions as Chip Select and PMCS1 functions as address bit 14<br>00 = PMCS1 and PMCS2 function as address bit 14 and address bit 15 |

| 64 C    |                                                                                                                                                 |

| bit 5   | ALP: Address Latch Polarity bit <sup>(1)</sup>                                                                                                  |

|         | <ol> <li>Active-high (PMALL and PMALH)</li> <li>Active-low (PMALL and PMALH)</li> </ol>                                                         |

| bit 4   | <b>CS2P:</b> Chip Select 2 Polarity bit <sup>(1)</sup>                                                                                          |

|         | 1 = Active-high (PMCS2)                                                                                                                         |

|         | $0 = \text{Active-low}(\overline{\text{PMCS2}})$                                                                                                |

| bit 3   | CS1P: Chip Select 1 Polarity bit <sup>(1)</sup>                                                                                                 |

|         | 1 = Active-high (PMCS1)                                                                                                                         |

|         | $0 = \text{Active-low}(\overline{PMCS1})$                                                                                                       |

| bit 2   | Unimplemented: Read as '0'                                                                                                                      |

| bit 1   | WRSP: Write Strobe Polarity bit                                                                                                                 |

|         | For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):                                                                                       |

|         | 1 = Write strobe active-high (PMWR)                                                                                                             |

|         | 0 = Write strobe active-low (PMWR)                                                                                                              |

|         | For Master mode 1 (MODE<1:0> = 11):                                                                                                             |

|         | 1 = Enable strobe active-high (PMENB)<br>0 = Enable strobe active-low (PMENB)                                                                   |

| bit 0   |                                                                                                                                                 |

| DILU    | <b>RDSP:</b> Read Strobe Polarity bit<br>For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):                                              |

|         | 1 = Read Strobe active-high (PMRD)                                                                                                              |

|         | $0 = \text{Read Strobe active-ling}(\underline{(\text{MRD})})$                                                                                  |

|         | For Master mode 1 (MODE<1:0> = 11):                                                                                                             |

|         | 1 = Read/write strobe active-high (PMRD/PMWR)                                                                                                   |

|         | 0 = Read/write strobe active-low (PMRD/PMWR)                                                                                                    |

|         |                                                                                                                                                 |

Note 1: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|------------------------|------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                      | —                      | —                 | _                 | —                 | -                 | -                | —                |  |  |  |

| 00.40        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                      | —                      | —                 | _                 | —                 | —                 | _                | —                |  |  |  |

|              | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | RCS2 <sup>(1)</sup>    | RCS1 <sup>(3)</sup>    | RADDR<13:8>       |                   |                   |                   |                  |                  |  |  |  |

|              | RADDR15 <sup>(2)</sup> | RADDR14 <sup>(4)</sup> |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              | RADDR<7:0>             |                        |                   |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 23-9: PMRADDR: PARALLEL PORT READ ADDRESS REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

# bit 31-16 **Unimplemented:** Read as '0'

| RCS2: Chip Select 2 bit <sup>(1)</sup>                                                                             |

|--------------------------------------------------------------------------------------------------------------------|

| 1 = Chip Select 2 is active                                                                                        |

| 0 = Chip Select 2 is inactive (RADDR15 function is selected)                                                       |

| RADDR<15>: Target Address bit 15 <sup>(2)</sup>                                                                    |

| RCS1: Chip Select 1 bit <sup>(3)</sup>                                                                             |

| <ul><li>1 = Chip Select 1 is active</li><li>0 = Chip Select 1 is inactive (RADDR14 function is selected)</li></ul> |

|                                                                                                                    |

- bit 14 RADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 RADDR<13:0>: Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 0            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   | HR10-             | <3:0>             |                   |                   | HR01              | <3:0>            |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | MIN10             | <3:0>             |                   | MIN01<3:0>        |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | SEC10             | <3:0>             |                   | SEC01<3:0>        |                   |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | —                 | —                 | —                 | —                 | —                 | _                 | —                | —                |  |  |

|              | •                 |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| R = Read     | lable bit         |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |  |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 25-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10 digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1 digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

'1' = Bit is set

-n = Value at POR

# TABLE 28-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                        |           |                        |                        |                        |                        |                        |                        |                           | Bit                    | s                      |                        |                        |                        |                        |                        |                        |                        |                         |

|-----------------------------|------------------------|-----------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|-------------------------|

| Virtual Address<br>(BF84_#) | Register<br>Name       | Bit Range | 31/15                  | 30/14                  | 29/13                  | 28/12                  | 27/11                  | 26/10                  | 25/9                      | 24/8                   | 23/7                   | 22/6                   | 21/5                   | 20/4                   | 19/3                   | 18/2                   | 17/1                   | 16/0                   | All Decete              |

|                             | ADCCMPCON4             | 31:16     |                        | —                      | —                      | —                      | —                      | _                      | _                         | —                      | -                      | -                      | -                      | —                      | —                      | —                      |                        |                        | 00                      |

|                             |                        | 15:0      |                        | —                      | —                      |                        |                        | AINID<4:0>             | •                         |                        | ENDCMP                 | DCMPGIEN               | DCMPED                 | IEBTWN                 | IEHIHI                 | IEHILO                 | IELOHI                 | IELOLO                 | 00                      |

| 30B0                        | ADCCMPCON5             | 31:16     |                        | _                      | _                      | _                      | —                      | —                      | —                         | _                      |                        |                        |                        | —                      | _                      | —                      |                        | _                      | 00                      |

|                             |                        | 15:0      |                        | —                      | —                      |                        |                        | AINID<4:0>             |                           |                        | ENDCMP                 | DCMPGIEN               | DCMPED                 | IEBTWN                 | IEHIHI                 | IEHILO                 | IELOHI                 | IELOLO                 | 00                      |

| 30B4                        | ADCCMPCON6             | 31:16     | _                      | _                      | _                      | _                      | —                      |                        | _                         | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | 00                      |

|                             |                        | 15:0      |                        | —                      | —                      |                        |                        | AINID<4:0>             | •                         |                        | ENDCMP                 | DCMPGIEN               | DCMPED                 | IEBTWN                 | IEHIHI                 | IEHILO                 | IELOHI                 | IELOLO                 | 00                      |

| 30B8                        | ADCFSTAT               | 31:16     | FEN                    | —                      | —                      | ADC4EN                 | ADC3EN                 | ADC2EN                 | ADC1EN                    | ADC0EN                 | FIEN                   | FRDY                   | FWROVERR               | —                      | —                      | —                      |                        | _                      | 00                      |

|                             |                        | 15:0      |                        |                        |                        | FCN                    | T<7:0>                 |                        |                           |                        | FSIGN                  | _                      | _                      | _                      | _                      |                        | ADCID<2:0>             |                        | 00                      |

| 80BC                        | ADCFIFO                | 31:16     |                        |                        |                        |                        |                        |                        |                           | DATA<                  | 31:16>                 |                        |                        |                        |                        |                        |                        |                        | 00                      |

|                             |                        | 15:0      |                        |                        |                        |                        |                        |                        |                           | DATA<                  | 15:0>                  |                        |                        |                        |                        |                        |                        |                        | 00                      |

| 80C0                        | ADCBASE                | 31:16     | —                      | —                      | —                      | —                      | —                      | —                      | -                         | —                      | —                      | _                      | _                      | —                      | —                      | _                      | —                      | —                      | 00                      |

|                             |                        | 15:0      |                        |                        |                        |                        |                        |                        |                           | ADCBAS                 | E<15:0>                |                        |                        |                        |                        |                        |                        |                        | 00                      |

| 0D0                         | ADCTRGSNS              | 31:16     | —                      |                        |                        | _                      | —                      | —                      | _                         | —                      | —                      | —                      | —                      | —                      | —                      |                        | —                      | _                      | 0                       |

|                             |                        | 15:0      | —                      | —                      | —                      | —                      | LVL11                  | LVL10                  | LVL9                      | LVL8                   | LVL7                   | LVL6                   | LVL5                   | LVL4                   | LVL3                   | LVL2                   | LVL1                   | LVL0                   | 0                       |

| 0D4                         | ADC0TIME               | 31:16     | —                      | —                      | —                      |                        | ADCEIS<2:0:            | >                      | SELRE                     | S<1:0>                 | _                      |                        |                        | A                      | DCDIV<6:0>             |                        |                        |                        | 0                       |

|                             |                        | 15:0      | —                      | —                      | —                      | —                      | —                      | —                      | SAMC<9:0>                 |                        |                        |                        |                        |                        | 0                      |                        |                        |                        |                         |

| 0D8                         | ADC1TIME               | 31:16     | —                      | —                      | —                      |                        | ADCEIS<2:0:            | >                      | SELRES<1:0> — ADCDIV<6:0> |                        |                        |                        |                        |                        | 0                      |                        |                        |                        |                         |

|                             |                        | 15:0      | —                      | —                      | —                      | —                      | —                      | —                      | SAMC<9:0>                 |                        |                        |                        |                        | 0                      |                        |                        |                        |                        |                         |

| 0DC                         | ADC2TIME               | 31:16     |                        | -                      | -                      |                        | ADCEIS<2:0>            | >                      | SELRE                     | S<1:0>                 |                        |                        |                        | A                      | DCDIV<6:0>             |                        |                        |                        | 0                       |

|                             |                        | 15:0      |                        | _                      | _                      | _                      | _                      | —                      |                           |                        |                        |                        | SAMC<                  | <9:0>                  |                        |                        |                        |                        | 0                       |

| 80E0                        | ADC3TIME               | 31:16     |                        | _                      | _                      |                        | ADCEIS<2:0>            | >                      | SELRE                     | S<1:0>                 |                        |                        |                        | A                      | DCDIV<6:0>             |                        |                        |                        | 0                       |

|                             |                        | 15:0      |                        | _                      | _                      | _                      | —                      | —                      |                           |                        |                        |                        | SAMC<                  | <9:0>                  |                        |                        |                        |                        | 00                      |

| 80E4                        | ADC4TIME               | 31:16     | -                      | _                      | _                      |                        | ADCEIS<2:0>            | <b>&gt;</b>            | SELRE                     | S<1:0>                 | _                      |                        |                        | A                      | DCDIV<6:0>             |                        |                        |                        | 0                       |

|                             |                        | 15:0      |                        |                        |                        |                        | —                      | —                      |                           | -                      |                        |                        | SAMC<                  |                        |                        | -                      |                        |                        | 00                      |

| 30F0                        | ADCEIEN1               | 31:16     | EIEN31 <sup>(1)</sup>  | EIEN30 <sup>(1)</sup>  | EIEN29 <sup>(1)</sup>  | EIEN28 <sup>(1)</sup>  | EIEN27 <sup>(1)</sup>  | EIEN26 <sup>(1)</sup>  | EIEN25 <sup>(1)</sup>     | EIEN24 <sup>(1)</sup>  | EIEN23 <sup>(1)</sup>  | EIEN22 <sup>(1)</sup>  | EIEN21 <sup>(1)</sup>  | EIEN20 <sup>(1)</sup>  | EIEN19 <sup>(1)</sup>  | EIEN18                 | EIEN17                 | EIEN16                 | 0                       |

|                             |                        | 15:0      | EIEN15                 | EIEN14                 | EIEN13                 | EIEN12                 | EIEN11                 | EIEN10                 | EIEN9                     | EIEN8                  | EIEN7                  | EIEN6                  | EIEN5                  | EIEN4                  | EIEN3                  | EIEN2                  | EIEN1                  | EIEN0                  | 00                      |