Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-LQFP                                                                          |

| Supplier Device Package    | 144-LQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024eff144t-i-pl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). This data sheet contains device-specific information for PIC32MZ EF devices.

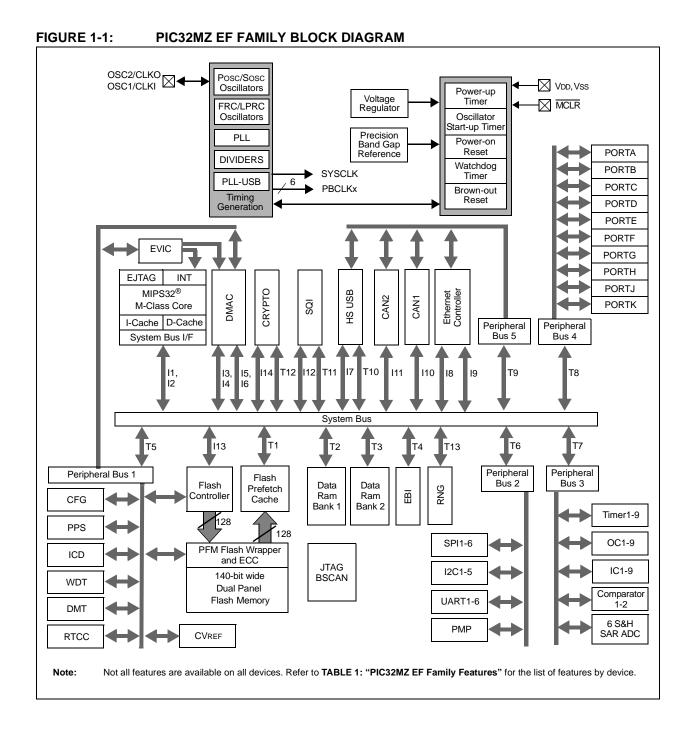

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MZ EF family of devices.

Table 1-21 through Table 1-22 list the pinout I/O descriptions for the pins shown in the device pin tables (see Table 2 through Table 5).

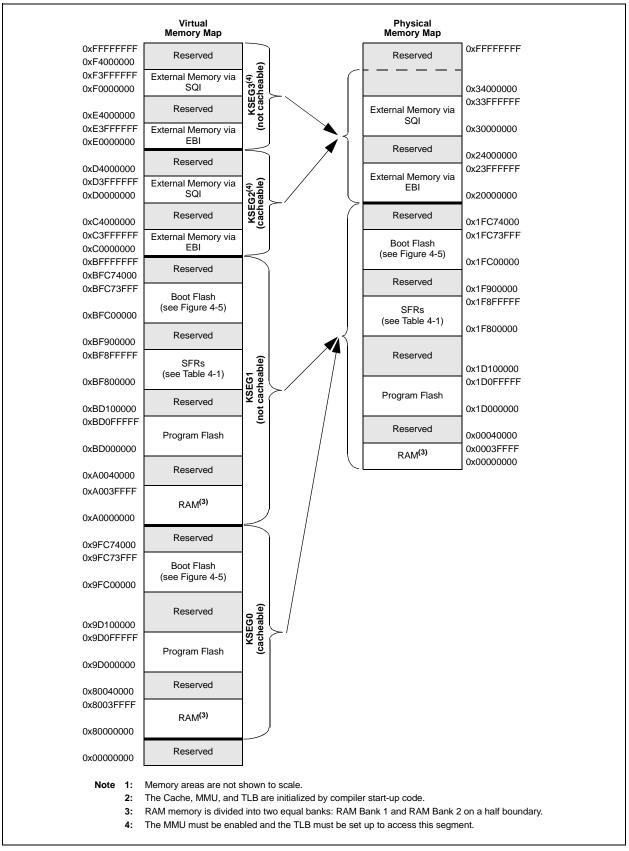

# FIGURE 4-2: MEMORY MAP FOR DEVICES WITH 1024 KB OF PROGRAM MEMORY AND 256 KB OF RAM<sup>(1,2)</sup>

# TABLE 4-6: SYSTEM BUS TARGETS AND ASSOCIATED PROTECTION REGISTERS

|                  |                                                                        |          |                                             | SBTxREC                      | Gy Register                                |                  |                   |                   | SBTxRD  | y Register                                                      | SBTxWRy Register |                                                                  |

|------------------|------------------------------------------------------------------------|----------|---------------------------------------------|------------------------------|--------------------------------------------|------------------|-------------------|-------------------|---------|-----------------------------------------------------------------|------------------|------------------------------------------------------------------|

| Target<br>Number | Target Description <sup>(5)</sup>                                      | Name     | Region Base<br>(BASE<21:0>)<br>(see Note 2) | Physical<br>Start<br>Address | Region Size<br>(SIZE<4:0>)<br>(see Note 3) | Region<br>Size   | Priority<br>(PRI) | Priority<br>Level | Name    | Read<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) | Name             | Write<br>Permissior<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) |

| <u>^</u>         | System Bus                                                             | SBT0REG0 | R                                           | 0x1F8F0000                   | R                                          | 64 KB            | —                 | 0                 | SBT0RD0 | R/W <sup>(1)</sup>                                              | SBT0WR0          | R/W <sup>(1)</sup>                                               |

| 0                |                                                                        | SBT0REG1 | R                                           | 0x1F8F8000                   | R                                          | 32 KB            | —                 | 3                 | SBT0RD1 | R/W <sup>(1)</sup>                                              | SBT0WR1          | R/W <sup>(1)</sup>                                               |

|                  | Flash Memory <sup>(6)</sup> :                                          | SBT1REG0 | R                                           | 0x1D000000                   | R <sup>(4)</sup>                           | R <sup>(4)</sup> | —                 | 0                 | SBT1RD0 | R/W <sup>(1)</sup>                                              | SBT1WR0          | 0, 0, 0, 0                                                       |

|                  | Program Flash<br>Boot Flash                                            | SBT1REG2 | R                                           | 0x1F8E0000                   | R                                          | 4 KB             | 1                 | 2                 | SBT1RD2 | R/W <sup>(1)</sup>                                              | SBT1WR2          | R/W <sup>(1)</sup>                                               |

|                  | Prefetch Module                                                        | SBT1REG3 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD3 | R/W <sup>(1)</sup>                                              | SBT1WR3          | 0, 0, 0, 0                                                       |

| 4                |                                                                        | SBT1REG4 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD4 | R/W <sup>(1)</sup>                                              | SBT1WR4          | 0, 0, 0, 0                                                       |

| 1                |                                                                        | SBT1REG5 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD5 | R/W <sup>(1)</sup>                                              | SBT1WR5          | 0, 0, 0, 0                                                       |

|                  |                                                                        | SBT1REG6 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD6 | R/W <sup>(1)</sup>                                              | SBT1WR6          | 0, 0, 0, 0                                                       |

|                  |                                                                        | SBT1REG7 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT1RD7 | R/W <sup>(1)</sup>                                              | SBT1WR7          | 0, 0, 0, 0                                                       |

|                  |                                                                        | SBT1REG8 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT1RD8 | R/W <sup>(1)</sup>                                              | SBT1WR8          | 0, 0, 0, 0                                                       |

|                  | RAM Bank 1 Memory                                                      | SBT2REG0 | R                                           | 0x00000000                   | R <sup>(4)</sup>                           | R <sup>(4)</sup> | _                 | 0                 | SBT2RD0 | R/W <sup>(1)</sup>                                              | SBT2WR0          | R/W <sup>(1)</sup>                                               |

| 2                |                                                                        | SBT2REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | —                 | 3                 | SBT2RD1 | R/W <sup>(1)</sup>                                              | SBT2WR1          | R/W <sup>(1)</sup>                                               |

|                  |                                                                        | SBT2REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT2RD2 | R/W <sup>(1)</sup>                                              | SBT2WR2          | R/W <sup>(1)</sup>                                               |

|                  | RAM Bank 2 Memory                                                      | SBT3REG0 | R <sup>(4)</sup>                            | R <sup>(4)</sup>             | R <sup>(4)</sup>                           | R <sup>(4)</sup> | —                 | 0                 | SBT3RD0 | R/W <sup>(1)</sup>                                              | SBT3WR0          | R/W <sup>(1)</sup>                                               |

| 3                |                                                                        | SBT3REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | —                 | 3                 | SBT3RD1 | R/W <sup>(1)</sup>                                              | SBT3WR1          | R/W <sup>(1)</sup>                                               |

|                  |                                                                        | SBT3REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT3RD2 | R/W <sup>(1)</sup>                                              | SBT3WR2          | R/W <sup>(1)</sup>                                               |

| 4                | External Memory via EBI and EBI Module <sup>(6)</sup>                  | SBT4REG0 | R                                           | 0x20000000                   | R                                          | 64 MB            | —                 | 0                 | SBT4RD0 | R/W <sup>(1)</sup>                                              | SBT4WR0          | R/W <sup>(1)</sup>                                               |

| 4                | Module                                                                 | SBT4REG2 | R                                           | 0x1F8E1000                   | R                                          | 4 KB             | 0                 | 1                 | SBT4RD2 | R/W <sup>(1)</sup>                                              | SBT4WR2          | R/W <sup>(1)</sup>                                               |

|                  | Peripheral Set 1:<br>System Control                                    | SBT5REG0 | R                                           | 0x1F800000                   | R                                          | 128 KB           | _                 | 0                 | SBT5RD0 | R/W <sup>(1)</sup>                                              | SBT5WR0          | R/W <sup>(1)</sup>                                               |

|                  | Flash Control                                                          | SBT5REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | —                 | 3                 | SBT5RD1 | R/W <sup>(1)</sup>                                              | SBT5WR1          | R/W <sup>(1)</sup>                                               |

| 5                | DMT/WDT<br>RTCC<br>CVR<br>PPS Input<br>PPS Output<br>Interrupts<br>DMA | SBT5REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT5RD2 | R/W <sup>(1)</sup>                                              | SBT5WR2          | R/W <sup>(1)</sup>                                               |

**Note** 1: Reset values for these bits are '0', '1', '1', '1', respectively.

2: The BASE<21:0> bits must be set to the corresponding Physical Address and right shifted by 10 bits. For Read-only bits, this value is set by hardware on Reset.

3: The SIZE<4:0> bits must be set to the corresponding Region Size, based on the following formula: Region Size = 2<sup>(SIZE-1)</sup> x 1024 bytes. For read-only bits, this value is set by hardware on Reset.

4: Refer to the Device Memory Maps (Figure 4-1 through Figure 4-4) for specific device memory sizes and start addresses.

5: See Table 4-1for information on specific target memory size and start addresses.

6: The SBTxREG1 SFRs are reserved, and therefore, are not listed in this table for this target.

# 7.0 CPU EXCEPTIONS AND INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108) and Section 50. "CPU MIPS32<sup>®</sup> for Devices with microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

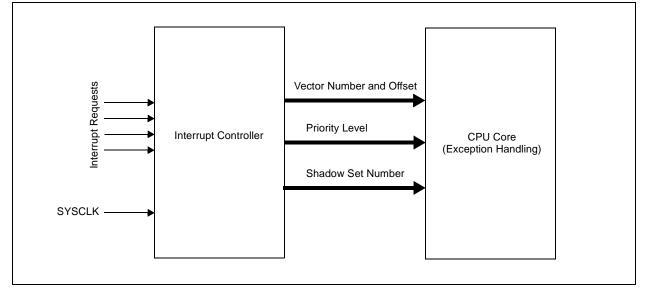

PIC32MZ EF devices generate interrupt requests in response to interrupt events from peripheral modules. The Interrupt Controller module exists outside of the CPU and prioritizes the interrupt events before presenting them to the CPU.

The CPU handles interrupt events as part of the exception handling mechanism, which is described in **Section 7.1 "CPU Exceptions"**.

The Interrupt Controller module includes the following features:

- Up to 213 interrupt sources and vectors with dedicated programmable offsets, eliminating the need for redirection

- · Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Seven shadow register sets that can be used for any priority level, eliminating software context switch and reducing interrupt latency

- Software can generate any interrupt

Figure 7-1 shows the block diagram for the Interrupt Controller and CPU exceptions.

# FIGURE 7-1: CPU EXCEPTIONS AND INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>)                   | _                               | Ð         |       |       |       |       |                               |       |          | Bi                     | ts   |      |      |                             |             |                     |                       |                       | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------------------------|-------|----------|------------------------|------|------|------|-----------------------------|-------------|---------------------|-----------------------|-----------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                         | 26/10 | 25/9     | 24/8                   | 23/7 | 22/6 | 21/5 | 20/4                        | 19/3        | 18/2                | 17/1                  | 16/0                  | All Resets |

|                             | BOOG                            | 31:16     | _     | _     | _     |       | CRPTIP<2:0>                   | (7)   | CRPTIS   | <1:0>(7)               | _    | —    | -    |                             | SBIP<2:0>   |                     | SBIS                  | <1:0>                 | 0000       |

| 02E0                        | PC26                            | 15:0      | _     | _     | _     |       | CFDCIP<2:0                    | >     | CFDCIS   | S<1:0>                 | _    | _    | -    | CPCIP<2:0>                  |             | CPCIS               | S<1:0>                | 0000                  |            |

| 02F0                        | 0007                            | 31:16     | _     | _     | _     |       | SPI1TXIP<2:0                  | )>    | SPI1TXI  | S<1:0>                 | _    | _    | _    |                             | SPI1RXIP<2: | 0>                  | SPI1RX                | IS<1:0>               | 0000       |

| 02F0                        | PC27                            | 15:0      | _     | _     | _     |       | SPI1EIP<2:0>                  |       | SPI1EIS  | S<1:0>                 | _    | —    | _    | _                           | _           | _                   | _                     | _                     | 0000       |

| 0300                        | 0000                            | 31:16     | _     | _     | _     |       | I2C1BIP<2:0                   | >     | I2C1BIS  | S<1:0>                 | _    | —    | _    |                             | U1TXIP<2:0  | >                   | U1TXI                 | S<1:0>                | 0000       |

| 0300                        | PC20                            | 15:0      | _     | _     | _     |       | U1RXIP<2:0>                   |       | U1RXIS   | 6<1:0>                 | _    | _    | _    |                             | U1EIP<2:0:  | >                   | U1EIS                 | S<1:0>                | 0000       |

| 0040                        | DOOD                            | 31:16     | _     | _     | _     |       | CNBIP<2:0>                    |       | CNBIS    | <1:0>                  | _    | —    | _    |                             | CNAIP<2:0>  | (2)                 | CNAIS                 | <1:0> <b>(2)</b>      | 0000       |

| 0310                        | PC29                            | 15:0      | _     | _     | _     |       | I2C1MIP<2:0                   | >     | I2C1MI   | S<1:0>                 | _    | —    | _    |                             | I2C1SIP<2:0 | )>                  | I2C1SI                | S<1:0>                | 0000       |

| 0320                        | BC20                            | 31:16     | —     | _     | _     |       | CNFIP<2:0>                    |       | CNFIS    | <1:0>                  | _    | —    |      |                             | CNEIP<2:0   | >                   | CNEIS                 | S<1:0>                | 0000       |

| 0320                        | FC30                            | 15:0      | —     | —     | —     |       | CNDIP<2:0>                    |       | CNDIS    | <1:0>                  |      | —    | -    |                             | CNCIP<2:0   | >                   | CNCIS                 | 6<1:0>                | 0000       |

| 0330                        | DC21                            | 31:16     | —     | _     | _     | C     | CNKIP<2:0> <sup>(2,4,8)</sup> |       | CNKIS<1  | :0> <sup>(2,4,8)</sup> | —    | —    |      | CNJIP<2:0> <sup>(2,4)</sup> |             | CNJIS<              | 1:0> <sup>(2,4)</sup> | 0000                  |            |

| 0330                        | FC31                            | 15:0      | —     | _     | _     | (     | CNHIP<2:0> <sup>(2,4)</sup>   |       | CNHIS<   | 1:0> <sup>(2,4)</sup>  | _    | —    |      | CNGIP<2:0>                  |             | CNGIS               | S<1:0>                | 0000                  |            |

| 0340                        | BC22                            | 31:16     | _     | _     | _     |       | CMP2IP<2:0>                   |       | CMP2IS   | S<1:0>                 | —    | _    |      | CMP1IP<2:0>                 |             | CMP1I               | S<1:0>                | 0000                  |            |

| 0340                        | F032                            | 15:0      | —     | —     | _     |       | PMPEIP<2:0>                   |       | PMPEIS   | S<1:0>                 | _    | —    |      | PMPIP<2:0>                  |             | PMPIS               | S<1:0>                | 0000                  |            |

| 0350                        | 0022                            | 31:16     | —     | _     | _     |       | DMA1IP<2:0                    | >     | DMA1IS   | S<1:0>                 | _    | —    |      |                             | DMA0IP<2:0  | )>                  | DMA0I                 | S<1:0>                | 0000       |

| 0350                        | FC33                            | 15:0      | _     | _     | _     | ι     | JSBDMAIP<2:                   | 0>    | USBDMA   | JS<1:0>                | —    | _    |      |                             | USBIP<2:0   | >                   | USBIS                 | S<1:0>                | 0000       |

| 0360                        | DC24                            | 31:16     | —     | —     | —     |       | DMA5IP<2:0                    | >     | DMA5IS   | S<1:0>                 | —    | _    |      |                             | DMA4IP<2:0  | )>                  | DMA4I                 | S<1:0>                | 0000       |

| 0300                        | FC34                            | 15:0      | —     | —     | —     |       | DMA3IP<2:0                    | >     | DMA3IS   | S<1:0>                 | _    | —    | _    |                             | DMA2IP<2:0  | )>                  | DMA2I                 | S<1:0>                | 0000       |

| 0370                        | DC25                            | 31:16     | —     | _     | _     |       | SPI2RXIP<2:(                  | )>    | SPI2RXI  | S<1:0>                 | _    | —    |      |                             | SPI2EIP<2:0 | )>                  | SPI2EI                | S<1:0>                | 0000       |

| 0370                        | FC35                            | 15:0      | —     | —     | _     |       | DMA7IP<2:0                    | >     | DMA7IS   | S<1:0>                 | _    | —    |      |                             | DMA6IP<2:0  | )>                  | DMA6I                 | S<1:0>                | 0000       |

| 0380                        | DC26                            | 31:16     | —     | —     | —     |       | U2TXIP<2:0:                   | >     | U2TXIS   | S<1:0>                 | _    | —    | _    |                             | U2RXIP<2:0  | )>                  | U2RXI                 | S<1:0>                | 0000       |

| 0360                        | FC30                            | 15:0      | —     | _     | _     |       | U2EIP<2:0>                    |       | U2EIS    |                        | _    | —    |      | :                           | SPI2TXIP<2: | 0>                  | SPI2TX                | IS<1:0>               | 0000       |

| 0390                        | 0007                            | 31:16     | —     | —     | _     |       | CAN1IP<2:0>                   | (3)   | CAN1IS-  | <1:0> <sup>(3)</sup>   | _    | —    |      | Ľ                           | 2C2MIP<2:0: | >(2)                | I2C2MIS               | S<1:0> <b>(2)</b>     | 0000       |

| 0390                        | PC37                            | 15:0      | —     | _     | _     | I     | 2C2SIP<2:0>                   | (2)   | I2C2SIS- | <1:0> <sup>(2)</sup>   | _    | —    |      | I                           | 2C2BIP<2:0; | _(2)                | I2C2BIS               | i<1:0> <sup>(2)</sup> | 0000       |

| 03A0                        | 0020                            | 31:16     | _     | _     | _     |       | SPI3RXIP<2:0                  | )>    | SPI3RXI  | S<1:0>                 | —    | _    |      |                             | SPI3EIP<2:0 | )>                  | SPI3EI                | S<1:0>                | 0000       |

| 0340                        | FC30                            | 15:0      | _     | _     | _     |       | ETHIP<2:0>                    |       | ETHIS    | <1:0>                  | —    | _    |      | (                           | CAN2IP<2:0> | <sub>&gt;</sub> (3) | CAN2IS                | <1:0> <sup>(3)</sup>  | 0000       |

| 03B0                        | PC 30                           | 31:16     | —     | _     |       |       | U3TXIP<2:0>                   |       | U3TXIS   | S<1:0>                 | _    | —    |      |                             | U3RXIP<2:0  | )>                  | U3RXI                 | S<1:0>                | 0000       |

| 0360                        | 1 0 3 9                         | 15:0      | —     | _     | —     |       | U3EIP<2:0>                    |       | U3EIS    | <1:0>                  | _    | —    |      |                             | SPI3TXIP<2: | 0>                  | SPI3TX                | IS<1:0>               | 0000       |

| 0200                        |                                 | 31:16     | —     | _     |       |       | SPI4EIP<2:0>                  |       | SPI4EIS  | S<1:0>                 | _    | _    |      | I2C3MIP<2:0>                |             | I2C3M               | S<1:0>                | 0000                  |            |

| 03C0                        | F 0 40                          | 15:0      | —     | _     | _     |       | I2C3SIP<2:0                   | >     | 12C3SI   | S<1:0>                 | _    | _    |      |                             | I2C3BIP<2:0 | )>                  | I2C3BI                | S<1:0>                | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

- Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

- Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

# **REGISTER 7-2:** PRISS: PRIORITY SHADOW SELECT REGISTER (CONTINUED) bit 15-12 PRI3SS<3:0>: Interrupt with Priority Level 3 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 3 uses Shadow Set 0) 0111 = Interrupt with a priority level of 3 uses Shadow Set 7 0110 = Interrupt with a priority level of 3 uses Shadow Set 6 0001 = Interrupt with a priority level of 3 uses Shadow Set 1 0000 = Interrupt with a priority level of 3 uses Shadow Set 0 bit 11-8 **PRI2SS<3:0>:** Interrupt with Priority Level 2 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 2 uses Shadow Set 0) 0111 = Interrupt with a priority level of 2 uses Shadow Set 7 0110 = Interrupt with a priority level of 2 uses Shadow Set 6 0001 = Interrupt with a priority level of 2 uses Shadow Set 1 0000 = Interrupt with a priority level of 2 uses Shadow Set 0 PRI1SS<3:0>: Interrupt with Priority Level 1 Shadow Set bits<sup>(1)</sup> bit 7-4 1xxx = Reserved (by default, an interrupt with a priority level of 1 uses Shadow Set 0) 0111 = Interrupt with a priority level of 1 uses Shadow Set 7 0110 = Interrupt with a priority level of 1 uses Shadow Set 6 0001 = Interrupt with a priority level of 1 uses Shadow Set 1 0000 = Interrupt with a priority level of 1 uses Shadow Set 0 bit 3-1 Unimplemented: Read as '0' bit 0 SS0: Single Vector Shadow Register Set bit 1 = Single vector is presented with a shadow set 0 = Single vector is not presented with a shadow set

**Note 1:** These bits are ignored if the MVEC bit (INTCON<12>) = 0.

|              | -                 |                   |                   |                   |                     |                   | - (                   | ,                     |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-----------------------|-----------------------|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |  |  |  |  |  |

| 31:24        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0                 | R/W-0                 |  |  |  |  |  |

| 31.24        | —                 | — RODIV<14:8>     |                   |                   |                     |                   |                       |                       |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0                 | R/W-0                 |  |  |  |  |  |

| 23.10        | RODIV<7:0>        |                   |                   |                   |                     |                   |                       |                       |  |  |  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC             | R-0, HS, HC           |  |  |  |  |  |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | OE                | RSLP <sup>(2)</sup> | —                 | DIVSWEN               | ACTIVE <sup>(1)</sup> |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0                 | R/W-0                 |  |  |  |  |  |

| 7:0          | _                 | _                 |                   |                   |                     | ROSEL             | -<3:0> <sup>(3)</sup> |                       |  |  |  |  |  |

#### **REGISTER 8-4: REFOXCON: REFERENCE OSCILLATOR CONTROL REGISTER ('x' = 1-4)**

| Legend:           | HC = Hardware Cleared | HS = Hardware Set      |                    |

|-------------------|-----------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 Unimplemented: Read as '0' bit 30-16 RODIV<14:0> Reference Clock Divider bits

The value selects the reference clock divider bits (see Figure 8-1 for details). A value of '0' selects no divider.

bit 15 **ON:** Output Enable bit<sup>(1)</sup>

- 1 = Reference Oscillator module is enabled

- 0 =Reference Oscillator module is disabled

- bit 14 **Unimplemented:** Read as '0'

- bit 13 **SIDL:** Peripheral Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 12 **OE:** Reference Clock Output Enable bit 1 = Reference clock is driven out on REFCLKOx pin

- 0 = Reference clock is not driven out on REFCLKOx pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit<sup>(1)</sup>

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

### bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(3)</sup>

- 1111 = Reserved

- - •

- 1001 = BFRC 1000 = REFCLKIx

- 0111 = System PLL output

- 0110 = Reserved

- 0101 = Sosc

- 0100 = LPRC

- 0011 = FRC

- 0010 = Posc 0001 = PBCLK1

- 0000 = SYSCLK

# **Note 1:** Do not write to this register when the ON bit is not equal to the ACTIVE bit.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: The ROSEL<3:0> bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

# TABLE 12-7: PORTC REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 | <i><b>a</b></i> |           |           |           |           |                |       | I    | Bits |      |      |      |      |      |      |      |      |               |

|-----------------------------|---------------------------------|-----------------|-----------|-----------|-----------|-----------|----------------|-------|------|------|------|------|------|------|------|------|------|------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range       | 31/15     | 30/14     | 29/13     | 28/12     | 27/11          | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All<br>Resets |

| 0210                        | TRISC                           | 31:16           | —         |           | —         |           |                |       |      | _    |      |      |      |      | —    | —    | -    |      | 0000          |

| 0210                        |                                 | 15:0            | TRISC15   | TRISC14   | TRISC13   | TRISC12   | _              | —     | -    | —    | —    | —    | _    | —    | —    | —    | —    | —    | F000          |

| 0220                        | PORTC                           | 31:16           | —         |           | —         | —         | -              | _     | _    | _    | —    | —    | _    | _    | _    | -    |      | _    | 0000          |

| 0220                        |                                 | 15:0            | RC15      | RC14      | RC13      | RC12      | —              | —     | —    | —    | —    | —    | _    | —    | _    | —    | _    | —    | xxxx          |

| 0230                        | LATC                            | 31:16           | —         | _         | —         | —         | —              | —     | _    | —    | —    | —    | —    | _    | —    | —    | _    |      | 0000          |

|                             |                                 | 15:0            | LATC15    | LATC14    | LATC13    | LATC12    | _              | _     |      |      | —    | —    | _    |      |      | —    |      |      | XXXX          |

| 0240                        | ODCC                            | 31:16           | —         | _         | —         | _         | _              | _     |      |      | —    | —    | _    |      |      | —    |      |      | 0000          |

|                             |                                 | 15:0            | ODCC15    | ODCC14    | ODCC13    | ODCC12    | _              | —     | —    | —    | _    | _    | —    | —    | —    | —    | —    | —    | XXXX          |

| 0250                        | CNPUC                           | 31:16           | —         | —         | —         | —         | _              | _     | _    | —    | _    | _    | _    | _    | —    | _    | _    | —    | 0000          |

|                             |                                 | 15:0            | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | _              | _     | _    | —    | _    | _    | _    | _    | —    | _    | _    | —    | 0000          |

| 0260                        | CNPDC                           | 31:16           | _         |           | _         |           | _              | _     | _    | _    | _    | _    | _    | _    | _    | _    | —    | _    | 0000          |

|                             |                                 | 15:0            | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | -              | _     | _    | —    | _    | _    | _    | _    | _    | _    | _    |      | 0000          |

| 0070                        |                                 | 31:16           | —         | —         | _         | _         | -              | _     | _    | —    | _    | _    | _    | _    | _    | _    | _    |      | 0000          |

| 0270                        | CNCONC                          | 15:0            | ON        | —         | —         | —         | EDGE<br>DETECT | —     |      | —    | -    | -    | —    |      | —    | —    | -    | —    | 0000          |

| 0280                        | CNENC                           | 31:16           | _         | _         | —         | _         | —              | —     | —    | —    | —    | —    | —    | —    | —    | —    | _    | —    | 0000          |

| 0200                        | CINEINO                         | 15:0            | CNENC15   | CNENC14   | CNENC13   | CNENC12   |                |       |      |      |      |      |      |      |      |      |      |      | 0000          |

| 0290                        | CNSTATC                         | 31:16           | —         | —         | —         | —         | —              | —     | _    | —    | —    | —    | _    | _    | —    | —    |      | —    | 0000          |

| 0200                        |                                 | 15:0            | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | —              | —     | _    | —    | —    | —    | _    | _    | —    | —    |      | —    | 0000          |

| 02A0                        | CNNEC                           | 31:16           | —         | _         |           | —         | —              | —     | _    | —    | —    | —    | —    | _    | —    | —    | —    | —    | 0000          |

| 02AU                        | ONNEO                           | 15:0            | CNNEC15   | CNNEC14   | CNNEC13   | CNNEC12   | —              | —     | _    | —    | —    | —    | _    | _    |      | —    |      | —    | 0000          |

| 02B0                        | CNFC                            | 31:16           | —         | _         | —         | —         | —              | —     | _    | —    | —    | —    | —    | —    | —    | —    | —    | —    | 0000          |

| 02D0                        |                                 | 15:0            | CNFC15    | CNFC14    | CNFC13    | CNFC12    | —              | —     | —    | _    | -    | -    | _    | —    | _    | —    | —    |      | 0000          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24     | —                    | —                 | —                 | —                 | —                 | _                 | _                | _                |  |

| 00.40     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16     | —                    | —                 | —                 | —                 | —                 | _                 | _                | _                |  |

| 45.0      | R/W-0                | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |

| 15:8      | ON                   | —                 | SIDL              | —                 | —                 | _                 | FEDGE            | C32              |  |

| 7.0       | R/W-0                | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0       | ICTMR <sup>(1)</sup> | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |  |

# REGISTER 17-1: ICXCON: INPUT CAPTURE X CONTROL REGISTER

# Legend:

| R = Readabl   | le bit W = Writable bit                                                                                             | U = Unimplemented bit                                      |

|---------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| -n = Bit Valu | e at POR: ('0', '1', x = unknown)                                                                                   | P = Programmable bit r = Reserved bit                      |

| 1 :: 04 40    |                                                                                                                     |                                                            |

| bit 31-16     | Unimplemented: Read as '0'                                                                                          |                                                            |

| bit 15        | <b>ON:</b> Input Capture Module Enable bit                                                                          |                                                            |

|               | 1 = Module is enabled                                                                                               | disable interrupt generation and allow CED modifications   |

| <b>L:</b> 4 4 |                                                                                                                     | , disable interrupt generation and allow SFR modifications |

| bit 14        | Unimplemented: Read as '0'                                                                                          |                                                            |

| bit 13        | SIDL: Stop in Idle Control bit                                                                                      |                                                            |

|               | 1 = Halt in CPU Idle mode                                                                                           |                                                            |

| 1 1 40 40     | 0 = Continue to operate in CPU Idle mode                                                                            |                                                            |

| bit 12-10     | Unimplemented: Read as '0'                                                                                          |                                                            |

| bit 9         | FEDGE: First Capture Edge Select bit (only u                                                                        | used in mode 6, ICM<2:0> = $110$ )                         |

|               | 1 = Capture rising edge first                                                                                       |                                                            |

| L:1.0         | 0 = Capture falling edge first                                                                                      |                                                            |

| bit 8         | <b>C32:</b> 32-bit Capture Select bit                                                                               |                                                            |

|               | 1 = 32-bit timer resource capture                                                                                   |                                                            |

| hit 7         | 0 = 16-bit timer resource capture                                                                                   | r coloction when C22 (ICyCON (9. ) is (1/)(1)              |

| bit 7         | ICTMR: Timer Select bit (Does not affect time                                                                       | er selection when C32 (ICXCON<8>) is 1)(**                 |

|               | <ul><li>0 = Timery is the counter source for capture</li><li>1 = Timerx is the counter source for capture</li></ul> |                                                            |

| bit 6-5       | ICI<1:0>: Interrupt Control bits                                                                                    |                                                            |

| DIL 0-5       | 11 = Interrupt on every fourth capture event                                                                        |                                                            |

|               | 10 = Interrupt on every third capture event<br>10 = Interrupt on every third capture event                          |                                                            |

|               | 01 = Interrupt on every second capture even                                                                         | nt                                                         |

|               | 00 = Interrupt on every capture event                                                                               |                                                            |

| bit 4         | <b>ICOV:</b> Input Capture Overflow Status Flag bit                                                                 | (read-only)                                                |

|               | 1 = Input capture overflow is occurred                                                                              |                                                            |

|               | 0 = No input capture overflow is occurred                                                                           |                                                            |

| bit 3         | ICBNE: Input Capture Buffer Not Empty State                                                                         | us bit (read-only)                                         |

|               | 1 = Input capture buffer is not empty; at least                                                                     |                                                            |

|               | 0 = Input capture buffer is empty                                                                                   | ·                                                          |

| bit 2-0       | ICM<2:0>: Input Capture Mode Select bits                                                                            |                                                            |

|               | 111 = Interrupt-Only mode (only supported v                                                                         | while in Sleep mode or Idle mode)                          |

|               |                                                                                                                     | edge, specified edge first and every edge thereafter       |

|               | 101 = Prescaled Capture Event mode - eve                                                                            |                                                            |

|               | 100 = Prescaled Capture Event mode - eve                                                                            | ry fourth rising edge                                      |

|               | 011 = Simple Capture Event mode – every r                                                                           | ising edge                                                 |

|               | 010 = Simple Capture Event mode – every f                                                                           |                                                            |

|               | 001 = Edge Detect mode – every edge (risin                                                                          | ng and falling)                                            |

|               | 000 = Input Capture module is disabled                                                                              |                                                            |

**Note 1:** Refer to Table 17-1 for Timerx and Timery selections.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | _                 | _                 |                   | —                 |                   |                   | _                | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | _                 |                   | —                 | _                 |                   | _                | _                |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | —                 | —                 | —                 | —                 | DMAEIE            | PKTCOMPIE         | BDDONEIE         | CONTHRIE         |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | CONEMPTYIE        | CONFULLIE         | RXTHRIE           | RXFULLIE          | RXEMPTYIE         | TXTHRIE           | TXFULLIE         | TXEMPTYIE        |  |  |  |  |

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

HS = Hardware Set

W = Writable bit

'1' = Bit is set

# REGISTER 20-8: SQI1INTEN: SQI INTERRUPT ENABLE REGISTER

| bit 31-12     | <b>Unimplemented:</b> Read as '0'                                     |

|---------------|-----------------------------------------------------------------------|

| bit 11        | DMAEIE: DMA Bus Error Interrupt Enable bit                            |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 10        | PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 9         | BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit             |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 8         | CONTHRIE: Control Buffer Threshold Interrupt Enable bit               |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 7         | CONEMPTYIE: Control Buffer Empty Interrupt Enable bit                 |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 6         | CONFULLIE: Control Buffer Full Interrupt Enable bit                   |

|               | This bit enables an interrupt when the receive FIFO buffer is full.   |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 5         | RXTHRIE: Receive Buffer Threshold Interrupt Enable bit                |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 4         | <b>RXFULLIE:</b> Receive Buffer Full Interrupt Enable bit             |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 3         | <b>RXEMPTYIE:</b> Receive Buffer Empty Interrupt Enable bit           |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 2         | TXTHRIE: Transmit Threshold Interrupt Enable bit                      |

|               | 1 = Interrupt is enabled                                              |

| L.1. A        | 0 = Interrupt is disabled                                             |

| bit 1         | TXFULLIE: Transmit Buffer Full Interrupt Enable bit                   |

|               | 1 = Interrupt is enabled                                              |

| <b>h</b> :+ 0 | 0 = Interrupt is disabled                                             |

| bit 0         | <b>TXEMPTYIE:</b> Transmit Buffer Empty Interrupt Enable bit          |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

Legend:

R = Readable bit

-n = Value at POR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4   | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|--------------------|---------------------|---------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                  | —                   | -                   |                   | —                | -                |

| 00.40        | R/W-0, HC         | U-0               | U-0                | U-0                 | U-0                 | U-0               | R/W-0            | U-0              |

| 23:16        | RDSTART           | _                 | —                  | —                   | _                   | —                 | DUALBUF          | _                |

| 45.0         | R/W-0             | U-0               | R/W-0              | R/W-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON                | -                 | SIDL               | ADRML               | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0             | R/W-0              | R/W-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0>(1)           | ALP <sup>(1)</sup> | CS2P <sup>(1)</sup> | CS1P <sup>(1)</sup> |                   | WRSP             | RDSP             |

### REGISTER 23-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

bit 23 RDSTART: Start Read on PMP Bus bit This bit is cleared by hardware at the end of the read cycle. 1 = Start a read cycle on the PMP bus 0 = No effect

bit 22-18 Unimplemented: Read as '0'

bit 17 DUALBUF: Dual Read/Write Buffers enable bit

This bit is valid in Master mode only.

1 = PMP uses separate registers for reads and writes (PMRADDR, PMDATAIN, PMWADDR, PMDATAOUT)

0 = PMP uses legacy registers (PMADDR, PMDATA)

- bit 16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit

1 = PMP is enabled

- 0 = PMP is disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

### bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = Lower 8 bits of address are multiplexed on PMD<15:0> pins; upper 8 bits are not used

- 10 = All 16 bits of address are multiplexed on PMD<15:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port is enabled

- 0 = PMWR/PMENB port is disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port is enabled

- 0 = PMRD/PMWR port is disabled

**Note 1:** These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | -                 | _                 | _                 | _                 | -                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | _                 | _                 | _                 | —                | —                |

| 45-0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | PTEN<             | :15:14>           | PTEN<13:8>        |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | PTEN<7:0>         |                   |                   |                   |                   |                   |                  |                  |

# REGISTER 23-6: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-15 Unimplemented: Read as '0'

- bit 15-14 **PTEN<15:14>:** PMCS1 Strobe Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS1 and PMCS2<sup>(1)</sup>

0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits

- 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 PTEN<1:0>: PMALH/PMALL Strobe Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15 and PMA14 or CS1 and CS2 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R-0, HS, HC       | R/W-0             | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | TRBEN             | TRBERR            | 7                 | TRBMST<2:0> TRBSLV<2:0> |                   |                   |                  |                  |

| 00.40        | R/W-0             | R/W-1             | R/W-1             | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FRACT             | SELRES            | S<1:0>            |                         | STRGSRC<4:0>      |                   |                  |                  |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-1                   | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 15:8         | ON                |                   | SIDL              | AICPMPEN                | CVDEN             | FSSCLKEN          | FSPBCLKEN        | —                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | U-0               | U-0              | U-0              |

| 7:0          | _                 |                   | IRQVS<2:0>        |                         | STRGLVL           | —                 | _                |                  |

#### REGISTER 28-1: ADCCON1: ADC CONTROL REGISTER 1

| Legend:           | HC = Hardware Set | HS = Hardware Cleared  |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown |

The status of this bit is valid only after the TRBEN bit is set.

1 = An error occurred while setting the Turbo channel and Turbo channel function to be disabled regardless

| • |

|---|

| • |

111 = Reserved

Note:

111 = Reserved

bit 31

bit 30

- 000 = ADC0 is selected as the Turbo Slave

- bit 23 FRACT: Fractional Data Output Format bit

**TRBEN:** Turbo Channel Enable bit 1 = Enable the Turbo channel 0 = Disable the Turbo channel

bit 29-27 TRBMST<2:0>: Turbo Master ADCx bits

bit 26-24 TRBSLV<2:0>: Turbo Slave ADCx bits

TRBERR: Turbo Channel Error Status bit

of the TRBEN bit being set to '1'. 0 = Turbo channel error did not occur

110 = ADC4 is selected as the Turbo Master

000 = ADC0 is selected as the Turbo Master

110 = ADC4 is selected as the Turbo Slave

- 1 = Fractional

- 0 = Integer

- bit 22-21 SELRES<1:0>: Shared ADC (ADC7) Resolution bits

- 11 = 12 bits (default)

- 10 = 10 bits

- 01 = 8 bits

- 00 = 6 bits

- **Note:** Changing the resolution of the ADC does not shift the result in the corresponding ADCDATAx register. The result will still occupy 12 bits, with the corresponding lower unused bits set to '0'. For example, a resolution of 6 bits will result in ADCDATAx<5:0> being set to '0', and ADCDATAx<11:6> holding the result.

| REGISTER 28-6: | ADCIMCON2: ADC INPUT MODE CONTROL REGISTER 2 (CONTINUED) |

|----------------|----------------------------------------------------------|

|----------------|----------------------------------------------------------|

| bit 6 | SIGN19: AN19 Signed Data Mode bit <sup>(1)</sup> |

|-------|--------------------------------------------------|

|       | 1 = AN19 is using Signed Data mode               |

|       | 0 = AN19 is using Unsigned Data mode             |

| bit 5 | DIFF18: AN18 Mode bit                            |

|       | 1 = AN18 is using Differential mode              |

|       | 0 = AN18 is using Single-ended mode              |

| bit 4 | SIGN18: AN18 Signed Data Mode bit                |

|       | 1 = AN18 is using Signed Data mode               |

|       | 0 = AN18 is using Unsigned Data mode             |

| bit 3 | DIFF17: AN17 Mode bit                            |

|       | 1 = AN17 is using Differential mode              |

|       | 0 = AN17 is using Single-ended mode              |

| bit 2 | SIGN17: AN17 Signed Data Mode bit                |

|       | 1 = AN17 is using Signed Data mode               |

|       | 0 = AN17 is using Unsigned Data mode             |

| bit 1 | DIFF16: AN16 Mode bit                            |

|       | 1 = AN16 is using Differential mode              |

|       | 0 = AN16 is using Single-ended mode              |

| bit 0 | SIGN16: AN16 Signed Data Mode bit                |

|       | 1 = AN16 is using Signed Data mode               |

|       | 0 = AN16 is using Unsigned Data mode             |

|       |                                                  |

Note 1: This bit is not available on 64-pin devices.

NOTES:

# 39.0 252 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MZ EF electrical characteristics for devices running at 252 MHz. Additional information will be provided in future revisions of this document as it becomes available.

The specifications for 252 MHz are identical to those shown in **37.0** "Electrical Characteristics" including absolute maximum ratings, with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 252 MHz operation. For example, parameter DC27a in **37.0** "Electrical Characteristics", is the up to 200 MHz operation equivalent for MDC27a.

NOTES:

# Revision D (July 2016)

This revision includes the following major changes, which are referenced by their respective chapter in Table C-3.

In addition, minor updates to text and formatting were incorporated throughout the document.

| TABLE C-3: MAJOR SECTIO | N UPDATES |

|-------------------------|-----------|

|-------------------------|-----------|

| Section Name                                                                                                                                           | Update Description                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 32-bit MCUs (up to 2 MB Live-<br>Update Flash and 512 KB SRAM)<br>with FPU, Audio and Graphics<br>Interfaces, HS USB, Ethernet,<br>and Advanced Analog | Updated the Operating Conditions and Core MHz values.<br>The XFBGA package was renamed to TFBGA.                              |

| 20.0 "Serial Quad Interface<br>(SQI)"                                                                                                                  | The CLKDIV<9:0> bits in the SQI1CLKCON register were updated (see Register 20-5).                                             |

|                                                                                                                                                        | The THRES<4:0> bits in the SQI1THR register were updated (see Register 20-21).                                                |

| 37.0 "Electrical Characteristics"                                                                                                                      | The Program Flash Memory Wait States were updated (see Table 37-13).                                                          |

|                                                                                                                                                        | The minimum value for System Time Requirements parameter OS51 (when the USB module is enabled) was updated (see Table 37-18). |

| 39.0 "252 MHz Electrical<br>Characteristics"                                                                                                           | This chapter was added.                                                                                                       |

| Appendix A: "Migrating from<br>PIC32MX5XX/6XX/7XX to                                                                                                   | The new ADC module reference was updated (see <b>A.2</b> "Analog-to-Digital <b>Converter (ADC)</b> ").                        |

| PIC32MZ EF"                                                                                                                                            | ADC Calibration was added to B.2 "Analog-to-Digital Converter (ADC)"                                                          |

| Appendix B: "Migrating from<br>PIC32MZ EC to PIC32MZ EF"                                                                                               | The Device Configuration and Control Differences (Table B-8) were updated to include the Boot Flash Sequence.                 |

|                                                                                                                                                        | B.10 "Serial Quad Interface (SQI)" was updated.                                                                               |

| Product Identification System                                                                                                                          | The Speed category was added.                                                                                                 |