Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

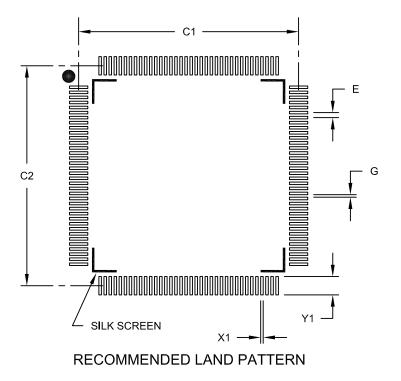

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efg100-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: PIN NAMES FOR 144-PIN DEVICES

#### 144-PIN LQFP AND TQFP (TOP VIEW)

#### PIC32MZ0512EF(E/F/K)144 PIC32MZ1024EF(G/H/M)144 PIC32MZ1024EF(E/F/K)144 PIC32MZ2048EF(G/H/M)144

144

1

| Pin<br>Number | Full Pin Name                  |     | Pin<br>Number | Full Pin Name              |

|---------------|--------------------------------|-----|---------------|----------------------------|

| 1             | AN23/RG15                      |     | 37            | PGEC2/AN46/RPB6/RB6        |

| 2             | EBIA5/AN34/PMA5/RA5            | 1 1 | 38            | PGED2/AN47/RPB7/RB7        |

| 3             | EBID5/AN17/RPE5/PMD5/RE5       | 1 1 | 39            | VREF-/CVREF-/AN27/RA9      |

| 4             | EBID6/AN16/PMD6/RE6            | 1 1 | 40            | VREF+/CVREF+/AN28/RA10     |

| 5             | EBID7/AN15/PMD7/RE7            | 1 1 | 41            | AVdd                       |

| 6             | EBIA6/AN22/RPC1/PMA6/RC1       | 1 1 | 42            | AVss                       |

| 7             | AN35/ETXD0/RJ8                 | 1   | 43            | AN38/ETXD2/RH0             |

| 8             | AN36/ETXD1/RJ9                 | 1 1 | 44            | AN39/ETXD3/RH1             |

| 9             | EBIBS0/RJ12                    | 1 [ | 45            | EBIRP/RH2                  |

| 10            | EBIBS1/RJ10                    | 1 1 | 46            | RH3                        |

| 11            | EBIA12/AN21/RPC2/PMA12/RC2     | 1 1 | 47            | EBIA10/AN48/RPB8/PMA10/RB8 |

| 12            | EBIWE/AN20/RPC3/PMWR/RC3       | 1 1 | 48            | EBIA7/AN49/RPB9/PMA7/RB9   |

| 13            | EBIOE/AN19/RPC4/PMRD/RC4       | 1   | 49            | CVREFOUT/AN5/RPB10/RB10    |

| 14            | AN14/C1IND/RPG6/SCK2/RG6       |     | 50            | AN6/RB11                   |

| 15            | AN13/C1INC/RPG7/SDA4/RG7       | 1 1 | 51            | EBIA1/PMA1/RK1             |

| 16            | AN12/C2IND/RPG8/SCL4/RG8       |     | 52            | EBIA3/PMA3/RK2             |

| 17            | Vss                            | 1 1 | 53            | EBIA17/RK3                 |

| 18            | Vdd                            |     | 54            | Vss                        |

| 19            | EBIA16/RK0                     | 1   | 55            | VDD                        |

| 20            | MCLR                           |     | 56            | TCK/AN29/RA1               |

| 21            | EBIA2/AN11/C2INC/RPG9/PMA2/RG9 | 1 1 | 57            | TDI/AN30/RPF13/SCK5/RF13   |

| 22            | TMS/AN24/RA0                   |     | 58            | TDO/AN31/RPF12/RF12        |

| 23            | AN25/RPE8/RE8                  |     | 59            | AN7/RB12                   |

| 24            | AN26/RPE9/RE9                  |     | 60            | AN8/RB13                   |

| 25            | AN45/C1INA/RPB5/RB5            |     | 61            | AN9/RPB14/SCK3/RB14        |

| 26            | AN4/C1INB/RB4                  |     | 62            | AN10/RPB15/OCFB/RB15       |

| 27            | AN37/ERXCLK/EREFCLK/RJ11       |     | 63            | Vss                        |

| 28            | EBIA13/PMA13/RJ13              |     | 64            | VDD                        |

| 29            | EBIA11/PMA11/RJ14              |     | 65            | AN40/ERXERR/RH4            |

| 30            | EBIA0/PMA0/RJ15                |     | 66            | AN41/ERXD1/RH5             |

| 31            | AN3/C2INA/RPB3/RB3             |     | 67            | AN42/ERXD2/RH6             |

| 32            | Vss                            |     | 68            | EBIA4/PMA4/RH7             |

| 33            | VDD                            |     | 69            | AN32/RPD14/RD14            |

| 34            | AN2/C2INB/RPB2/RB2             |     | 70            | AN33/RPD15/SCK6/RD15       |

| 35            | PGEC1/AN1/RPB1/RB1             |     | 71            | OSC1/CLKI/RC12             |

| 36            | PGED1/AN0/RPB0/RB0             | l l | 72            | OSC2/CLKO/RC15             |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.4 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See Section 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

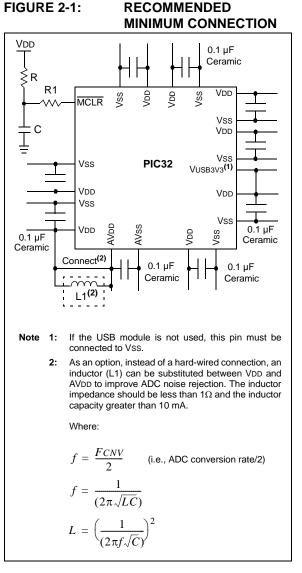

#### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

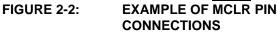

# 2.3 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

Pulling The MCLR pin low generates either a device Reset or a POR, depending on the setting of the SMCLR bit (DEVCFG0<15>). Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

**3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

DS60001320D-page 38

#### 3.1.4 FLOATING POINT UNIT (FPU)

The Floating Point Unit (FPU), Coprocessor (CP1), implements the MIPS Instruction Set Architecture for floating point computation. The implementation supports the ANSI/IEEE Standard 754 (IEEE for Binary Floating Point Arithmetic) for 32-bit and 64-bit floating point data formats. The FPU can be programmed to have thirty-two 32-bit or 64-bit floating point registers used for floating point operations.

The performance is optimized for 32-bit formats. Most instructions have one FPU cycle throughput and four FPU cycle latency. The FPU implements the multiplyadd (MADD) and multiply-sub (MSUB) instructions with intermediate rounding after the multiply function. The result is guaranteed to be the same as executing a MUL and an ADD instruction separately, but the instruction latency, instruction fetch, dispatch bandwidth, and the total number of register accesses are improved.

IEEE denormalized input operands and results are supported by hardware for some instructions. IEEE denormalized results are not supported by hardware in general, but a fast flush-to-zero mode is provided to optimize performance. The fast flush-to-zero mode is enabled through the FCCR register, and use of this mode is recommended for best performance when denormalized results are generated.

The FPU has a separate pipeline for floating point instruction execution. This pipeline operates in parallel with the integer core pipeline and does not stall when the integer pipeline stalls. This allows long-running FPU operations, such as divide or square root, to be partially masked by system stalls and/or other integer unit instructions. Arithmetic instructions are always dispatched and completed in order, but loads and stores can complete out of order. The exception model is "precise" at all times.

Table 3-4 contains the floating point instruction latencies and repeat rates for the processor core. In this table, 'Latency' refers to the number of FPU cycles necessary for the first instruction to produce the result needed by the second instruction. The "Repeat Rate" refers to the maximum rate at which an instruction can be executed per FPU cycle.

#### TABLE 3-4: FPU INSTRUCTION LATENCIES AND REPEAT RATES

| Op code                                                                                                            | Latency<br>(FPU<br>Cycles) | Repeat<br>Rate<br>(FPU<br>Cycles) |

|--------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------|

| ABS.[S,D], NEG.[S,D],<br>ADD.[S,D], SUB.[S,D],<br>C.cond.[S,D], MUL.S                                              | 4                          | 1                                 |

| MADD.S, MSUB.S,<br>NMADD.S, NMSUB.S,<br>CABS.cond.[S,D]                                                            | 4                          | 1                                 |

| CVT.D.S, CVT.PS.PW,<br>CVT.[S,D].[W,L]                                                                             | 4                          | 1                                 |

| CVT.S.D,<br>CVT.[W,L].[S,D],<br>CEIL.[W,L].[S,D],<br>FLOOR.[W,L].[S,D],<br>ROUND.[W,L].[S,D],<br>TRUNC.[W,L].[S,D] | 4                          | 1                                 |

| MOV.[S,D], MOVF.[S,D],<br>MOVN.[S,D],<br>MOVT.[S,D], MOVZ.[S,D]                                                    | 4                          | 1                                 |

| MUL.D                                                                                                              | 5                          | 2                                 |

| MADD.D, MSUB.D,<br>NMADD.D, NMSUB.D                                                                                | 5                          | 2                                 |

| RECIP.S                                                                                                            | 13                         | 10                                |

| RECIP.D                                                                                                            | 26                         | 21                                |

| RSQRT.S                                                                                                            | 17                         | 14                                |

| RSQRT.D                                                                                                            | 36                         | 31                                |

| DIV.S, SQRT.S                                                                                                      | 17                         | 14                                |

| DIV.D, SQRT.D                                                                                                      | 32                         | 29                                |

| MTC1, DMTC1, LWC1,<br>LDC1, LDXC1, LUXC1,<br>LWXC1                                                                 | 4                          | 1                                 |

| MFC1, DMFC1, SWC1,<br>SDC1, SDXC1, SUXC1,<br>SWXC1                                                                 | 1                          | 1                                 |

Legend: S = Single (32-bit) D = Double (64-bit)W = Word (32-bit) L = Long word (64-bit)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit         Bit         Bit           29/21/13/5         28/20/12/4         27/19/11 |                            |       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|--------------------------------------------------------------------------------------|----------------------------|-------|-------------------|------------------|------------------|

| 21.24        | R/W-x             | R/W-x             | R/W-x                                                                                | R/W-x                      | R/W-x | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   |                   | FS                                                                                   |                            |       |                   |                  |                  |

| 23:16        | R/W-x             | R/W-x             | R/W-x                                                                                | R-0                        | R-1   | R-1               | R/W-x            | R/W-x            |

| 23:16        | FCC<0>            | FO                | FN                                                                                   | ABS2008 NAN2008 CAUSE<5:4> |       |                   |                  |                  |

|              | R/W-x             | R/W-x             | R/W-x                                                                                | R/W-x                      | R/W-x | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | CAUSE             | .2.0.                                                                                |                            |       |                   |                  |                  |

|              |                   | CAUSE             | <3.0>                                                                                | V                          | Z     | 0                 | U                |                  |

|              | R/W-x             | R/W-x             | R/W-x                                                                                | R/W-x R/W-x                |       | R/W-x             | R/W-x            | R/W-x            |

| 7:0          | ENABLES<0>        |                   |                                                                                      | FLAGS<4:0>                 |       | DM                |                  |                  |

|              | I                 | V                 | Z                                                                                    | U                          |       | RM<1:0>           |                  |                  |

#### REGISTER 3-10: FCSR: FLOATING POINT CONTROL AND STATUS REGISTER; CP1 REGISTER 31

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-25 FCC<7:1>: Floating Point Condition Code bits

These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

#### bit 24 **FS:** Flush to Zero control bit

1 = Denormal input operands are flushed to zero. Tiny results are flushed to either zero or the applied format's smallest normalized number (MinNorm) depending on the rounding mode settings.

0 = Denormal input operands result in an Unimplemented Operation exception.

#### bit 23 FCC<0>: Floating Point Condition Code bits

These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

- bit 22 **FO:** Flush Override Control bit

- 1 = The intermediate result is kept in an internal format, which can be perceived as having the usual mantissa precision but with unlimited exponent precision and without forcing to a specific value or taking an exception.

- 0 = Handling of Tiny Result values depends on setting of the FS bit.

#### bit 21 FN: Flush to Nearest Control bit

- 1 = Final result is rounded to either zero or 2E\_min (MinNorm), whichever is closest when in Round to Nearest (RN) rounding mode. For other rounding modes, a final result is given as if FS was set to 1.

0 = Handling of Tiny Result values depends on setting of the FS bit.

- bit 20 MAC2008: Fused Multiply Add mode control bit

- 0 = Unfused multiply-add. Intermediary multiplication results are rounded to the destination format.

- bit 19 ABS2008: Absolute value format control bit

- 1 = ABS.fmt and NEG.fmt instructions compliant with IEEE Standard 754-2008. The ABS and NEG functions accept QNAN inputs without trapping.

- bit 18 NAN2008: NaN Encoding control bit

- 1 = Quiet and signaling NaN encodings recommended by the IEEE Standard 754-2008. A quiet NaN is encoded with the first bit of the fraction being 1 and a signaling NaN is encoded with the first bit of the fraction being 0.

#### bit 17-12 CAUSE<5:0>: FPU Exception Cause bits

These bits indicated the exception conditions that arise during execution of an FPU arithmetic instruction.

bit 17 E: Unimplemented Operation bit

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |        | Bit Bit<br>29/21/13/5 28/20/12/4 |             | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|----------------------------------|--------|----------------------------------|-------------|----------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 31:24        | U-0                              | U-0    | U-0                              | U-0         | U-0                  | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31.24        | —                                |        |                                  | —           | —                    | _                 |                  | —                |  |  |  |  |  |  |

| 00.40        | R/W-1 R/W-1                      |        | R/W-1                            | R/W-1 R/W-1 |                      | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup>       |        |                                  |             |                      |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-1                            | R/W-1  | R/W-1                            | R/W-1       | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |  |

| 15:8         |                                  |        |                                  | CHSIRQ<     | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | S-0                              | S-0    | R/W-0                            | R/W-0       | R/W-0                | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 7:0          | CFORCE                           | CABORT | PATEN                            | SIRQEN      | AIRQEN               | _                 | _                | _                |  |  |  |  |  |  |

### REGISTER 10-8: DCHxECON: DMA CHANNEL x EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

and set CHAIF flag

#### bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>   |

|-----------|---------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress |

|           | •                                                             |

|           | •                                                             |

|           | •                                                             |

|           |                                                               |

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

#### bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits<sup>(1)</sup>

11111111 = Interrupt 255 will initiate a DMA transfer

• 00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

#### bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

#### bit 6 CABORT: DMA Abort Transfer bit

- 1 = A DMA transfer is aborted when this bit is written to a '1'

- 0 = This bit always reads '0'

#### bit 5 **PATEN:** Channel Pattern Match Abort Enable bit

- 1 = Abort transfer and clear CHEN on pattern match

- 0 = Pattern match is disabled

- bit 4 SIRQEN: Channel Start IRQ Enable bit

- 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

- 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-2: "Interrupt IRQ, Vector, and Bit Location" for the list of available interrupt IRQ sources.

|              |                   |                   | 1 1-7)            |                   |                   |                  |                  |       |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|-------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |       |  |  |

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            | R/W-0 |  |  |

| 31:24        | TXINTERV<7:0>     |                   |                   |                   |                   |                  |                  |       |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            | R/W-0 |  |  |

| 23:16        | SPEE              | D<1:0>            | PROTOCO           | OL<1:0>           | TEP<3:0>          |                  |                  |       |  |  |

| 15.0         | U-0               | U-0               | R-0               | R-0               | R-0 R-0 R-0       |                  |                  |       |  |  |

| 15:8         | _                 | _                 |                   |                   | RXCNT             | <13:8>           |                  |       |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              | R-0   |  |  |

| 7:0          |                   |                   |                   | RXC               | NT<7:0>           |                  |                  |       |  |  |

#### REGISTER 11-10: USBIENCSR2: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 2 (ENDPOINT 1-7)

| Legend:           | HC = Hardware Cleared | HS = Hardware Set          |                    |

|-------------------|-----------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-24 TXINTERV<7:0>: Endpoint TX Polling Interval/NAK Limit bits (Host mode)

For Interrupt and Isochronous transfers, this field defines the polling interval for the endpoint. For Bulk endpoints, this field sets the number of frames/microframes after which the endpoint should time out on receiving a stream of NAK responses.

The following table describes the valid values and interpretation for these bits:

| Transfer Type | Speed        | Valid Values (m) | Interpretation                                                                                                |

|---------------|--------------|------------------|---------------------------------------------------------------------------------------------------------------|

| Interrupt     | Low/Full     | 0x01 to 0xFF     | Polling interval is 'm' frames.                                                                               |

|               | High         | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames.                                                                |

| Isochronous   | Full or High | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames/microframes.                                                    |

| Bulk          | Full or High | 0x02 to 0x10     | NAK limit is 2 <sup>(m-1)</sup> frames/microframes. A value of '0' or '1' disables the NAK time-out function. |

bit 23-22 SPEED<1:0>: TX Endpoint Operating Speed Control bits (Host mode)

- 11 = Low-Speed

- 10 = Full-Speed

- 01 = Hi-Speed

- 00 = Reserved

bit 21-20 PROTOCOL<1:0>: TX Endpoint Protocol Control bits

- 11 = Interrupt

- 10 = Bulk

- 01 = Isochronous

00 = Control

bit 19-16 **TEP<3:0>:** TX Target Endpoint Number bits

This value is the endpoint number contained in the TX endpoint descriptor returned to the USB module during device enumeration.

- bit 15-14 Unimplemented: Read as '0'

- bit 13-0 RXCNT<13:0>: Receive Count bits

The number of received data bytes in the endpoint RX FIFO. The value returned changes as the contents of the FIFO change and is only valid while RXPKTRDY is set.

#### REGISTER 11-30: USBCRCON: USB CLOCK/RESET CONTROL REGISTER (CONTINUED)

- bit 3 SENDMONEN: Session End VBUS Monitoring for OTG Enable bit

- 1 = Enable monitoring for VBUS in Session End range (between 0.2V and 0.8V)

- 0 = Disable monitoring for VBUS in Session End range

- bit 2 USB General Interrupt Enable bit

- 1 = Enables general interrupt from USB module

- 0 = Disables general interrupt from USB module

- bit 1 USBRIE: USB Resume Interrupt Enable bit

- 1 = Enable remote resume from suspend Interrupt

- 0 = Disable interrupt to a Remote Devices USB resume signaling

#### bit 0 USBWKUPEN: USB Activity Detection Interrupt Enable bit

- 1 = Enable interrupt for detection of activity on USB bus in Sleep mode

- 0 = Disable interrupt for detection of activity on USB bus in Sleep mode

| SSS                         |                  |           |       |       |       |       |       |       |      | B    | its  |      |      |      |           |        |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|-----------|--------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3      | 18/2   | 17/1   | 16/0 | All Resets |

| 4444                        | IC4R             | 31:16     | —     | —     | -     | —     | -     | —     | —    | —    | —    | -    | —    | —    | —         | -      | -      | —    | 0000       |

| 1444                        | IC4R             | 15:0      |       | _     | —     | _     |       | _     | _    | _    | _    | —    | —    | —    |           | IC4R   | <3:0>  |      | 0000       |

| 1448                        | IC5R             | 31:16     |       | —     | —     | _     |       | —     | —    |      | —    | _    | _    | _    | _         | _      | _      |      | 0000       |

| 1440                        | 10.51            | 15:0      |       | —     | —     | —     |       | —     | —    | —    | _    | _    | —    | —    |           | IC5R   | <3:0>  |      | 0000       |

| 144C                        | IC6R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —         | —      | —      | —    | 0000       |

| 1440                        | ICOIX            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |           | IC6R   | <3:0>  |      | 0000       |

| 1450                        | IC7R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —         | —      | —      | —    | 0000       |

| 1430                        | 10/10            | 15:0      | _     | _     | —     | —     | _     | _     | —    | _    | _    | —    | _    | —    |           | IC7R   | <3:0>  |      | 0000       |

| 1454                        | IC8R             | 31:16     | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —         | —      | —      | —    | 0000       |

| 1-0-1                       | 10011            | 15:0      | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |           | IC8R   | <3:0>  |      | 0000       |

| 1458                        | IC9R             | 31:16     | -     | —     | —     | —     | _     | —     | —    | _    | _    | —    | _    | —    | —         | —      | —      | —    | 0000       |

|                             |                  | 15:0      | -     | —     |       | —     | _     | _     | —    | —    | _    |      |      | _    | IC9R<3:0> |        |        | 0000 |            |

| 1460                        | OCFAR            | 31:16     | _     | —     |       | —     | _     | —     | —    | _    | —    | —    | —    | —    | —         | —      | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     |       | —     |       | —     | —    |      | _    | —    | —    | —    |           | OCFA   | R<3:0> |      | 0000       |

| 1468                        | U1RXR            | 31:16     | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |           | —      | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |           | U1RXI  | R<3:0> |      | 0000       |

| 146C                        | U1CTSR           | 31:16     | _     |       |       | —     | _     | —     | —    | —    | _    |      |      | —    | —         | —      | —      | —    | 0000       |

|                             |                  | 15:0      | —     | —     | _     | —     | _     | —     | —    | —    | —    | —    | —    | —    |           | U1CTS  |        |      | 0000       |

| 1470                        | U2RXR            | 31:16     | _     | —     |       | _     | _     | —     | —    | —    | —    | —    | _    | —    | —         | —      | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | -     | —     | —     | —     | —    | _    | _    | —    | —    | —    |           | U2RXI  |        |      | 0000       |

| 1474                        | U2CTSR           | 31:16     | _     | _     |       |       | _     | _     | _    |      | _    |      | _    | _    | _         |        | —      | —    | 0000       |

|                             |                  | 15:0      | _     | _     | -     | _     | _     | _     | _    | _    | _    | _    | _    | _    |           | U2CTS  |        |      | 0000       |

| 1478                        | <b>U3RXR</b>     | 31:16     | _     |       | -     | _     | _     |       | _    | _    | _    | —    |      | _    | —         |        | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     |       | _     |       | _     | _    | _    | _    | _    |      | _    |           | U3RXI  |        |      | 0000       |

| 147C                        | <b>U3CTSR</b>    | 31:16     | _     | _     |       | _     | _     | _     | _    | _    | _    |      |      | _    | —         |        | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     |       | _     |       | _     | _    | _    | _    | _    | _    | _    |           | U3CTS  | R<3:0> |      | 0000       |

| 1480                        | U4RXR            | 31:16     |       | —     | _     | _     | _     | —     | _    |      | _    | _    | _    | _    | _         |        |        | _    | 0000       |

|                             |                  | 15:0      |       | —     |       | _     | _     | —     | —    |      | _    | _    | _    | _    |           | U4RXI  |        |      | 0000       |

| 1484                        | U4CTSR           | 31:16     |       | —     |       | _     | _     | —     | —    |      | _    | _    | _    | _    |           | -      | —      | _    | 0000       |

|                             | 15:0             |           | —     | —     | —     | -     | —     | —     | —    | —    |      | _    | —    |      | U4CTS     | R<3:0> |        | 0000 |            |

# TABLE 12-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

# TABLE 12-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                       |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 15B4                        | RPC13R                | 31:16     | _     |       | —     |       | _     |       |      | _    |      | —    | —    | —    | —    | —     | _      | -    | 0000       |

| 1364                        | RECISK                | 15:0      | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    |      | RPC13 | R<3:0> |      | 0000       |

| 15B8                        | RPC14R                | 31:16     | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1300                        | KFC14K                | 15:0      | _     |       | _     |       | —     |       |      | _    |      | -    | _    | _    |      | RPC14 | R<3:0> |      | 0000       |

| 15C0                        | RPD0R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1300                        | REDOR                 | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD0  | R<3:0> |      | 0000       |

| 15C4                        | RPD1R                 | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | _     | —      | —    | 0000       |

| 1304                        | REDIK                 | 15:0      | —     |       | —     | _     | —     | _     |      | —    | _    | —    | —    | —    |      | RPD1  | R<3:0> |      | 0000       |

| 15C8                        | RPD2R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1300                        | KF D2K                | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | RPD2  | R<3:0> |      | 0000       |

| 15CC                        | RPD3R                 | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1300                        | KF D3K                | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD3  | R<3:0> |      | 0000       |

| 15D0                        | RPD4R                 | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | _     | —      | —    | 0000       |

| 1300                        | KF D4K                | 15:0      | _     | _     | _     | -     | —     | _     | _    | —    | -    | _    | _    | _    |      | RPD4  | R<3:0> |      | 0000       |

| 15D4                        | RPD5R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1304                        | REDSK                 | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | RPD5  | R<3:0> |      | 0000       |

| 15D8                        | RPD6R <sup>(2)</sup>  | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 1300                        | KFD0K*/               | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD6  | R<3:0> |      | 0000       |

| 15DC                        | RPD7R <sup>(2)</sup>  | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 1300                        | KFD/K·/               | 15:0      | _     | _     | _     | -     | —     | _     | _    | —    | -    | _    | _    | _    |      | RPD7  | R<3:0> |      | 0000       |

| 15E4                        | RPD9R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1324                        | KF D9K                | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | RPD9  | R<3:0> |      | 0000       |

| 15E8                        | RPD10R                | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 1020                        | IN DIGIN              | 15:0      | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    |      | RPD10 | R<3:0> |      | 0000       |

| 15EC                        | RPD11R                | 31:16     | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1020                        | KI DIIK               | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD11 | R<3:0> |      | 0000       |

| 15F0                        | RPD12R <sup>(1)</sup> | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1010                        | KI DIZIK <sup>1</sup> | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD12 | R<3:0> |      | 0000       |

| 15F8                        | RPD14R <sup>(1)</sup> | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 101.0                       | IN DI4IN              | 15:0      | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    |      | RPD14 | R<3:0> |      | 0000       |

| 15FC                        | RPD15R <sup>(1)</sup> | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1010                        | N D ION /             | 15:0      | —     | _     |       |       | —     | _     | _    | —    | _    |      | _    |      |      | RPD15 | R<3:0> |      | 0000       |

| 160C                        | RPE3R                 | 31:16     | —     | _     | —     | _     | —     | —     | _    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1000                        | INF LOIN              | 15:0      | —     | -     | —     |       | _     | -     | -    | —    |      | —    | —    | —    |      | RPE3  | R<3:0> |      | 0000       |

| 1614                        | RPE5R                 | 31:16     | _     |       | —     |       | —     |       |      | _    | —    | —    | —    | _    | —    | —     | —      | —    | 0000       |

| 1014                        |                       | 15:0      | —     |       | _     | —     | —     | —     | —    | —    | —    | —    | —    | _    |      | RPE5  | R<3:0> |      | 0000       |

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is not available on 64-pin devices. Note 1:

This register is not available on 64-pin and 100-pin devices. 2:

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |  |

|--------------|------------------------|--------------------|-------------------|-----------------------|-------------------|-------------------|------------------|-----------------------|--|

|              | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN                 | FRMSYPW           | FRMCNT<2:0>       |                  |                       |  |

|              | R/W-0                  | U-0                | U-0               | U-0                   | U-0               | U-0               | R/W-0            | R/W-0                 |  |

| 23:16        | MCLKSEL <sup>(1)</sup> | _                  |                   | —                     | _                 | _                 | SPIFE            | ENHBUF <sup>(1)</sup> |  |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |

| 15:8         | ON                     | _                  | SIDL              | DISSDO <sup>(4)</sup> | MODE32            | MODE16            | SMP              | CKE <sup>(2)</sup>    |  |

| 7.0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |

| 7:0          | SSEN                   | CKP <sup>(3)</sup> | MSTEN             | DISSDI <sup>(4)</sup> | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |  |

#### REGISTER 19-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled ( $\overline{SSx}$  pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support is enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(1)</sup>

- 1 = REFCLKO1 is used by the Baud Rate Generator

- 0 = PBCLK2 is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** This bit can only be written when the ON bit = 0. Refer to **Section 37.0** "**Electrical Characteristics**" for maximum clock frequency requirements.

- 2: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: This bit present for legacy compatibility and is superseded by PPS functionality on these devices (see Section 12.4 "Peripheral Pin Select (PPS)" for more information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 |                   | _                 |                   |                   | —                 |                  | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | —                 | _                 | —                 |                   | —                 |                  | _                |  |  |

| 45.0         | R-0, HS, HC       | R-0, HS, HC       | R/C-0, HS, HC     | U-0               | U-0               | R/C-0, HS         | R-0, HS, HC      | R-0, HS, HC      |  |  |

| 15:8         | ACKSTAT           | TRSTAT            | ACKTIM            | _                 |                   | BCL               | GCSTAT           | ADD10            |  |  |

| 7.0          | R/C-0, HS, SC     | R/C-0, HS, SC     | R-0, HS, HC       | R/C-0, HS, HC     | R/C-0, HS, HC     | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |  |

# REGISTER 21-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Legend:           | HS = Hardware Set | HC = Hardware Cleared     | SC = Software Cleared |  |

|-------------------|-------------------|---------------------------|-----------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'            |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | C = Clearable bit     |  |

#### bit 21 16 Linin nnla tod. De 24 <u>'</u>∩'

| bit 31-16 | Unimplemented: Read as 10 <sup>°</sup>                                                                                                                               |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                          |

|           | 1 = NACK received from slave                                                                                                                                         |

|           | 0 = ACK received from slave                                                                                                                                          |

|           | Hardware set or clear at end of slave Acknowledge.                                                                                                                   |

| bit 14    | <b>TRSTAT:</b> Transmit Status bit (when operating as $I^2C$ master, applicable to master transmit operation)<br>1 = Master transmit is in progress (8 bits + ACK)   |

|           | 0 = Master transmit is not in progress                                                                                                                               |

|           | Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.                                                                        |

| bit 13    | <b>ACKTIM:</b> Acknowledge Time Status bit (Valid in I <sup>2</sup> C Slave mode only)                                                                               |

|           | $1 = I^2C$ bus is in an Acknowledge sequence, set on the eight falling edge of SCL clock<br>0 = Not an Acknowledge sequence, cleared on 9th rising edge of SCL clock |

| bit 12-11 | Unimplemented: Read as '0'                                                                                                                                           |

| bit 10    | BCL: Master Bus Collision Detect bit                                                                                                                                 |

|           | 1 = A bus collision has been detected during a master operation                                                                                                      |

|           | 0 = No collision                                                                                                                                                     |

|           | Hardware set at detection of bus collision.                                                                                                                          |

| bit 9     | GCSTAT: General Call Status bit                                                                                                                                      |

|           | 1 = General call address was received                                                                                                                                |

|           | 0 = General call address was not received                                                                                                                            |

|           | Hardware set when address matches general call address. Hardware clear at Stop detection.                                                                            |

| bit 8     | ADD10: 10-bit Address Status bit                                                                                                                                     |

|           | 1 = 10-bit address was matched                                                                                                                                       |

|           | 0 = 10-bit address was not matched                                                                                                                                   |

|           | Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.                                                                       |

| bit 7     | IWCOL: Write Collision Detect bit                                                                                                                                    |

|           | 1 = An attempt to write the I2CxTRN register failed because the $I^2$ C module is busy                                                                               |

|           | <ul> <li>0 = No collision</li> <li>Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).</li> </ul>                                       |

| L:1.0     |                                                                                                                                                                      |

| bit 6     | I2COV: Receive Overflow Flag bit                                                                                                                                     |

|           | <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> </ul>                                   |

|           | Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                        |

|           |                                                                                                                                                                      |

|           |                                                                                                                                                                      |

|           |                                                                                                                                                                      |

|              |                   | -                 |                   |                   |                                    |                   |                  |                  |  |  |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |  |  |

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |  |  |

|              |                   | HR10              | <3:0>             |                   | HR01<3:0>                          |                   |                  |                  |  |  |  |  |  |  |  |  |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |  |  |

|              |                   | MIN10             | <3:0>             |                   | MIN01<3:0>                         |                   |                  |                  |  |  |  |  |  |  |  |  |  |  |

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |  |  |  |

| 15:8         |                   | SEC10             | <3:0>             |                   | SEC01<3:0>                         |                   |                  |                  |  |  |  |  |  |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                                | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |  |

| 7:0          | —                 | —                 | —                 | _                 | —                                  | —                 | _                | —                |  |  |  |  |  |  |  |  |  |  |

|              |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |  |  |  |  |  |  |  |

| Legend:      |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |  |  |  |  |  |  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |  |  |  |  |  |  |  |  |  |

0' = Bit is cleared

x = Bit is unknown

#### REGISTER 25-3: RTCTIME: REAL-TIME CLOCK TIME VALUE REGISTER

'1' = Bit is set

| bit 31-28 | HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10 digits; contains a value from 0 to 2    |

|-----------|-------------------------------------------------------------------------------------------------|

| bit 27-24 | HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1 digit; contains a value from 0 to 9      |

| bit 23-20 | MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10 digits; contains a value from 0 to 5 |

| bit 19-16 | MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1 digit; contains a value from 0 to 9   |

| bit 15-12 | SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10 digits; contains a value from 0 to 5 |

| bit 11-8  | SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1 digit; contains a value from 0 to 9   |

bit 7-0 Unimplemented: Read as '0'

-n = Value at POR

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                                            | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------------------------------------|------------------|

| 21.24     | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                                                                       | R/W-0            |

| 31:24     | FEN               | _                 | —                 | ADC4EN            | ADC3EN            | ADC2EN            | ADC1EN                                                                      | ADC0EN           |

| 00.40     | R/W-0             | R-0, HS, HC       | R-0, HS, HC       | U-0               | U-0               | U-0               | U-0                                                                         | U-0              |

| 23:16     | FIEN              | FRDY              | FWROVERR          | —                 | _                 | —                 |                                                                             | _                |

| 45.0      | R-0                                                                         | R-0              |

| 15:8      |                   |                   |                   | FCNT              | <7:0>             |                   | 25/17/9/1         2           R/W-0         ADC1EN         //           U-0 |                  |

| 7.0       | R-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0                                                                         | R-0              |

| 7:0       | FSIGN             | —                 | —                 | _                 | —                 |                   | ADCID<2:0>                                                                  |                  |

#### REGISTER 28-22: ADCFSTAT: ADC FIFO STATUS REGISTER

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                    |

|-------------------|-------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set  | 0' = Bit is cleared $x = Bit is unknown$ |

| bit 31    | FEN: FIFO Enable bit                                                                                                                                                |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = FIFO is enabled                                                                                                                                                 |

|           | 0 = FIFO is disabled; no data is being saved into the FIFO                                                                                                          |

| bit 30-29 | Unimplemented: Read as '0'                                                                                                                                          |

| bit 28-24 | <b>ADC4EN:ADC0EN:</b> ADCx Enable bits ('x' = 0 through 4)                                                                                                          |

|           | 1 = Converted output data of ADCx is stored in the FIFO                                                                                                             |

|           | 0 = Converted output data of ADCx is not stored in the FIFO                                                                                                         |

|           | <b>Note:</b> While using FIFO, the output data is additionally stored in the respective output data register (ADCDATAx).                                            |

| bit 23    | FIEN: FIFO Interrupt Enable bit                                                                                                                                     |

|           | <ul> <li>1 = FIFO interrupts are enabled; an interrupt is generated once the FRDY bit is set</li> <li>0 = FIFO interrupts are disabled</li> </ul>                   |

| bit 22    | FRDY: FIFO Data Ready Interrupt Status bit                                                                                                                          |

|           | 1 = FIFO has data to be read                                                                                                                                        |

|           | 0 = No data is available in the FIFO                                                                                                                                |

|           | <b>Note:</b> This bit is cleared when the FIFO output data in ADCFIFO has been read and there is no additional data ready in the FIFO (that is, the FIFO is empty). |

| bit 21    | FWROVERR: FIFO Write Overflow Error Status bit                                                                                                                      |

|           | <ul> <li>1 = A write overflow error in the FIFO has occurred (circular FIFO)</li> <li>0 = A write overflow error in the FIFO has not occurred</li> </ul>            |

|           | <b>Note:</b> This bit is cleared after ADCFSTAT<23:16> are read by software.                                                                                        |

| bit 15-8  | <b>FCNT&lt;7:0&gt;:</b> FIFO Data Entry Count Status bit                                                                                                            |

|           | The value in these bits indicates the number of data entries in the FIFO.                                                                                           |

| bit 7     | FSIGN: FIFO Sign Setting bit                                                                                                                                        |

|           | This bit reflects the sign of data stored in the ADCFIFO register.                                                                                                  |

| bit 6-3   | Unimplemented: Read as '0'                                                                                                                                          |

| bit 2-0   | <b>ADCID&lt;2:0&gt;:</b> ADCx Identifier bits ('x' = 0 through 4)                                                                                                   |

|           | These bits specify the ADC module whose data is stored in the FIFO.                                                                                                 |

|           | 111 = Reserved                                                                                                                                                      |

|           | 110 = Reserved                                                                                                                                                      |

|           | 101 = Reserved<br>100 = Converted data of ADC4 is stored in FIFO                                                                                                    |

|           | •                                                                                                                                                                   |

|           | •                                                                                                                                                                   |

|           | •<br>000 = Converted data of ADC0 is stored in FIFO                                                                                                                 |

|           | 000 - Converted data of ADCO is stored in FIFO                                                                                                                      |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31.24        | HT<31:24>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22.16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | HT<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | HT<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | HT<               | 7:0>              |                   |                  |                  |  |  |  |  |

#### REGISTER 30-5: ETHHT0: ETHERNET CONTROLLER HASH TABLE 0 REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 HT<31:0>: Hash Table Bytes 0-3 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

#### REGISTER 30-6: ETHHT1: ETHERNET CONTROLLER HASH TABLE 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24     |                   |                   |                   | HT<6              | 3:56>             |                   |                  |                  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16     | HT<55:48>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      |                   |                   |                   | HT<4              | 7:40>             |                   |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | HT<39:32>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 HT<63:32>: Hash Table Bytes 4-7 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

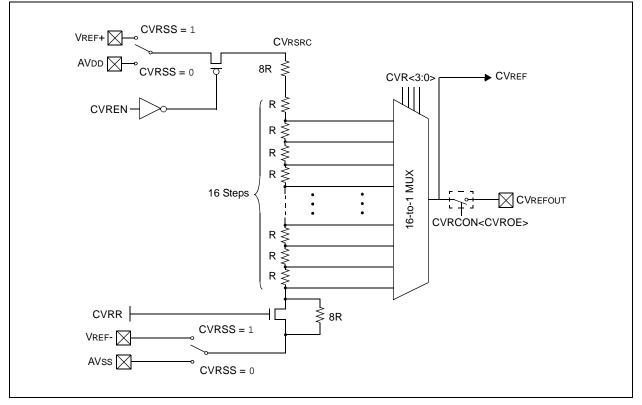

# 32.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

| Note: | This data sheet summarizes the          |

|-------|-----------------------------------------|

|       | features of the PIC32MZ EF family of    |

|       | devices. It is not intended to be a     |

|       | comprehensive reference source. To      |

|       | complement the information in this data |

|       | sheet, refer to Section 20. "Comparator |

|       | Voltage Reference (CVREF)"              |

|       | (DS60001109) in the "PIC32 Family       |

|       | Reference Manual", which is available   |

|       | from the Microchip web site             |

|       | (www.microchip.com/PIC32).              |

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The comparator voltage reference has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

A block diagram of the CVREF module is illustrated in Figure 32-1.