Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efg100-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   |                   | —                 |                   | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   |                   | —                 |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | _                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   |                   |                   | FCC<              | 7:0>              |                   |                  |                  |

#### REGISTER 3-7: FCCR: FLOATING POINT CONDITION CODES REGISTER; CP1 REGISTER 25

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FCC<7:0>:** Floating Point Condition Code bits These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

| 1            |                   |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 |                   |                  | —                |  |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x            | R/W-x            |  |

| 23:16        | _                 | —                 | —                 | —                 | —                 | —                 | CAUSE<5:4>       |                  |  |

|              |                   |                   |                   |                   |                   |                   | E                | V                |  |

|              | R/W-x             | R/W-x             | R/W-x             | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         |                   | CAUSE             |                   |                   |                   |                   |                  |                  |  |

|              | Z                 | 0                 | U                 | I                 |                   | _                 | _                | _                |  |

|              | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0              | U-0              |  |

| 7:0          |                   | FLAGS<4:0>        |                   |                   |                   |                   |                  |                  |  |

|              | _                 | V                 | Z                 | 0                 | U                 | I                 |                  |                  |  |

#### REGISTER 3-8: FEXR: FLOATING POINT EXCEPTIONS STATUS REGISTER; CP1 REGISTER 26

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-18 Unimplemented: Read as '0'

bit 17-12 **CAUSE<5:0>:** FPU Exception Cause bits These bits indicated the exception conditions that arise during execution of an FPU arithmetic instruction.

- bit 17 E: Unimplemented Operation bit

- bit 16 V: Invalid Operation bit

- bit 15 **Z:** Divide-by-Zero bit

- bit 14 **O:** Overflow bit

- bit 13 **U:** Underflow bit

- bit 12 I: Inexact bit

- bit 11-7 Unimplemented: Read as '0'

- bit 6-2 FLAGS<4:0>: FPU Flags bits

These bits show any exception conditions that have occurred for completed instructions since the flag was last reset by software.

- bit 6 V: Invalid Operation bit

- bit 4 **Z:** Divide-by-Zero bit

- bit 4 O: Overflow bit

- bit 3 U: Underflow bit

- bit 2 I: Inexact bit

- bit 1-0 Unimplemented: Read as '0'

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>t)                  | <b>b</b> -                      | e               |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |         | s          |

|-----------------------------|---------------------------------|-----------------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|---------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range       | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0    | All Resets |

|                             | OFF062                          | 31:16           | _     | _     | -     | —     | _     | _     | —    | _          | _    | _    | -    | —    | -    | —    | VOFF< | :17:16> | 0000       |

| 0638                        | 0FF062                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0620                        | OFF063                          | 31:16           | _     |       | _     | _     |       |       | —    |            | —    | —    | _    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0030                        | 0FF003                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0640                        | OFF064                          | 31:16           | _     |       | —     | —     |       | -     | —    |            | _    | —    | —    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0040                        | OFF004                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0644                        | OFF065                          | 31:16           | _     |       | -     | —     | —     |       | —    | —          | —    | —    | -    | —    | -    | _    | VOFF< | :17:16> | 0000       |

| 0644                        | UFFU05                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0649                        | OFF066                          | 31:16           | _     |       | _     | _     |       |       | —    |            | —    | —    | _    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0040                        | OFF000                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0640                        | OFF067                          | 31:16           | _     |       | —     | —     |       | -     | —    |            | _    | —    | —    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 064C                        | 06600                           | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0050                        |                                 | 31:16           | _     | _     | -     | —     | _     | —     | —    |            | _    | —    | -    | —    | -    | —    | VOFF< | :17:16> | 0000       |

| 0630                        | OFF068                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0054                        | OFF069                          | 31:16           | _     | _     | -     | _     | _     | _     | _    | _          | _    | _    | -    | _    | -    | _    | VOFF< | :17:16> | 0000       |

| 0654                        | 06609                           | 15:0 VOFF<15:1> |       |       |       |       |       |       |      |            | —    | 0000 |      |      |      |      |       |         |            |

| 0050                        | OFF070                          | 31:16           | _     |       | —     | —     |       | -     | —    |            | _    | —    | —    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0630                        | 066070                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0050                        | OFF071                          | 31:16           | _     | _     | -     | _     | _     | _     | _    | _          | _    | _    | -    | _    | -    | _    | VOFF< | :17:16> | 0000       |

| 0690                        |                                 | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0000                        | OFF072                          | 31:16           | -     | -     | -     | -     | —     | -     | —    | —          | —    | -    | -    | —    | -    | —    | VOFF< | :17:16> | 0000       |

| 0660                        | 0FF072                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0004                        | 055070                          | 31:16           | _     | —     | -     | —     | _     | _     | —    | _          | _    | —    | -    | —    | —    | _    | VOFF< | :17:16> | 0000       |

| 0664                        | OFF073                          | 15:0            |       |       | •     |       |       | -     |      | VOFF<15:1> |      | •    |      |      | •    |      |       | _       | 0000       |

| 0000                        | 055074                          | 31:16           | _     | —     | -     | —     | _     | _     | —    | _          | _    | —    | -    | —    | —    | _    | VOFF< | :17:16> | 0000       |

| 0668                        | OFF074                          | 15:0            |       |       | •     |       |       |       |      | VOFF<15:1> |      | •    | •    |      | •    | •    |       | _       | 0000       |

| 0000                        | 055075                          | 31:16           | _     | —     | -     | —     | _     | —     | —    | _          | _    | —    | -    | —    | -    | —    | VOFF< | :17:16> | 0000       |

| 066C                        | OFF075                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

|                             |                                 | 31:16           | _     | —     | —     | —     | _     | _     | —    | _          | _    | —    | —    | _    | —    | _    | VOFF< | :17:16> | 0000       |

| 0670                        | OFF076                          | 15:0            |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |         | 0000       |

© 2015-2016 Microchip Technology Inc.

Legend:

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

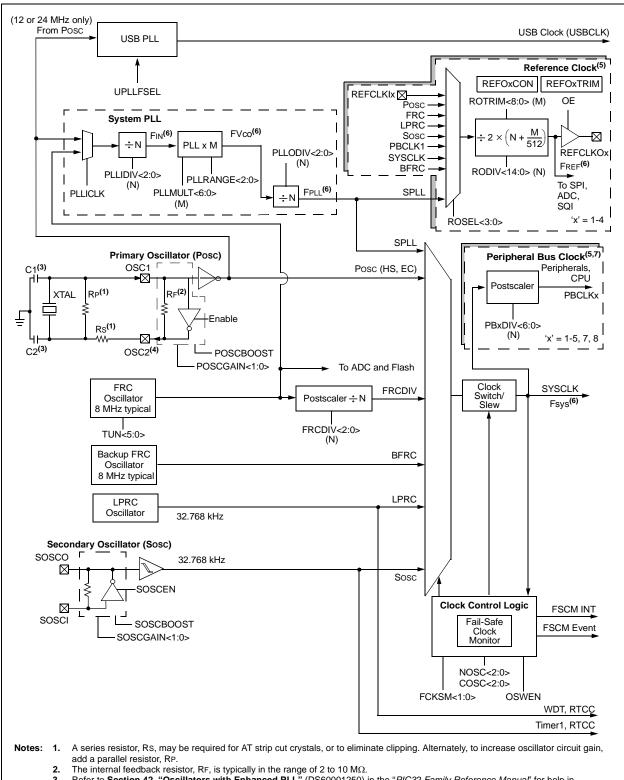

#### FIGURE 8-1: PIC32MZ EF FAMILY OSCILLATOR DIAGRAM

3. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for help in determining the best oscillator components.

- 4. PBCLK1 divided by 2 is available on the OSC2 pin in certain clock modes.

- 5. Shaded regions indicate multiple instantiations of a peripheral or feature.

- 6. Refer to Table 37-19 in Section 37.0 "Electrical Characteristics" for frequency limitations.

7. If the DEVCFG registers are configured for a SYSCLK speed greater than 200 MHz, these PBCLKs will be running faster than the maximum rating when the device comes out of Reset. To ensure proper operation, firmware must start the device at a speed less than or equal to 200 MHz, adjust the speed of the PBCLKs, and then raise the SYSCLK speed to the desired speed.

#### 12.2 Registers for Slew Rate Control

Some I/O pins can be configured for various types of slew rate control on its associated port. This is controlled by the Slew Rate Control bits in the SRCON1x and SRCON0x registers that are associated with each I/O port. The slew rate control is configured using the corresponding bit in each register, as shown in Table 12-1.

As an example, writing 0x0001, 0x0000 to SRCON1A and SRCON0A, respectively, will enable slew rate control on the RA0 pin and sets the slew rate to the slow edge rate.

|         | •=··    |                                                                         |

|---------|---------|-------------------------------------------------------------------------|

| SRCON1x | SRCON0x | Description                                                             |

| 1       | 1       | Slew rate control is enabled<br>and is set to the slowest<br>edge rate. |

| 1       | 0       | Slew rate control is enabled<br>and is set to the slow edge<br>rate.    |

| 0       | 1       | Slew rate control is enabled<br>and is set to the medium<br>edge rate.  |

| 0       | 0       | Slew rate control is disabled and is set to the fastest                 |

TABLE 12-1: SLEW RATE CONTROL BIT SETTINGS

**Note:** By default, all of the Port pins are set to the fastest edge rate.

edge rate.

### 12.3 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

### 12.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option. PPS configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 12.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

#### 12.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART, SPI, and CAN), general purpose timer clock inputs, timer-related peripherals (input capture and output compare), interrupt-on-change inputs, and reference clocks (input and output).

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

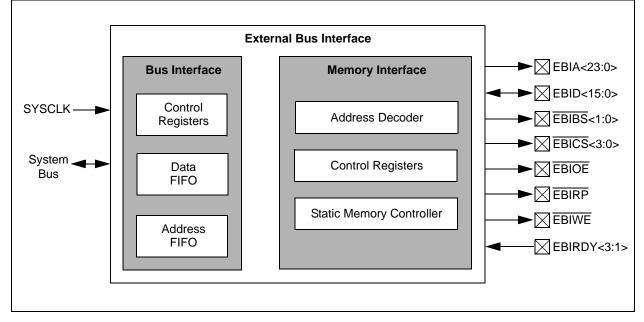

## 24.0 EXTERNAL BUS INTERFACE (EBI)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 47. "External Bus Interface (EBI)" (DS60001245) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The External Bus Interface (EBI) module provides a high-speed, convenient way to interface external parallel memory devices to the PIC32MZ EF family device.

With the EBI module, it is possible to connect asynchronous SRAM and NOR Flash devices, as well as non-memory devices such as camera sensors and LCDs.

The features of the EBI module depend on the pin count of the PIC32MZ EF device, as shown in Table 24-1.

Note: The EBI module is not available on 64-pin devices.

#### TABLE 24-1: EBI MODULE FEATURES

| Feature                   | Number of Device<br>Pins |     |     |  |  |  |

|---------------------------|--------------------------|-----|-----|--|--|--|

|                           | 100                      | 124 | 144 |  |  |  |

| Async SRAM                | Y                        | Y   | Y   |  |  |  |

| Async NOR Flash           | Y                        | Y   | Y   |  |  |  |

| Available address lines   | 20                       | 20  | 24  |  |  |  |

| 8-bit data bus support    | Y                        | Y   | Y   |  |  |  |

| 16-bit data bus support   | Y                        | Y   | Y   |  |  |  |

| Available Chip Selects    | 1                        | 1   | 4   |  |  |  |

| Timing mode sets          | 3                        | 3   | 3   |  |  |  |

| 8-bit R/W from 16-bit bus | N                        | Ν   | Y   |  |  |  |

| Non-memory device         | Y                        | Y   | Y   |  |  |  |

| LCD                       | Y                        | Y   | Y   |  |  |  |

Note: Once the EBI module is configured, external devices will be memory mapped and can be access from KSEG2 memory space (see Figure 4-1 through Figure 4-4 in Section 4.0 "Memory Organization" for more information). The MMU must be enabled and the TLB must be set up to access this memory (refer to Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) of the *"PIC32 Family Reference Manual"* for more information).

### FIGURE 24-1: EBI SYSTEM BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        | EF                | RRMODE<2:0        | >                 |                   | ERROP<2:0>        | ERRPHASE<1:0>     |                  |                  |  |  |

| 22.16        | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | —                 | —                 |                   | BDSTAT            | START             | ACTIVE            |                  |                  |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | BDCTRL<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BDCTRI            | _<7:0>            |                   |                  |                  |  |  |

#### **REGISTER 26-5: CESTAT: CRYPTO ENGINE STATUS REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-29 ERRMODE<2:0>: Internal Error Mode Status bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CEK operation

- 010 = KEK operation

- 001 = Preboot authentication

- 000 = Normal operation

#### bit 28-26 ERROP<2:0>: Internal Error Operation Status bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 = Authentication

- 011 = Reserved

- 010 = Decryption

- 001 = Encryption

- 000 = Reserved

#### bit 25-24 ERRPHASE<1:0>: Internal Error Phase of DMA Status bits

- 11 = Destination data

- 10 = Source data

- 01 = Security Association (SA) access

- 00 = Buffer Descriptor (BD) access

#### bit 23-22 Unimplemented: Read as '0'

#### bit 21-18 BDSTATE<3:0>: Buffer Descriptor Processor State Status bits

The current state of the BDP:

- 1111 = Reserved

- •

- 0111 = Reserved

- 0110 = SA fetch

- 0101 = Fetch BDP is disabled

- 0100 = Descriptor is done

- 0011 = Data phase

- 0010 = BDP is loading

- 0001 = Descriptor fetch request is pending

- 0000 = BDP is idle

- bit 17 START: DMA Start Status bit

- 1 = DMA start has occurred

- 0 = DMA start has not occurred

#### REGISTER 28-1: ADCCON1: ADC CONTROL REGISTER 1 (CONTINUED)

bit 3 STRGLVL: Scan Trigger High Level/Positive Edge Sensitivity bit

- 1 = Scan trigger is high level sensitive. Once STRIG mode is selected (TRGSRCx<4:0> in the ADCTRGx register), the scan trigger will continue for all selected analog inputs, until the STRIG option is removed.

- 0 = Scan trigger is positive edge sensitive. Once STRIG mode is selected (TRGSRCx<4:0> in the ADCTRGx register), only a single scan trigger will be generated, which will complete the scan of all selected analog inputs.

- bit 2-0 Unimplemented: Read as '0'

#### REGISTER 28-3: ADCCON3: ADC CONTROL REGISTER 3 (CONTINUED)

- bit 18 **DIGEN2:** ADC2 Digital Enable bit 1 = ADC2 is digital enabled

- 0 = ADC2 is digital disabled

- bit 17 DIGEN1: ADC1 Digital Enable bit

- 1 = ADC1 is digital enabled

- 0 = ADC1 is digital disabled

- bit 16 **DIGEN0:** ADC0 Digital Enable bit 1 = ADC0 is digital enabled 0 = ADC0 is digital disabled

- bit 15-13 VREFSEL<2:0>: Voltage Reference (VREF) Input Selection bits

| VREFSEL<2:0> | ADREF+               | ADREF-         |  |  |

|--------------|----------------------|----------------|--|--|

| 1xx          | Reserved; do not use |                |  |  |

| 011          | External VREFH       | External VREFL |  |  |

| 010          | AVdd                 | External VREFL |  |  |

| 001          | External VREFH       | AVss           |  |  |

| 000          | AVdd                 | AVss           |  |  |

bit 12 TRGSUSP: Trigger Suspend bit

1 = Triggers are blocked from starting a new analog-to-digital conversion, but the ADC module is not disabled 0 = Triggers are not blocked

- bit 11 UPDIEN: Update Ready Interrupt Enable bit

- $\ensuremath{\mathtt{1}}$  = Interrupt will be generated when the UPDRDY bit is set by hardware

- 0 = No interrupt is generated

- bit 10 UPDRDY: ADC Update Ready Status bit

- 1 = ADC SFRs can be updated

- 0 = ADC SFRs cannot be updated

**Note:** This bit is only active while the TRGSUSP bit is set and there are no more running conversions of any ADC modules.

- bit 9 SAMP: Class 2 and Class 3 Analog Input Sampling Enable bit<sup>(1,2,3,4)</sup>

- 1 = The ADC S&H amplifier is sampling

- 0 = The ADC S&H amplifier is holding

- bit 8 **RQCNVRT:** Individual ADC Input Conversion Request bit

This bit and its associated ADINSEL<5:0> bits enable the user to individually request an analog-to-digital conversion of an analog input through software.

- 1 = Trigger the conversion of the selected ADC input as specified by the ADINSEL<5:0> bits

- 0 =Do not trigger the conversion

**Note:** This bit is automatically cleared in the next ADC clock cycle.

- bit 7 GLSWTRG: Global Level Software Trigger bit

- 1 = Trigger conversion for ADC inputs that have selected the GLSWTRG bit as the trigger signal, either through the associated TRGSRC<4:0> bits in the ADCTRGx registers or through the STRGSRC<4:0> bits in the ADCCON1 register

- 0 = Do not trigger an analog-to-digital conversion

- **Note 1:** The SAMP bit has the highest priority and setting this bit will keep the S&H circuit in Sample mode until the bit is cleared. Also, usage of the SAMP bit will cause settings of SAMC<9:0> bits (ADCCON2<25:16>) to be ignored.

- 2: The SAMP bit only connects Class 2 and Class 3 analog inputs to the shared ADC, ADC7. All Class 1 analog inputs are not affected by the SAMP bit.

- **3:** The SAMP bit is not a self-clearing bit and it is the responsibility of application software to first clear this bit and only after setting the RQCNVRT bit to start the analog-to-digital conversion.

- 4: Normally, when the SAMP and RQCNVRT bits are used by software routines, all TRGSRCx<4:0> bits and STRGSRC<4:0> bits should be set to '00000' to disable all external hardware triggers and prevent them from interfering with the software-controlled sampling command signal SAMP and with the software-controlled trigger RQCNVRT.

#### REGISTER 28-14: ADCCMPENX: ADC DIGITAL COMPARATOR 'x' ENABLE REGISTER ('x' = 1 THROUGH 6)

|              |                       | <b>(</b>              |                       |                       |                       |                       |                       |                       |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

| 24.24        | R/W-0                 |

| 31:24        | CMPE31 <sup>(1)</sup> | CMPE30 <sup>(1)</sup> | CMPE29 <sup>(1)</sup> | CMPE28 <sup>(1)</sup> | CMPE27 <sup>(1)</sup> | CMPE26 <sup>(1)</sup> | CMPE25 <sup>(1)</sup> | CMPE24 <sup>(1)</sup> |

| 00.40        | R/W-0                 |

| 23:16        | CMPE23 <sup>(1)</sup> | CMPE22 <sup>(1)</sup> | CMPE21 <sup>(1)</sup> | CMPE20 <sup>(1)</sup> | CMPE19 <sup>(1)</sup> | CMPE18                | CMPE17                | CMPE16                |

| 45.0         | R/W-0                 |

| 15:8         | CMPE15                | CMPE14                | CMPE13                | CMPE12                | CMPE11                | CMPE10                | CMPE9                 | CMPE8                 |

| 7.0          | R/W-0                 |

| 7:0          | CMPE7                 | CMPE6                 | CMPE5                 | CMPE4                 | CMPE3                 | CMPE2                 | CMPE1                 | CMPE0                 |

|              | -                     | •                     | •                     | •                     | -                     | -                     |                       | -                     |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-0 CMPE31:CMPE0: ADC Digital Comparator 'x' Enable bits<sup>(2,3)</sup>

These bits enable conversion results corresponding to the Analog Input to be processed by the Digital Comparator. CMPE0 enables AN0, CMPE1 enables AN1, and so on.

**Note 1:** This bit is not available on 64-pin devices.

- **2**: CMPEx = ANx, where 'x' = 0.31 (Digital Comparator inputs are limited to AN0 through AN31).

- **3:** Changing the bits in this register while the Digital Comparator is enabled (ENDCMP = 1) can result in unpredictable behavior.

| Bit Range                                                | Bit                                                                                                                                                                                                                                      | Bit                                                                                                                                                                                                                                                                                                                                                                         | Bit                                                                                                                                                                                                                   | Bit                                                                                                                                     | Bit                                                                                      | Bit                                                                               | Bit                                                                                                               | Bit                                                                              |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| U                                                        | 31/23/15/7                                                                                                                                                                                                                               | 30/22/14/6                                                                                                                                                                                                                                                                                                                                                                  | 29/21/13/5                                                                                                                                                                                                            | 28/20/12/4                                                                                                                              | 27/19/11/3                                                                               | 26/18/10/2                                                                        | 25/17/9/1                                                                                                         | 24/16/8/0                                                                        |

| 31:24                                                    | U-0                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                   | R/W-0                                                                                                                                   | R/W-0                                                                                    | R/W-0                                                                             | R/W-1                                                                                                             | R/W-1                                                                            |

| 01.21                                                    | —                                                                                                                                                                                                                                        | —                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                     |                                                                                                                                         | ADCEIS<2:0>                                                                              |                                                                                   |                                                                                                                   | S<1:0>                                                                           |

| 23:16                                                    | U-0                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                 | R/W-0                                                                                                                                   | R/W-0                                                                                    | R/W-0                                                                             | R/W-0                                                                                                             | R/W-0                                                                            |

|                                                          | —                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                                                                                                                                         | ADCDIV<6:0>                                                                              |                                                                                   | DAMA                                                                                                              | DAMO                                                                             |

| 15:8                                                     | U-0                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                   | U-0                                                                                                                                     | U-0                                                                                      | U-0                                                                               | R/W-0                                                                                                             | R/W-0<br>C<9:8>                                                                  |

|                                                          | <br>R/W-0                                                                                                                                                                                                                                | <br>R/W-0                                                                                                                                                                                                                                                                                                                                                                   | <br>R/W-0                                                                                                                                                                                                             | <br>R/W-0                                                                                                                               | <br>R/W-0                                                                                | <br>R/W-0                                                                         | R/W-0                                                                                                             | <9.6><br>R/W-0                                                                   |

| 7:0                                                      | 10/00-0                                                                                                                                                                                                                                  | 17/10-0                                                                                                                                                                                                                                                                                                                                                                     | 10/00-0                                                                                                                                                                                                               | SAMC                                                                                                                                    |                                                                                          | 17/17-0                                                                           | 17/17-0                                                                                                           | 10/10-0                                                                          |

| Legend:                                                  |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                                                                                                                                         |                                                                                          |                                                                                   |                                                                                                                   |                                                                                  |

| R = Readat                                               | ole hit                                                                                                                                                                                                                                  | W = Writable                                                                                                                                                                                                                                                                                                                                                                | hit                                                                                                                                                                                                                   | II – Unimple                                                                                                                            | emented bit, r                                                                           | ead as 'O'                                                                        |                                                                                                                   |                                                                                  |

| -n = Value a                                             |                                                                                                                                                                                                                                          | 1' = Bit is se                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                       | $0^{\circ} = \text{Bit is cl}$                                                                                                          |                                                                                          | x = Bit is unl                                                                    | known                                                                                                             |                                                                                  |

|                                                          |                                                                                                                                                                                                                                          | 1 – Dit 13 36                                                                                                                                                                                                                                                                                                                                                               | ι.                                                                                                                                                                                                                    |                                                                                                                                         | ealeu                                                                                    |                                                                                   | KIIOWII                                                                                                           |                                                                                  |

| oit 31-29                                                | Unimpleme                                                                                                                                                                                                                                | nted: Read a                                                                                                                                                                                                                                                                                                                                                                | s'0'                                                                                                                                                                                                                  |                                                                                                                                         |                                                                                          |                                                                                   |                                                                                                                   |                                                                                  |

| bit 28-26                                                | •                                                                                                                                                                                                                                        | 0>: ADCx Ear                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                       | elect bits                                                                                                                              |                                                                                          |                                                                                   |                                                                                                                   |                                                                                  |

|                                                          |                                                                                                                                                                                                                                          | lata ready inte                                                                                                                                                                                                                                                                                                                                                             | •                                                                                                                                                                                                                     |                                                                                                                                         | clocks prior to                                                                          | o the end of c                                                                    | conversion                                                                                                        |                                                                                  |

|                                                          |                                                                                                                                                                                                                                          | lata ready inte                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                                                                                                                                         |                                                                                          |                                                                                   |                                                                                                                   |                                                                                  |

|                                                          | •                                                                                                                                                                                                                                        | 2                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                       |                                                                                                                                         |                                                                                          |                                                                                   |                                                                                                                   |                                                                                  |

|                                                          | •                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                                                                                                                                         |                                                                                          |                                                                                   |                                                                                                                   |                                                                                  |

|                                                          | •<br>001 – The d                                                                                                                                                                                                                         | lata ready inte                                                                                                                                                                                                                                                                                                                                                             | errunt is dene                                                                                                                                                                                                        | rated 2 ADC                                                                                                                             | clocks prior to                                                                          | the end of c                                                                      | onversion                                                                                                         |                                                                                  |

|                                                          |                                                                                                                                                                                                                                          | lata ready inte                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                       |                                                                                                                                         |                                                                                          |                                                                                   |                                                                                                                   |                                                                                  |

|                                                          |                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                           | June prilo goilo                                                                                                                                                                                                      |                                                                                                                                         | 0.00.000                                                                                 |                                                                                   |                                                                                                                   |                                                                                  |

|                                                          |                                                                                                                                                                                                                                          | All ontions are                                                                                                                                                                                                                                                                                                                                                             | availahla wi                                                                                                                                                                                                          | han tha salar                                                                                                                           | tad resolutio                                                                            | n snacifiad l                                                                     |                                                                                                                   | ES-1.05 h                                                                        |

|                                                          |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                             | e available wl                                                                                                                                                                                                        |                                                                                                                                         |                                                                                          |                                                                                   | by the SELR                                                                                                       |                                                                                  |

|                                                          | (                                                                                                                                                                                                                                        | ADCxTIME<2                                                                                                                                                                                                                                                                                                                                                                  | 25:24>), is 12·                                                                                                                                                                                                       | -bit or 10-bit.                                                                                                                         | For a selecte                                                                            | d resolution                                                                      | by the SELR<br>of 8-bit, option                                                                                   | n <mark>s from</mark> '00                                                        |

| oit 25-24                                                | (<br>t                                                                                                                                                                                                                                   | ADCxTIME<2<br>o '101' are va                                                                                                                                                                                                                                                                                                                                                | 25:24>), is 12<br>Ilid. For a sele                                                                                                                                                                                    | -bit or 10-bit.<br>ected resolution                                                                                                     | For a selecte                                                                            | d resolution                                                                      | by the SELR<br>of 8-bit, option                                                                                   | n <mark>s from</mark> '00                                                        |

| bit 25-24                                                | (<br>t                                                                                                                                                                                                                                   | ADCxTIME<2<br>o '101' are va<br><b>0&gt;:</b> ADCx Re                                                                                                                                                                                                                                                                                                                       | 25:24>), is 12<br>Ilid. For a sele                                                                                                                                                                                    | -bit or 10-bit.<br>ected resolution                                                                                                     | For a selecte                                                                            | d resolution                                                                      | by the SELR<br>of 8-bit, option                                                                                   | n <b>s from</b> '00                                                              |

| bit 25-24                                                | (<br>t<br>SELRES<1:                                                                                                                                                                                                                      | ADCxTIME<2<br>o '101' are va<br>a <b>0&gt;:</b> ADCx Re                                                                                                                                                                                                                                                                                                                     | 25:24>), is 12<br>Ilid. For a sele                                                                                                                                                                                    | -bit or 10-bit.<br>ected resolution                                                                                                     | For a selecte                                                                            | d resolution                                                                      | by the SELR<br>of 8-bit, option                                                                                   | n <b>s from</b> '00                                                              |

| bit 25-24                                                | (<br>t<br>SELRES<1:<br>11 = 12 bits                                                                                                                                                                                                      | ADCxTIME<2<br>o '101' are va<br>a <b>0&gt;:</b> ADCx Re                                                                                                                                                                                                                                                                                                                     | 25:24>), is 12<br>Ilid. For a sele                                                                                                                                                                                    | -bit or 10-bit.<br>ected resolution                                                                                                     | For a selecte                                                                            | d resolution                                                                      | by the SELR<br>of 8-bit, option                                                                                   | n <b>s from</b> '00                                                              |