Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | MIPS32® M-Class                                                                  |

| Core Size                 | 32-Bit Single-Core                                                               |

| peed                      | 200MHz                                                                           |

| Connectivity              | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG          |

| Peripherals               | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| lumber of I/O             | 78                                                                               |

| rogram Memory Size        | 1MB (1M x 8)                                                                     |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AM Size                   | 512K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| ata Converters            | A/D 40x12b                                                                       |

| Oscillator Type           | Internal                                                                         |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Nounting Type             | Surface Mount                                                                    |

| ackage / Case             | 100-TQFP                                                                         |

| upplier Device Package    | 100-TQFP (14x14)                                                                 |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efg100-i-pf |

## TABLE 5: PIN NAMES FOR 144-PIN DEVICES (CONTINUED)

144-PIN LQFP AND TQFP (TOP VIEW)

PIC32MZ0512EF(E/F/K)144 PIC32MZ1024EF(G/H/M)144 PIC32MZ1024EF(E/F/K)144 PIC32MZ2048EF(G/H/M)144

144

1

| Pin<br>Number | Full Pin Name               |

|---------------|-----------------------------|

| 73            | VBUS                        |

| 74            | VUSB3V3                     |

| 75            | Vss                         |

| 76            | D-                          |

| 77            | D+                          |

| 78            | RPF3/USBID/RF3              |

| 79            | SDA3/RPF2/RF2               |

| 80            | SCL3/RPF8/RF8               |

| 81            | ERXD0/RH8                   |

| 82            | ERXD3/RH9                   |

| 83            | ECOL/RH10                   |

| 84            | EBIRDY2/RH11                |

| 85            | SCL2/RA2                    |

| 86            | EBIRDY1/SDA2/RA3            |

| 87            | EBIA14/PMCS1/PMA14/RA4      |

| 88            | VDD                         |

| 89            | Vss                         |

| 90            | EBIA9/RPF4/SDA5/PMA9/RF4    |

| 91            | EBIA8/RPF5/SCL5/PMA8/RF5    |

| 92            | EBIA18/RK4                  |

| 93            | EBIA19/RK5                  |

| 94            | EBIA20/RK6                  |

| 95            | RPA14/SCL1/RA14             |

| 96            | RPA15/SDA1/RA15             |

| 97            | EBIA15/RPD9/PMCS2/PMA15/RD9 |

| 98            | RPD10/SCK4/RD10             |

| 99            | EMDC/RPD11/RD11             |

| 100           | ECRS/RH12                   |

| 101           | ERXDV/ECRSDV/RH13           |

| 102           | RH14                        |

| 103           | EBIA23/RH15                 |

| 104           | RPD0/RTCC/INT0/RD0          |

| 105           | SOSCI/RPC13/RC13            |

| 106           | SOSCO/RPC14/T1CK/RC14       |

| 107           | VDD                         |

| 108           | Vss                         |

| Pin<br>Number | Full Pin Name           |

|---------------|-------------------------|

| 109           | RPD1/SCK1/RD1           |

| 110           | EBID14/RPD2/PMD14/RD2   |

| 111           | EBID15/RPD3/PMD15/RD3   |

| 112           | EBID12/RPD12/PMD12/RD12 |

| 113           | EBID13/PMD13/RD13       |

| 114           | ETXERR/RJ0              |

| 115           | EMDIO/RJ1               |

| 116           | EBIRDY3/RJ2             |

| 117           | EBIA22/RJ3              |

| 118           | SQICS0/RPD4/RD4         |

| 119           | SQICS1/RPD5/RD5         |

| 120           | ETXEN/RPD6/RD6          |

| 121           | ETXCLK/RPD7/RD7         |

| 122           | VDD                     |

| 123           | Vss                     |

| 124           | EBID11/RPF0/PMD11/RF0   |

| 125           | EBID10/RPF1/PMD10/RF1   |

| 126           | EBIA21/RK7              |

| 127           | EBID9/RPG1/PMD9/RG1     |

| 128           | EBID8/RPG0/PMD8/RG0     |

| 129           | TRCLK/SQICLK/RA6        |

| 130           | TRD3/SQID3/RA7          |

| 131           | EBICS0/RJ4              |

| 132           | EBICS1/RJ5              |

| 133           | EBICS2/RJ6              |

| 134           | EBICS3/RJ7              |

| 135           | EBID0/PMD0/RE0          |

| 136           | Vss                     |

| 137           | VDD                     |

| 138           | EBID1/PMD1/RE1          |

| 139           | TRD2/SQID2/RG14         |

| 140           | TRD1/SQID1/RG12         |

| 141           | TRD0/SQID0/RG13         |

| 142           | EBID2/PMD2/RE2          |

| 143           | EBID3/RPE3/PMD3/RE3     |

| 144           | EBID4/AN18/PMD4/RE4     |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.4 "Peripheral Pin Select (PPS)" for restrictions.

<sup>2:</sup> Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See Section 12.0 "I/O Ports" for more information.

<sup>3:</sup> Shaded pins are 5V tolerant.

|   | c | ,        |

|---|---|----------|

|   | Q | Ō        |

|   | č | "        |

|   | ۲ | 3        |

|   | - | <u>.</u> |

| i | Ň | š        |

|   | c | 2        |

|   | è | 5        |

| , | ٥ | Š        |

|   | a | 5        |

|   | ç | o        |

| 1 | u | v        |

TABLE 4-14: SYSTEM BUS TARGET 6 REGISTER MAP

| ess                         |                  |           |       |       |       |          |          |       |          |      | Bits        |       |          |      |        |        |          |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|----------|------|-------------|-------|----------|------|--------|--------|----------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9     | 24/8 | 23/7        | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1     | 16/0   | All<br>Resets |

| 9820                        | SBT6ELOG1        | 31:16     | MULTI | _     | _     | _        |          | CODE  | <3:0>    |      | _           | _     | _        | _    | _      | _      | _        | _      | 0000          |

| 3020                        | OBTOLLOGT        | 15:0      |       |       |       | INIT     | TD<7:0>  |       |          |      |             | REGIO | N<3:0>   |      | _      | С      | CMD<2:0> |        |               |

| 9824                        | SBT6ELOG2        | 31:16     | _     | _     | _     | _        | _        | _     | _        | _    | _           | _     | _        | _    | _      | _      | _        | _      | 0000          |

| 3024                        | OBTOLLOGE        | 15:0      | _     | _     | _     | _        | _        | _     | _        | _    | _           | _     | _        | _    | _      | _      | GROU     | P<1:0> | 0000          |

| 9828                        | SBT6ECON         | 31:16     | _     | _     | _     | _        |          | _     | _        | ERRP | _           | _     | _        | _    | _      | _      | _        | _      | 0000          |

| 3020                        | SBIOLOGIA        | 15:0      | _     | _     | _     | _        |          | _     | _        |      | _           | _     | _        | _    | _      | _      | _        | _      | 0000          |

| 9830                        | SBT6ECLRS        | 31:16     | _     | _     | _     | _        | _        | _     | _        | _    | _           | _     | _        | _    | _      | _      | _        | _      | 0000          |

| 3000                        | OBTOLOLINO       | 15:0      | _     | _     | _     | _        | _        | _     | _        | _    | _           | _     | _        | _    | _      | _      | _        | CLEAR  | 0000          |

| 9838                        | SBT6ECLRM        | 31:16     | _     | _     | _     | _        | _        | _     | _        | _    | _           | _     | _        | _    | _      | _      | _        | _      | 0000          |

| 0000                        | OBTOLOLINI       | 15:0      | _     | _     | _     | _        | _        | _     | _        | _    | _           | _     | _        | _    | _      | _      | _        | CLEAR  | 0000          |

| 9840                        | SBT6REG0         | 31:16     |       |       |       |          |          |       | 1        | BA   | SE<21:6>    |       |          |      |        |        |          |        | xxxx          |

| 00.0                        |                  | 15:0      |       | •     | BA    | \SE<5:0> |          |       | PRI      | _    |             |       | SIZE<4:0 | >    |        | _      | _        | _      | xxxx          |

| 9850                        | SBT6RD0          | 31:16     | _     | _     | _     | _        | _        | _     |          | _    |             |       |          |      | _      | _      | _        | _      | xxxx          |

|                             |                  | 15:0      | _     | _     | _     | _        | _        | _     |          | _    |             |       |          |      | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 9858                        | SBT6WR0          | 31:16     | _     | _     | _     | _        | _        | _     |          | _    |             |       |          |      | _      | _      | _        | _      | xxxx          |

|                             |                  | 15:0      | _     | _     | _     | _        | _        | _     | _        | _    | _           | _     | _        | _    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 9860                        | SBT6REG1         | 31:16     |       |       |       |          |          |       |          | BA   | BASE<21:6>  |       |          |      |        |        |          | 1      | xxxx          |

|                             |                  | 15:0      |       |       | BA    | \SE<5:0> |          | I     | PRI      | _    | - SIZE<4:0> |       |          |      |        |        | _        | _      | xxxx          |

| 9870                        | SBT6RD1          | 31:16     | _     | _     | _     |          |          |       |          |      |             |       |          |      | _      | _      | _        | _      | xxxx          |

|                             | - ***-           | 15:0      | _     | _     | _     | _        | _        | _     | _        | _    | _           | _     | _        | _    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 9878                        | SBT6WR1          | 31:16     | _     | _     | _     | _        | _        | _     | _        | _    | _           | _     | _        | _    | _      | _      | _        | _      | xxxx          |

|                             |                  | 15:0      | _     | _     | _     | _        | <u> </u> | _     | <u> </u> |      | _           | _     |          |      | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

TABLE 4-21: SYSTEM BUS TARGET 13 REGISTER MAP

| ess                         |                  |           |       |       |       |         |            |       |       |                   | Bits     |       |        |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|---------|------------|-------|-------|-------------------|----------|-------|--------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11      | 26/10 | 25/9  | 24/8              | 23/7     | 22/6  | 21/5   | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             | SBT13ELOG1       | 31:16     | MULTI | _     | _     | 1       |            | CODE  | <3:0> |                   | 1        | -     | _      | _    | _      | 1      | _       | _      | 0000          |

| D420                        | SBITSELOGI       | 15:0      |       |       |       | INI     | NITID<7:0> |       |       |                   |          | REGIO | N<3:0> |      | _      | С      | MD<2:0> |        | 0000          |

| D404                        | SBT13ELOG2       | 31:16     | _     | _     | _     | _       | _          | _     | -     | _                 | 1        | _     | _      | _    | _      | _      | _       | _      | 0000          |

| D424                        | SB113ELOG2       | 15:0      | -     | _     | _     | ı       | -          | 1     | I     | -                 | 1        | 1     | 1      | _    | _      | I      | GROU    | P<1:0> | 0000          |

| B428                        | SBT13ECON        | 31:16     | _     | _     | _     | _       | _          | _     | _     | ERRP              | _        | _     | _      | _    | _      | _      | _       | _      | 0000          |

| D420                        | SBITSECON        | 15:0      | _     | _     | _     | _       | _          | _     | _     | _                 | _        | _     | _      | _    | _      | _      | _       | _      | 0000          |

| D420                        | SBT13ECLRS       | 31:16     | _     | _     | _     | _       | _          | _     | ı     | _                 | -        | -     | 1      | _    | _      | ı      | _       | _      | 0000          |

| D430                        | SBITSECERS       | 15:0      | -     | _     | _     | ı       | -          | 1     | I     | -                 | 1        | 1     | 1      | _    | _      | I      | 1       | CLEAR  | 0000          |

| D420                        | SBT13ECLRM       | 31:16     | _     | _     | _     | _       | _          | _     | ı     | _                 | -        | -     | 1      | _    | _      | ı      | _       | _      | 0000          |

| D430                        | SB113ECLRIVI     | 15:0      | _     | _     | _     | _       | _          | _     | _     | _                 | _        | _     | _      | _    | _      | _      | _       | CLEAR  | 0000          |

| B440                        | SBT13REG0        | 31:16     |       |       |       |         |            |       |       | BA                | SE<21:6> |       |        |      |        |        |         |        | xxxx          |

| D440                        | SBITSREGU        | 15:0      |       |       | BA    | SE<5:0> |            |       | PRI   | I — SIZE<4:0> — - |          |       |        |      |        | _      | _       | xxxx   |               |

| B450                        | SBT13RD0         | 31:16     | _     | _     | _     | _       | _          | _     | _     | _                 | _        | _     | _      | _    | _      | _      | _       | _      | xxxx          |

| B450                        | 3B113RD0         | 15:0      | _     | _     | _     | _       | _          | _     | _     | _                 | _        | _     | _      | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| B458                        | SBT13WR0         | 31:16     | _     | _     | _     | _       | _          | _     | 1     | _                 |          | _     | _      | _    | _      | -      | _       | _      | xxxx          |

| D438                        | SDIISWKU         | 15:0      | _     | _     | _     | _       | _          | _     | _     | _                 | _        | _     | _      | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note:** For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| ഗ       |

|---------|

| S600013 |

| 0       |

| 0       |

| 0       |

| _       |

| ω       |

| N       |

| 320[    |

|         |

| u       |

| Ÿ       |

| 끅       |

| 끅       |

| 끅       |

| ģ       |

| 끅       |

| 끅       |

| 끅       |

| 끅       |

| <b>TABLE 7-3:</b> | INTERRUPT REGISTER MAP ( | (CONTINUED) |

|-------------------|--------------------------|-------------|

|                   |                          |             |

| ress<br>()                  |                                 |           |       |       |       |       |       | •     |      | Bi         | ts   |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

| 0744                        | OFF153                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | -          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 07A4                        | OFF 153                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0740                        | OFF154                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | -    | -    | _    | _    | VOFF< | 17:16> | 0000       |

| UTAO                        | OFF 134                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0740                        | OFF155                          | 31:16     | _     | _     | _     | _     | _     | _     | -    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| UTAC                        | OFF 133                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0780                        | OFF156                          | 31:16     | _     | ı     | _     | _     | 1     |       | I    | _          | _    | 1    | -    |      | ı    | 1    | VOFF< | 17:16> | 0000       |

| 0760                        | OFF 130                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 07B4                        | OFF157                          | 31:16     | _     | ı     | _     | _     |       | _     | ı    | _          | -    | ı    | -    | -    | -    | -    | VOFF< | 17:16> | 0000       |

| 0764                        | OFF 137                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 07B8                        | OFF158                          | 31:16     | _     |       | _     | _     | -     | _     |      | _          | _    | -    | -    | _    | -    | -    | VOFF< | 17:16> | 0000       |

| 0766                        | OFF 136                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0700                        | OFF159                          | 31:16     | _     | ı     | _     | _     | 1     |       | I    | _          | _    | 1    | -    |      | ı    | 1    | VOFF< | 17:16> | 0000       |

| UIBC                        | OFF 139                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0700                        | OFF160                          | 31:16     | _     | -     | _     | _     |       | _     | -    | _          | _    | -    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0700                        | OFF 160                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0704                        | OFF161                          | 31:16     | _     |       | _     | _     | -     | _     |      | _          | _    | -    | -    | _    | -    | -    | VOFF< | 17:16> | 0000       |

| 0704                        | OFFIGI                          | 15:0      |       |       | •     |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      | •     | _      | 0000       |

| 0708                        | OFF162                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0700                        | 011102                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0700                        | OFF163                          | 31:16     | _     | -     | _     | _     | _     | _     | -    | _          | _    | -    | _    | _    | -    | _    | VOFF< | 17:16> | 0000       |

| 0700                        | 011103                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0700                        | OFF164                          | 31:16     | _     |       | _     | _     | -     | _     |      | _          | _    | -    | -    | _    | -    | -    | VOFF< | 17:16> | 0000       |

| 0700                        | OFF 104                         | 15:0      |       |       | •     |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      | •     | _      | 0000       |

| 0704                        | OFF165                          | 31:16     | _     | 1     | _     | _     | -     | _     | -    | _          | _    | 1    | _    | _    | 1    | _    | VOFF< | 17:16> | 0000       |

| 0704                        | 011103                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0708                        | OFF166                          | 31:16     | _     | _     |       |       |       |       | _    | _          |      |      |      |      | _    | _    | VOFF< | 17:16> | 0000       |

| 0100                        | 011100                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0700                        | OFF167                          | 31:16     | _     | _     | _     | _     | -     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0700                        | OI F 107                        | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

- All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: Registers" for more information.

- This bit or register is not available on 64-pin devices.

- This bit or register is not available on devices without a CAN module.

- 4: This bit or register is not available on 100-pin devices.

- Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

- 6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

- 7: 8: This bit or register is not available on devices without a Crypto module.

- This bit or register is not available on 124-pin devices.

| TABLE 10-3: | DMA CHANNEL | <b>0 THROUGH CHANNEL</b> | 7 REGISTER MAP |

|-------------|-------------|--------------------------|----------------|

| IADEE IV-J. |             | O IIIIXOOOII OIIAINILE   |                |

| ess                         |                                 |               |                       |          |             |           |                 |            |            | Bit       | s             |        |        |        |        |        |         |          | "          |

|-----------------------------|---------------------------------|---------------|-----------------------|----------|-------------|-----------|-----------------|------------|------------|-----------|---------------|--------|--------|--------|--------|--------|---------|----------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                 | 30/14    | 29/13       | 28/12     | 27/11           | 26/10      | 25/9       | 24/8      | 23/7          | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1    | 16/0     | All Resets |

|                             | BOLLOOON                        | 31:16         | •                     |          | •           | CHPIG     | N<7:0>          |            | •          | •         | _             | _      | _      | _      | _      | _      | _       | _        | 0000       |

| 1060                        |                                 |               |                       |          |             |           |                 |            |            | CHEDET    | ET CHPRI<1:0> |        |        |        |        |        |         |          |            |

| 1070                        | DCH0ECON                        | 31:16         | _                     | _        | _           | _         | _               | _          | _          | _         |               |        |        | CHAIR  | Q<7:0> |        |         |          | 00FF       |

| 1070                        | DOI IOLOGIA                     | 15:0          |                       |          |             | CHSIR     | Q<7:0>          |            |            |           | CFORCE        |        | PATEN  | SIRQEN | AIRQEN | _      | _       |          | FF00       |

| 1080                        | DCH0INT                         | 31:16         | _                     |          | _           |           | _               |            | _          | _         | CHSDIE        | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE  | CHERIE   | 0000       |

| 1000                        | DOMONY                          | 15:0          | _                     | _        | _           | _         | _               | _          | _          | _         | CHSDIF        | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF  | CHERIF   | 0000       |

| 1090                        | DCH0SSA                         | 31:16<br>15:0 |                       |          |             |           |                 |            |            | CHSSA     | <31:0>        |        |        |        |        |        |         |          | 0000       |

| 10A0                        | DCH0DSA                         | 31:16<br>15:0 |                       |          |             |           |                 |            |            | CHDSA     | <31:0>        |        |        |        |        |        |         |          | 0000       |

| 4000                        | DOLLOCOLZ                       | 31:16         | _                     | _        | _           | _         | _               | _          | _          | _         | _             | _      | _      | _      | _      | _      | _       | _        | 0000       |

| 1080                        | DCH0SSIZ                        | 15:0          |                       |          |             |           |                 |            |            | CHSSIZ    | <15:0>        |        |        |        |        |        |         |          | 0000       |

| 1000                        | DCHODGIZ                        | 31:16         | _                     | _        | _           | _         | _               | _          | _          | _         | _             | _      | _      | _      | _      | _      | _       | _        | 0000       |

| 1000                        | DCH0DSIZ                        | 15:0          | 5:0 CHDSIZ<15:0> 0000 |          |             |           |                 |            |            |           |               |        |        |        |        |        |         |          |            |

| 1000                        | DCH0SPTR                        | 31:16         | _                     | _        | _           | _         | _               | _          | _          | _         | -             | _      | _      | _      | _      | _      | _       | _        | 0000       |

| 1000                        | DCHOSFIK                        | 15:0          |                       |          |             |           |                 |            |            | CHSPTR    | <15:0>        |        |        |        |        |        |         |          | 0000       |

| 10F0                        | DCH0DPTR                        | 31:16         | _                     |          | _           |           | _               |            | _          | _         | _             | _      | _      | _      | _      | _      | _       |          | 0000       |

| 1020                        | DOTIOD! TIX                     | 15:0          |                       |          |             |           |                 |            |            | CHDPTR    | <15:0>        |        |        |        |        |        |         |          | 0000       |

| 10F0                        | DCH0CSIZ                        | 31:16         | _                     | _        | _           | _         | _               | _          | _          | _         | _             | _      | _      | _      | _      | _      | _       | _        | 0000       |

| . 0. 0                      | 201.000.2                       | 15:0          |                       |          |             |           | 1               |            | 1          | CHCSIZ    | <15:0>        | 1      | I      | I      | I      | 1      |         |          | 0000       |

| 1100                        | DCH0CPTR                        | 31:16         | _                     | _        | _           | _         | _               |            | _          |           |               | _      | _      | _      | _      | _      | _       | _        | 0000       |

|                             |                                 | 15:0          |                       |          |             |           | 1               |            | 1          | CHCPTR    | <15:0>        | 1      |        |        |        | ı      |         |          | 0000       |

| 1110                        | DCH0DAT                         | 31:16         | _                     | _        | _           |           | _               |            | _          | OLIDDAT   |               | _      | _      | _      | _      | _      | _       | _        | 0000       |

|                             |                                 | 15:0          |                       |          |             |           |                 |            |            | CHPDAT    | <15:0>        |        |        |        |        |        |         |          | 0000       |

| 1120                        | DCH1CON                         | 31:16         |                       |          |             | CHPIG     |                 |            |            | T =       |               |        |        |        |        |        | _       |          | 0000       |

|                             |                                 | 15:0          | CHBUSY                |          | CHPIGNEN    |           | CHPATLEN        |            |            | CHCHNS    | CHEN          | CHAED  | CHCHN  | CHAEN  |        | CHEDET | CHPR    | I<1:0>   | 0000       |

| 1130                        | DCH1ECON                        | 31:16         | _                     | _        | _           | _         |                 |            | _          | _         | 050005        | CARORT | DATEN  | CHAIR  |        |        |         |          | 00FF       |

|                             |                                 | 15:0          |                       |          |             | CHSIR     | Q<7:0>          |            |            |           | CFORCE        | CABORT | PATEN  | SIRQEN | AIRQEN |        | CLITAIE | - CHEDIE | FF00       |

| 1140                        | DCH1INT                         | 31:16         | _                     |          | _           |           | _               |            | _          | _         | CHSDIE        | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE  | CHERIE   | 0000       |

|                             |                                 | 15:0          | _                     | _        | _           | _         | _               | _          | _          |           | CHODIF        | CHOULE | CHDDIF | CUDUIL | CHBCIF | CHCCIF | CHIAIF  | CHEKIF   | 0000       |

| 1150                        | DCH1SSA                         | 31:16<br>15:0 | CHSSAZ31:05           |          |             |           |                 |            |            |           |               |        |        |        | 0000   |        |         |          |            |

|                             |                                 | 31:16         |                       |          |             |           |                 |            |            |           |               |        |        |        |        |        |         |          |            |

| 1160                        | DCH1DSA                         | 15:0          | CHDSA<31:0>           |          |             |           |                 |            |            |           |               |        |        | 0000   |        |        |         |          |            |

| Leger                       |                                 |               | . value en D          | looot: - | unimplement | od rood o | s '0'. Reset va | duos oro s | hown in ho | vodocimal |               |        |        |        |        |        |         |          | 12200      |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

# REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7) (CONTINUED)

bit 15-11 MULT<4:0>: Multiplier Control bits

For Isochronous/Interrupt endpoints or of packet splitting on Bulk endpoints, multiplies TXMAXP by MULT+1 for the payload size.

For Bulk endpoints, MULT can be up to 32 and defines the number of "USB" packets of the specified payload into which a single data packet placed in the FIFO should be split, prior to transfer. The data packet is required to be an exact multiple of the payload specified by TXMAXP.

For Isochronous/Interrupts endpoints operating in Hi-Speed mode, MULT may be either 2 or 3 and specifies the maximum number of such transactions that can take place in a single microframe.

bit 10-0 TXMAXP<10:0>: Maximum TX Payload per transaction Control bits

This field sets the maximum payload (in bytes) transmitted in a single transaction. The value is subject to the constraints placed by the USB Specification on packet sizes for Bulk, Interrupt and Isochronous transfers in Full-Speed and Hi-Speed operations.

TXMAXP must be set to an even number of bytes for proper interrupt generation in DMA Mode 1.

## REGISTER 11-24: USBEXRPC: USB ENDPOINT 'x' REQUEST PACKET COUNT REGISTER (HOST MODE ONLY) ('x' = 1-7)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        |                   | _                 | _                 | _                 | _                 |                   | _                | _                |  |  |  |  |  |

| 23:16        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10        |                   | _                 | _                 | _                 | _                 |                   | _                | _                |  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15.6         |                   |                   |                   | RQPKTC            | NT<15:8>          |                   |                  |                  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7.0          | RQPKTCNT<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 RQPKTCNT<15:0>: Request Packet Count bits

Sets the number of packets of size MAXP that are to be transferred in a block transfer. This register is only available in *Host mode* when AUTOREQ is set.

#### REGISTER 11-25: USBDPBFD: USB DOUBLE PACKET BUFFER DISABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   |                   | _                 |                   | _                 | _                | _                |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 23.10        | EP7TXD            | EP6TXD            | EP5TXD            | EP4TXD            | EP3TXD            | EP2TXD            | EP1TXD           | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7:0          | EP7RXD            | EP6RXD            | EP5RXD            | EP4RXD            | EP3RXD            | EP2RXD            | EP1RXD           | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-17 EP7TXD:EP1TXD: TX Endpoint 'x' Double Packet Buffer Disable bits

1 = TX double packet buffering is disabled for endpoint 'x' 0 = TX double packet buffering is enabled for endpoint 'x'

bit 16 Unimplemented: Read as '0'

bit 15-1 EP7RXD: EP1RXD: RX Endpoint 'x' Double Packet Buffer Disable bits

1 = RX double packet buffering is disabled for endpoint 'x'

0 = RX double packet buffering is enabled for endpoint 'x'

bit 0 Unimplemented: Read as '0'

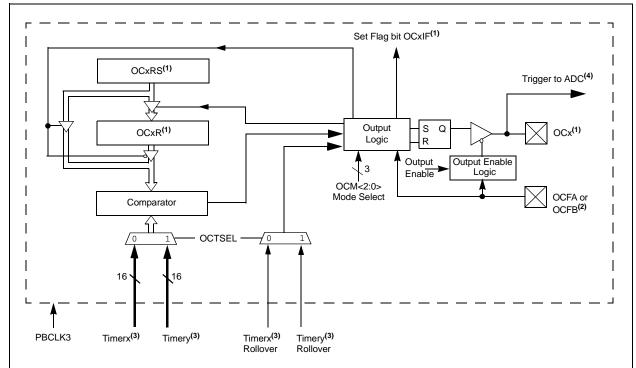

#### 18.0 OUTPUT COMPARE

Note:

This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events.

For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of the Output Compare module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- · Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Programmable selection of 16-bit or 32-bit time bases

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

- ADC event trigger

#### FIGURE 18-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

- Note 1: Where 'x' is shown, reference is made to the registers associated with the respective output compare channels, 1 through 9.

- 2: The OCFA pin controls the OC1, OC3, and OC7-OC9 channels. The OCFB pin controls the OC4-OC6 channels.

- 3: Refer to Table 18-1 for Timerx and Timery selections.

- 4: The ADC event trigger is only available on OC1, OC3, and OC 5.

### REGISTER 20-26: SQI1XCON4: SQI XIP CONTROL REGISTER 4

| Bit<br>Range | Bit<br>31/23/15/7             | Bit<br>30/22/14/6             | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------------------|-------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0                           | U-0                           | U-0               | R/W-0             | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | _                             | _                             | _                 | INIT2SCHECK       | INIT2CO           | UNT<1:0>          | INIT2TYPE<1:0>   |                  |  |  |  |  |  |

| 00:40        | R/W-0                         | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | INIT2CMD3<7:0>(1)             |                               |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0                         | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | INIT2CMD2<7:0> <sup>(1)</sup> |                               |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0                         | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                               | INIT2CMD1<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

R = Readable bit W = Writable bit-n = Value at POR '1' = Bit is set U = Unimplemented bit, read as '0'

'0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

Legend:

Note:

bit 28 INIT2SCHECK: Flash Initialization 2 Command Status Check bit

1 = Check the status after executing the INIT2 command

0 = Do not check the status

bit 27-26 INIT2COUNT<1:0>: Flash Initialization 2 Command Count bits

11 = INIT2CMD1, INIT2CMD2, and INIT2CMD3 are sent

10 = INIT2CMD1 and INIT2CMD2 are sent, but INIT2CMD3 is still pending

01 = INIT2CMD1 is sent, but INIT2CMD2 and INIT2CMD3 are still pending

00 = No commands are sent

bit 25-24 INIT2TYPE<1:0>: Flash Initialization 2 Command Type bits

11 = Reserved

10 = INIT2 commands are sent in Quad Lane mode

01 = INIT2 commands are sent in Dual Lane mode

00 = INIT2 commands are sent in Single Lane mode

bit 24-16 INIT2CMD3<7:0>: Flash Initialization Command 3 bits(1)

Third command of the Flash initialization.

bit 15-8 INIT2CMD2<7:0>: Flash Initialization Command 2 bits<sup>(1)</sup>

Second command of the Flash initialization.

bit 7-0 **INIT2CMD1<7:0>:** Flash Initialization Command 1 bits<sup>(1)</sup>

First command of the Flash initialization.

Note 1: INIT2CMD1 can be WEN and INIT2CMD2 can be SECTOR UNPROTECT.

Some Flash devices require Write Enable and Sector Unprotect commands before read/write operations and this register is useful in working with those Flash types (XIP mode only)

| ഗ         |

|-----------|

| ©         |

| 2         |

| $\approx$ |

| $\preceq$ |

| ώ         |

| $\simeq$  |

| జ         |

| Y         |

| g         |

| Š         |

| ĕ         |

| 363       |

|           |

TABLE 22-1: UART1 THROUGH UART6 REGISTER MAP (CONTINUED)

| ess                         |                       | •         |        |         |        |       |        |       |       | Bi          | ts          |         |       |          |          |      |        |       | "          |

|-----------------------------|-----------------------|-----------|--------|---------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name      | Bit Range | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 2600                        | U4MODE <sup>(1)</sup> | 31:16     | _      | _       | _      | _     | _      | -     | _     | _           | -           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      | ON     |         | SIDL   | IREN  | RTSMD  |       | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 2610                        | U4STA <sup>(1)</sup>  | 31:16     |        | _       | _      | _     | _      |       | _     | ADM_EN      |             |         | 1     | ADDR     |          | 1    | 1      |       | 0000       |

|                             |                       | 15:0      | UTXISE | L<1:0>  | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 2620                        | U4TXREG               | 31:16     |        | _       | _      |       | _      |       |       | _           |             | _       | _     |          | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      |        | _       | _      |       | _      |       | _     | TX8         |             | I       |       | Transmit | Register | 1    | I      |       | 0000       |

| 2630                        | U4RXREG               | 31:16     |        | _       | _      |       | _      |       | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      |        | _       | _      |       | _      |       | _     | RX8         |             | I       |       | Receive  | Register | 1    | I      |       | 0000       |

| 2640                        | U4BRG <sup>(1)</sup>  | 31:16     | _      | _       | _      | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 2800                        | U5MODE <sup>(1)</sup> | 31:16     |        | _       | _      | _     | _      |       | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             |                       | 15:0      | ON     | _       | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 2810                        | U5STA <sup>(1)</sup>  | 31:16     | _      | _       | _      | -     | _      | _     | _     | ADM_EN      |             |         |       | ADDR     |          |      |        | 1     | 0000       |

|                             |                       | 15:0      | UTXISE | L<1:0>  | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 2820                        | U5TXREG               | 31:16     | _      | _       | _      | -     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 2020                        |                       | 15:0      | _      | _       | _      | -     | _      | _     | _     | TX8         |             |         |       | Transmit | Register |      |        | 1     | 0000       |

| 2830                        | U5RXREG               | 31:16     | _      | _       | _      | -     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

|                             | 00.020                | 15:0      | _      | _       | _      | _     | _      | _     | _     | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 2840                        | U5BRG <sup>(1)</sup>  | 31:16     | _      | _       | _      | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 2010                        | CODICO                | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 2400                        | U6MODE <sup>(1)</sup> | 31:16     | _      | _       | _      | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 27100                       |                       | 15:0      | ON     | _       | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 2A10                        | U6STA <sup>(1)</sup>  | 31:16     | _      | _       | _      | -     | _      | _     | _     | ADM_EN      |             |         |       | ADDR     |          |      |        | 1     | 0000       |

|                             |                       | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 2A20                        | U6TXREG               | 31:16     | _      | _       | _      | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| _,0                         |                       | 15:0      | _      | _       | _      | _     | _      | _     | _     | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 2A30                        | U6RXREG               | 31:16     | _      | _       | _      | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      |       | 0000       |

| 2,100                       | SSICKILLO             | 15:0      | _      | _       | _      | _     | _      | _     | _     | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 2A40                        | U6BRG <sup>(1)</sup>  | 31:16     | _      | _       | _      | _     | _      | _     | _     | _           | _           | _       | _     | _        | _        | _    | _      | _     | 0000       |

| _,                          | CODICO                | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more informa-Note 1:

| DECICTED 20 2. | ADCCON3: ADC CON | TRAL DECISTER 2 |  |

|----------------|------------------|-----------------|--|

| REGISTER 28-3: | ADGGONS: ADG GON | TRUL REGISTER 3 |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|--|--|--|

| 24.24        | R/W-0                     | R/W-0            |  |  |  |  |

| 31:24        | ADCSE             | L<1:0>            |                   | CONCLKDIV<5:0>    |                   |                   |                           |                  |  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |  |  |

| 23:16        | DIGEN7            | _                 | _                 | DIGEN4            | DIGEN3            | DIGEN2            | DIGEN1                    | DIGEN0           |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0, HS, HC       | R/W-0                     | R-0, HS, HC      |  |  |  |  |

| 15:8         | V                 | REFSEL<2:0        | >                 | TRGSUSP           | UPDIEN            | UPDRDY            | SAMP <sup>(1,2,3,4)</sup> | RQCNVRT          |  |  |  |  |

| 7.0          | R/W-0             | R/W-0, HC         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |  |  |

| 7:0          | GLSWTRG           | GSWTRG            |                   |                   | ADINS             | SEL<5:0>          |                           |                  |  |  |  |  |

Legend:HC = Hardware SetHS = Hardware ClearedR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

```

bit 31-30 ADCSEL<1:0>: Analog-to-Digital Clock Source (TCLK) bits

```

11 = FRC

10 = REFCLK3

01 = System Clock (Tcy)

00 = PBCLK3

bit 29-24 CONCLKDIV<5:0>: Analog-to-Digital Control Clock (TQ) Divider bits

1111111 = 64 \* TCLK = TQ

•

000011 = 4 \* TCLK = TQ

000010 = 3 \* TCLK = TQ

000001 = 2 \* TCLK = TQ

000000 = TCLK = TQ

bit 23 DIGEN7: Shared ADC (ADC7) Digital Enable bit

1 = ADC7 is digital enabled

0 = ADC7 is digital disabled

bit 22-21 Unimplemented: Read as '0'

bit 20 **DIGEN4:** ADC4 Digital Enable bit

1 = ADC4 is digital enabled

0 = ADC4 is digital disabled

bit 19 DIGEN3: ADC3 Digital Enable bit

1 = ADC3 is digital enabled

0 = ADC3 is digital disabled

- Note 1: The SAMP bit has the highest priority and setting this bit will keep the S&H circuit in Sample mode until the bit is cleared. Also, usage of the SAMP bit will cause settings of SAMC<9:0> bits (ADCCON2<25:16>) to be ignored.

- 2: The SAMP bit only connects Class 2 and Class 3 analog inputs to the shared ADC, ADC7. All Class 1 analog inputs are not affected by the SAMP bit.

- **3:** The SAMP bit is not a self-clearing bit and it is the responsibility of application software to first clear this bit and only after setting the RQCNVRT bit to start the analog-to-digital conversion.

- **4:** Normally, when the SAMP and RQCNVRT bits are used by software routines, all TRGSRCx<4:0> bits and STRGSRC<4:0> bits should be set to '00000' to disable all external hardware triggers and prevent them from interfering with the software-controlled sampling command signal SAMP and with the software-controlled trigger RQCNVRT.

### REGISTER 29-21: CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' ('n' = 0-31)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2        | Bit<br>25/17/9/1        | Bit<br>24/16/8/0          |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|---------------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24        | _                 | _                 | _                 | _                 | 1                 | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |

| 00:40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16        | _                 | _                 | 1                 | _                 | RXOVFLIE          | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0                      | R-0                     | R-0                       |

| 15:8         | _                 | _                 | 1                 | _                 |                   | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R-0                      | R-0                     | R-0                       |

| 7:0          | _                 | _                 | _                 | _                 | RXOVFLIF          | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-27 Unimplemented: Read as '0'

bit 26 TXNFULLIE: Transmit FIFO Not Full Interrupt Enable bit

1 = Interrupt enabled for FIFO not full0 = Interrupt disabled for FIFO not full

bit 25 TXHALFIE: Transmit FIFO Half Full Interrupt Enable bit

1 = Interrupt enabled for FIFO half full 0 = Interrupt disabled for FIFO half full

bit 24 **TXEMPTYIE:** Transmit FIFO Empty Interrupt Enable bit

1 = Interrupt enabled for FIFO empty0 = Interrupt disabled for FIFO empty

bit 23-20 Unimplemented: Read as '0'

bit 19 RXOVFLIE: Overflow Interrupt Enable bit

1 = Interrupt enabled for overflow event

0 = Interrupt disabled for overflow event

bit 18 RXFULLIE: Full Interrupt Enable bit

1 = Interrupt enabled for FIFO full

0 = Interrupt disabled for FIFO full

bit 17 **RXHALFIE:** FIFO Half Full Interrupt Enable bit

1 = Interrupt enabled for FIFO half full

0 = Interrupt disabled for FIFO half full

bit 16 RXNEMPTYIE: Empty Interrupt Enable bit

1 = Interrupt enabled for FIFO not empty

0 = Interrupt disabled for FIFO not empty

bit 15-11 Unimplemented: Read as '0'

bit 10 **TXNFULLIF:** Transmit FIFO Not Full Interrupt Flag bit<sup>(1)</sup>

TXEN = 1: (FIFO configured as a Transmit Buffer)

1 = FIFO is not full

0 = FIFO is full

TXEN = 0: (FIFO configured as a Receive Buffer)

Unused, reads '0'

Note 1: This bit is read-only and reflects the status of the FIFO.

# REGISTER 30-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER (CONTINUED)

- bit 7 CRCERREN: CRC Error Collection Enable bit

- 1 = The received packet CRC must be invalid for the packet to be accepted

- 0 = Disable CRC Error Collection filtering

This bit allows the user to collect all packets that have an invalid CRC.

- bit 6 CRCOKEN: CRC OK Enable bit

- 1 = The received packet CRC must be valid for the packet to be accepted

- 0 = Disable CRC filtering

This bit allows the user to reject all packets that have an invalid CRC.

- bit 5 RUNTERREN: Runt Error Collection Enable bit

- 1 = The received packet must be a runt packet for the packet to be accepted

- 0 = Disable Runt Error Collection filtering

This bit allows the user to collect all packets that are runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes (when CRCOKEN = 0) or any packet with a size of less than 64 bytes that has a valid CRC (when CRCOKEN = 1).

- bit 4 RUNTEN: Runt Enable bit

- 1 = The received packet must not be a runt packet for the packet to be accepted

- 0 = Disable Runt filtering

This bit allows the user to reject all runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes.

- bit 3 UCEN: Unicast Enable bit

- 1 = Enable Unicast Filtering

- 0 = Disable Unicast Filtering

This bit allows the user to accept all unicast packets whose Destination Address matches the Station Address.

- bit 2 NOTMEEN: Not Me Unicast Enable bit

- 1 = Enable Not Me Unicast Filtering

- 0 = Disable Not Me Unicast Filtering

This bit allows the user to accept all unicast packets whose Destination Address does not match the Station Address.

- bit 1 MCEN: Multicast Enable bit

- 1 = Enable Multicast Filtering

- 0 = Disable Multicast Filtering

This bit allows the user to accept all Multicast Address packets.

- bit 0 BCEN: Broadcast Enable bit

- 1 = Enable Broadcast Filtering

- 0 = Disable Broadcast Filtering

This bit allows the user to accept all Broadcast Address packets.

- **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

- Note 1: This register is only used for RX operations.

- 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

### 37.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MZ EF electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MZ EF devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

Specifications for Extended Temperature devices (-40°C to +125°C) that are different from the specifications in this section are provided in **38.0** "Extended Temperature Electrical Characteristics".

# Absolute Maximum Ratings (See Note 1)

| Ambient temperature under bias                                              |                          |

|-----------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                         | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                          | -0.3V to +4.0V           |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)    | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD ≥ 2.1V (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.1V (Note 3) | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                             | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                         | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                           | 200 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                    | 200 mA                   |

| Maximum current sunk/sourced by any 4x I/O pin (Note 4)                     | 15 mA                    |

| Maximum current sunk/sourced by any 8x I/O pin (Note 4)                     | 25 mA                    |

| Maximum current sunk/sourced by any 12x I/O pin (Note 4)                    | 33 mA                    |

| Maximum current sunk by all ports                                           | 150 mA                   |

| Maximum current sourced by all ports (Note 2)                               | 150 mA                   |

- **Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 37-2).

- 3: See the pin name tables (Table 2 through Table 4) for the 5V tolerant pins.

- **4:** Characterized, but not tested. Refer to parameters DO10, DO20, and DO20a for the 4x, 8x, and 12x I/O pin lists.

TABLE 37-7: DC CHARACTERISTICS: IDLE CURRENT (IDLE)

| IABLE 31-1.       | DO CHARACTERIOTICS. IDEE CORRENT (IIDEE) |                        |            |                                                                                                                                              |  |  |  |  |  |  |  |  |

|-------------------|------------------------------------------|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| DC CHARACTI       | ERISTICS                                 |                        | (unless o  | Operating Conditions: 2.1V to 3.6V therwise stated) temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial |  |  |  |  |  |  |  |  |

| Parameter<br>No.  | Typical <sup>(2)</sup>                   | Maximum <sup>(4)</sup> | Units      | Conditions                                                                                                                                   |  |  |  |  |  |  |  |  |

| Idle Current (III | DLE): Core Of                            | f, Clock on Ba         | ase Curren | t (Note 1)                                                                                                                                   |  |  |  |  |  |  |  |  |

| DC30a             | 7                                        | 22                     | mA         | 4 MHz (Note 3)                                                                                                                               |  |  |  |  |  |  |  |  |

| DC31a             | 8                                        | 24                     | mA         | 10 MHz                                                                                                                                       |  |  |  |  |  |  |  |  |

| DC32a             | 13                                       | 32                     | mA         | 60 MHz (Note 3)                                                                                                                              |  |  |  |  |  |  |  |  |

| DC33a             | 21                                       | 42                     | mA         | 130 MHz (Note 3)                                                                                                                             |  |  |  |  |  |  |  |  |

| DC34              | 26                                       | 48                     | mA         | 180 MHz (Note 3)                                                                                                                             |  |  |  |  |  |  |  |  |

| DC35              | 28                                       | 52                     | mA         | 200 MHz                                                                                                                                      |  |  |  |  |  |  |  |  |

**Note 1:** The test conditions for IDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBPMD = 1), VUSB3V3 is connected to Vss, PBCLKx divisor = 1:128 ('x' ≠ 7)

- CPU is in Idle mode (CPU core Halted)

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared (except USBPMD)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** Data in the "Maximum" column is at 3.3V, +85°C at specified operating frequency, unless otherwise stated. Parameters are for design guidance only and are not tested.

**TABLE 37-18: SYSTEM TIMING REQUIREMENTS**

| AC CHARACTERISTICS |        |                           | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |         |         |       |                                                  |  |  |

|--------------------|--------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|--------------------------------------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics           | Minimum                                                                                                                                                                | Typical | Maximum | Units | Conditions                                       |  |  |

| OS51               | Fsys   | System Frequency          | DC                                                                                                                                                                     | _       | 200     | MHz   | USB module disabled                              |  |  |

|                    |        |                           | 60                                                                                                                                                                     | _       | 200     | MHz   | USB module enabled                               |  |  |

| OS55a              | FРВ    | Peripheral Bus Frequency  | DC                                                                                                                                                                     | _       | 100     | MHz   | For PBCLKx, 'x' $\neq$ 4, 7                      |  |  |