Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efg100t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.9 Designing for High-Speed Peripherals

The PIC32MZ EF family devices have peripherals that operate at frequencies much higher than typical for an embedded environment. Table 2-1 lists the peripherals that produce high-speed signals on their external pins:

# TABLE 2-1: PERIPHERALS THAT PRODUCE HS SIGNALS ON EXTERNAL PINS

| Peripheral | High-Speed<br>Signal Pins   | Maximum<br>Speed on<br>Signal Pin |

|------------|-----------------------------|-----------------------------------|

| EBI        | EBIAx,<br>EBIDx             | 50 MHz                            |

| SQI1       | SQICLK,<br>SQICSx,<br>SQIDx | 50 MHz                            |

| HS USB     | D+, D-                      | 480 MHz                           |

Due to these high-speed signals, it is important to consider several factors when designing a product that uses these peripherals, as well as the PCB on which these components will be placed. Adhering to these recommendations will help achieve the following goals:

- Minimize the effects of electromagnetic interference to the proper operation of the product

- Ensure signals arrive at their intended destination at the same time

- Minimize crosstalk

- Maintain signal integrity

- Reduce system noise

- Minimize ground bounce and power sag

# 2.9.1 SYSTEM DESIGN

# 2.9.1.1 Impedance Matching

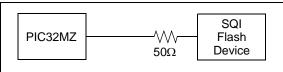

When selecting parts to place on high-speed buses, particularly the SQI bus, if the impedance of the peripheral device does not match the impedance of the pins on the PIC32MZ EF device to which it is connected, signal reflections could result, thereby degrading the quality of the signal.

If it is not possible to select a product that matches impedance, place a series resistor at the load to create the matching impedance. See Figure 2-4 for an example.

# FIGURE 2-4: SERIES RESISTOR

# 2.9.1.2 PCB Layout Recommendations

The following list contains recommendations that will help ensure the PCB layout will promote the goals previously listed.

# Component Placement

- Place bypass capacitors as close to their component power and ground pins as possible, and place them on the same side of the PCB

- Devices on the same bus that have larger setup times should be placed closer to the PIC32MZ EF device

# • Power and Ground

- Multi-layer PCBs will allow separate power and ground planes

- Each ground pin should be connected to the ground plane individually

- Place bypass capacitor vias as close to the pad as possible (preferably inside the pad)

- If power and ground planes are not used, maximize width for power and ground traces

- Use low-ESR, surface-mount bypass capacitors

# • Clocks and Oscillators

- Place crystals as close as possible to the PIC32MZ EF device OSC/SOSC pins

- Do not route high-speed signals near the clock or oscillator

- Avoid via usage and branches in clock lines (SQICLK)

- Place termination resistors at the end of clock lines

- Traces

- Higher-priority signals should have the shortest traces

- Match trace lengths for parallel buses (EBIAx, EBIDx, SQIDx)

- Avoid long run lengths on parallel traces to reduce coupling

- Make the clock traces as straight as possible

- Use rounded turns rather than right-angle turns

- Have traces on different layers intersect on right angles to minimize crosstalk

- Maximize the distance between traces, preferably no less than three times the trace width

- Power traces should be as short and as wide as possible

- High-speed traces should be placed close to the ground plane

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-------------------|-------------------|-------------------|----------------------|------------------|

| 04-04        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 31:24        |                   | PRI7SS            | <3:0> <sup>(1)</sup> |                   |                   | PRI6SS            | <3:0> <sup>(1)</sup> |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 23:16        |                   | PRI5SS            | <3:0> <sup>(1)</sup> |                   |                   | PRI4SS            | <3:0> <sup>(1)</sup> |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 15:8         |                   | PRI3S             | S<3:0>               |                   |                   | PRI2SS            | <3:0> <sup>(1)</sup> |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0             | U-0               | U-0               | U-0                  | R/W-0            |

| 7:0          |                   | PRI1SS            | <3:0> <sup>(1)</sup> | •                 |                   |                   | _                    | SS0              |

# REGISTER 7-2: PRISS: PRIORITY SHADOW SELECT REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-28 **PRI7SS<3:0>:** Interrupt with Priority Level 7 Shadow Set bits<sup>(1)</sup>

1xxx = Reserved (by default, an interrupt with a priority level of 7 uses Shadow Set 0) 0111 = Interrupt with a priority level of 7 uses Shadow Set 7 0110 = Interrupt with a priority level of 7 uses Shadow Set 6 0001 = Interrupt with a priority level of 7 uses Shadow Set 1 0000 = Interrupt with a priority level of 7 uses Shadow Set 0 bit 27-24 **PRI6SS<3:0>:** Interrupt with Priority Level 6 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 6 uses Shadow Set 0) 0111 = Interrupt with a priority level of 6 uses Shadow Set 7 0110 = Interrupt with a priority level of 6 uses Shadow Set 6 0001 = Interrupt with a priority level of 6 uses Shadow Set 1 0000 = Interrupt with a priority level of 6 uses Shadow Set 0 bit 23-20 PRI5SS<3:0>: Interrupt with Priority Level 5 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 5 uses Shadow Set 0) 0111 = Interrupt with a priority level of 5 uses Shadow Set 7 0110 = Interrupt with a priority level of 5 uses Shadow Set 6 0001 = Interrupt with a priority level of 5 uses Shadow Set 1 0000 = Interrupt with a priority level of 5 uses Shadow Set 0 bit 19-16 PRI4SS<3:0>: Interrupt with Priority Level 4 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 4 uses Shadow Set 0) 0111 = Interrupt with a priority level of 4 uses Shadow Set 7 0110 = Interrupt with a priority level of 4 uses Shadow Set 6 0001 = Interrupt with a priority level of 4 uses Shadow Set 1 0000 = Interrupt with a priority level of 4 uses Shadow Set 0

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |  |  |  |

| 00:40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8      |                   |                   |                   | CHSSA<            | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |  |

# REGISTER 10-10: DCHxSSA: DMA CHANNEL x SOURCE START ADDRESS REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CHSSA<31:0> Channel Source Start Address bits Channel source start address. Note: This must be the physical address of the source.

Γ.

# REGISTER 10-11: DCHxDSA: DMA CHANNEL x DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | CHDSA<            | 31:24>            |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | CHDSA<            | 23:16>            |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSA-            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits Channel destination start address.

Note: This must be the physical address of the destination.

# TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| ss                          |                  |               |                     |                                                                                                           |       |       |       |        |              |        | Bits        |          |             |      |            |             |        |       |            |

|-----------------------------|------------------|---------------|---------------------|-----------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|--------------|--------|-------------|----------|-------------|------|------------|-------------|--------|-------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15               | 30/14                                                                                                     | 29/13 | 28/12 | 27/11 | 26/10  | 25/9         | 24/8   | 23/7        | 22/6     | 21/5        | 20/4 | 19/3       | 18/2        | 17/1   | 16/0  | All Resets |

| 3248                        | USB              | 31:16         |                     |                                                                                                           |       |       |       |        |              | DMA    | ADDR<31:16  | >        |             |      |            |             |        |       | 0000       |

| 3248                        | DMA5A            | 15:0          |                     | DMAADDR<15:0> 0000                                                                                        |       |       |       |        |              |        |             |          |             |      |            |             |        |       |            |

| 324C                        | USB              | 31:16         |                     | DMACOUNT<31:16> 0000                                                                                      |       |       |       |        |              |        |             |          |             |      |            |             |        |       |            |

| 0240                        | DMA5N            | 15:0          |                     |                                                                                                           |       | -     | •     |        |              | DMA    | COUNT<15:0  | >        |             |      |            |             |        |       | 0000       |

| 3254                        | USB              | 31:16         | _                   |                                                                                                           |       |       |       |        |              |        |             |          |             |      |            |             |        |       |            |

|                             | DMA6C            | 15:0          | —                   |                                                                                                           |       |       |       |        |              |        |             |          |             |      |            |             |        |       |            |

| 3258                        | USB<br>DMA6A     | 31:16         |                     |                                                                                                           |       |       |       |        |              |        | ADDR<31:16  |          |             |      |            |             |        |       | 0000       |

|                             |                  | 15:0          |                     | DMAADDR<15:0> 0000                                                                                        |       |       |       |        |              |        |             |          |             |      |            |             |        |       |            |

| 325C                        | USB<br>DMA6N     | 31:16         |                     |                                                                                                           |       |       |       |        |              |        | COUNT<31:10 |          |             |      |            |             |        |       | 0000       |

| $\vdash$                    |                  | 15:0          |                     | DMACOUNT<15:0> 0000                                                                                       |       |       |       |        |              |        |             |          |             |      |            |             |        |       |            |

| 3264                        | USB<br>DMA7C     | 31:16<br>15:0 | _                   |                                                                                                           | _     |       | _     |        | <br>STM<1:0> |        | —           | -        | <br>EP<3:0> | _    | —<br>DMAIE | <br>DMAMODE |        |       | 0000       |

|                             |                  | 31:16         | —                   | _                                                                                                         | —     |       | _     | DIMABR | 51M<1:0>     | DMAERR | ADDR<31:16  |          | EP<3:0>     |      | DIVIAIE    | DMAMODE     | DMADIR | DMAEN | 0000       |

| 3268                        | USB<br>DMA7A     | 15:0          |                     |                                                                                                           |       |       |       |        |              |        | ADDR<15:0:  |          |             |      |            |             |        |       | 0000       |

|                             | USB              | 31:16         |                     |                                                                                                           |       |       |       |        |              |        | COUNT<31:10 |          |             |      |            |             |        |       | 0000       |

| 326C                        | DMA7N            | 15:0          |                     |                                                                                                           |       |       |       |        |              |        | COUNT<15:0  |          |             |      |            |             |        |       | 0000       |

|                             | USB              | 31:16         | _                   | _                                                                                                         |       | _     | _     | _      | _            | _      | _           | _        | _           | _    | _          | _           | _      | _     | 0000       |

| 3274                        | DMA8C            | 15:0          | _                   | _                                                                                                         | _     | _     | _     | DMABR  | STM<1:0>     | DMAERR |             | DMA      | EP<3:0>     |      | DMAIE      | DMAMODE     | DMADIR | DMAEN | 0000       |

| 0070                        | USB              | 31:16         |                     |                                                                                                           |       |       |       | 1      |              | DMA    | ADDR<31:16  | >        |             |      | 1          |             | 1      | J     | 0000       |

| 3278                        | DMA8A            | 15:0          |                     |                                                                                                           |       |       |       |        |              | DM     | ADDR<15:0   | •        |             |      |            |             |        |       | 0000       |

| 327C                        | USB              | 31:16         |                     |                                                                                                           |       |       |       |        |              | DMA    | COUNT<31:10 | i>       |             |      |            |             |        |       | 0000       |

| 3270                        | DMA8N            | 15:0          |                     |                                                                                                           |       |       |       |        |              | DMA    | COUNT<15:0  | >        |             |      |            |             |        |       | 0000       |

| 3304                        | USB              | 31:16         | —                   |                                                                                                           | —     | _     | —     | _      | —            | —      | _           | —        | _           | -    | —          | _           | —      | —     | 0000       |

| 5504                        | E1RPC            | 15:0          |                     |                                                                                                           |       | -     |       | -      |              | RQP    | KTCNT<15:0  | >        |             | -    |            |             |        |       | 0000       |

| 3308                        | USB              | 31:16         | —                   | —                                                                                                         | —     | —     | -     | —      | —            | —      | —           | —        | -           | -    | —          | -           | —      | —     | 0000       |

|                             | E2RPC            | 15:0          |                     |                                                                                                           |       |       |       |        |              | RQP    | KTCNT<15:0  | >        | 1           |      |            |             |        |       | 0000       |

| 330C                        | USB              | 31:16         | _                   | _                                                                                                         | —     |       | —     |        | —            | —      |             |          | _           | _    | _          | _           | _      | —     | 0000       |

|                             | E3RPC            | 15:0          |                     |                                                                                                           |       |       | 1     |        |              |        | KTCNT<15:0  |          |             |      |            |             |        |       | 0000       |

| 3310                        | USB<br>E4RPC     | 31:16         | _                   | _                                                                                                         | —     |       | -     | _      | —            | —      | —           | _        | _           | -    | _          | _           | _      |       | 0000       |

| $\vdash$                    |                  | 15:0          |                     |                                                                                                           |       |       |       |        |              |        | KTCNT<15:0  |          |             |      |            |             |        |       | 0000       |

| 3314                        | USB<br>E5RPC     | 31:16<br>15:0 | —                   | _                                                                                                         | —     | _     | —     | _      | —            |        |             | _        | —           | —    | _          | —           | —      | —     | 0000       |

| $\vdash$                    |                  |               | RQPKTCNT<15:0> 0000 |                                                                                                           |       |       |       |        |              |        |             |          |             |      |            |             |        |       |            |

| 3318                        | USB<br>E6RPC     | 31:16<br>15:0 | <u> </u>            |                                                                                                           |       |       |       |        |              |        |             |          |             |      |            |             |        |       |            |

| $\vdash$                    |                  | 31:16         | _                   | _                                                                                                         | _     |       |       | _      |              |        |             | <u> </u> |             | _    | _          | _           |        | _     | 0000       |

| 331C                        | USB<br>E7RPC     | 15:0          | _                   | _                                                                                                         |       |       | _     |        |              | ROP    |             |          | _           | _    |            | _           |        |       |            |

| 1                           |                  | 10.0          |                     | RQPKTCNT<15:0> 0000 alue on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |       |       |       |        |              |        |             |          |             |      |            |             |        |       |            |

Legend: Note x = unknownDevice mode.

Host mode.

1: 2: 3: 4: Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

# REGISTER 11-11: USBIENCSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 1-7) (CONTINUED)

### bit 15-8 **RXINTERV<7:0>:** Endpoint RX Polling Interval/NAK Limit bits

For Interrupt and Isochronous transfers, this field defines the polling interval for the endpoint. For Bulk endpoints, this field sets the number of frames/microframes after which the endpoint should time out on receiving a stream of NAK responses.

The following table describes the valid values and meaning for this field:

| Transfer Type | Speed        | Valid Values (m) | Interpretation                                                                                                |

|---------------|--------------|------------------|---------------------------------------------------------------------------------------------------------------|

| Interrupt     | Low/Full     | 0x01 to 0xFF     | Polling interval is 'm' frames.                                                                               |

|               | High         | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames.                                                                |

| Isochronous   | Full or High | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames/microframes.                                                    |

| Bulk          | Full or High | 0x02 to 0x10     | NAK limit is 2 <sup>(m-1)</sup> frames/microframes. A value of '0' or '1' disables the NAK time-out function. |

bit 7-6 **SPEED<1:0>:** RX Endpoint Operating Speed Control bits

- 11 = Low-Speed

- 10 = Full-Speed

- 01 = Hi-Speed

00 = Reserved

# bit 5-4 **PROTOCOL<1:0>:** RX Endpoint Protocol Control bits

- 11 = Interrupt

- 10 = Bulk

- 01 = Isochronous

- 00 = Control

# bit 3-0 **TEP<3:0>:** RX Target Endpoint Number bits

This value is the endpoint number contained in the TX endpoint descriptor returned to the USB module during device enumeration.

# TABLE 12-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SSS                         |                      |               |       |       |       |       |       |       |      | E    | Bits |      |      |      |      |       |             |      |            |

|-----------------------------|----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|-------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1        | 16/0 | All Resets |

| 4.400                       |                      | 31:16         | -     | —     | _     | —     | —     | —     | —    | _    | -    | —    | —    | —    | —    | —     | —           | —    | 000        |

| 1488                        | U5RXR                | 15:0          | _     | —     | —     | —     | —     | —     | —    | —    |      | —    | —    | —    |      | U5RXI | R<3:0>      | •    | 000        |

| 148C                        | U5CTSR               | 31:16         |       | —     | —     | —     | —     | —     | —    | —    | 1    | —    | —    | —    | —    | —     | —           | —    | 000        |

| 1400                        | USCISK               | 15:0          |       | _     | —     | _     | _     | —     | —    | —    |      | _    | —    | _    |      | U5CTS | R<3:0>      |      | 000        |

| 1490                        | U6RXR                | 31:16         |       | _     | —     | _     | _     | —     | —    | —    |      | _    | —    | _    | _    | _     | _           | _    | 000        |

| 1490                        | UUKAK                | 15:0          | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | U6RXI | R<3:0>      |      | 000        |

| 1494                        | U6CTSR               | 31:16         | _     | —     | —     | —     | —     | —     | _    | —    | _    | —    | —    | _    | _    | —     | —           | —    | 000        |

| 1404                        | 000101               | 15:0          | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | U6CTS | R<3:0>      |      | 000        |

| 149C                        | SDI1R                | 31:16         | _     | —     | —     | —     | _     | —     | —    | —    | _    | —    | —    | —    | —    | —     | —           | —    | 000        |

|                             | 00                   | 15:0          | _     |       | —     |       |       | —     | _    | —    | _    |      | —    | —    |      | SDI1F | R<3:0>      |      | 000        |

| 14A0                        | SS1R                 | 31:16         | _     | _     | —     | _     | _     | _     | _    | —    | _    | _    | —    | _    |      | —     | —           |      | 000        |

|                             |                      | 15:0          | _     |       | —     |       |       |       |      | —    | _    |      | —    | —    |      | SS1R  | <3:0>       |      | 000        |

| 14A8                        | SDI2R                | 31:16         | _     | —     | —     | —     | —     | _     | —    | —    | _    | —    |      | —    | —    | —     | —           | —    | 000        |

|                             |                      | 15:0          | _     |       | —     |       |       |       |      | —    | _    |      | —    | —    |      | SDI2F | R<3:0>      |      | 000        |

| 14AC                        | SS2R                 | 31:16         | _     | —     | —     | —     | —     | _     | —    | —    | _    | —    |      | —    | —    | —     | —           | —    | 000        |

|                             |                      | 15:0          | _     | —     | —     | _     | _     |       | —    | —    | _    | —    | —    | —    |      | SS2R  |             |      | 000        |

| 14B4                        | SDI3R                | 31:16         | _     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | —    |       | —           | —    | 000        |

|                             |                      | 15:0          | _     |       | _     |       |       | —     | _    | _    | _    | _    | _    | _    |      | SDI3F | R<3:0>      |      | 000        |

| 14B8                        | SS3R                 | 31:16         | —     | _     | _     | _     | _     | _     | _    | _    | _    | —    | _    | —    | —    |       | —           | _    | 000        |

|                             |                      | 15:0          | _     |       |       |       |       |       | _    | _    |      |      |      |      |      | SS3R  |             |      | 000        |

| 14C0                        | SDI4R                | 31:16         |       | _     | _     | _     | _     | _     | _    | _    |      | _    |      |      |      |       | —           |      | 000        |

|                             |                      | 15:0          |       | _     | _     | _     | _     | _     | _    | _    |      | _    |      |      |      | SDI4F | R<3:0>      |      | 000        |

| 14C4                        | SS4R                 | 31:16         |       | _     | _     | _     | _     |       |      | —    |      |      |      |      |      |       | —           | —    | 000        |

|                             |                      | 15:0          |       | _     | _     | _     | _     |       |      | —    |      |      |      |      |      | SS4R  |             |      | 000        |

| 14CC                        | SDI5R <sup>(1)</sup> | 31:16         |       | _     | —     | _     | _     |       | —    | —    |      |      | —    | —    | —    | -     | —           | —    | 000        |

|                             |                      | 15:0          |       |       | _     | _     |       |       | —    | —    |      |      | —    |      |      |       | R<3:0>      |      | 0000       |

| 14D0                        | SS5R <sup>(1)</sup>  | 31:16         |       |       | _     |       |       |       | —    | —    |      |      | _    |      | —    |       | -           | —    | 0000       |

|                             |                      | 15:0          |       |       | —     |       |       |       | —    | —    |      |      | _    |      |      | SS5R  | <3:0>       |      | 0000       |

| 14D8                        | SDI6R <sup>(1)</sup> | 31:16<br>15:0 |       | —     | _     | —     | _     | —     | _    | _    |      | —    | _    |      | —    |       | —<br>R<3:0> |      | 0000       |

| Logon                       |                      |               |       |       |       |       |       | —     |      | _    | —    | —    | _    | —    |      | 20101 | <3.0>       |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

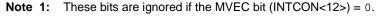

# 20.0 SERIAL QUAD INTERFACE (SQI)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 46. "Serial Quad Interface (SQI)" (DS60001244) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SQI module is a synchronous serial interface that provides access to serial Flash memories and other serial devices. The SQI module supports Single Lane (identical to SPI), Dual Lane, and Quad Lane modes.

The following are key feature of the SQI module:

- Supports Single, Dual, and Quad Lane modes

- Supports Single Data Rate (SDR) mode

- Programmable command sequence

- eXecute-In-Place (XIP)

- Data transfer:

- Programmed I/O mode (PIO)

- Buffer descriptor DMA

- Supports SPI Mode 0 and Mode 3

- Programmable Clock Polarity (CPOL) and Clock Phase (CPHA) bits

- Supports up to two Chip Selects

- · Supports up to four bytes of Flash address

- · Programmable interrupt thresholds

- · 32-byte transmit data buffer

- 32-byte receive data buffer

- 4-word controller buffer

- Once the SQI module is configured, Note: external devices are memory mapped into KSEG2 and KSEG3 (see Figure 4-1 through Figure 4-4 in Section 4.0 "Memory Organization" for more information). The MMU must be enabled and the TLB must be set up to access this memory (refer to Section 50. "CPU MIPS32<sup>®</sup> for Devices with microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) of the "PIC32 Family Reference Manual" for more information).

# FIGURE 20-1: SQI MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | —                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   |                   | —                 | _                 | —                 | _                 | _                | _                |  |

| 45.0         | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | —                 |                   |                   | CLKIND            | LY<5:0>           |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   | DATAOUT           | DLY<3:0>          |                   |                   | CLKOUTI           | DLY<3:0>         |                  |  |

# REGISTER 20-23: SQI1TAPCON: SQI TAP CONTROL REGISTER

# Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

# bit 31-14 Unimplemented: Read as '0'

bit 13-8 CLKINDLY<5:0>: SQI Clock Input Delay bits

These bits are used to add fractional delays to SQI Clock Input while sampling the incoming data.

111111 = 64 taps added on clock input

111110 = 63 taps added on clock input

•

.

000001 = 2 taps added on clock input 000000 = 1 tap added on clock input

# bit 7-4 DATAOUTDLY<3:0>: SQI Data Output Delay bits

These bits are used to add fractional delays to SQI Data Output while writing the data to the Flash. 1111 = 16 taps added on clock output

- 1110 = 15 taps added on clock output

- •

•

0001 = 2 taps added on clock output 0000 = 1 tap added on clock output

# bit 3-0 CLKOUTDLY<3:0>: SQI Clock Output Delay bits

These bits are used to add fractional delays to SQI Clock Output while writing the data to the Flash.

1111 = 16 taps added on clock output

- 1110 = 15 taps added on clock output

- •

•

- 0001 = 2 taps added on clock output

- 0000 = 1 tap added on clock output

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | —                | —                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | _                 |                   | TRPD              | <11:8>           |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | TRPD              | <7:0>             |                   |                  |                  |

# REGISTER 24-4: EBIFTRPD: EXTERNAL BUS INTERFACE FLASH TIMING REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

# bit 31-12 Unimplemented: Read as '0'

# bit 11-0 TRPD<11:0>: Flash Timing bits

These bits define the number of clock cycles to wait after resetting the external Flash memory before any read/write access.

# REGISTER 25-1: RTCCON: REAL-TIME CLOCK AND CALENDAR CONTROL REGISTER (CONTINUED)

bit 10-9 RTCCLKSEL<1:0>: RTCC Clock Select bits

When a new value is written to these bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.

- 11 = Reserved

- 10 = Reserved

- 01 = RTCC uses the external 32.768 kHz Secondary Oscillator (SOSC)

- 00 = RTCC uses the internal 32 kHz oscillator (LPRC)

- bit 8-7 RTCOUTSEL<1:0>: RTCC Output Data Select bits<sup>(2)</sup>

- 11 = Reserved

- 10 = RTCC Clock is presented on the RTCC pin

- 01 = Seconds Clock is presented on the RTCC pin

- 00 = Alarm Pulse is presented on the RTCC pin when the alarm interrupt is triggered

- bit 6 RTCCLKON: RTCC Clock Enable Status bit<sup>(5)</sup>

- 1 = RTCC Clock is actively running

- 0 = RTCC Clock is not running

- bit 5-4 Unimplemented: Read as '0'

- bit 3 RTCWREN: Real-Time Clock Value Registers Write Enable bit<sup>(3)</sup>

- 1 = Real-Time Clock Value registers can be written to by the user

- 0 = Real-Time Clock Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: Real-Time Clock Value Registers Read Synchronization bit

- 1 = Real-time clock value registers can change while reading (due to a rollover ripple that results in an invalid data read). If the register is read twice and results in the same data, the data can be assumed to be valid.

- 0 = Real-time clock value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(4)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 **RTCOE:** RTCC Output Enable bit

- 1 = RTCC output is enabled

- 0 = RTCC output is not enabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- **2**: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 3: The RTCWREN bit can be set only when the write sequence is enabled.

- 4: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

- 5: This bit is undefined when RTCCLKSEL<1:0> = 00 (LPRC is the clock source).

Note: This register is reset only on a Power-on Reset (POR).

# PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

| REGIST  | ER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER (CONTINUED)                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-0 | ARPT<7:0>: Alarm Repeat Counter Value bits <sup>(2)</sup>                                                                                        |

|         | 11111111 = Alarm will trigger 256 times                                                                                                          |

|         | •                                                                                                                                                |

|         |                                                                                                                                                  |

|         | 00000000 = Alarm will trigger one time<br>The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1. |

| Note 1: | Hardware clears the ALRMEN bit anytime the alarm event occurs, when $ARPT < 7:0 > = 0.0$ and $CHIME = 0.$                                        |

| 2:      | This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.                                                       |

|         |                                                                                                                                                  |

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        |                   | HR10-             | <3:0>             |                   |                   | HR01              | <3:0>            |                  |  |

| 22.16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   | MIN10             | <3:0>             |                   | MIN01<3:0>        |                   |                  |                  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   | SEC10             | <3:0>             |                   |                   | SEC01<3:0>        |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | —                 | —                 | —                 | —                 | —                 | _                 | —                | —                |  |

|              | •                 |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |

| R = Read     | lable bit         |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |

'0' = Bit is cleared

x = Bit is unknown

# REGISTER 25-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10 digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1 digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

'1' = Bit is set

-n = Value at POR

# 26.3 Security Association Structure

Table 26-4 shows the Security Association Structure. The Crypto Engine uses the Security Association to determine the settings for processing a Buffer Descriptor Processor. The Security Association contains:

- · Which algorithm to use

- Whether to use engines in parallel (for both authentication and encryption/decryption)

- The size of the key

- Authentication key

- Encryption/decryption key

- Authentication Initialization Vector (IV)

- Encryption IV

| Name        |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| SA_CTRL     | 31:24 | _                 |                   | VERIFY            | _                 | NO_RX             | OR_EN             | ICVONLY          | IRFLAG           |

| _           | 23:16 | LNC               | LOADIV            | FB                | FLAGS             | _                 | _                 |                  | ALGO<6>          |

|             | 15:8  |                   |                   | ALGO<             | :5:0>             | 1                 |                   | ENCTYPE          | KEYSIZE<1:       |

|             | 7:0   | KEYSIZE<0>        | N                 | IULTITASK<2:0     | >                 |                   | CRYPTOA           | LGO<3:0>         | ILE FOILE ST     |

| AUTHKEY1    | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |

| _           | 23:16 |                   |                   |                   | AUTHKEY<          |                   |                   |                  |                  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |

|             | 7:0   |                   |                   |                   | AUTHKEY           | <7:0>             |                   |                  |                  |

| SA_AUTHKEY2 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |

| -           | 23:16 |                   |                   |                   | AUTHKEY<          | 23:16>            |                   |                  |                  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |

|             | 7:0   |                   |                   |                   | AUTHKEY           | <7:0>             |                   |                  |                  |

| SA_AUTHKEY3 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |

| _           | 23:16 |                   |                   |                   | AUTHKEY<          | 23:16>            |                   |                  |                  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |

|             | 7:0   |                   |                   |                   | AUTHKEY           | <7:0>             |                   |                  |                  |

| SA_AUTHKEY4 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |

|             | 23:16 | AUTHKEY<23:16>    |                   |                   |                   |                   |                   |                  |                  |

|             | 15:8  | AUTHKEY<15:8>     |                   |                   |                   |                   |                   |                  |                  |

|             | 7:0   | AUTHKEY<7:0>      |                   |                   |                   |                   |                   |                  |                  |

| SA_AUTHKEY5 | 31:24 |                   | AUTHKEY<31:24>    |                   |                   |                   |                   |                  |                  |

|             | 23:16 | AUTHKEY<23:16>    |                   |                   |                   |                   |                   |                  |                  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          |                   |                   |                  |                  |

|             | 7:0   | AUTHKEY<7:0>      |                   |                   |                   |                   |                   |                  |                  |

| SA_AUTHKEY6 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |

|             | 23:16 |                   |                   |                   | AUTHKEY<          | 23:16>            |                   |                  |                  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |

|             | 7:0   |                   |                   |                   | AUTHKEY           | <7:0>             |                   |                  |                  |

| SA_AUTHKEY7 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |

|             | 23:16 |                   |                   |                   | AUTHKEY<          | 23:16>            |                   |                  |                  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |

|             | 7:0   |                   |                   |                   | AUTHKEY           | <7:0>             |                   |                  |                  |

| SA_AUTHKEY8 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |

|             | 23:16 |                   |                   |                   | AUTHKEY<          | 23:16>            |                   |                  |                  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |

|             | 7:0   |                   |                   |                   | AUTHKEY           | <7:0>             |                   |                  |                  |

| SA_ENCKEY1  | 31:24 |                   |                   |                   | ENCKEY<3          | 31:24>            |                   |                  |                  |

|             | 23:16 |                   |                   |                   | ENCKEY<2          | 23:16>            |                   |                  |                  |

|             | 15:8  |                   |                   |                   | ENCKEY<           | 15:8>             |                   |                  |                  |

|             | 7:0   |                   |                   |                   | ENCKEY<           | :7:0>             |                   |                  |                  |

| SA_ENCKEY2  | 31:24 |                   |                   |                   | ENCKEY<3          | 31:24>            |                   |                  |                  |

|             | 23:16 |                   |                   |                   | ENCKEY<2          | 23:16>            |                   |                  |                  |

# TABLE 26-4: CRYPTO ENGINE SECURITY ASSOCIATION STRUCTURE

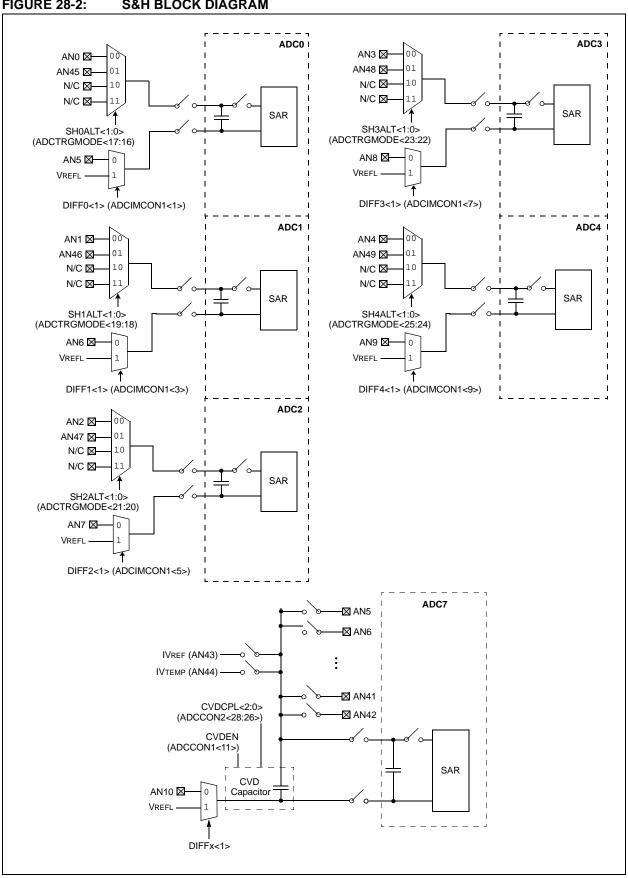

**FIGURE 28-2: S&H BLOCK DIAGRAM**

# PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

|              |                        |                        |                        |                        |                        |                        | • • = • • •            |                        |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|              | R/W-0                  |

| 31:24        | AGIEN31 <sup>(1)</sup> | AGIEN30 <sup>(1)</sup> | AGIEN29 <sup>(1)</sup> | AGIEN28 <sup>(1)</sup> | AGIEN27 <sup>(1)</sup> | AGIEN26 <sup>(1)</sup> | AGIEN25 <sup>(1)</sup> | AGIEN24 <sup>(1)</sup> |

| 00.40        | R/W-0                  |

| 23:16        | AGIEN23 <sup>(1)</sup> | AGIEN22 <sup>(1)</sup> | AGIEN21 <sup>(1)</sup> | AGIEN20 <sup>(1)</sup> | AGIEN19 <sup>(1)</sup> | AGIEN18                | AGIEN17                | AGIEN16                |

| 45.0         | R/W-0                  |

| 15:8         | AGIEN15                | AGIEN14                | AGIEN13                | AGIEN12                | AGIEN11                | AGIEN10                | AGIEN9                 | AGIEN8                 |

| 7:0          | R/W-0                  |

|              | AGIEN7                 | AGIEN6                 | AGIEN5                 | AGIEN4                 | AGIEN3                 | AGIEN2                 | AGIEN1                 | AGIEN0                 |

# REGISTER 28-8: ADCGIRQEN1: ADC GLOBAL INTERRUPT ENABLE REGISTER 1

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

bit 31-0 AGIEN31:AGIEN0: ADC Global Interrupt Enable bits

- 1 = Interrupts are enabled for the selected analog input. The interrupt is generated after the converted data is ready (indicated by the ARDYx bit ('x' = 31-0) of the ADCDSTAT1 register)

- 0 = Interrupts are disabled

**Note 1:** This bit is not available on 64-pin devices.

# REGISTER 28-9: ADCGIRQEN2: ADC GLOBAL INTERRUPT ENABLE REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 24.24        | U-0                    |

| 31:24        | —                      | —                      | —                      | —                      | —                      | —                      | —                      | —                      |

| 00.40        | U-0                    |

| 23:16        | —                      | -                      | -                      | _                      | —                      | —                      | —                      | _                      |

| 45.0         | U-0                    | U-0                    | U-0                    | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

| 15:8         | —                      | -                      | —                      | AGIEN44                | AGIEN43                | AGIEN42 <sup>(2)</sup> | AGIEN41 <sup>(2)</sup> | AGIEN40 <sup>(2)</sup> |

| 7.0          | R/W-0                  |

| 7:0          | AGIEN39 <sup>(2)</sup> | AGIEN38 <sup>(2)</sup> | AGIEN37 <sup>(2)</sup> | AGIEN36 <sup>(2)</sup> | AGIEN35 <sup>(2)</sup> | AGIEN34 <sup>(1)</sup> | AGIEN33 <sup>(1)</sup> | AGIEN32 <sup>(1)</sup> |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-13 Unimplemented: Read as '0'

bit 12-0 AGIEN44:AGIEN32 ADC Global Interrupt Enable bits

- 1 = Interrupts are enabled for the selected analog input. The interrupt is generated after the converted data is ready (indicated by the ARDY*x* bit ('x' = 44-32) of the ADCDSTAT2 register)

- 0 =Interrupts are disabled

- Note 1: This bit is not available on 64-pin devices.

- 2: This bit is not available on 64-pin and 100-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2        | Bit<br>25/17/9/1        | Bit<br>24/16/8/0          |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|---------------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24        | _                 | —                 | —                 | _                 | _                 | TXNFULLIE                | TXHALFIE                | TXEMPTYIE                 |

| 22.16        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16        | _                 | —                 | —                 | —                 | RXOVFLIE          | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0                      | R-0                     | R-0                       |

| 15:8         | —                 | —                 | —                 | —                 | —                 | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R-0                      | R-0                     | R-0                       |

| 7:0          | _                 | _                 | —                 | _                 | RXOVFLIF          | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

# REGISTER 29-21: CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' ('n' = 0-31)

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

# bit 31-27 Unimplemented: Read as '0'

| bit 26    | TXNFULLIE: Transmit FIFO Not Full Interrupt Enable bit                                                          |

|-----------|-----------------------------------------------------------------------------------------------------------------|

|           | 1 = Interrupt enabled for FIFO not full                                                                         |

|           | 0 = Interrupt disabled for FIFO not full                                                                        |

| bit 25    | TXHALFIE: Transmit FIFO Half Full Interrupt Enable bit                                                          |

|           | 1 = Interrupt enabled for FIFO half full                                                                        |

|           | 0 = Interrupt disabled for FIFO half full                                                                       |

| bit 24    | <b>TXEMPTYIE:</b> Transmit FIFO Empty Interrupt Enable bit                                                      |

|           | 1 = Interrupt enabled for FIFO empty                                                                            |

|           | 0 = Interrupt disabled for FIFO empty                                                                           |

| bit 23-20 | Unimplemented: Read as '0'                                                                                      |

| bit 19    | RXOVFLIE: Overflow Interrupt Enable bit                                                                         |

|           | 1 = Interrupt enabled for overflow event                                                                        |

|           | 0 = Interrupt disabled for overflow event                                                                       |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                             |

|           | 1 = Interrupt enabled for FIFO full                                                                             |

| 6447      | 0 = Interrupt disabled for FIFO full                                                                            |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                   |

|           | <ul><li>1 = Interrupt enabled for FIFO half full</li><li>0 = Interrupt disabled for FIFO half full</li></ul>    |

| bit 16    | RXNEMPTYIE: Empty Interrupt Enable bit                                                                          |

|           |                                                                                                                 |

|           | <ul> <li>1 = Interrupt enabled for FIFO not empty</li> <li>0 = Interrupt disabled for FIFO not empty</li> </ul> |

| bit 15-11 | Unimplemented: Read as '0'                                                                                      |

| bit 10    | <b>TXNFULLIF:</b> Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                      |

|           | <u>TXEN = 1:</u> (FIFO configured as a Transmit Buffer)                                                         |

|           | 1 = FIFO is not full                                                                                            |

|           | 0 = FIFO is full                                                                                                |

|           | TXEN = 0: (FIFO configured as a Receive Buffer)                                                                 |

|           | Unused, reads '0'                                                                                               |

|           |                                                                                                                 |

**Note 1:** This bit is read-only and reflects the status of the FIFO.

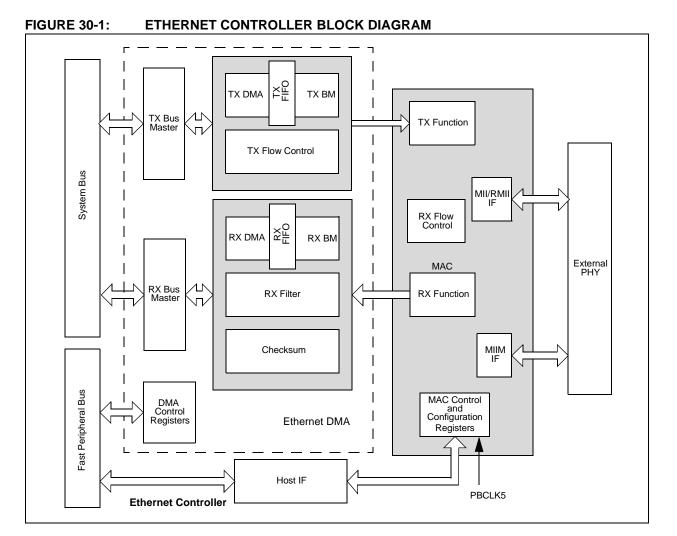

# **30.0 ETHERNET CONTROLLER**

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- · Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- Supports various hardware statistics counters

Figure 30-1 illustrates a block diagram of the Ethernet controller.

### **REGISTER 30-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER (CONTINUED)** bit 7 **CRCERREN:** CRC Error Collection Enable bit 1 = The received packet CRC must be invalid for the packet to be accepted 0 = Disable CRC Error Collection filtering This bit allows the user to collect all packets that have an invalid CRC. bit 6 CRCOKEN: CRC OK Enable bit 1 = The received packet CRC must be valid for the packet to be accepted 0 = Disable CRC filtering This bit allows the user to reject all packets that have an invalid CRC. **RUNTERREN:** Runt Error Collection Enable bit bit 5 1 = The received packet must be a runt packet for the packet to be accepted 0 = Disable Runt Error Collection filtering This bit allows the user to collect all packets that are runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes (when CRCOKEN = 0) or any packet with a size of less than 64 bytes that has a valid CRC (when CRCOKEN = 1). RUNTEN: Runt Enable bit bit 4 1 = The received packet must not be a runt packet for the packet to be accepted 0 = Disable Runt filtering This bit allows the user to reject all runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes. bit 3 UCEN: Unicast Enable bit 1 = Enable Unicast Filtering 0 = Disable Unicast Filtering This bit allows the user to accept all unicast packets whose Destination Address matches the Station Address. bit 2 NOTMEEN: Not Me Unicast Enable bit 1 = Enable Not Me Unicast Filtering 0 = Disable Not Me Unicast Filtering This bit allows the user to accept all unicast packets whose Destination Address does not match the Station Address. MCEN: Multicast Enable bit bit 1 1 = Enable Multicast Filtering 0 = Disable Multicast Filtering This bit allows the user to accept all Multicast Address packets. bit 0 BCEN: Broadcast Enable bit 1 = Enable Broadcast Filtering 0 = Disable Broadcast Filtering This bit allows the user to accept all Broadcast Address packets. Note 1: XOR = True when either one or the other conditions are true, but not both. 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

# Note 1: This register is only used for RX operations. 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | —                 | _                 | _                 | _                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |