Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32 <sup>®</sup> M-Class                                                      |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efh064-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.4 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available from the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.5 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements.

# 2.6 Trace

The trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

# 2.7 External Oscillator Pins

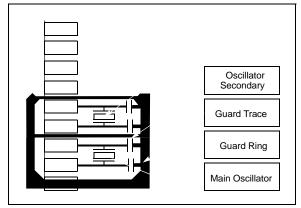

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

#### 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

The MIPS architecture defines that the result of a multiply or divide operation be placed in one of four pairs of HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

The MDU also implements various shift instructions operating on the HI/LO register and multiply instructions as defined in the DSP ASE. The MDU supports all of the data types required for this purpose and includes three extra HI/LO registers as defined by the ASE.

Table 3-2 lists the latencies and repeat rates for the DSP multiply and dot-product operations. The approximate latencies and repeat rates are listed in terms of pipeline clocks.

| TABLE 3-2: | DSP-RELATED LATENCIES |

|------------|-----------------------|

|            | AND REPEAT RATES      |

| Op code                                                        | Latency | Repeat<br>Rate |

|----------------------------------------------------------------|---------|----------------|

| Multiply and dot-product without saturation after accumulation | 5       | 1              |

| Multiply and dot-product with saturation after accumulation    | 5       | 1              |

| Multiply without accumulation                                  | 5       | 1              |

#### 3.1.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation and cache protocols, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as cache size and set associativity, and the presence of options like microMIPS is also available by accessing the CP0 registers, listed in Table 3-3.

| Register<br>Number | Register<br>Name       | Function                                                                                                                                                    |

|--------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | Index                  | Index into the TLB array (MPU only).                                                                                                                        |

| 1                  | Random                 | Randomly generated index into the TLB array (MPU only).                                                                                                     |

| 2                  | EntryLo0               | Low-order portion of the TLB entry for even-numbered virtual pages (MPU only).                                                                              |

| 3                  | EntryLo1               | Low-order portion of the TLB entry for odd-numbered virtual pages (MPU only).                                                                               |

| 4                  | Context/<br>UserLocal  | Pointer to the page table entry in memory (MPU only).<br>User information that can be written by privileged software and read via the RDHWR<br>instruction. |

| 5                  | PageMask/<br>PageGrain | PageMask controls the variable page sizes in TLB entries. PageGrain enables support<br>of 1 KB pages in the TLB (MPU only).                                 |

| 6                  | Wired                  | Controls the number of fixed (i.e., wired) TLB entries (MPU only).                                                                                          |

| 7                  | HWREna                 | Enables access via the RDHWR instruction to selected hardware registers in Non-privileged mode.                                                             |

| 8                  | BadVAddr               | Reports the address for the most recent address-related exception.                                                                                          |

|                    | BadInstr               | Reports the instruction that caused the most recent exception.                                                                                              |

|                    | BadInstrP              | Reports the branch instruction if a delay slot caused the most recent exception.                                                                            |

| 9                  | Count                  | Processor cycle count.                                                                                                                                      |

| 10                 | EntryHi                | High-order portion of the TLB entry (MPU only).                                                                                                             |

| 11                 | Compare                | Core timer interrupt control.                                                                                                                               |

#### TABLE 3-3: COPROCESSOR 0 REGISTERS

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0   |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|--------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |  |  |

| 31:24        | —                 | —                 | _                 | _                 | -                 | _                 | —                | _                  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |  |  |

| 15:8         | —                 | _                 | _                 | _                 | -                 | _                 | _                |                    |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0                |  |  |

| 7:0          |                   |                   |                   | _                 |                   |                   | GROU             | <sup>D</sup> <1:0> |  |  |

#### **REGISTER 4-4:** SBTxELOG2: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 2 ('x' = 0-13)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

#### bit 31-3 Unimplemented: Read as '0'

- bit 1-0 GROUP<1:0>: Requested Permissions Group bits

- 11 = Group 3

- 10 = Group 2

- 01 = Group 1

- 00 = Group 0

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

#### REGISTER 4-5: SBTxECON: SYSTEM BUS TARGET 'x' ERROR CONTROL REGISTER ('x' = 0-13)

|              |                   | x = 0 = 13        |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        | —                 | —                 | _                 | _                 | _                 |                   | _                | ERRP             |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | -                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | —                 |                   |                   |                   |                   |                   |                  | —                |

| Legend:           |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-25 Unimplemented: Read as '0'

bit 24 ERRP: Error Control bit

1 = Report protection group violation errors

0 = Do not report protection group violation errors

bit 23-0 Unimplemented: Read as '0'

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

# 5.1 Flash Control Registers

# TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | Ð             |           | Bits            |       |        |       |       |       |        |            |         | Ś    |        |       |       |        |       |            |

|-----------------------------|------------------------|---------------|-----------|-----------------|-------|--------|-------|-------|-------|--------|------------|---------|------|--------|-------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range     | 31/15     | 30/14           | 29/13 | 28/12  | 27/11 | 26/10 | 25/9  | 24/8   | 23/7       | 22/6    | 21/5 | 20/4   | 19/3  | 18/2  | 17/1   | 16/0  | All Resets |

| 0600                        | NVMCON <sup>(1)</sup>  | 31:16         | _         |                 | _     | —      | —     | —     |       |        | _          | _       | —    | —      | —     | —     |        | —     | 0000       |

| 0000                        | NVINCON                | 15:0          | WR        | WREN            | WRERR | LVDERR | —     | _     |       |        | PFSWAP     | BFSWAP  | _    | _      |       | NVMO  | P<3:0> |       | 00x0       |

| 0610                        | NVMKEY                 | 31:16<br>15:0 |           | NVMKEY<31:0>    |       |        |       |       |       |        |            |         |      | 0000   |       |       |        |       |            |

| 0620                        | NVMADDR <sup>(1)</sup> | 31:16<br>15:0 |           |                 |       |        |       |       |       |        |            |         |      | 0000   |       |       |        |       |            |

| 0630                        | NVMDATA0               | 31:16<br>15:0 |           | NVMDATA0<31:0>  |       |        |       |       |       |        |            |         |      | 0000   |       |       |        |       |            |

| 0640                        | NVMDATA1               | 31:16<br>15:0 |           | NV/MDATA1<31:05 |       |        |       |       |       |        |            |         |      | 0000   |       |       |        |       |            |

| 0650                        | NVMDATA2               | 31:16<br>15:0 |           | NV/MDATA2<31:05 |       |        |       |       |       |        |            |         |      | 0000   |       |       |        |       |            |

| 0660                        | NVMDATA3               | 31:16<br>15:0 |           |                 |       |        |       |       |       | NVMD   | ATA3<31:0> |         |      |        |       |       |        |       | 0000       |

| 0670                        | NVMSRC<br>ADDR         | 31:16<br>15:0 |           |                 |       |        |       |       |       | NVMSRC | ADDR<31:0> |         |      |        |       |       |        |       | 0000       |

| 0000                        | NVMPWP <sup>(1)</sup>  | 31:16         | PWPULOCK  | _               | _     | _      | —     | —     | _     | _      |            |         |      | PWP<23 | :16>  |       |        |       | 8000       |

| 0680                        | NVMPWP                 | 15:0          |           |                 | •     |        |       |       |       | PW     | P<15:0>    |         |      |        |       |       |        |       | 0000       |

| 0690                        | NVMBWP <sup>(1)</sup>  | 31:16         | —         | _               | —     | —      | _     | —     | _     | _      | _          | —       |      | —      | —     | —     | _      | —     | 0000       |

| 0090                        |                        | 15:0          | LBWPULOCK | _               | —     | LBWP4  | LBWP3 | LBWP2 | LBWP1 | LBWP0  | UBWPULOCK  | —       | _    | UBWP4  | UBWP3 | UBWP2 | UBWP1  | UBWP0 | 9FDF       |

| 0640                        | NVMCON2 <sup>(1)</sup> | 31:16         | _         | _               | —     | —      | —     | —     | —     | _      | —          | —       | —    | —      | —     | —     | _      | —     | 001F       |

| 0040                        |                        | 15:0          | _         | I               | —     | —      | —     | _     | 1     |        | SWAPLO     | CK<1:0> | —    | _      | _     | _     | -      |       | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

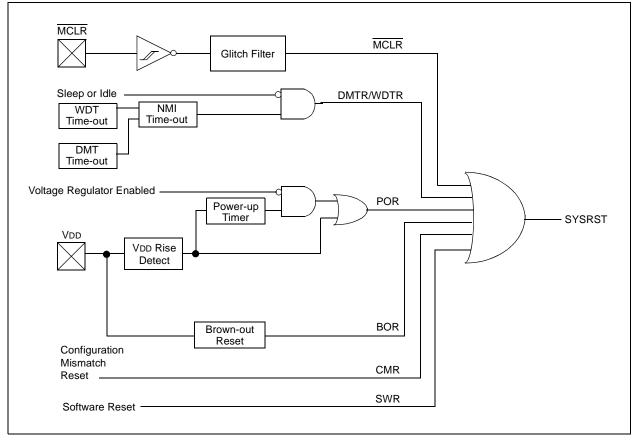

# 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7**. "**Resets**" (DS60001118) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The device Reset sources are as follows:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

- Deadman Timer Reset (DMTR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

# FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | R/W-0, HS         | R/W-0, HS         | U-0                | U-0                |  |  |

| 31:24        | _                 | —                 | _                 | —                 | BCFGERR           | BCFGFAIL          | —                  | —                  |  |  |

| 23:16        | U-0                | U-0                |  |  |

| 23.10        | _                 | —                 | _                 | —                 | —                 | —                 | _                  | —                  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | U-0                |  |  |

| 15.0         | _                 | —                 | _                 | —                 | —                 | —                 | CMR                | —                  |  |  |

| 7.0          | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |  |  |

| 7:0          | EXTR              | SWR               | DMTO              | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |  |  |

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Hardware Set | HC = Hardware Cleared              |                    |  |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 31-28 | Unimplemented: Read as ' | 0 |

|-----------|--------------------------|---|

|-----------|--------------------------|---|

|        | <b>BCFGERR:</b> Primary Configuration Registers Error Flag bit 1 = An error occurred during a read of the primary configuration registers |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

|        | 0 = No error occurred during a read of the primary configuration registers                                                                |

| bit 26 | BCFGFAIL: Primary/Secondary Configuration Registers Error Flag bit                                                                        |

| 1 = An error | occurred | during a | read of | of the p | primary | and | alternate | configuration | registers |

|--------------|----------|----------|---------|----------|---------|-----|-----------|---------------|-----------|

| 0 = No error | occurred | during a | read    | of the   | primary | and | alternate | configuration | registers |

bit 25-10 **Unimplemented:** Read as '0'

| bit 9 | <b>CMR:</b> Configuration Mismatch Reset Flag bit<br>1 = A Configuration Mismatch Reset has occurred<br>0 = A Configuration Mismatch Reset has not occurred |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8 | Unimplemented: Read as '0'                                                                                                                                  |

| bit 7 | <b>EXTR:</b> External Reset (MCLR) Pin Flag bit<br>1 = Master Clear (pin) Reset has occurred                                                                |

- 0 = Master Clear (pin) Reset has not occurred

- bit 6 SWR: Software Reset Flag bit

- 1 = Software Reset was executed

- 0 = Software Reset was not executed

- bit 5 DMTO: Deadman Timer Time-out Flag bit

- 1 = A DMT time-out has occurred

- 0 = A DMT time-out has not occurred

- bit 4 WDTO: Watchdog Timer Time-out Flag bit

- 1 = WDT Time-out has occurred

- 0 = WDT Time-out has not occurred

- bit 3 **SLEEP:** Wake From Sleep Flag bit 1 = Device was in Sleep mode

- 0 = Device was not in Sleep mode

- bit 2 **IDLE:** Wake From Idle Flag bit 1 = Device was in Idle mode 0 = Device was not in Idle mode

- bit 1 **BOR:** Brown-out Reset Flag bit<sup>(1)</sup> 1 = Brown-out Reset has occurred 0 = Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup>

- 1 = Power-on Reset has occurred

- 0 = Power-on Reset has not occurred

**Note 1:** User software must clear this bit to view the next detection.

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>f)                  | <b>b</b> -                      | Ð         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | Ś          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Recete |

|                             | 055000                          | 31:16     | _     | _     | —     | _     | _     | _     | —    | _          |      | _    | _    | _    | —    | _    | VOFF< | 17:16> | 00         |

| 0548                        | OFF002                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      | •     | —      | 000        |

| 0540                        | OFF003                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | —          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 000        |

| J54C                        | 0FF003                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 000        |

| 0550                        | OFF004                          | 31:16     | _     | _     | —     | —     |       | -     | —    | _          |      | _    | -    | _    | _    | _    | VOFF< | 17:16> | 000        |

| 0550                        | 011004                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 0554                        | OFF005                          | 31:16     | _     | -     | —     | —     | -     | -     | —    | —          | _    | —    | -    | -    | —    | -    | VOFF< | 17:16> | 000        |

| 0554                        | 011005                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 00         |

| 0558                        | OFF006                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 000        |

| 0550                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 155C                        | OFF007                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 00         |

|                             | 011007                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 00         |

| 0560                        | OFF008                          | 31:16     | _     | -     | —     | —     | -     | -     | —    | —          | _    | —    | -    | -    | —    | -    | VOFF< | 17:16> | 00         |

| 0500                        | 011000                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 000        |

| 0564                        | OFF009                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 00         |

| 0004                        | 011005                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 00         |

| 0568                        | OFF010                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 00         |

| 0000                        | 011010                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       |        | 000        |

| 156C                        | OFF011                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 000        |

| 0000                        | onioni                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0570                        | OFF012                          | 31:16     | —     | —     | —     | —     | —     | —     |      | —          | —    | —    | _    | —    | —    | —    | VOFF< | 17:16> | 00         |

| 0010                        | 011012                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0574                        | OFF013                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          |      | —    | —    | —    | —    | —    | VOFF< | 17:16> | 00         |

| 0374                        | 011013                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0578                        | OFF014                          | 31:16     | —     | —     | —     | —     | _     | _     | _    | —          |      | —    | —    | —    |      | —    | VOFF< | 17:16> | 000        |

| 0070                        | 011014                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0570                        | OFF015                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 000        |

|                             | 0.7010                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0580                        | OFF016                          | 31:16     | _     | _     | —     | —     | —     | —     | —    | —          | —    | —    | —    | _    | —    | —    | VOFF< | 17:16> | 000        |

| 0000                        | 011010                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 000        |

© 2015-2016 Microchip Technology Inc.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

- Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

- Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

<sup>2:</sup>

| ess                         |                                 |                      |                |       |          |       |          |       |      | Bit    | s      |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|----------------------|----------------|-------|----------|-------|----------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range            | 31/15          | 30/14 | 29/13    | 28/12 | 27/11    | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH2CPTR                        | 31:16                | —              |       | —        | _     | —        | _     | —    | —      | —      | _      |        | —      | _      | _      | —      |        | 000        |

| 1200                        | DUHZUFIK                        | 15:0                 |                |       |          |       |          |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |        | 000        |

| 1000                        | DCH2DAT                         | 31:16                | _              | _     | _        | _     | _        | —     | _    | _      | _      | _      |        | _      |        |        | —      |        | 000        |

| 290                         | DCH2DAI                         | 15:0                 | ) CHPDAT<15:0> |       |          |       |          |       |      |        |        |        |        | 000    |        |        |        |        |            |

| 1240                        | DCH3CON                         | 31:16 CHPIGN<7:0>    |                |       |          |       |          |       |      | _      | _      | 000    |        |        |        |        |        |        |            |

| IZAU                        | DCH3CON                         | 15:0                 | CHBUSY         |       | CHPIGNEN | _     | CHPATLEN |       | _    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | l<1:0> | 000        |

| 2B0                         | DCH3ECON                        | DN 31:16 CHAIRQ<7:0> |                |       |          |       |          |       |      |        |        | 00F    |        |        |        |        |        |        |            |

| 1200                        | DOINCEOUN                       | 15:0                 |                |       |          |       | Q<7:0>   |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | —      | —      | _      | FFC        |

| 12C0                        | DCH3INT                         | 31:16                | —              | —     | —        | —     | —        | _     | —    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 000        |

|                             |                                 | 15:0                 | —              |       | —        | _     | —        |       | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 000        |

| 2D0                         | DCH3SSA                         | 31:16<br>15:0        | CHSSA<31:0>    |       |          |       |          |       |      |        |        |        |        |        |        |        |        |        |            |

|                             |                                 |                      | 31-1           |       |          |       |          |       |      |        |        |        |        |        |        |        |        |        |            |

| 12E0                        | DCH3DSA                         |                      | CHDSA<31:0>    |       |          |       |          |       |      |        |        |        |        |        |        |        |        |        |            |

|                             |                                 | 31:16                | _              | _     |          | _     |          | _     | _    | _      | _      | _      | _      | _      | _      | _      | _      | _      | 000        |

| 2F0                         | DCH3SSIZ                        | 15:0                 |                |       |          |       |          |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |        | 000        |

|                             |                                 | 31:16                | _              | _     | —        | _     | —        | _     | —    | _      | —      | _      | _      | —      | _      | _      | —      | _      | 000        |

| 300                         | DCH3DSIZ                        | 15:0                 | •              |       |          |       |          |       |      | CHDSIZ | <15:0> |        |        | •      |        |        |        |        | 000        |

| 1310                        | DCH3SPTR                        | 31:16                | —              | _     | —        | _     | —        | _     | —    | —      | _      | —      | _      | —      | _      | —      | —      | —      | 000        |

| 1010                        |                                 | 15:0                 |                |       |          |       |          |       |      | CHSPTR | <15:0> |        |        |        |        |        |        |        | 000        |

| 320                         | DCH3DPTR                        | 31:16                | —              | _     | —        | _     | —        | _     | —    |        | —      | —      | —      | —      | —      | —      | —      | —      | 000        |

|                             |                                 | 15:0                 |                |       |          |       |          |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |        | 000        |

| 330                         | DCH3CSIZ                        | 31:16<br>15:0        | —              |       | —        |       | —        |       | _    | CHCSIZ |        |        | _      | _      | _      | _      | _      | _      | 000        |

|                             |                                 | 31:16                | _              |       | _        |       | [        |       |      |        | <15:0> |        |        |        |        |        |        | _      | 000        |

| 1340                        | DCH3CPTR                        | 15:0                 | _              | _     | _        | _     | _        | _     | _    | CHCPTR |        | _      | _      | _      | _      | _      | _      |        | 000        |

|                             |                                 | 31:16                | _              | _     |          | _     |          | _     | _    |        | _      | _      | _      | _      | _      | _      | _      | _      | 000        |

| 1350                        | DCH3DAT                         | 15:0                 |                |       |          |       |          |       |      | CHPDAT | <15:0> |        |        |        |        |        |        |        | 000        |

|                             |                                 | 31:16                |                |       |          | CHPIG | N<7:0>   |       |      |        | _      |        | _      | _      | _      |        |        |        | 000        |

| 360                         | DCH4CON                         |                      | CHBUSY         | _     | CHPIGNEN |       | CHPATLEN | _     |      | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | l<1:0> | 000        |

| 070                         | DOLIAEOON                       | 31:16                | _              | _     | —        | _     | —        | _     | —    | —      |        |        |        | CHAIR  | Q<7:0> |        | •      |        | 00F        |

| 370                         | DCH4ECON                        | 15:0                 |                |       |          | CHSIR | Q<7:0>   |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | —      | —      | _      | FF0        |

| 380                         | DCH4INT                         | 31:16                | —              | _     | —        | _     | —        | _     | _    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 000        |

| 1000                        | DOLIHINI                        | 15:0                 | —              | _     | —        | _     | —        | _     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

#### TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |  |

| 31:24        | —                 | —                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO             |  |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                     | —                 | —                 | —                  | _                 | _                | —                |  |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | —                 | —                     | _                 | PLEN<4:0>         |                    |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | —                  | (                 | CRCCH<2:0>       |                  |  |

#### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

# Legend:

| - J      |            |                  |                                    |                    |  |  |

|----------|------------|------------------|------------------------------------|--------------------|--|--|

| R = Rea  | adable bit | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Val | lue at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 **BYTO<1:0>:** CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 WBO: CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

# TABLE 12-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                       |           | Bits  |       |       |       |       |       |      |      |      |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 15B4                        | RPC13R                | 31:16     | _     |       | —     |       | _     |       |      | _    |      | —    | —    | —    | —    | —     | _      | -    | 0000       |

| 1364                        | RECISK                | 15:0      | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    |      | RPC13 | R<3:0> |      | 0000       |

| 15B8                        | RPC14R                | 31:16     | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1300                        | KFC14K                | 15:0      | _     |       | _     |       | —     |       |      | _    |      | -    | _    | _    |      | RPC14 | R<3:0> |      | 0000       |

| 15C0                        | RPD0R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1300                        | REDOR                 | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD0  | R<3:0> |      | 0000       |

| 15C4                        | RPD1R                 | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 1304                        | REDIK                 | 15:0      | —     |       | —     | _     | —     | _     |      | —    | _    | —    | —    | —    |      | RPD1  | R<3:0> |      | 0000       |

| 15C8                        | RPD2R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1300                        | KF D2K                | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | RPD2  | R<3:0> |      | 0000       |

| 15CC                        | RPD3R                 | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1300                        | KF D3K                | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD3  | R<3:0> |      | 0000       |

| 15D0                        | RPD4R                 | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 1300                        | KF D4K                | 15:0      | _     | _     | _     | -     | —     | _     | _    | —    | -    | _    | _    | _    |      | RPD4  | R<3:0> |      | 0000       |

| 15D4                        | RPD5R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1304                        | REDSK                 | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | RPD5  | R<3:0> |      | 0000       |

| 15D8                        | RPD6R <sup>(2)</sup>  | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 1300                        | KFD0K*/               | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD6  | R<3:0> |      | 0000       |

| 15DC                        | RPD7R <sup>(2)</sup>  | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 1300                        | KFD/K·/               | 15:0      | _     | _     | _     | -     | —     | _     | _    | —    | -    | —    | _    | _    |      | RPD7  | R<3:0> |      | 0000       |

| 15E4                        | RPD9R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1324                        | KF D9K                | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | RPD9  | R<3:0> |      | 0000       |

| 15E8                        | RPD10R                | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | _     | —      | —    | 0000       |

| 1020                        | IN DIGIN              | 15:0      | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    |      | RPD10 | R<3:0> |      | 0000       |

| 15EC                        | RPD11R                | 31:16     | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1020                        | KI DIIK               | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD11 | R<3:0> |      | 0000       |

| 15F0                        | RPD12R <sup>(1)</sup> | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1010                        | KI DIZIK <sup>1</sup> | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD12 | R<3:0> |      | 0000       |

| 15F8                        | RPD14R <sup>(1)</sup> | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 101.0                       | IN DI4IN              | 15:0      | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    |      | RPD14 | R<3:0> |      | 0000       |

| 15FC                        | RPD15R <sup>(1)</sup> | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1010                        | N D ION /             | 15:0      | —     | _     |       |       | —     | _     | _    | —    | _    |      | _    |      |      | RPD15 | R<3:0> |      | 0000       |

| 160C                        | RPE3R                 | 31:16     | —     | _     | —     | _     | —     | —     | _    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1000                        | INF LOIN              | 15:0      | —     | -     | —     |       | —     | -     | -    | —    |      | —    | —    | —    |      | RPE3  | R<3:0> |      | 0000       |

| 1614                        | RPE5R                 | 31:16     | _     |       | —     |       | —     |       |      | _    | —    | —    | —    | _    | —    | —     | _      | —    | 0000       |

| 1014                        |                       | 15:0      | —     |       | _     | —     | —     | —     | —    | —    | —    | —    | —    | _    |      | RPE5  | R<3:0> |      | 0000       |

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is not available on 64-pin devices. Note 1:

This register is not available on 64-pin and 100-pin devices. 2:

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     | —                    | —                 | —                 | —                 | —                 | _                 | _                | _                |  |  |

| 00.40     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | —                    | —                 | —                 | —                 | —                 | _                 | _                | _                |  |  |

| 45.0      | R/W-0                | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |

| 15:8      | ON                   | —                 | SIDL              | —                 | —                 | _                 | FEDGE            | C32              |  |  |

| 7.0       | R/W-0                | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | ICTMR <sup>(1)</sup> | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |  |  |

# REGISTER 17-1: ICXCON: INPUT CAPTURE X CONTROL REGISTER

# Legend:

| R = Readabl   | le bit W = Writable bit                                                                                             | U = Unimplemented bit                                      |

|---------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| -n = Bit Valu | e at POR: ('0', '1', x = unknown)                                                                                   | P = Programmable bit r = Reserved bit                      |

| 1 :: 04 40    |                                                                                                                     |                                                            |

| bit 31-16     | Unimplemented: Read as '0'                                                                                          |                                                            |

| bit 15        | <b>ON:</b> Input Capture Module Enable bit                                                                          |                                                            |

|               | 1 = Module is enabled                                                                                               | disable interrupt generation and allow CED modifications   |

| <b>L:</b> 4 4 |                                                                                                                     | , disable interrupt generation and allow SFR modifications |

| bit 14        | Unimplemented: Read as '0'                                                                                          |                                                            |

| bit 13        | SIDL: Stop in Idle Control bit                                                                                      |                                                            |

|               | 1 = Halt in CPU Idle mode                                                                                           |                                                            |

| 1 1 40 40     | 0 = Continue to operate in CPU Idle mode                                                                            |                                                            |

| bit 12-10     | Unimplemented: Read as '0'                                                                                          |                                                            |

| bit 9         | FEDGE: First Capture Edge Select bit (only u                                                                        | used in mode 6, ICM<2:0> = $110$ )                         |

|               | 1 = Capture rising edge first                                                                                       |                                                            |

| L:1.0         | 0 = Capture falling edge first                                                                                      |                                                            |

| bit 8         | <b>C32:</b> 32-bit Capture Select bit                                                                               |                                                            |

|               | 1 = 32-bit timer resource capture                                                                                   |                                                            |

| hit 7         | 0 = 16-bit timer resource capture                                                                                   | r coloction when C22 (ICyCON (9. ) is (1/)(1)              |

| bit 7         | ICTMR: Timer Select bit (Does not affect time                                                                       | er selection when C32 (ICXCON<8>) is 1)(**                 |

|               | <ul><li>0 = Timery is the counter source for capture</li><li>1 = Timerx is the counter source for capture</li></ul> |                                                            |

| bit 6-5       | ICI<1:0>: Interrupt Control bits                                                                                    |                                                            |

| DIL 0-5       | 11 = Interrupt on every fourth capture event                                                                        |                                                            |

|               | 10 = Interrupt on every third capture event<br>10 = Interrupt on every third capture event                          |                                                            |

|               | 01 = Interrupt on every second capture even                                                                         | nt                                                         |

|               | 00 = Interrupt on every capture event                                                                               |                                                            |

| bit 4         | <b>ICOV:</b> Input Capture Overflow Status Flag bit                                                                 | (read-only)                                                |

|               | 1 = Input capture overflow is occurred                                                                              |                                                            |

|               | 0 = No input capture overflow is occurred                                                                           |                                                            |

| bit 3         | ICBNE: Input Capture Buffer Not Empty State                                                                         | us bit (read-only)                                         |

|               | 1 = Input capture buffer is not empty; at least                                                                     |                                                            |

|               | 0 = Input capture buffer is empty                                                                                   | ·                                                          |

| bit 2-0       | ICM<2:0>: Input Capture Mode Select bits                                                                            |                                                            |

|               | 111 = Interrupt-Only mode (only supported v                                                                         | while in Sleep mode or Idle mode)                          |

|               |                                                                                                                     | edge, specified edge first and every edge thereafter       |

|               | 101 = Prescaled Capture Event mode - eve                                                                            |                                                            |

|               | 100 = Prescaled Capture Event mode - eve                                                                            | ry fourth rising edge                                      |

|               | 011 = Simple Capture Event mode – every r                                                                           | ising edge                                                 |

|               | 010 = Simple Capture Event mode – every f                                                                           |                                                            |

|               | 001 = Edge Detect mode – every edge (risin                                                                          | ng and falling)                                            |

|               | 000 = Input Capture module is disabled                                                                              |                                                            |

**Note 1:** Refer to Table 17-1 for Timerx and Timery selections.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | -                 | _                 | _                 | _                 | -                 |                  | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | -                 | _                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | PTEN<             | :15:14>           | PTEN<13:8>        |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | PTEN<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 23-6: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-15 Unimplemented: Read as '0'

- bit 15-14 **PTEN<15:14>:** PMCS1 Strobe Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS1 and PMCS2<sup>(1)</sup>

0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits

- 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 PTEN<1:0>: PMALH/PMALL Strobe Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15 and PMA14 or CS1 and CS2 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | -                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | —                | —                |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | _                 | _                 | _                 | TRPD<11:8>        |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | TRPD<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |

# REGISTER 24-4: EBIFTRPD: EXTERNAL BUS INTERFACE FLASH TIMING REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-12 Unimplemented: Read as '0'

#### bit 11-0 TRPD<11:0>: Flash Timing bits

These bits define the number of clock cycles to wait after resetting the external Flash memory before any read/write access.

| REGISTE   | R 29-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4 (CONTINUED)                                                            |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| bit 15    | FLTEN17: Filter 13 Enable bit                                                                                            |  |  |  |  |  |

|           | 1 = Filter is enabled                                                                                                    |  |  |  |  |  |

|           | 0 = Filter is disabled                                                                                                   |  |  |  |  |  |

| bit 14-13 | MSEL17<1:0>: Filter 17 Mask Select bits                                                                                  |  |  |  |  |  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |  |  |  |  |  |

|           | 10 = Acceptance Mask 2 selected                                                                                          |  |  |  |  |  |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                       |  |  |  |  |  |

| h:+ 40.0  |                                                                                                                          |  |  |  |  |  |

| bit 12-8  | FSEL17<4:0>: FIFO Selection bits                                                                                         |  |  |  |  |  |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |  |  |  |  |  |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |  |  |  |  |  |

|           | •                                                                                                                        |  |  |  |  |  |

|           |                                                                                                                          |  |  |  |  |  |

|           | •                                                                                                                        |  |  |  |  |  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |  |  |  |  |  |

| bit 7     | FLTEN16: Filter 16 Enable bit                                                                                            |  |  |  |  |  |

|           | 1 = Filter is enabled                                                                                                    |  |  |  |  |  |

|           | 0 = Filter is disabled                                                                                                   |  |  |  |  |  |

| bit 6-5   | MSEL16<1:0>: Filter 16 Mask Select bits                                                                                  |  |  |  |  |  |