Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efh064-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |                        | Pin Nu          | mber            |                          |             |                |                                   |  |  |  |

|-----------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|--|--|--|

| Pin Name        | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |  |  |  |

|                 |                        |                 | •               |                          | PO          | RTA            | ·                                 |  |  |  |

| RA0             | _                      | 17              | A11             | 22                       | I/O         | ST             | PORTA is a bidirectional I/O port |  |  |  |

| RA1             | —                      | 38              | B21             | 56                       | I/O         | ST             |                                   |  |  |  |

| RA2             | —                      | 59              | A41             | 85                       | I/O         | ST             |                                   |  |  |  |

| RA3             | —                      | 60              | B34             | 86                       | I/O         | ST             |                                   |  |  |  |

| RA4             | —                      | 61              | A42             | 87                       | I/O         | ST             |                                   |  |  |  |

| RA5             | —                      | 2               | B1              | 2                        | I/O         | ST             |                                   |  |  |  |

| RA6             | —                      | 89              | A61             | 129                      | I/O         | ST             |                                   |  |  |  |

| RA7             | —                      | 90              | B51             | 130                      | I/O         | ST             |                                   |  |  |  |

| RA9             | —                      | 28              | B15             | 39                       | I/O         | ST             |                                   |  |  |  |

| RA10            | _                      | 29              | A20             | 40                       | I/O         | ST             | ]                                 |  |  |  |

| RA14            | _                      | 66              | B37             | 95                       | I/O         | ST             |                                   |  |  |  |

| RA15            | _                      | 67              | A45             | 96                       | I/O         | ST             |                                   |  |  |  |

|                 |                        |                 |                 |                          | PO          | RTB            |                                   |  |  |  |

| RB0             | 16                     | 25              | A18             | 36                       | I/O         | ST             | PORTB is a bidirectional I/O port |  |  |  |

| RB1             | 15                     | 24              | A17             | 35                       | I/O         | ST             |                                   |  |  |  |

| RB2             | 14                     | 23              | A16             | 34                       | I/O         | ST             |                                   |  |  |  |

| RB3             | 13                     | 22              | A14             | 31                       | I/O         | ST             |                                   |  |  |  |

| RB4             | 12                     | 21              | A13             | 26                       | I/O         | ST             |                                   |  |  |  |

| RB5             | 11                     | 20              | B11             | 25                       | I/O         | ST             |                                   |  |  |  |

| RB6             | 17                     | 26              | B14             | 37                       | I/O         | ST             |                                   |  |  |  |

| RB7             | 18                     | 27              | A19             | 38                       | I/O         | ST             |                                   |  |  |  |

| RB8             | 21                     | 32              | B18             | 47                       | I/O         | ST             |                                   |  |  |  |

| RB9             | 22                     | 33              | A23             | 48                       | I/O         | ST             |                                   |  |  |  |

| RB10            | 23                     | 34              | B19             | 49                       | I/O         | ST             | _                                 |  |  |  |

| RB11            | 24                     | 35              | A24             | 50                       | I/O         | ST             | _                                 |  |  |  |

| RB12            | 27                     | 41              | A27             | 59                       | I/O         | ST             | _                                 |  |  |  |

| RB13            | 28                     | 42              | B23             | 60                       | I/O         | ST             | -                                 |  |  |  |

| RB14            | 29                     | 43              | A28             | 61                       | I/O         | ST             | -                                 |  |  |  |

| RB15            | 30                     | 44              | B24             | 62                       | I/O         | ST             |                                   |  |  |  |

| <b>D</b> O1     |                        | -               |                 |                          |             | RTC            |                                   |  |  |  |

| RC1             | —                      | 6               | B3              | 6                        | I/O         | ST             | PORTC is a bidirectional I/O port |  |  |  |

| RC2             |                        | 7               | A6              | 11                       | I/O         | ST             | 4                                 |  |  |  |

| RC3             |                        | 8               | B5              | 12                       | I/O         | ST             | 4                                 |  |  |  |

| RC4             | -                      | 9               | A7              | 13                       | I/O         | ST             | 4                                 |  |  |  |

| RC12            | 31                     | 49              | B28             | 71                       | I/O         | ST             | 4                                 |  |  |  |

| RC13            | 47                     | 72              | B41             | 105                      | I/O         | ST             | 4                                 |  |  |  |

| RC14            | 48                     | 73              | A49             | 106                      | I/O         | ST             | 4                                 |  |  |  |

| RC15<br>Legend: | 32                     | 50<br>MOS-comp  | A33             | 72                       | I/O         | ST             | Analog input P = Power            |  |  |  |

#### **TABLE 1-6:** PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select I = Input

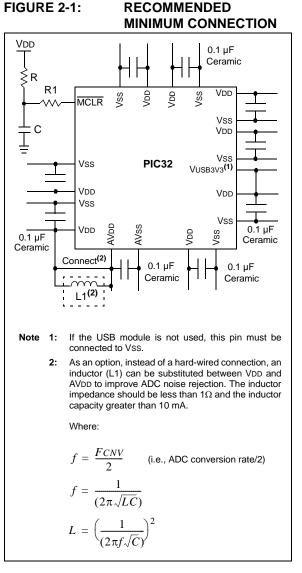

#### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

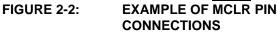

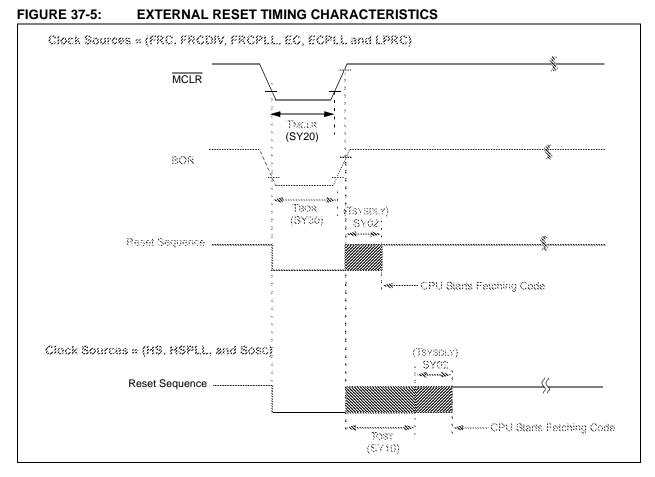

## 2.3 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

Pulling The MCLR pin low generates either a device Reset or a POR, depending on the setting of the SMCLR bit (DEVCFG0<15>). Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

**3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

DS60001320D-page 38

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   |                   | —                 |                   | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   |                   | —                 |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | _                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   |                   |                   | FCC<              | 7:0>              |                   |                  |                  |

### REGISTER 3-7: FCCR: FLOATING POINT CONDITION CODES REGISTER; CP1 REGISTER 25

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FCC<7:0>:** Floating Point Condition Code bits These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

#### TABLE 4-19: SYSTEM BUS TARGET 11 REGISTER MAP

| SSS                         |                  |           |       |       |       |          |          |       |       |      | Bits      |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|-----------|-------|----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7      | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| AC20                        |                  | 31:16     | MULTI | —     | —     | —        |          | CODE  | <3:0> |      | _         | —     |          |      | —      | —      | —       |        | 0000          |

| AC20                        | SBITTELOGI       | 15:0      |       |       |       | INI      | ΓID<7:0> |       |       |      |           | REGIO | N<3:0>   |      | —      | C      | MD<2:0> |        | 0000          |

| AC24                        | SBT11ELOG2       | 31:16     | _     | -     | _     | —        | -        | -     | _     | -    | _         | -     |          |      | —      | -      | -       |        | 0000          |

| AC24                        | 3BTTTELOG2       | 15:0      | _     | -     | _     | —        | -        | -     | _     | -    | _         | -     |          |      | —      | -      | GROU    | P<1:0> | 0000          |

| AC28                        | SBT11ECON        | 31:16     | _     | -     | _     | —        | -        | -     | _     | ERRP | _         | -     |          |      | —      | -      | -       |        | 0000          |

| AC20                        | SBITTECON        | 15:0      | _     | -     | _     | —        | -        | -     | _     | -    | _         | -     |          |      | —      | -      | -       |        | 0000          |

| AC30                        | SBT11ECLRS       | 31:16     | —     | —     | —     | —        | _        | —     | —     | _    | _         | —     | _        | _    | —      | _      | —       | -      | 0000          |

| AC30                        | SBITTECERS       | 15:0      | —     | _     | —     | —        | —        | —     | —     | —    | _         | —     | _        | _    | —      | _      | —       | CLEAR  | 0000          |

| AC 38                       | SBT11ECLRM       | 31:16     | —     | _     | —     | —        | —        | —     | —     | —    | _         | —     | _        | _    | —      | _      | —       | _      | 0000          |

| AC30                        | SBITTECERM       | 15:0      | —     | -     | _     | —        | _        | _     | —     | _    | _         | —     | _        | _    | _      | —      | —       | CLEAR  | 0000          |

| AC40                        | SBT11REG0        | 31:16     |       |       |       |          |          |       |       | BA   | ASE<21:6> |       |          |      |        |        |         | xxxx   |               |

| 7040                        | SBITIKEGO        | 15:0      |       | _     | BA    | ASE<5:0> | -        | -     | PRI   | —    |           | -     | SIZE<4:0 | >    |        | —      | —       |        | xxxx          |

| AC50                        | SBT11RD0         | 31:16     | —     | —     | _     | _        | _        | _     | —     | _    | _         | _     | _        | _    | _      | _      | _       | _      | xxxx          |

| 7030                        | 30111120         | 15:0      | —     | —     | _     | _        | _        | _     | —     | _    | _         | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC58                        | SBT11WR0         | 31:16     | —     | —     | —     | —        | —        | —     | —     | —    | —         | —     | _        |      | —      | —      | —       |        | xxxx          |

| //000                       | OBIIII           | 15:0      | —     | —     | —     | —        | —        | —     | —     | —    | —         | —     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC60                        | SBT11REG1        | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6>  |       |          |      |        |        |         |        | xxxx          |

| /.000                       | OBTINEOT         | 15:0      |       |       | BA    | ASE<5:0> |          |       | PRI   |      | SIZE<4:0> |       |          |      | _      | _      | _       | xxxx   |               |

| AC70                        | SBT11RD1         | 31:16     | —     | —     | —     | —        | —        | —     | —     | —    | —         | —     | _        | _    | —      | —      | —       | —      | xxxx          |

|                             | 55111151         | 15:0      | —     | —     | —     | —        | —        | —     | —     | —    | —         | —     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC78                        | SBT11WR1         | 31:16     | —     | —     | —     | —        | —        | —     | —     | —    | —         | —     | _        | _    | —      | —      | —       | —      | xxxx          |

|                             | C78 SBITTWRT     | 15:0      | _     | —     | _     | —        | _        | _     | —     | _    | _         | _     | -        | -    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note:** For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>f)                  | <b>b</b> -a                     | e         |               |               |              |          |                         |                         |                       | Bi                    | ts                          |                        |            |                        |            |                         |                         |                        | s          |

|-----------------------------|---------------------------------|-----------|---------------|---------------|--------------|----------|-------------------------|-------------------------|-----------------------|-----------------------|-----------------------------|------------------------|------------|------------------------|------------|-------------------------|-------------------------|------------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13        | 28/12    | 27/11                   | 26/10                   | 25/9                  | 24/8                  | 23/7                        | 22/6                   | 21/5       | 20/4                   | 19/3       | 18/2                    | 17/1                    | 16/0                   | All Resets |

|                             | u= o.o(6)                       | 31:16     | CNKIE         | CNJIE         | CNHIE        | CNGIE    | CNFIE                   | CNEIE                   | CNDIE                 | CNCIE                 | CNBIE                       | CNAIE                  | I2C1MIE    | I2C1SIE                | I2C1BIE    | U1TXIE                  | U1RXIE                  | U1EIE                  | 0000       |

| 00F0                        | IEC3 <sup>(6)</sup>             | 15:0      | SPI1TXIE      | SPI1RXIE      | SPI1EIE      | -        | CRPTIE <sup>(7)</sup>   | SBIE                    | CFDCIE                | CPCIE                 | ADCD44IE                    | ADCD43IE               | ADCD42IE   | ADCD41IE               | ADCD40IE   | ADCD39IE                | ADCD38IE                | ADCD37IE               | 0000       |

| 04.00                       | 1504                            | 31:16     | <b>U3TXIE</b> | <b>U3RXIE</b> | <b>U3EIE</b> | SPI3TXIE | SPI3RXIE                | SPI3EIE                 | ETHIE                 | CAN2IE <sup>(3)</sup> | CAN1IE <sup>(3)</sup>       | 12C2MIE <sup>(2)</sup> | 12C2SIE(2) | I2C2BIE <sup>(2)</sup> | U2TXIE     | U2RXIE                  | U2EIE                   | SPI2TXIE               | 0000       |

| 0100                        | IEC4                            | 15:0      | SPI2RXIE      | SPI2EIE       | DMA7IE       | DMA6IE   | DMA5IE                  | DMA4IE                  | <b>DMA3IE</b>         | DMA2IE                | DMA1IE                      | DMA0IE                 | USBDMAIE   | USBIE                  | CMP2IE     | CMP1IE                  | PMPEIE                  | PMPIE                  | 0000       |

| 0110                        |                                 | 31:16     | _             | U6TXIE        | U6RXIE       | U6EIE    | SPI6TXIE <sup>(2)</sup> | SPI6RXIE <sup>(2)</sup> | SPI6IE <sup>(2)</sup> | I2C5MIE               | I2C5SIE                     | I2C5BIE                | U5TXIE     | U5RXIE                 | U5EIE      | SPI5TXIE <sup>(2)</sup> | SPI5RXIE <sup>(2)</sup> | SPI5EIE <sup>(2)</sup> | 0000       |

| 0110                        | IECS                            | 15:0      | I2C4MIE       | I2C4SIE       | I2C4BIE      | U4TXIE   | U4RXIE                  | U4EIE                   | SQI1IE                | PREIE                 | FCEIE                       | RTCCIE                 | SPI4TXIE   | SPI4RXIE               | SPI4EIE    | I2C3MIE                 | I2C3SIE                 | I2C3BIE                | 0000       |

| 04.00                       | 1500                            | 31:16     | _             | _             | _            | _        | _                       | _                       | _                     | —                     | _                           | _                      | ADC7WIE    | _                      | _          | ADC4WIE                 | ADC3WIE                 | ADC2WIE                | 0000       |

| 0120                        | IEC6                            | 15:0      | ADC1WIE       | ADC0WIE       | ADC7EIE      | _        | —                       | ADC4EIE                 | ADC3EIF               | ADC2EIE               | ADC1EIE                     | ADC0EIE                | —          | ADCGRPIE               | _          | ADCURDYIE               | ADCARDYIE               | ADCEOSIE               | 0000       |

| 04.40                       |                                 | 31:16     | _             | _             | _            |          | INT0IP<2:0>             |                         | INTOIS                | 6<1:0>                | _                           | _                      | _          |                        | CS1IP<2:0: | >                       | CS1IS                   | i<1:0>                 | 0000       |

| 0140                        | IPC0                            | 15:0      | _             | _             | _            |          | CS0IP<2:0>              |                         | CS0IS                 | <1:0>                 | _                           | _                      | _          | CTIP<2:0>              |            | CTIS<1:0>               |                         | 0000                   |            |

| 0150                        |                                 | 31:16     | _             | _             | _            |          | OC1IP<2:0>              |                         | OC1IS                 | 5<1:0>                | _                           | _                      | —          | IC1IP<2:0>             |            | IC1IS                   | <1:0>                   | 0000                   |            |

| 0150                        | IPC1                            | 15:0      | _             | _             | _            |          | IC1EIP<2:0>             |                         | IC1EIS                | S<1:0>                | _                           | _                      | _          | T1IP<2:0>              |            | T1IS∢                   | <1:0>                   | 0000                   |            |

| 04.00                       | 1000                            | 31:16     | _             | _             | _            |          | IC2IP<2:0>              |                         | IC2IS                 | <1:0>                 | _                           | _                      | —          | IC2EIP<2:0>            |            | IC2EIS                  | S<1:0>                  | 0000                   |            |

| 0160                        | IPC2                            | 15:0      | _             | _             | _            |          | T2IP<2:0>               |                         | T2IS<                 | <1:0>                 | _                           | _                      | —          | INT1IP<2:0>            |            | INT1IS                  | S<1:0>                  | 0000                   |            |

| 0470                        | IPC3                            | 31:16     | -             | _             | _            |          | IC3EIP<2:0>             |                         | IC3EIS                | S<1:0>                | _                           | -                      | _          | T3IP<2:0>              |            | T3IS<1:0>               |                         | 0000                   |            |

| 0170                        | IPCS                            | 15:0      | -             | _             | _            |          | INT2IP<2:0>             |                         | INT2IS                | S<1:0>                | _                           | -                      | _          | OC2IP<2:0>             |            | OC2IS<1:0>              |                         | 0000                   |            |

| 0180                        |                                 | 31:16     | -             | _             | _            |          | T4IP<2:0>               |                         | T4IS<1:0>             |                       | _                           | -                      | _          | INT3IP<2:0>            |            | INT3IS                  | S<1:0>                  | 0000                   |            |

| 0180                        | IPC4                            | 15:0      | -             | _             | _            |          | OC3IP<2:0>              |                         | OC3IS                 | i<1:0>                | _                           | -                      | _          | IC3IP<2:0>             |            | IC3IS                   | <1:0>                   | 0000                   |            |

| 0400                        | IDOC                            | 31:16     | -             | _             | _            |          | INT4IP<2:0>             |                         | INT4IS<1:0>           |                       | _                           | -                      | _          | OC4IP<2:0>             |            | OC4IS                   | S<1:0>                  | 0000                   |            |

| 0190                        | IPC5                            | 15:0      | _             | _             | _            |          | IC4IP<2:0>              |                         | IC4IS<1:0>            |                       | _                           | _                      | —          |                        | IC4EIP<2:0 | >                       | IC4EIS                  | S<1:0>                 | 0000       |

| 0140                        | IDCC                            | 31:16     | -             | _             | _            |          | OC5IP<2:0>              |                         | OC5IS<1:0>            |                       | _                           | _                      | _          | IC5IP<2:0>             |            | IC5IS                   | <1:0>                   | 0000                   |            |

| 01A0                        | IPCO                            | 15:0      | -             | _             | _            |          | IC5EIP<2:0>             |                         | IC5EIS<1:0>           |                       | _                           | -                      | _          |                        | T5IP<2:0>  |                         | T5IS<                   | <1:0>                  | 0000       |

| 0400                        | 1007                            | 31:16     | -             | _             | _            |          | OC6IP<2:0>              |                         | OC6IS                 | <1:0>                 | _                           | -                      | _          |                        | IC6IP<2:0> | •                       | IC6IS                   | <1:0>                  | 0000       |

| 01B0                        | IPC7                            | 15:0      | -             | _             | _            |          | IC6EIP<2:0>             |                         | IC6EIS                | S<1:0>                | _                           | -                      | _          |                        | T6IP<2:0>  |                         | T6IS<                   | <1:0>                  | 0000       |

| 04.00                       |                                 | 31:16     | _             | _             | _            |          | OC7IP<2:0>              |                         | OC7IS                 | 5<1:0>                | _                           | _                      | _          |                        | IC7IP<2:0> | •                       | IC7IS                   | <1:0>                  | 0000       |

| 0100                        | IPC8                            | 15:0      | _             | _             | _            |          | IC7EIP<2:0>             |                         | IC7EIS                | S<1:0>                | _                           | _                      | _          |                        | T7IP<2:0>  |                         | T7IS∢                   | <1:0>                  | 0000       |

| 04 D 0                      |                                 | 31:16     | _             | _             | _            |          | OC8IP<2:0>              |                         | OC8IS                 | i<1:0>                |                             | —                      | —          |                        | IC8IP<2:0> | •                       | IC8IS                   | <1:0>                  | 0000       |

| 01D0                        | IPC9                            | 15:0      | _             | _             | —            |          | IC8EIP<2:0>             |                         | IC8EIS<1:0>           |                       | IC8EIS<1:0> — — — T8IP<2:0> |                        | T8IP<2:0>  |                        | T8IS<      | <1:0>                   | 0000                    |                        |            |

| 0450                        | 10040                           | 31:16     | _             | _             | _            |          | OC9IP<2:0>              |                         | OC9IS                 | i<1:0>                | _                           | _                      | —          |                        | IC9IP<2:0> | •                       | IC9IS                   | <1:0>                  | 0000       |

| 01E0                        | IPC10                           | 15:0      | _             | _             | _            |          | IC9EIP<2:0>             |                         | IC9EIS                | S<1:0>                | _                           | _                      | —          |                        | T9IP<2:0>  |                         | T9IS<                   | <1:0>                  | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

#### REGISTER 11-5: USBIE0CSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 0) (CONTINUED)

#### bit 21 SENDSTALL: Send Stall Control bit (Device mode)

- 1 = Terminate the current transaction and transmit a STALL handshake. This bit is automatically cleared.

- 0 = Do not send STALL handshake.

**REQPKT:** IN transaction Request Control bit (Host mode)

- 1 = Request an IN transaction. This bit is cleared when the RXPKTRDY bit is set.

- 0 = Do not request an IN transaction

- bit 20 SETUPEND: Early Control Transaction End Status bit (Device mode)

- 1 = A control transaction ended before the DATAEND bit has been set. An interrupt will be generated and the FIFO flushed at this time.

- 0 = Normal operation

This bit is cleared by writing a '1' to the SVCSETEND bit in this register.

#### ERROR: No Response Error Status bit (Host mode)

- 1 = Three attempts have been made to perform a transaction with no response from the peripheral. An interrupt is generated.

- 0 = Clear this flag. Software must write a '0' to this bit to clear it.

#### DATAEND: End of Data Control bit (Device mode)

The software sets this bit when:

bit 19

- Setting TXPKTRDY for the last data packet

- Clearing RXPKTRDY after unloading the last data packet

- Setting TXPKTRDY for a zero length data packet

Hardware clears this bit.

**SETUPPKT:** Send a SETUP token Control bit (*Host mode*)

- 1 = When set at the same time as the TXPKTRDY bit is set, the module sends a SETUP token instead of an OUT token for the transaction

- 0 = Normal OUT token operation

Setting this bit also clears the Data Toggle.

- bit 18 SENTSTALL: STALL sent status bit (Device mode)

- 1 = STALL handshake has been transmitted

- 0 = Software clear of bit

RXSTALL: STALL handshake received Status bit (Host mode)

- 1 = STALL handshake was received

- 0 = Software clear of bit

- bit 17 **TXPKTRDY:** TX Packet Ready Control bit

- 1 = Data packet has been loaded into the FIFO. It is cleared automatically.

- 0 = No data packet is ready for transmit

- bit 16 **RXPKTRDY:** RX Packet Ready Status bit

- 1 = Data packet has been received. Interrupt is generated (when enabled) when this bit is set.

- 0 = No data packet has been received

This bit is cleared by setting the SVCRPR bit.

bit 15-0 Unimplemented: Read as '0'

## 12.1 Parallel I/O (PIO) Ports

All port pins have up to 14 registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

#### 12.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to the pin name tables (Table 2 through Table 5) for the available pins and their functionality.

# 12.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 12.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP.

#### 12.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MZ EF devices to generate interrupt requests to the processor in response to a change-ofstate on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Seven control registers are associated with the CN functionality of each I/O port. The CNENx/CNNEx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins. CNENx enables a mismatch CN interrupt condition when the EDGEDETECT bit (CNCONx<11>) is not set. When the EDGEDETECT bit is set, CNNEx controls the negative edge while CNENx controls the positive.

The CNSTATx/CNFx registers indicate the status of change notice based on the setting of the EDGEDETECT bit. If the EDGEDETECT bit is set to '0', the CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. If the EDGEDETECT bit is set to '1', the CNFx register indicates whether a change has occurred and through the CNNEx/CNENx registers the edge type of the change that occurred is also indicated.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

An additional control register (CNCONx) is shown in Register 12-3.

| TABLE 12-3: | <b>OUTPUT PIN SELECTION</b> |

|-------------|-----------------------------|

|-------------|-----------------------------|

| RPn Port Pin         | RPnR SFR              | RPnR bits                  | RPnR Value to Peripheral<br>Selection         |

|----------------------|-----------------------|----------------------------|-----------------------------------------------|

| RPD2                 | RPD2R                 | RPD2R<3:0>                 | 0000 = No Connect                             |

| RPG8                 | RPG8R                 | RPG8R<3:0>                 | 0001 = <u>U3TX</u>                            |

| RPF4                 | RPF4R                 | RPF4R<3:0>                 | 0010 = U4RTS                                  |

| RPD10                | RPD10R                | RPD10R<3:0>                | 0011 = Reserved<br>0100 = Reserved            |

| RPF1                 | RPF1R                 | RPF1R<3:0>                 | 0100 = Reserved<br>0101 = SDO1                |

| RPB9                 | RPB9R                 | RPB9R<3:0>                 | 0110 = SD02                                   |

| RPB10                | RPB10R                | RPB10R<3:0>                | 0111 = SDO3                                   |

| RPC14                | RPC14R                | RPC14R<3:0>                | 1000 = Reserved                               |

| RPB5                 | RPB5R                 | RPB5R<3:0>                 | $1001 = SDO5^{(1)}$                           |

| RPC1 <sup>(1)</sup>  | RPC1R <sup>(1)</sup>  | RPC1R<3:0> <sup>(1)</sup>  | $1010 = \overline{SS6}^{(1)}$                 |

| RPD14 <sup>(1)</sup> | RPD14R <sup>(1)</sup> | RPD14R<3:0> <sup>(1)</sup> | 1011 = OC3<br>1100 = OC6                      |

| RPG1 <sup>(1)</sup>  | RPG1R <sup>(1)</sup>  | RPG1R<3:0> <sup>(1)</sup>  | 1100 = 000<br>1101 = REFCLKO4                 |

| RPA14 <sup>(1)</sup> | RPA14R <sup>(1)</sup> | RPA14R<3:0> <sup>(1)</sup> | 1110 = C2OUT                                  |

| RPD6 <sup>(2)</sup>  | RPD6R <sup>(2)</sup>  | RPD6R<3:0> <sup>(2)</sup>  | 1111 = C1TX <sup>(3)</sup>                    |

| RPD3                 | RPD3R                 | RPD3R<3:0>                 | 0000 = No Connect                             |

| RPG7                 | RPG7R                 | RPG7R<3:0>                 | 0001 = <u>U1TX</u>                            |

| RPF5                 | RPF5R                 | RPF5R<3:0>                 | 0010 = U2RTS                                  |

| RPD11                | RPD11R                | RPD11R<3:0>                | - 0011 = U5TX                                 |

| RPF0                 | RPF0R                 | RPF0R<3:0>                 |                                               |

| RPB1                 | RPB1R                 | RPB1R<3:0>                 | 0110 = SD02                                   |

| RPE5                 | RPE5R                 | RPE5R<3:0>                 | 0111 = SDO3                                   |

| RPC13                | RPC13R                | RPC13R<3:0>                | 1000 = SDO4                                   |

| RPB3                 | RPB3R                 | RPB3R<3:0>                 | 1001 = SDO5 <sup>(1)</sup>                    |

| RPC4 <sup>(1)</sup>  | RPC4R <sup>(1)</sup>  | RPC4R<3:0> <sup>(1)</sup>  | 1010 = Reserved                               |

| RPD15 <sup>(1)</sup> | RPD15R <sup>(1)</sup> | RPD15R<3:0> <sup>(1)</sup> | 1011 = OC4<br>1100 = OC7                      |

| RPG0 <sup>(1)</sup>  | RPG0R <sup>(1)</sup>  | RPG0R<3:0> <sup>(1)</sup>  | 1100 = CC7                                    |

| RPA15 <sup>(1)</sup> | RPA15R <sup>(1)</sup> | RPA15R<3:0> <sup>(1)</sup> | 1110 = Reserved                               |

| RPD7 <sup>(2)</sup>  | RPD7R <sup>(2)</sup>  | RPD7R<3:0> <sup>(2)</sup>  | 1111 = REFCLKO1                               |

| RPD9                 | RPD9R                 | RPD9R<3:0>                 | 0000 = <u>No Connect</u>                      |

| RPG6                 | RPG6R                 | RPG6R<3:0>                 | 0001 = U3RTS                                  |

| RPB8                 | RPB8R                 | RPB8R<3:0>                 | 0010 = U4TX<br>0011 = Reserved                |

| RPB15                | RPB15R                | RPB15R<3:0>                | 0011 = Reserved<br>0100 = U6TX                |

| RPD4                 | RPD4R                 | RPD4R<3:0>                 | 0101 = SS1                                    |

| RPB0                 | RPB0R                 | RPB0R<3:0>                 | 0110 = Reserved                               |

| RPE3                 | RPE3R                 | RPE3R<3:0>                 | $ 0111 = \frac{SS3}{1000} = \frac{SS3}{SS4} $ |

| RPB7                 | RPB7R                 | RPB7R<3:0>                 | $1000 = \frac{334}{\text{SS5}^{(1)}}$         |

| RPF12 <sup>(1)</sup> | RPF12R <sup>(1)</sup> | RPF12R<3:0> <sup>(1)</sup> | 1010 = SDO6 <sup>(1)</sup>                    |

| RPD12 <sup>(1)</sup> | RPD12R <sup>(1)</sup> | RPD12R<3:0> <sup>(1)</sup> | 1011 = OC5                                    |

| RPF8 <sup>(1)</sup>  | RPF8R <sup>(1)</sup>  | RPF8R<3:0> <sup>(1)</sup>  |                                               |

| RPC3 <sup>(1)</sup>  | RPC3R <sup>(1)</sup>  | RPC3R<3:0> <sup>(1)</sup>  | 1110 = C1OUT                                  |

| RPE9 <sup>(1)</sup>  | RPE9R <sup>(1)</sup>  | RPE9R<3:0> <sup>(1)</sup>  | 1111 = REFCLKO3                               |

Note 1: This selection is not available on 64-pin devices.

2: This selection is not available on 64-pin or 100-pin devices.

3: This selection is not available on devices without a CAN module.

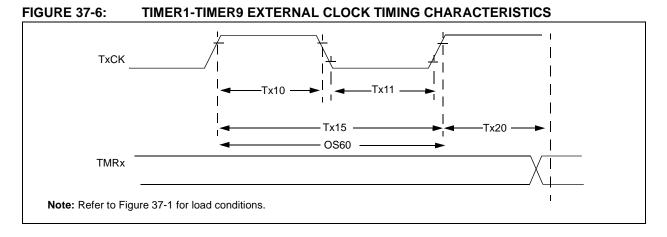

#### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 2

TSYNC: Timer External Clock Input Synchronization Selection bit

When TCS = 1:

1 = External clock input is synchronized

0 = External clock input is not synchronized

When TCS = 0:

When TCS = 0:

This bit is ignored.

bit 1

TCS: Timer Clock Source Select bit

- 1 = External clock from T1CKI pin 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

#### REGISTER 20-9: SQI1INTSTAT: SQI INTERRUPT STATUS REGISTER (CONTINUED)

- bit 2 TXTHRIF: Transmit Buffer Threshold Interrupt Flag bit

Transmit buffer has more than TXINTTHR words of space available

Transmit buffer has less than TXINTTHR words of space available

bit 1 TXFULLIF: Transmit Buffer Full Interrupt Flag bit

The transmit buffer is full

The transmit buffer is not full

bit 0 TXEMPTYIF: Transmit Buffer Empty Interrupt Flag bit

The transmit buffer is empty

- 0 = The transmit buffer has content

- **Note 1:** In Boot/XIP mode, the POR value of the receive buffer threshold is zero. Therefore, this bit will be set to a '1', immediately after a POR until a read request on the System Bus is received.

Note: The bits in the register are cleared by writing a '1' to the corresponding bit position.

| bit 15 FLTEN29: Filter 29 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled<br>bit 14-13 MSEL29<1:0>: Filter 29 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 0 selected<br>00 = Acceptance Mask 0 selected<br>bit 12-8 FSEL29<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0<br>bit 7 FLTEN28: Filter 28 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled<br>bit 6-5 MSEL28<1:0>: Filter 28 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 3 selected<br>11 = Acceptance Mask 3 selected<br>12 = Acceptance Mask 3 selected<br>13 = Acceptance Mask 3 selected<br>14-0 FSEL28<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 0<br>Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                                                                                                                                                                                                                                                                         | REGISTE   | ER 29-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7 (CONTINUED)                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------|

| 0 = Filter is disabled bit 14-13 MSEL29<1:D>: Filter 29 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 1 selected 00 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL29<4:D>: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 1 00001 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN28: Filter 28 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL28<1:D>: FIFC Selection bits 11 = Acceptance Mask 3 selected bit 4-0 FSEL28<1:D>: Filter 28 Mask Select bits 11 = Acceptance Mask 1 selected 00 = Acceptance Mask 3 selected 10 = Acceptance Mask 4 selected 10 = Acceptance Mask 2 selected 10 = Acceptance Mask 3 selected 10 = Acceptance Mask 1 selected 11 = Acceptance Mask 0 selected 11 = Acceptance Mask 1 selected 00 = Acceptance Mask 1 selected 11 = Acceptance Mask 1 selected 11 = Acceptance Mask 1 selected 10 = Acceptance Mask 1 selected 11 = Acceptance Mask 1 selected 12 = Acceptance Mask 1 selected 13 = Acceptance Mask                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15    | FLTEN29: Filter 29 Enable bit                                                                          |

| <pre>bit 14-13 MSEL29-1:0-: Filter 29 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 0 selected bit 12-3 FSEL29-4:0-: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | 1 = Filter is enabled                                                                                  |

| <pre>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 0 selected<br/>bit 12-8 FSEL29-4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31<br/>11110 = Message matching filter is stored in FIFO buffer 30<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | 0 = Filter is disabled                                                                                 |

| <pre>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 0 selected<br/>00 = Acceptance Mask 0 selected<br/>bit 12-8 FSEL29&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31<br/>11110 = Message matching filter is stored in FIFO buffer 30<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 14-13 | MSEL29<1:0>: Filter 29 Mask Select bits                                                                |

| <pre>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>bit 12-8 FSEL29&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31<br/>11110 = Message matching filter is stored in FIFO buffer 30<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                                                                                        |

| 00 = Acceptance Mask 0 selected<br>bit 12-8 FSEL29<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                                                                                        |

| <pre>bit 12-8 FSEL29&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                                                                                        |

| <pre>11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | hit 12 8  |                                                                                                        |

| <pre>11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DIL 12-0  |                                                                                                        |

| <ul> <li>00001 = Message matching filter is stored in FIFO buffer 1</li> <li>00000 = Message matching filter is stored in FIFO buffer 0</li> <li>bit 7 FLTEN28: Filter 28 Enable bit</li> <li>1 = Filter is enabled</li> <li>0 = Filter is disabled</li> <li>bit 6-5 MSEL28</li> <li>bit 6-5 MSEL28</li> <li>10 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>00 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> <li>bit 4-0 FSEL28</li> <li>4-0 FSEL28</li> &lt;</ul>                              |           |                                                                                                        |

| <pre>00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN28: Filter 28 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL28&lt;1:0&gt;: Filter 28 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 1 selected 00 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL28&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 • • • • • • • • • • • • • • • • • • •</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                                                                                        |