Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 46                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efh064t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The MIPS architecture defines that the result of a multiply or divide operation be placed in one of four pairs of HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

The MDU also implements various shift instructions operating on the HI/LO register and multiply instructions as defined in the DSP ASE. The MDU supports all of the data types required for this purpose and includes three extra HI/LO registers as defined by the ASE.

Table 3-2 lists the latencies and repeat rates for the DSP multiply and dot-product operations. The approximate latencies and repeat rates are listed in terms of pipeline clocks.

| TABLE 3-2: | DSP-RELATED LATENCIES |

|------------|-----------------------|

|            | AND REPEAT RATES      |

| Op code                                                        | Latency | Repeat<br>Rate |

|----------------------------------------------------------------|---------|----------------|

| Multiply and dot-product without saturation after accumulation | 5       | 1              |

| Multiply and dot-product with saturation after accumulation    | 5       | 1              |

| Multiply without accumulation                                  | 5       | 1              |

#### 3.1.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation and cache protocols, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as cache size and set associativity, and the presence of options like microMIPS is also available by accessing the CP0 registers, listed in Table 3-3.

| Register<br>Number | Register<br>Name       | Function                                                                                                                                                    |

|--------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | Index                  | Index into the TLB array (MPU only).                                                                                                                        |

| 1                  | Random                 | Randomly generated index into the TLB array (MPU only).                                                                                                     |

| 2                  | EntryLo0               | Low-order portion of the TLB entry for even-numbered virtual pages (MPU only).                                                                              |

| 3                  | EntryLo1               | Low-order portion of the TLB entry for odd-numbered virtual pages (MPU only).                                                                               |

| 4                  | Context/<br>UserLocal  | Pointer to the page table entry in memory (MPU only).<br>User information that can be written by privileged software and read via the RDHWR<br>instruction. |

| 5                  | PageMask/<br>PageGrain | PageMask controls the variable page sizes in TLB entries. PageGrain enables support<br>of 1 KB pages in the TLB (MPU only).                                 |

| 6                  | Wired                  | Controls the number of fixed (i.e., wired) TLB entries (MPU only).                                                                                          |

| 7                  | HWREna                 | Enables access via the RDHWR instruction to selected hardware registers in Non-privileged mode.                                                             |

| 8                  | BadVAddr               | Reports the address for the most recent address-related exception.                                                                                          |

|                    | BadInstr               | Reports the instruction that caused the most recent exception.                                                                                              |

|                    | BadInstrP              | Reports the branch instruction if a delay slot caused the most recent exception.                                                                            |

| 9                  | Count                  | Processor cycle count.                                                                                                                                      |

| 10                 | EntryHi                | High-order portion of the TLB entry (MPU only).                                                                                                             |

| 11                 | Compare                | Core timer interrupt control.                                                                                                                               |

#### TABLE 3-3: COPROCESSOR 0 REGISTERS

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1        | Bit<br>24/16/8/0 |  |

|--------------|-------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|------------------|--|

| 24.24        | r-1               | U-0                | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0              |  |

| 31:24        | —                 | —                  | —                 | —                 | —                 | —                 | _                       | —                |  |

| 22.46        | U-0               | R-0                | R-1               | R-0               | R-0               | R-0               | R-1                     | R/W-y            |  |

| 23:16        | —                 | IPLW               | <1:0>             |                   | MMAR<2:0>         | MCU               | ISAONEXC <sup>(1)</sup> |                  |  |

| 15.0         | R-y               | R-y                | R-1               | R-1               | R-1               | R-1               | U-0                     | R-1              |  |

| 15:8         | ISA<1             | :0> <sup>(1)</sup> | ULRI              | RXI               | DSP2P             | DSPP              | _                       | ITL              |  |

| 7.0          | U-0               | R-1                | R-1               | R-0               | R-1               | U-0               | U-0                     | R-0              |  |

| 7:0          | _                 | VEIC               | VINT              | SP                | CDMM              | _                 | —                       | TL               |  |

|              | •                 | •                  |                   | •                 | -                 |                   |                         |                  |  |

#### REGISTER 3-3: CONFIG3: CONFIGURATION REGISTER 3; CP0 REGISTER 16, SELECT 3

| Legend:           | r = Reserved bit | y = Value set from Co | nfiguration bits on POR |

|-------------------|------------------|-----------------------|-------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b   | it, read as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown      |

bit 31 **Reserved:** This bit is hardwired as '1' to indicate the presence of the Config4 register

- bit 30-23 Unimplemented: Read as '0'

- bit 22-21 **IPLW<1:0>:** Width of the Status IPL and Cause RIPL bits 01 = IPL and RIPL bits are 8-bits in width

- bit 20-18 **MMAR<2:0>:** microMIPS Architecture Revision Level bits 000 = Release 1

- bit 17 MCU: MIPS<sup>®</sup> MCU<sup>™</sup> ASE Implemented bit

- 1 = MCU ASE is implemented

- bit 16 **ISAONEXC:** ISA on Exception bit<sup>(1)</sup> 1 = microMIPS is used on entrance to an exception vector 0 = MIPS32 ISA is used on entrance to an exception vector

- bit 15-14 **ISA<1:0>:** Instruction Set Availability bits<sup>(1)</sup> 11 = Both MIPS32 and microMIPS are implemented; microMIPS is used when coming out of reset

- 10 = Both MIPS32 and microMIPS are implemented; MIPS32 ISA used when coming out of reset

- bit 13 ULRI: UserLocal Register Implemented bit

- 1 = UserLocal Coprocessor 0 register is implemented

- bit 12 RXI: RIE and XIE Implemented in PageGrain bit

- 1 = RIE and XIE bits are implemented

- bit 11 **DSP2P:** MIPS DSP ASE Revision 2 Presence bit 1 = DSP Revision 2 is present

- bit 10 **DSPP:** MIPS DSP ASE Presence bit

- 1 = DSP is present

- bit 9 Unimplemented: Read as '0'

- bit 8 ITL: Indicates that iFlowtrace<sup>®</sup> hardware is present

- $1 = \text{The iFlowtrace}^{\mathbb{R}}$  is implemented in the core

- bit 7 Unimplemented: Read as '0'

- bit 6 **VEIC:** External Vector Interrupt Controller bit

- 1 = Support for an external interrupt controller is implemented

- bit 5 **VINT:** Vector Interrupt bit

- 1 = Vector interrupts are implemented

- bit 4 SP: Small Page bit

- 0 = 4 KB page size

- bit 3 CDMM: Common Device Memory Map bit

- 1 = CDMM is implemented

- bit 2-1 Unimplemented: Read as '0'

- bit 0 **TL:** Trace Logic bit

- 0 = Trace logic is not implemented

Note 1: These bits are set based on the value of the BOOTISA Configuration bit (DEVCFG0<6>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 |                   |                   | —                 |                   | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | —                 |                   |                   | —                 |                   | —                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 10.0         | —                 | —                 | _                 | —                 | —                 | -                 | —                | —                |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          | FCC<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |

### REGISTER 3-7: FCCR: FLOATING POINT CONDITION CODES REGISTER; CP1 REGISTER 25

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FCC<7:0>:** Floating Point Condition Code bits These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

## TABLE 4-4: INITIATORS TO TARGETS ACCESS ASSOCIATION

| Torgot      | Initiator ID                                                                                                          | 1 | 2   | 3   | 4      | 5   | 6         | 7 | 8                | 9                 | 10   | 11   | 12   | 13                  | 14     |

|-------------|-----------------------------------------------------------------------------------------------------------------------|---|-----|-----|--------|-----|-----------|---|------------------|-------------------|------|------|------|---------------------|--------|

| Target<br># | Name                                                                                                                  | C | CPU | DMA | A Read | DMA | DMA Write |   | Ethernet<br>Read | Ethernet<br>Write | CAN1 | CAN2 | SQI1 | Flash<br>Controller | Crypto |

| 1           | Flash Memory:<br>Program Flash<br>Boot Flash<br>Prefetch Module                                                       |   | x   |     | x      |     |           |   | x                |                   | х    | х    |      |                     | х      |

| 2           | RAM Bank 1 Memory                                                                                                     |   | Х   |     | Х      |     | Х         | Х | Х                | Х                 | Х    | Х    | Х    | Х                   | Х      |

| 3           | RAM Bank 2 Memory                                                                                                     |   | Х   |     | Х      | 2   | Х         | Х | Х                | Х                 | Х    | Х    | Х    | Х                   | Х      |

| 4           | External Memory via EBI and EBI Module                                                                                |   | Х   |     | Х      | 2   | Х         | Х | Х                | Х                 | Х    | Х    | Х    |                     | Х      |

| 5           | Peripheral Set 1:<br>System Control, Flash Control, DMT,<br>RTCC, CVR, PPS Input, PPS Output,<br>Interrupts, DMA, WDT |   | x   |     |        |     |           |   |                  |                   |      |      |      |                     |        |

| 6           | Peripheral Set 2:<br>SPI1-SPI6<br>I2C1-I2C5<br>UART1-UART6<br>PMP                                                     |   | х   |     | x      | :   | x         |   |                  |                   |      |      |      |                     |        |

| 7           | Peripheral Set 3:<br>Timer1-Timer9<br>IC1-IC9<br>OC1-OC9<br>ADC<br>Comparator 1<br>Comparator 2                       |   | x   |     | x      | :   | x         |   |                  |                   |      |      |      |                     |        |

| 8           | Peripheral Set 4:<br>PORTA-PORTK                                                                                      |   | Х   |     | Х      | 2   | х         |   |                  |                   |      |      |      |                     |        |

| 9           | Peripheral Set 5:<br>CAN1<br>CAN2<br>Ethernet Controller                                                              |   | x   |     |        |     |           |   |                  |                   |      |      |      |                     |        |

| 10          | Peripheral Set 6:<br>USB                                                                                              |   | Х   |     |        |     |           |   |                  |                   |      |      |      |                     |        |

| 11          | External Memory via SQI1 and SQI1 Module                                                                              |   | Х   |     |        |     |           |   |                  |                   |      |      |      |                     |        |

| 12          | Peripheral Set 7:<br>Crypto Engine                                                                                    |   | х   |     |        |     |           |   |                  |                   |      |      |      |                     |        |

| 13          | Peripheral Set 8:<br>RNG Module                                                                                       |   | х   |     |        |     |           |   |                  |                   |      |      |      |                     |        |

# TABLE 4-10: SYSTEM BUS TARGET 2 REGISTER MAP

| ess                         |                  | 0         |       |           |       |          |          |       |       |           | Bits     |       |           |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-----------|-------|----------|----------|-------|-------|-----------|----------|-------|-----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14     | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8      | 23/7     | 22/6  | 21/5      | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             |                  | 31:16     | MULTI |           | —     | _        |          | CODE  | <3:0> |           | -        | _     | _         | —    | —      | _      | _       | —      | 0000          |

| 8820                        | SBT2ELOG1        | 15:0      |       |           |       | INI      | ΓID<7:0> |       |       |           |          | REGIO | N<3:0>    |      | —      | C      | MD<2:0> |        | 0000          |

| 0004                        | SBT2ELOG2        | 31:16     | _     | —         | _     | —        | _        | _     | _     | _         | _        | _     | —         | _    | _      | —      | _       | _      | 0000          |

| 8824                        | SBIZELUGZ        | 15:0      | _     | _         | _     | _        | _        | _     | _     | _         | -        | _     | _         | _    | _      | _      | GROU    | P<1:0> | 0000          |

| 8828                        | SBT2ECON         | 31:16     |       |           | —     | _        | —        |       | _     | ERRP      | _        | _     |           |      | —      |        | —       | —      | 0000          |

| 0020                        | 3BT2ECON         | 15:0      |       | -         | -     | _        | -        |       | _     | _         | _        | _     |           |      |        |        | _       | -      | 0000          |

| 8830                        | SBT2ECLRS        | 31:16     | _     | _         | —     | —        | —        | _     | —     | —         | _        | _     | —         | _    | —      | _      | —       |        | 0000          |

| 0030                        | SBIZLOLKS        | 15:0      | _     | _         | —     | —        | —        | _     | —     | —         | _        | _     | —         | _    | —      | _      | —       | CLEAR  | 0000          |

| 8838                        | SBT2ECLRM        | 31:16     | —     | —         | _     | _        | _        | _     | —     | _         | —        | _     | _         | _    | _      | _      | _       | _      | 0000          |

| 0000                        | OBTZEOER         | 15:0      | _     | —         | —     | —        | —        | —     | —     | —         | —        | —     | —         | —    | —      | —      | —       | CLEAR  | 0000          |

| 8840                        | SBT2REG0         | 31:16     |       |           |       |          |          |       |       |           |          |       | xxxx      |      |        |        |         |        |               |

| 0010                        | OBTEREOU         | 15:0      |       | BASE<5:0> |       |          |          | PRI   | —     | SIZE<4:0> |          |       |           |      | —      | —      | —       | xxxx   |               |

| 8850                        | SBT2RD0          | 31:16     | _     | _         | —     | —        | —        | _     | —     | —         | —        |       | _         | _    | —      | _      | —       | —      | xxxx          |

|                             | 0012:00          | 15:0      | _     | _         | —     | —        | —        | _     | _     | —         | —        | _     | —         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8858                        | SBT2WR0          | 31:16     | _     | —         | —     | —        | —        |       | —     | —         | —        | —     |           |      | —      | —      | —       | —      | xxxx          |

|                             |                  | 15:0      | —     |           | —     | —        | <u> </u> | —     | _     |           | —        | —     | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8860                        | SBT2REG1         | 31:16     |       |           |       |          |          |       | 1     | BAS       | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

|                             |                  | 15:0      |       |           | BA    | \SE<5:0> |          |       | PRI   | _         |          |       | SIZE<4:0: | >    |        | _      | _       |        | xxxx          |

| 8870                        | SBT2RD1          | 31:16     | —     | —         | _     | _        |          |       | _     | _         | _        | _     | _         | _    | —      | —      | —       |        | xxxx          |

|                             | -                | 15:0      | —     | _         | _     | _        |          | _     | _     | _         | _        | _     | _         |      | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8878                        | SBT2WR1          | 31:16     |       | _         | —     | —        | —        | —     | —     | —         | —        | —     | —         | _    | —      | —      | _       | —      | XXXX          |

|                             | -                | 15:0      |       | —         | —     | _        | —        | —     |       | —         |          | _     | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8880                        | SBT2REG2         | 31:16     |       |           |       |          |          |       | 1     | BAS       | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

|                             |                  | 15:0      |       |           | BA    | \SE<5:0> |          |       | PRI   | —         |          |       | SIZE<4:0: | >    |        | _      | —       | —      | XXXX          |

| 8890                        | SBT2RD2          | 31:16     | _     | _         | —     | —        | —        | —     | —     | —         | _        | _     | —         | —    | —      | —      | —       | —      | xxxx          |

|                             |                  | 15:0      | _     | _         | —     | —        | —        | —     | —     | —         | _        | _     | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8898                        | SBT2WR2          | 31:16     | _     | _         | —     | —        | —        | —     | —     | —         | _        | _     | —         | —    | —      | —      | —       | —      | xxxx          |

|                             |                  | 15:0      | —     | —         | —     | —        | —        | —     | —     | —         | —        | —     | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

# PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

# REGISTER 4-10: SBTxWRy: SYSTEM BUS TARGET 'x' REGION 'y' WRITE PERMISSIONS REGISTER ('x' = 0-13; 'y' = 0-8)

|              |                   | •                 | ,                 |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 |                   |                   | _                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 |                   |                   | _                 |                   | _                 |                  | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 |                  | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-1             | R/W-1            | R/W-1            |

| 7:0          |                   |                   | _                 | _                 | GROUP3            | GROUP2            | GROUP1           | GROUP0           |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

#### bit 31-4 Unimplemented: Read as '0'

more information.

|       |      | •·····•                                                                                                    |

|-------|------|------------------------------------------------------------------------------------------------------------|

| bit 3 |      | Group3: Group 3 Write Permissions bits                                                                     |

|       |      | 1 = Privilege Group 3 has write permission                                                                 |

|       |      | 0 = Privilege Group 3 does not have write permission                                                       |

| bit 2 |      | Group2: Group 2 Write Permissions bits                                                                     |

|       |      | 1 = Privilege Group 2 has write permission                                                                 |

|       |      | 0 = Privilege Group 2 does not have write permission                                                       |

| bit 1 |      | Group1: Group 1 Write Permissions bits                                                                     |

|       |      | 1 = Privilege Group 1 has write permission                                                                 |

|       |      | 0 = Privilege Group 1 does not have write permission                                                       |

| bit 0 |      | Group0: Group 0 Write Permissions bits                                                                     |

|       |      | 1 = Privilege Group 0 has write permission                                                                 |

|       |      | 0 = Privilege Group 0 does not have write permission                                                       |

|       |      |                                                                                                            |

| Note  | ə 1: | Refer to Table 4-6 for the list of available targets and their descriptions.                               |

|       | 2:   | For some target regions, certain bits in this register are read-only with preset values. See Table 4-6 for |

DS60001320D-page 98

NOTES:

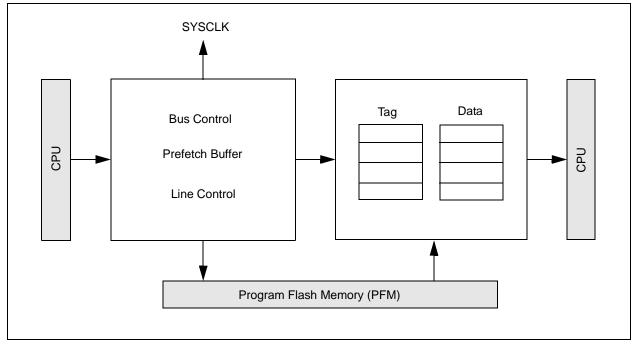

# 9.0 PREFETCH MODULE

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Prefetch module is a performance enhancing module that is included in the PIC32MZ EF family of devices. When running at high-clock rates, Wait states must be inserted into Program Flash Memory (PFM) read transactions to meet the access time of the PFM. Wait states can be hidden to the core by prefetching and storing instructions in a temporary holding area that the CPU can access quickly. Although the data path to the CPU is 32 bits wide, the data path to the PFM is 128 bits wide. This wide data path provides the same bandwidth to the CPU as a 32-bit path running at four times the frequency.

The Prefetch module holds a subset of PFM in temporary holding spaces known as lines. Each line contains a tag and data field. Normally, the lines hold a copy of what is currently in memory to make instructions or data available to the CPU without Flash Wait states.

The following are key features of the Prefetch module:

- 4x16 byte fully-associative lines

- One line for CPU instructions

- · One line for CPU data

- Two lines for peripheral data

- 16-byte parallel memory fetch

- Configurable predictive prefetch

- Error detection and correction

A simplified block diagram of the Prefetch module is shown in Figure 9-1.

#### FIGURE 9-1: PREFETCH MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 |                   |                   |                   | _                 |                   |                  | —                |  |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |

#### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL x SOURCE SIZE REGISTER

# Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

#### **REGISTER 10-13: DCHxDSIZ: DMA CHANNEL x DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 |                   | —                 | —                 | _                 | —                 |                  | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 15-0 **CHDSIZ<15:0>:** Channel Destination Size bits

111111111111111 = 65,535 byte destination size  $\ensuremath{\cdot}$

|              | 1)                |                   | 0)                |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|              | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0, HC         | R/W-0            | R/W-0, HC        |

| 31:24        |                   |                   |                   | _                 | -                 |                   | —                | FLSHFIFO         |

|              |                   | _                 |                   |                   | DISPING           | DTWREN            | DATATGGL         |                  |

|              | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/C-0, HS         | R/W-0, HS         | R-0, HS           | R-0              | R-0              |

| 23:16        | SVCSETEND         | SVCRPR            | SENDSTALL         | SETUPEND          | DATAEND           | SENTSTALL         | TXPKTRDY         | RXPKTRDY         |

|              | NAKTMOUT          | STATPKT           | REQPKT            | ERROR             | SETUPPKT          | RXSTALL           | IAPKIKUT         | KAFKIKUT         |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | —                 | —                 | —                 | _                 | -                 | —                 | _                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

# REGISTER 11-5: USBIE0CSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 0)

| Legend:           | HC = Hardware Cleared | HS = Hardware Set         |                    |

|-------------------|-----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-28 Unimplemented: Read as '0'

- bit 27 DISPING: Disable Ping tokens control bit (*Host mode*)

1 = USB Module will not issue PING tokens in data and status phases of a Hi-Speed Control transfer

0 = Ping tokens are issued

bit 26 DTWREN: Data Toggle Write Enable bit (*Host mode*)

1 = Enable the current state of the Endpoint 0 data toggle to be written. Automatically cleared.

0 = Disable data toggle write

- bit 25 **DATATGGL:** Data Toggle bit (*Host mode*)

When read, this bit indicates the current state of the Endpoint 0 data toggle.

If DTWREN = 1, this bit is writable with the desired setting.

If DTWREN = 0, this bit is read-only.

- bit 24 FLSHFIFO: Flush FIFO Control bit

- 1 = Flush the next packet to be transmitted/read from the Endpoint 0 FIFO. The FIFO pointer is reset and the TXPKTRDY/RXPKTRDY bit is cleared. Automatically cleared when the operation completes. Should only be used when TXPKTRDY/RXPKTRDY = 1.

- 0 = No Flush operation

- bit 23 SVCSETEND: Clear SETUPEND Control bit (Device mode)

- 1 = Clear the SETUPEND bit in this register. This bit is automatically cleared.

- 0 = Do not clear

NAKTMOUT: NAK Time-out Control bit (Host mode)

- 1 = Endpoint 0 is halted following the receipt of NAK responses for longer than the time set by the NAKLIM<4:0> bits (USBICSR<28:24>)

- 0 = Allow the endpoint to continue

- bit 22 SVCRPR: Serviced RXPKTRDY Clear Control bit (Device mode)

- 1 = Clear the RXPKTRDY bit in this register. This bit is automatically cleared.

- 0 = Do not clear

**STATPKT:** Status Stage Transaction Control bit (*Host mode*)

- 1 = When set at the same time as the TXPKTRDY or REQPKT bit is set, performs a status stage transaction

- 0 = Do not perform a status stage transaction

| REGISTE | R 21-2: I2CxSTAT: I <sup>2</sup> C STATUS REGISTER (CONTINUED)                                                                                                                                                                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <ul> <li>D_A: Data/Address bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Indicates that the last byte received was data</li> <li>0 = Indicates that the last byte received was device address</li> <li>Hardware clear at device address match. Hardware set by reception of slave byte.</li> </ul> |

| bit 4   | P: Stop bit                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                                                                                                               |

| bit 3   | S: Start bit                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                                                                                         |

| bit 2   | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                              |

|         | 1 = Read – indicates data transfer is output from slave<br>0 = Write – indicates data transfer is input to slave<br>Hardware set or clear after reception of $I^2C$ device address byte.                                                                                                                       |

| bit 1   | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul>                                                                                    |

| bit 0   | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                           |

|         | 1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty                                                                                                                                                                                                                           |

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04:04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | _                 | —                 | —                 | _                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | BDPPLCON<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | BDPPLCON<7:0>     |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 26-8: CEPOLLCON: CRYPTO ENGINE POLL CONTROL REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15 **BDPPLCON<15:0>:** Buffer Descriptor Processor Poll Control bits

These bits determine the number of SYSCLK cycles that the Crypto DMA would wait before refetching the descriptor control word if the Buffer Descriptor fetched was disabled.

| REGIST    | ER 28-1: ADCCON1: ADC CONTROL REGISTER 1 (CONTINUED)                                                                                                                      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 20-16 | S STRGSRC<4:0>: Scan Trigger Source Select bits                                                                                                                           |

|           | 11111 = Reserved                                                                                                                                                          |

|           | •                                                                                                                                                                         |

|           | •                                                                                                                                                                         |

|           | 01101 = Reserved                                                                                                                                                          |

|           | 01100 = Comparator 2 (COUT)                                                                                                                                               |

|           | 01011 = Comparator 1 (COUT)<br>01010 = OCMP5                                                                                                                              |

|           | 01001 = OCMP3                                                                                                                                                             |

|           | 01000 = OCMP1                                                                                                                                                             |

|           | 00111 = TMR5 match                                                                                                                                                        |

|           | 00110 = TMR3 match<br>00101 = TMR1 match                                                                                                                                  |

|           | 00100 = INTO External interrupt                                                                                                                                           |

|           | 00011 = Reserved                                                                                                                                                          |

|           | 00010 = Global level software trigger (GLSWTRG)                                                                                                                           |

|           | 00001 = Global software edge trigger (GSWTRG)<br>00000 = No Trigger                                                                                                       |

| bit 15    | ON: ADC Module Enable bit                                                                                                                                                 |

| bit 10    | 1 = ADC module is enabled                                                                                                                                                 |

|           | 0 = ADC module is disabled                                                                                                                                                |

|           | <b>Note:</b> The ON bit should be set only after the ADC module has been configured.                                                                                      |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                               |

|           | <ol> <li>Discontinue module operation when device enters Idle mode</li> <li>Continue module operation in Idle mode</li> </ol>                                             |

| bit 12    | AICPMPEN: Analog Input Charge Pump Enable bit                                                                                                                             |

|           | 1 = Analog input charge pump is enabled (default)                                                                                                                         |

|           | 0 = Analog input charge pump is disabled                                                                                                                                  |

| bit 11    | CVDEN: Capacitive Voltage Division Enable bit                                                                                                                             |

|           | <ul> <li>1 = CVD operation is enabled</li> <li>0 = CVD operation is disabled</li> </ul>                                                                                   |

| bit 10    | <b>FSSCLKEN:</b> Fast Synchronous System Clock to ADC Control Clock bit                                                                                                   |

|           | 1 = Fast synchronous system clock to ADC control clock is enabled                                                                                                         |

|           | 0 = Fast synchronous system clock to ADC control clock is disabled                                                                                                        |

| bit 9     | FSPBCLKEN: Fast Synchronous Peripheral Clock to ADC Control Clock bit                                                                                                     |

|           | <ul> <li>1 = Fast synchronous peripheral clock to ADC control clock is enabled</li> <li>0 = Fast synchronous peripheral clock to ADC control clock is disabled</li> </ul> |

| bit 8-7   | Unimplemented: Read as '0'                                                                                                                                                |

| bit 6-4   | IRQVS<2:0>: Interrupt Vector Shift bits                                                                                                                                   |

|           | To determine interrupt vector address, this bit specifies the amount of left shift done to the ARDYx status                                                               |

|           | bits in the ADCDSTAT1 and ADCDSTAT2 registers, prior to adding with the ADCBASE register.                                                                                 |

|           | Interrupt Vector Address = Read Value of ADCBASE and Read Value of ADCBASE = Value written to                                                                             |

|           | ADCBASE + $x \ll IRQVS < 2:0$ , where 'x' is the smallest active input ID from the ADCDSTAT1 or ADCDSTAT2 registers (which has highest priority).                         |

|           | 111 = Shift x left 7 bit position                                                                                                                                         |

|           | 110 = Shift x left 6 bit position                                                                                                                                         |

|           | 101 = Shift x left 5 bit position                                                                                                                                         |

|           | 100 = Shift x left 4 bit position<br>011 = Shift x left 3 bit position                                                                                                    |

|           | 010 = Shift x left 2 bit position                                                                                                                                         |

|           | 001 = Shift x left 1 bit position                                                                                                                                         |

|           | 000 = Shift x left 0 bit position                                                                                                                                         |

|           |                                                                                                                                                                           |

| REGIST   | R 29-3: CIINT: CAN INTERRUPT REGISTER (CONTINUED)                                                                                                        |       |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| bit 14   | <b>NAKIF:</b> CAN Bus Activity Wake-up Interrupt Flag bit<br>L = A bus wake-up activity interrupt has occurred                                           |       |

|          | ) = A bus wake-up activity interrupt has not occurred                                                                                                    |       |

| bit 13   | CERRIF: CAN Bus Error Interrupt Flag bit                                                                                                                 |       |

|          | L = A CAN bus error has occurred                                                                                                                         |       |

|          | ) = A CAN bus error has not occurred                                                                                                                     |       |

| bit 12   | SERRIF: System Error Interrupt Flag bit                                                                                                                  |       |

|          | <ul> <li>A system error occurred (typically an illegal address was presented to the System Bu</li> <li>A system error has not occurred</li> </ul>        | ls)   |

| bit 11   | RBOVIF: Receive Buffer Overflow Interrupt Flag bit                                                                                                       |       |

|          | L = A receive buffer overflow has occurred                                                                                                               |       |

|          | D = A receive buffer overflow has not occurred                                                                                                           |       |

| bit 10-4 | Jnimplemented: Read as '0'                                                                                                                               |       |

| bit 3    | MODIF: CAN Mode Change Interrupt Flag bit                                                                                                                |       |

|          | <ul> <li>A CAN module mode change has occurred (OPMOD&lt;2:0&gt; has changed to reflect RI</li> <li>A CAN module mode change has not occurred</li> </ul> | EQOP) |

| bit 2    | CTMRIF: CAN Timer Overflow Interrupt Flag bit                                                                                                            |       |

|          | L = A CAN timer (CANTMR) overflow has occurred                                                                                                           |       |

|          | ) = A CAN timer (CANTMR) overflow has not occurred                                                                                                       |       |

| bit 1    | RBIF: Receive Buffer Interrupt Flag bit                                                                                                                  |       |

|          | L = A receive buffer interrupt is pending                                                                                                                |       |

|          | ) = A receive buffer interrupt is not pending                                                                                                            |       |

| bit 0    | <b>TBIF:</b> Transmit Buffer Interrupt Flag bit                                                                                                          |       |

|          | L = A transmit buffer interrupt is pending                                                                                                               |       |

|          | ) = A transmit buffer interrupt is not pending                                                                                                           |       |

**Note 1:** This bit can only be cleared by turning the CAN module off and on by clearing or setting the ON bit (CiCON<15>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN23           | MSEL23<1:0>       |                   | FSEL23<4:0>       |                   |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN22           | MSEL22<1:0>       |                   | FSEL22<4:0>       |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         | FLTEN21           | MSEL2             | :1<1:0>           |                   | F                 | SEL21<4:0>        |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FLTEN20           | MSEL2             | MSEL20<1:0>       |                   | F                 | SEL20<4:0>        | •                |                  |

#### REGISTER 29-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN23: Filter 23 Enable bit<br>1 = Filter is enabled                                                                                                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | <ul> <li>0 = Filter is disabled</li> <li>MSEL23&lt;1:0&gt;: Filter 23 Mask Select bits</li> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 28-24 | FSEL23<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>•                                                                                                   |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                                              |

| bit 23    | FLTEN22: Filter 22 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                      |

| bit 22-21 | MSEL22<1:0>: Filter 22 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                   |

| bit 20-16 | <pre>FSEL22&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                                                             |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                                                                                                                |

DS60001320D-page 510

| Bit<br>Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6            | Bit<br>29/21/13/5              | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>25/16/8/0 |

|--------------|------------------------------|------------------------------|--------------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                          | U-0                          | U-0                            | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                              |                              | —                              | —                 | —                 |                   |                  | —                |

| 23:16        | U-0                          | U-0                          | U-0                            | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                              |                              | —                              | —                 | —                 |                   |                  | —                |

|              | U-0                          | R/W-1                        | R/W-0                          | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         |                              | EXCESS<br>DFR                | BPNOBK<br>OFF                  | NOBK<br>OFF       | —                 |                   | LONGPRE          | PUREPRE          |

|              | R/W-1                        | R/W-0                        | R/W-1                          | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | AUTO<br>PAD <sup>(1,2)</sup> | VLAN<br>PAD <sup>(1,2)</sup> | PAD<br>ENABLE <sup>(1,3)</sup> | CRC<br>ENABLE     | DELAYCRC          | HUGEFRM           | LENGTHCK         | FULLDPLX         |

#### REGISTER 30-24: EMAC1CFG2: ETHERNET CONTROLLER MAC CONFIGURATION 2 REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-15 Unimplemented: Read as '0'

#### bit 14 **EXCESSDER:** Excess Defer bit

- 1 = The MAC will defer to carrier indefinitely as per the Standard

- 0 = The MAC will abort when the excessive deferral limit is reached

#### bit 13 BPNOBKOFF: Backpressure/No Backoff bit

- 1 = The MAC after incidentally causing a collision during backpressure will immediately retransmit without backoff reducing the chance of further collisions and ensuring transmit packets get sent

- 0 = The MAC will not remove the backoff

#### bit 12 NOBKOFF: No Backoff bit

- 1 = Following a collision, the MAC will immediately retransmit rather than using the Binary Exponential Backoff algorithm as specified in the Standard

- 0 = Following a collision, the MAC will use the Binary Exponential Backoff algorithm

- bit 11-10 Unimplemented: Read as '0'

- bit 9 LONGPRE: Long Preamble Enforcement bit

- 1 = The MAC only allows receive packets which contain preamble fields less than 12 bytes in length

- 0 = The MAC allows any length preamble as per the Standard

#### bit 8 **PUREPRE:** Pure Preamble Enforcement bit

- 1 = The MAC will verify the content of the preamble to ensure it contains 0x55 and is error-free. A packet with errors in its preamble is discarded

- 0 = The MAC does not perform any preamble checking

#### bit 7 AUTOPAD: Automatic Detect Pad Enable bit<sup>(1,2)</sup>

- 1 = The MAC will automatically detect the type of frame, either tagged or untagged, by comparing the two octets following the source address with 0x8100 (VLAN Protocol ID) and pad accordingly

- 0 = The MAC does not perform automatic detection

- Note 1: Table 30-6 provides a description of the pad function based on the configuration of this register.

- 2: This bit is ignored if the PADENABLE bit is cleared.

- **3:** This bit is used in conjunction with the AUTOPAD and VLANPAD bits.

Note: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware

### 33.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes power-saving features for the PIC32MZ EF devices. These devices offer various methods and modes that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 33.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the speed of PBCLK7, or selecting a lower power clock source (i.e., LPRC or Sosc).

In addition, the Peripheral Bus Scaling mode is available for each peripheral bus where peripherals are clocked at reduced speed by selecting a higher divider for the associated PBCLKx, or by disabling the clock completely.

# 33.2 Power-Saving with CPU Halted

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

#### 33.2.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted and the associated clocks are disabled. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the peripheral bus clocks will start running and the device will enter into Idle mode.

#### 33.2.2 IDLE MODE

In Idle mode, the CPU is Halted; however, all clocks are still enabled. This allows peripherals to continue to operate. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

| DC CHARA      | ACTERISTICS            |                        |                  |       | Conditions: 2.1V to 3.6V (unless otherwise stated) re $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |  |  |

|---------------|------------------------|------------------------|------------------|-------|-------------------------------------------------------------------------------------------------------------|--|--|