Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efh100-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 1            |                   |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 |                   |                  | —                |  |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x            | R/W-x            |  |

| 23:16        |                   |                   |                   | —                 |                   |                   | CAUS             | E<5:4>           |  |

|              | —                 | _                 | _                 |                   |                   | _                 | E                | V                |  |

|              | R/W-x             | R/W-x             | R/W-x             | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         |                   | CAUSE             | <3:0>             |                   |                   |                   |                  |                  |  |

|              | Z                 | 0                 | U                 | I                 |                   | _                 | _                | _                |  |

|              | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0              | U-0              |  |

| 7:0          |                   |                   |                   | FLAGS<4:0>        |                   |                   |                  |                  |  |

|              |                   | V                 | Z                 | 0                 | U                 | I                 |                  | _                |  |

#### REGISTER 3-8: FEXR: FLOATING POINT EXCEPTIONS STATUS REGISTER; CP1 REGISTER 26

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-18 Unimplemented: Read as '0'

bit 17-12 **CAUSE<5:0>:** FPU Exception Cause bits These bits indicated the exception conditions that arise during execution of an FPU arithmetic instruction.

- bit 17 E: Unimplemented Operation bit

- bit 16 V: Invalid Operation bit

- bit 15 **Z:** Divide-by-Zero bit

- bit 14 **O:** Overflow bit

- bit 13 **U:** Underflow bit

- bit 12 I: Inexact bit

- bit 11-7 Unimplemented: Read as '0'

- bit 6-2 FLAGS<4:0>: FPU Flags bits

These bits show any exception conditions that have occurred for completed instructions since the flag was last reset by software.

- bit 6 V: Invalid Operation bit

- bit 4 **Z:** Divide-by-Zero bit

- bit 4 O: Overflow bit

- bit 3 U: Underflow bit

- bit 2 I: Inexact bit

- bit 1-0 Unimplemented: Read as '0'

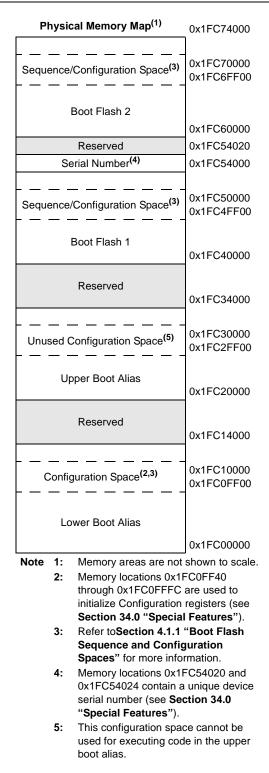

# FIGURE 4-5: BOOT AND ALIAS MEMORY MAP

#### TABLE 4-1: SFR MEMORY MAP

|                           | Virtual Ad | dress           |

|---------------------------|------------|-----------------|

| Peripheral                | Base       | Offset<br>Start |

| System Bus <sup>(1)</sup> | 0xBF8F0000 | 0x0000          |

| Prefetch                  |            | 0x0000          |

| EBI                       |            | 0x1000          |

| SQI1                      |            | 0x2000          |

| USB                       | 0xBF8E0000 | 0x3000          |

| Crypto                    |            | 0x5000          |

| RNG                       |            | 0x6000          |

| CAN1 and CAN2             |            | 0x0000          |

| Ethernet                  | 0xBF880000 | 0x2000          |

| USBCR                     |            | 0x4000          |

| PORTA-PORTK               | 0xBF860000 | 0x0000          |

| Timer1-Timer9             |            | 0x0000          |

| IC1-IC9                   |            | 0x2000          |

| OC1-OC9                   | 0xBF840000 | 0x4000          |

| ADC                       |            | 0xB000          |

| Comparator 1, 2           |            | 0xC000          |

| I2C1-I2C5                 |            | 0x0000          |

| SPI1-SPI6                 | 0,000000   | 0x1000          |

| UART1-UART6               | 0xBF820000 | 0x2000          |

| PMP                       |            | 0xE000          |

| Interrupt Controller      | 0xBF810000 | 0x0000          |

| DMA                       | 00000      | 0x1000          |

| Configuration             |            | 0x0000          |

| Flash Controller          |            | 0x0600          |

| Watchdog Timer            |            | 0x0800          |

| Deadman Timer             | 0vPE800000 | 0x0A00          |

| RTCC                      | 0xBF800000 | 0x0C00          |

| CVREF                     |            | 0x0E00          |

| Oscillator                |            | 0x1200          |

| PPS                       |            | 0x1400          |

Note 1: Refer to 4.2 "System Bus Arbitration" for important legal information.

# 4.2 System Bus Arbitration

| Note: | The     | System                                             | Bus       | interconnect     |  |  |  |  |  |  |  |

|-------|---------|----------------------------------------------------|-----------|------------------|--|--|--|--|--|--|--|

|       |         |                                                    |           | nstantiations of |  |  |  |  |  |  |  |

|       | the So  | the SonicsSX <sup>®</sup> interconnect from Sonics |           |                  |  |  |  |  |  |  |  |

|       | Inc. T  | his docum                                          | ent conta | ains materials   |  |  |  |  |  |  |  |

|       | that a  | e (c) 2003-                                        | 2015 So   | nics, Inc., and  |  |  |  |  |  |  |  |

|       | that co | onstitute pro                                      | oprietary | information of   |  |  |  |  |  |  |  |

|       | Sonics  | , Inc. Son                                         | icsSX is  | a registered     |  |  |  |  |  |  |  |

|       | tradem  | nark of S                                          | onics, I  | nc. All such     |  |  |  |  |  |  |  |

|       | materi  | als and trad                                       | emarks a  | are used under   |  |  |  |  |  |  |  |

|       | license | e from Sonic                                       | s, Inc.   |                  |  |  |  |  |  |  |  |

As shown in the PIC32MZ EF Family Block Diagram (see Figure 1-1), there are multiple initiator modules (I1 through I14) in the system that can access various target modules (T1 through T13). Table 4-4 illustrates which initiator can access which target. The System Bus supports simultaneous access to targets by initiators, so long as the initiators are accessing different targets. The System Bus will perform arbitration, if multiple initiators attempt to access the same target.

The System Bus arbitration scheme implements a nonprogrammable, Least Recently Serviced (LRS) priority, which provides Quality Of Service (QOS) for most initiators. However, some initiators can use Fixed High Priority (HIGH) arbitration to guarantee their access to data.

The arbitration scheme for the available initiators is shown in Table 4-5.

| ID | QOS                                                                     |

|----|-------------------------------------------------------------------------|

| 1  | LRS <sup>(1)</sup>                                                      |

| 2  | HIGH <sup>(1,2)</sup>                                                   |

| 3  | LRS <sup>(1)</sup>                                                      |

| 4  | HIGH <sup>(1,2)</sup>                                                   |

| 5  | LRS <sup>(1)</sup>                                                      |

| 6  | HIGH <sup>(1,2)</sup>                                                   |

| 7  | LRS                                                                     |

| 8  | LRS                                                                     |

| 9  | LRS                                                                     |

| 10 | LRS                                                                     |

| 11 | LRS                                                                     |

| 12 | LRS                                                                     |

| 13 | HIGH <sup>(2)</sup>                                                     |

| 14 | LRS                                                                     |

|    | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>11<br>12<br>13 |

TABLE 4-5:INITIATOR ID AND QOS

- Note 1: When accessing SRAM, the DMAPRI bit (CFGCON<25>) and the CPUPRI bit (CFGCON<24>) provide arbitration control for the DMA and CPU (when servicing an interrupt (i.e., EXL = 1)), respectively, by selecting the use of LRS or HIGH When using HIGH, the DMA and CPU get arbitration preference over all initiators using LRS.

- 2: Using HIGH arbitration can have serious negative effects on other initiators. Therefore, it is recommended to not enable this type of arbitration for an initiator that uses significant system bandwidth. HIGH arbitration is intended to be used for low bandwidth applications that require low latency, such as LCC graphics applications.

# 4.3 Permission Access and System Bus Registers

The System Bus on PIC32MZ EF family of microcontrollers provides access control capabilities for the transaction initiators on the System Bus.

The System Bus divides the entire memory space into fourteen target regions and permits access to each target by initiators via permission groups. Four Permission Groups (0 through 3) can be assigned to each initiator. Each permission group is independent of the others and can have exclusive or shared access to a region.

Using the CFGPG register (see Register 34-10 in **Section 34.0 "Special Features"**), Boot firmware can assign a permission group to each initiator, which can make requests on the System Bus.

The available targets and their regions, as well as the associated control registers to assign protection, are described and listed in Table 4-6.

Register 4-2 through Register 4-10 are used for setting and controlling access permission groups and regions.

To change these registers, they must be unlocked in hardware. The register lock is controlled by the PGLOCK Configuration bit (CFGCON<11>). Setting PGLOCK prevents writes to the control registers; clearing PGLOCK allows writes.

To set or clear the PGLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators with Enhanced PLL"** in the *"PIC32 Family Reference Manual"* for details.

|                                   | NORO Martin Martin | IRQ         | Martin       |          | Interru  | upt Bit Locatior | ı            | Persistent |

|-----------------------------------|--------------------|-------------|--------------|----------|----------|------------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>   | XC32 Vector Name   | #           | Vector #     | Flag     | Enable   | Priority         | Sub-priority | Interrupt  |

| UART6 Transfer Done               | _UART6_TX_VECTOR   | 190         | OFF190<17:1> | IFS5<30> | IEC5<30> | IPC47<20:18>     | IPC47<17:16> | Yes        |

| Reserved                          | —                  | 191         | —            | —        | _        | —                | —            | —          |

| ADC End of Scan Ready             | _ADC_EOS_VECTOR    | 192         | OFF192<17:1> | IFS6<0>  | IEC6<0>  | IPC48<4:2>       | IPC48<1:0>   | Yes        |

| ADC Analog Circuits Ready         | _ADC_ARDY_VECTOR   | 193         | OFF193<17:1> | IFS6<1>  | IEC6<1>  | IPC48<12:10>     | IPC48<9:8>   | Yes        |

| ADC Update Ready                  | _ADC_URDY_VECTOR   | 194         | OFF194<17:1> | IFS6<2>  | IEC6<2>  | IPC48<20:18>     | IPC48<17:16> | Yes        |

| Reserved                          | —                  | 195         | —            | _        | _        | —                | _            | —          |

| ADC Group Early Interrupt Request | _ADC_EARLY_VECTOR  | 196         | OFF196<17:1> | IFS6<4>  | IEC6<4>  | IPC49<4:2>       | IPC49<1:0>   | Yes        |

| Reserved                          | —                  | 197         | —            | —        | _        | —                | _            | —          |

| ADC0 Early Interrupt              | _ADC0_EARLY_VECTOR | 198         | OFF198<17:1> | IFS6<6>  | IEC6<6>  | IPC49<20:18>     | IPC49<17:16> | Yes        |

| ADC1 Early Interrupt              | _ADC1_EARLY_VECTOR | 199         | OFF199<17:1> | IFS6<7>  | IEC6<7>  | IPC49<28:26>     | IPC49<25:24> | Yes        |

| ADC2 Early Interrupt              | _ADC2_EARLY_VECTOR | 200         | OFF200<17:1> | IFS6<8>  | IEC6<8>  | IPC50<4:2>       | IPC50<1:0>   | Yes        |

| ADC3 Early Interrupt              | _ADC2_EARLY_VECTOR | 201         | OFF201<17:1> | IFS6<9>  | IEC6<9>  | IPC50<12:10>     | IPC50<9:8>   | Yes        |

| ADC4 Early Interrupt              | _ADC4_EARLY_VECTOR | 202         | OFF202<17:1> | IFS6<10> | IEC6<10> | IPC50<20:18>     | IPC50<17:16> | Yes        |

| Reserved                          | —                  | 203         | —            | —        | _        | —                | _            | —          |

| Reserved                          | —                  | 204         | —            | —        | _        | —                | _            | —          |

| ADC7 Early Interrupt              | _ADC7_EARLY_VECTOR | 205         | OFF205<17:1> | IFS6<13> | IEC6<13> | IPC51<12:10>     | IPC51<9:8>   | Yes        |

| ADC0 Warm Interrupt               | _ADC0_WARM_VECTOR  | 206         | OFF206<17:1> | IFS6<14> | IEC6<14> | IPC51<20:18>     | IPC51<17:16> | Yes        |

| ADC1 Warm Interrupt               | _ADC1_WARM_VECTOR  | 207         | OFF207<17:1> | IFS6<15> | IEC6<15> | IPC51<28:26>     | IPC51<25:24> | Yes        |

| ADC2 Warm Interrupt               | _ADC2_WARM_VECTOR  | 208         | OFF208<17:1> | IFS6<16> | IEC6<16> | IPC52<4:2>       | IPC52<1:0>   | Yes        |

| ADC3 Warm Interrupt               | _ADC3_WARM_VECTOR  | 209         | OFF209<17:1> | IFS6<17> | IEC6<17> | IPC52<12:10>     | IPC52<9:8>   | Yes        |

| ADC4 Warm Interrupt               | _ADC4_WARM_VECTOR  | 210         | OFF210<17:1> | IFS6<18> | IEC6<18> | IPC52<20:18>     | IPC52<17:16> | Yes        |

| Reserved                          |                    | 211         | —            | _        | _        | —                | —            | _          |

| Reserved                          | _                  | 212         | _            | _        | _        | —                | —            | _          |

| ADC7 Warm Interrupt               | _ADC7_WARM_VECTOR  | 213         | OFF213<17:1> | IFS6<21> | IEC6<21> | IPC53<12:10>     | IPC53<9:8>   | Yes        |

|                                   | Lowest N           | atural Orde | er Priority  |          |          |                  |              |            |

# TABLE 7-2: INTERRUPT IRQ, VECTOR, AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

3: This interrupt source is not available on 100-pin devices.

4: This interrupt source is not available on 124-pin devices.

# **REGISTER 7-2:** PRISS: PRIORITY SHADOW SELECT REGISTER (CONTINUED) bit 15-12 PRI3SS<3:0>: Interrupt with Priority Level 3 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 3 uses Shadow Set 0) 0111 = Interrupt with a priority level of 3 uses Shadow Set 7 0110 = Interrupt with a priority level of 3 uses Shadow Set 6 0001 = Interrupt with a priority level of 3 uses Shadow Set 1 0000 = Interrupt with a priority level of 3 uses Shadow Set 0 bit 11-8 **PRI2SS<3:0>:** Interrupt with Priority Level 2 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 2 uses Shadow Set 0) 0111 = Interrupt with a priority level of 2 uses Shadow Set 7 0110 = Interrupt with a priority level of 2 uses Shadow Set 6 0001 = Interrupt with a priority level of 2 uses Shadow Set 1 0000 = Interrupt with a priority level of 2 uses Shadow Set 0 PRI1SS<3:0>: Interrupt with Priority Level 1 Shadow Set bits<sup>(1)</sup> bit 7-4 1xxx = Reserved (by default, an interrupt with a priority level of 1 uses Shadow Set 0) 0111 = Interrupt with a priority level of 1 uses Shadow Set 7 0110 = Interrupt with a priority level of 1 uses Shadow Set 6 0001 = Interrupt with a priority level of 1 uses Shadow Set 1 0000 = Interrupt with a priority level of 1 uses Shadow Set 0 bit 3-1 Unimplemented: Read as '0' bit 0 SS0: Single Vector Shadow Register Set bit 1 = Single vector is presented with a shadow set 0 = Single vector is not presented with a shadow set

**Note 1:** These bits are ignored if the MVEC bit (INTCON<12>) = 0.

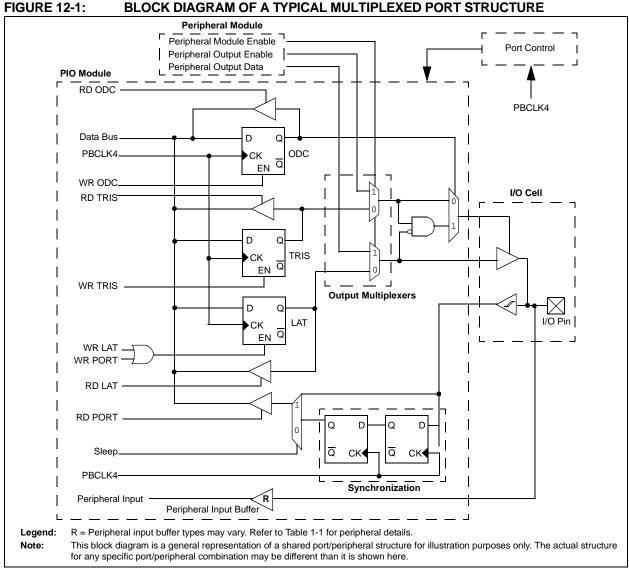

#### 12.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC32MZ EF family device to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Some of the key features of the I/O ports are:

- Individual output pin open-drain enable/disable

- Individual input pin weak pull-up and pull-down

- · Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- · Fast bit manipulation using CLR, SET and INV registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

BLOCK DIAGRAM OF A TYPICAL MULTIPLEXED PORT STRUCTURE

# TABLE 12-11: PORTE REGISTER MAP FOR 100-PIN, 124-PIN, AND 144-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |                |       |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0400                        | ANSELE                          | 31:16     |       | _     |       |       | —              |       | _            | _            |              | _            | —            |              | _            | _            |              | _            | 0000          |

| 0400                        | ANOLLL                          | 15:0      | —     | _     |       |       | —              | _     | ANSE9        | ANSE8        | ANSE7        | ANSE6        | ANSE5        | ANSE4        | _            | _            | —            |              | 03F0          |

| 0410                        | TRISE                           | 31:16     | —     | —     | —     | —     | —              | _     | —            | —            | —            | —            | —            | -            | —            | —            | —            | —            | 0000          |

| 0110                        | HUGE                            | 15:0      | —     | -     | —     | —     | —              | -     | TRISE9       | TRISE8       | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | 03FF          |

| 0420                        | PORTE                           | 31:16     | —     | —     | —     | —     | —              |       | —            | —            | —            | —            | —            |              | —            | —            | —            | —            | 0000          |

| 0.20                        |                                 | 15:0      | —     | —     | —     | —     | —              |       | RE9          | RE8          | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 0430                        | LATE                            | 31:16     | —     | —     | —     | —     | —              |       | —            | —            | —            | —            | —            |              | —            | _            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | _     | —     | —     | —              | _     | LATE9        | LATE8        | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | XXXX          |

| 0440                        | ODCE                            | 31:16     | _     | _     | —     | —     | —              | —     | —            | —            |              | —            | —            |              | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | _     | —     | —     | _              | —     | ODCE9        | ODCE8        | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 0450                        | CNPUE                           | 31:16     | —     | _     | —     | —     | _              | —     | —            | —            | _            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | —     | _     | _              | _     | CNPUE9       | CNPUE8       | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPUE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 0460                        | CNPDE                           | 31:16     | _     | _     | —     | _     | _              | _     | —            | _            | _            | —            | —            | _            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _              |       | CNPDE9       | CNPDE8       | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

| 0470                        |                                 | 31:16     | _     | _     | _     | _     | -              | _     |              | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0470                        | CNCONE                          | 15:0      | ON    | _     | _     | _     | EDGE<br>DETECT | _     | —            | —            | —            | _            | —            | _            | _            | _            | _            | _            | 0000          |

| 0480                        | CNENE                           | 31:16     | —     | -     | —     | —     | —              | -     | —            | —            | _            | _            | —            |              | —            | _            | —            | _            | 0000          |

| 0.00                        | 0.12.12                         | 15:0      | _     | _     | —     | _     | _              | _     | CNENE9       | CNENE8       | CNENE7       | CNENE6       | CNENE5       | CNENE4       | CNENE3       | CNENE2       | CNENE1       | CNENE0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | —     | —              |       | —            | —            | —            | —            | —            |              | —            | _            | —            | —            | 0000          |

| 0490                        | CNSTATE                         | 15:0      | _     | -     | —     | —     | —              | _     | CN<br>STATE9 | CN<br>STATE8 | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

| 04A0                        | CNNEE                           | 31:16     | _     |       | -     | _     | -              |       | _            |              | -            | ١            | -            |              |              |              | _            |              | 0000          |

| 04A0                        | CININEL                         | 15:0      | _     |       |       |       | -              |       | CNNEE9       | CNNEE8       | CNNEE7       | CNNEE6       | CNNEE5       | CNNEE4       | CNNEE3       | CNNEE2       | CNNEE1       | CNNEE0       | 0000          |

| 04B0                        | CNFE                            | 31:16     | _     | -     | —     | _     | _              | _     | —            | —            | _            | -            | _            | -            | _            | -            | _            | -            | 0000          |

| 0400                        |                                 | 15:0      | _     |       | —     | —     | _              |       | CNFE9        | CNFE8        | CNFE7        | CNFE6        | CNFE5        | CNFE4        | CNFE3        | CNFE2        | CNFE1        | CNFE0        | 0000          |

| 04C0                        | SRCON0E                         | 31:16     | —     | _     | —     | —     | —              | _     | —            | —            | —            | _            | —            | —            | _            | _            | —            |              | 0000          |

| 0400                        | SILCONUL                        | 15:0      | _     |       | —     | —     | —              | _     | —            | —            | -            |              | —            | —            | SR0E3        | SR0E2        | SR0E1        | SR0E0        | 0000          |

| 04D0                        | SRCON1E                         | 31:16     | —     | _     | —     | —     | —              | _     | —            | —            | —            | _            | —            | —            | —            | _            | —            | —            | 0000          |

| 0400                        | SILCONTE                        | 15:0      | _     | -     | —     | _     | _              | _     | -            | —            | _            | -            | _            | —            | SR1E3        | SR1E2        | SR1E1        | SR1E0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

# TABLE 14-1: TIMER2 THROUGH TIMER9 REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |                 |       |       |       |       |      | В    | its    |      |           |      |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-----------------|-------|-------|-------|-------|------|------|--------|------|-----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14           | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5      | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

|                             | TMR7                            | 31:16     | _     |                 | —     | —     | _     | _     | —    | —    | —      | _    | _         | _    | _    | —    | —    | —    | 0000       |

| 0010                        |                                 | 15:0      |       | TMR7<15:0> 0000 |       |       |       |       |      |      |        |      |           |      |      |      |      |      |            |

| 0C20                        | PR7                             | 31:16     | -     | _               | _     | _     | _     | -     | _    | _    | —      |      | _         |      | _    | _    | _    |      | 0000       |

| 0020                        |                                 | 15:0      |       |                 |       |       |       |       |      | PR7< | :15:0> |      |           |      |      |      |      |      | FFFF       |

| 0500                        | T8CON                           | 31:16     | _     | _               | —     | —     | —     | _     |      | —    | _      | _    | —         | _    | —    | _    |      | —    | 0000       |

| UEUU                        | TOCON                           | 15:0      | ON    | —               | SIDL  | -     |       |       | —    | —    | TGATE  | -    | CKPS<2:0  | >    | T32  | —    | TCS  | -    | 0000       |

| 0E10                        | TMR8                            | 31:16     |       | _               | —     | —     | _     | —     | _    | —    | —      | —    | —         | —    | —    | —    | _    | —    | 0000       |

| UEIU                        | TIVIRO                          | 15:0      |       |                 |       |       |       |       |      | TMR8 | <15:0> |      |           |      |      |      |      |      | 0000       |

| 0E20                        | PR8                             | 31:16     |       | _               | —     | —     | _     | —     | _    | —    | —      | —    | —         | —    | —    | —    | _    | —    | 0000       |

| UEZU                        | FRO                             | 15:0      |       |                 |       |       |       |       |      | PR8< | :15:0> |      |           |      |      |      |      |      | FFFF       |

| 1000                        | T9CON                           | 31:16     |       | _               | —     | —     | _     | —     | _    | —    | —      | —    | —         | —    | —    | —    | _    | —    | 0000       |

| 1000                        | 19001                           | 15:0      | ON    | _               | SIDL  | —     | _     | —     | _    | —    | TGATE  | -    | FCKPS<2:0 | >    | —    | —    | TCS  | —    | 0000       |

| 1010                        | TMR9                            | 31:16     |       | _               | —     | —     | _     | —     | _    | _    | —      | _    | _         | _    | _    | _    | _    | _    | 0000       |

| 1010                        | TIVIR9                          | 15:0      |       |                 |       |       |       |       |      | TMR9 | <15:0> |      |           |      |      |      |      |      | 0000       |

| 1020                        | PR9                             | 31:16     | —     |                 | —     | —     | —     | _     | —    | —    | —      | —    | —         | —    | —    | —    | —    | —    | 0000       |

| 1020                        | PK9                             | 15:0      |       |                 |       |       |       |       |      | PR9< | :15:0> |      |           |      |      |      |      |      | FFFF       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

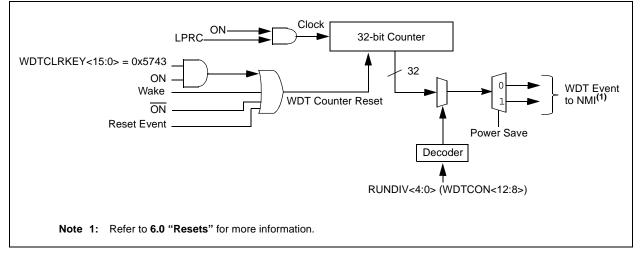

# 16.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). When enabled, the Watchdog Timer (WDT) operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

# FIGURE 16-1: WATCHDOG TIMER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | —                 | _                 | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | -                 |                   | —                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | _                 |                   | TΣ                | CMDTHR<4:         | 0>               |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 |                   | RX                | CMDTHR<4:0        | > <sup>(1)</sup> |                  |

#### REGISTER 20-6: SQI1CMDTHR: SQI COMMAND THRESHOLD REGISTER

# Legend:

| Logonal           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-13 Unimplemented: Read as '0'

bit 12-8 TXCMDTHR<4:0>: Transmit Command Threshold bits

In transmit initiation mode, the SQI module performs a transmit operation when transmit command threshold bytes are present in the TX FIFO. These bits should usually be set to '1' for normal Flash commands, and set to a higher value for page programming. For 16-bit mode, the value should be a multiple of 2.

bit 7-5 Unimplemented: Read as '0'

#### bit 4-0 **RXCMDTHR<4:0>:** Receive Command Threshold bits<sup>(1)</sup>

In receive initiation mode, the SQI module attempts to perform receive operations to fetch the receive command threshold number of bytes in the receive buffer. If space for these bytes is not present in the FIFO, the SQI will not initiate a transfer. For 16-bit mode, the value should be a multiple of 2.

If software performs any reads, thereby reducing the FIFO count, hardware would initiate a receive transfer to make the FIFO count equal to the value in these bits. If software would not like any more words latched into the FIFO, command initiation mode needs to be changed to Idle before any FIFO reads by software.

In the case of Boot/XIP mode, the SQI module will use the System Bus burst size, instead of the receive command threshold value.

Note 1: These bits should only be programmed when a receive is not active (i.e., during Idle mode or a transmit).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | _                 | _                 |                   | —                 |                   |                   | _                | _                |  |  |  |  |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | _                 |                   | —                 | _                 |                   | _                | _                |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | —                 | —                 | —                 | —                 | DMAEIE            | PKTCOMPIE         | BDDONEIE         | CONTHRIE         |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | CONEMPTYIE        | CONFULLIE         | RXTHRIE           | RXFULLIE          | RXEMPTYIE         | TXTHRIE           | TXFULLIE         | TXEMPTYIE        |  |  |  |  |

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

HS = Hardware Set

W = Writable bit

'1' = Bit is set

# REGISTER 20-8: SQI1INTEN: SQI INTERRUPT ENABLE REGISTER

| bit 31-12     | <b>Unimplemented:</b> Read as '0'                                     |

|---------------|-----------------------------------------------------------------------|

| bit 11        | DMAEIE: DMA Bus Error Interrupt Enable bit                            |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 10        | PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 9         | BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit             |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 8         | CONTHRIE: Control Buffer Threshold Interrupt Enable bit               |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 7         | CONEMPTYIE: Control Buffer Empty Interrupt Enable bit                 |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 6         | CONFULLIE: Control Buffer Full Interrupt Enable bit                   |

|               | This bit enables an interrupt when the receive FIFO buffer is full.   |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 5         | RXTHRIE: Receive Buffer Threshold Interrupt Enable bit                |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 4         | <b>RXFULLIE:</b> Receive Buffer Full Interrupt Enable bit             |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 3         | <b>RXEMPTYIE:</b> Receive Buffer Empty Interrupt Enable bit           |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 2         | TXTHRIE: Transmit Threshold Interrupt Enable bit                      |

|               | 1 = Interrupt is enabled                                              |

| L.1. A        | 0 = Interrupt is disabled                                             |

| bit 1         | TXFULLIE: Transmit Buffer Full Interrupt Enable bit                   |

|               | 1 = Interrupt is enabled                                              |

| <b>h</b> :+ 0 | 0 = Interrupt is disabled                                             |

| bit 0         | <b>TXEMPTYIE:</b> Transmit Buffer Empty Interrupt Enable bit          |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

Legend:

R = Readable bit

-n = Value at POR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | BDADDR<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | BDADDR<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | BDADDR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                   |                   |                   | BDADDF            | R<7:0>            |                   |                  |                  |  |

#### REGISTER 20-16: SQI1BDBASEADD: SQI BUFFER DESCRIPTOR BASE ADDRESS REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 BDADDR<31:0>: DMA Base Address bits

These bits contain the physical address of the root buffer descriptor. This register should be updated only when the DMA is idle.

### REGISTER 20-17: SQI1BDSTAT: SQI BUFFER DESCRIPTOR STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 00.40        | U-0               | U-0               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 23:16        | —                 | —                 |                   | BDSTAT            | DMASTART          | DMAACTV           |                  |                  |  |

| 45.0         | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 15:8         | BDCON<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

|              |                   |                   |                   | BDCO              | N<7:0>            |                   |                  |                  |  |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-22 Unimplemented: Read as '0'

bit 21-18 BDSTATE<3:0>: DMA Buffer Descriptor Processor State Status bits

- These bits return the current state of the buffer descriptor processor:

- 5 = Fetched buffer descriptor is disabled

- 4 = Descriptor is done

- 3 = Data phase

- 2 = Buffer descriptor is loading

- 1 = Descriptor fetch request is pending

- 0 = Idle

- bit 17 DMASTART: DMA Buffer Descriptor Processor Start Status bit

- 1 = DMA has started

- 0 = DMA has not started

- bit 16 DMAACTV: DMA Buffer Descriptor Processor Active Status bit

- 1 = Buffer Descriptor Processor is active

- 0 = Buffer Descriptor Processor is idle

- bit 15-0 **BDCON<15:0>:** DMA Buffer Descriptor Control Word bits These bits contain the current buffer descriptor control word.

### REGISTER 26-5: CESTAT: CRYPTO ENGINE STATUS REGISTER (CONTINUED)

bit 16 ACTIVE: Buffer Descriptor Processor Status bit

- 1 = BDP is active

- 0 = BDP is idle

- bit 15-0 BDCTRL<15:0>: Descriptor Control Word Status bits

These bits contain the Control Word for the current Buffer Descriptor.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 |                   |                   | TRGSRC7<4:0>      |                   |                   |                  |                  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 |                   |                   | TRGSRC6<4:0>      |                   |                   |                  |                  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 |                   |                   | TRGSRC5<4:0>      |                   |                   |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   |                   | Т                 | RGSRC4<4:0        | )>               |                  |

#### REGISTER 28-18: ADCTRG2: ADC TRIGGER SOURCE 2 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

bit 28-24 TRGSRC7<4:0>: Trigger Source for Conversion of Analog Input AN7 Select bits

```

11111 = Reserved

.

.

01101 = Reserved

01100 = Comparator 2 (COUT)

01011 = Comparator 1 (COUT)

01010 = OCMP5

01001 = OCMP3

01000 = OCMP1

00111 = TMR5 match

00101 = TMR3 match

00101 = TMR1 match

00101 = TMR1 match

00101 = STRIG

00011 = Global level software trigger (GLSWTRG)

00001 = Global software edge Trigger (GSWTRG)

00000 = No Trigger

```

For STRIG, in addition to setting the trigger, it also requires programming of the STRGSRC<4:0> bits (ADCCON1<20:16>) to select the trigger source, and requires the appropriate CSS bits to be set in the ADCCSS*x* registers.

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TRGSRC6<4:0>:** Trigger Source for Conversion of Analog Input AN6 Select bits See bits 28-24 for bit value definitions.

- bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **TRGSRC5<4:0>:** Trigger Source for Conversion of Analog Input AN5 Select bits See bits 28-24 for bit value definitions.

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **TRGSRC4<4:0>:** Trigger Source for Conversion of Analog Input AN4 Select bits See bits 28-24 for bit value definitions.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     | FLTEN3            | MSEL3<1:0>        |                   | FSEL3<4:0>        |                   |                   |                  |                  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     | FLTEN2            | MSEL2<1:0>        |                   | FSEL2<4:0>        |                   |                   |                  |                  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | FLTEN1            | MSEL1<1:0>        |                   | FSEL1<4:0>        |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN0            | MSEL0<1:0>        |                   | FSEL0<4:0>        |                   |                   |                  |                  |

### REGISTER 29-10: CIFLTCON0: CAN FILTER CONTROL REGISTER 0

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN3: Filter 3 Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 0 = Filter is disabled                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 30-29 | MSEL3<1:0>: Filter 3 Mask Select bits                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 11 = Acceptance Mask 3 selected                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 10 = Acceptance Mask 2 selected                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 01 = Acceptance Mask 1 selected                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 00 = Acceptance Mask 0 selected                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 28-24 | FSEL3<4:0>: FIFO Selection bits                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                                                                                                                                                                                                                                                                                 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                                                                                                                                                                                                                                                                                 |

|           | •                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | •                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | •                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                                                                                                                                                                                                                    |

| bit 23    | FLTEN2: Filter 2 Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DIL 23    | FLIENZ: Filler 2 Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DIL 23    | 1 = Filter is enabled                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DIL 23    |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 22-21 | 1 = Filter is enabled                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Filter is enabled</li> <li>0 = Filter is disabled</li> <li>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits</li> <li>11 = Acceptance Mask 3 selected</li> </ul>                                                                                                                                                                                                                                                                     |

|           | <ul> <li>1 = Filter is enabled</li> <li>0 = Filter is disabled</li> <li>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits</li> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> </ul>                                                                                                                                                                                                                            |

|           | <ul> <li>1 = Filter is enabled</li> <li>0 = Filter is disabled</li> <li>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits</li> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> </ul>                                                                                                                                                                                   |

| bit 22-21 | <pre>1 = Filter is enabled<br/>0 = Filter is disabled<br/>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits<br/>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected</pre>                                                                                                                                                                                 |

|           | <pre>1 = Filter is enabled<br/>0 = Filter is disabled<br/>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits<br/>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>FSEL2&lt;4:0&gt;: FIFO Selection bits</pre>                                                                                                                                       |

| bit 22-21 | <pre>1 = Filter is enabled<br/>0 = Filter is disabled<br/>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits<br/>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>FSEL2&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31</pre>                                                                       |

| bit 22-21 | <pre>1 = Filter is enabled<br/>0 = Filter is disabled<br/>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits<br/>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>FSEL2&lt;4:0&gt;: FIFO Selection bits</pre>                                                                                                                                       |

| bit 22-21 | <pre>1 = Filter is enabled<br/>0 = Filter is disabled<br/>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits<br/>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>FSEL2&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31</pre>                                                                       |

| bit 22-21 | <pre>1 = Filter is enabled<br/>0 = Filter is disabled<br/>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits<br/>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>FSEL2&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31</pre>                                                                       |

| bit 22-21 | <pre>1 = Filter is enabled<br/>0 = Filter is disabled<br/>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits<br/>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>FSEL2&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31<br/>11110 = Message matching filter is stored in FIFO buffer 30<br/>•</pre> |

| bit 22-21 | <pre>1 = Filter is enabled<br/>0 = Filter is disabled<br/>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits<br/>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>FSEL2&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31</pre>                                                                       |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range          | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |

|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|

| 04.04                 | R/W-0              | R/W-0              |  |  |

| 31:24 CiFIFOBA<31:24> |                   |                   |                   |                   |                   |                   |                    |                    |  |  |

| 00.40                 | R/W-0              | R/W-0              |  |  |

| 23:16                 | CiFIFOBA<23:16>   |                   |                   |                   |                   |                   |                    |                    |  |  |

| 15:8                  | R/W-0              | R/W-0              |  |  |

| 15:8                  | CiFIFOBA<15:8>    |                   |                   |                   |                   |                   |                    |                    |  |  |

| 7.0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |

| 7:0                   |                   | CiFIFOBA<7:0>     |                   |                   |                   |                   |                    |                    |  |  |

#### REGISTER 29-19: CIFIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

# Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 CiFIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Note that bits <1:0> are read-only and read '0', forcing the messages to be 32-bit word-aligned in device RAM.

**Note 1:** This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

#### REGISTER 30-19: ETHMCOLFRM: ETHERNET CONTROLLER MULTIPLE COLLISION FRAMES STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                 | _                 | _                 | —                 | _                | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | —                 | _                | —                |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 10.0         | MCOLFRMCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | MCOLFRMCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |