Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efh100t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                                   |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|          | •                      | •               |                 | •                        | PO          | RTD            | ·                                 |

| RD0      | 46                     | 71              | A48             | 104                      | I/O         | ST             | PORTD is a bidirectional I/O port |

| RD1      | 49                     | 76              | A52             | 109                      | I/O         | ST             |                                   |

| RD2      | 50                     | 77              | B42             | 110                      | I/O         | ST             |                                   |

| RD3      | 51                     | 78              | A53             | 111                      | I/O         | ST             |                                   |

| RD4      | 52                     | 81              | A56             | 118                      | I/O         | ST             |                                   |

| RD5      | 53                     | 82              | B46             | 119                      | I/O         | ST             |                                   |

| RD6      | —                      | _               | A57             | 120                      | I/O         | ST             |                                   |

| RD7      | —                      | _               | B47             | 121                      | I/O         | ST             |                                   |

| RD9      | 43                     | 68              | B38             | 97                       | I/O         | ST             |                                   |

| RD10     | 44                     | 69              | A46             | 98                       | I/O         | ST             |                                   |

| RD11     | 45                     | 70              | B39             | 99                       | I/O         | ST             |                                   |

| RD12     | —                      | 79              | B43             | 112                      | I/O         | ST             |                                   |

| RD13     | —                      | 80              | A54             | 113                      | I/O         | ST             |                                   |

| RD14     | —                      | 47              | B27             | 69                       | I/O         | ST             |                                   |

| RD15     | —                      | 48              | A32             | 70                       | I/O         | ST             |                                   |

|          |                        |                 |                 |                          | PO          | RTE            |                                   |

| RE0      | 58                     | 91              | B52             | 135                      | I/O         | ST             | PORTE is a bidirectional I/O port |

| RE1      | 61                     | 94              | A64             | 138                      | I/O         | ST             |                                   |

| RE2      | 62                     | 98              | A66             | 142                      | I/O         | ST             |                                   |

| RE3      | 63                     | 99              | B56             | 143                      | I/O         | ST             |                                   |

| RE4      | 64                     | 100             | A67             | 144                      | I/O         | ST             |                                   |

| RE5      | 1                      | 3               | A3              | 3                        | I/O         | ST             |                                   |

| RE6      | 2                      | 4               | B2              | 4                        | I/O         | ST             |                                   |

| RE7      | 3                      | 5               | A4              | 5                        | I/O         | ST             |                                   |

| RE8      | —                      | 18              | B10             | 23                       | I/O         | ST             |                                   |

| RE9      |                        | 19              | A12             | 24                       | I/O         | ST             |                                   |

|          |                        |                 |                 |                          | PC          | RTF            |                                   |

| RF0      | 56                     | 85              | A59             | 124                      | I/O         | ST             | PORTF is a bidirectional I/O port |

| RF1      | 57                     | 86              | B49             | 125                      | I/O         | ST             |                                   |

| RF2      |                        | 57              | B31             | 79                       | I/O         | ST             |                                   |

| RF3      | 38                     | 56              | A38             | 78                       | I/O         | ST             |                                   |

| RF4      | 4 41 64 B36 90         | 90              | I/O             | ST                       |             |                |                                   |

| RF5      | 42                     | 65              | A44             | 91                       | I/O         | ST             |                                   |

| RF8      |                        | 80              | I/O             | ST                       | ]           |                |                                   |

| RF12     | —                      | 40              | B22             | 58                       | I/O         | ST             |                                   |

| RF13     | —                      | 39              | A26             | 57                       | I/O         | ST             |                                   |

| Legend:  | CMOS = C               | MOS-comp        | atible input    | t or output              |             | Analog =       | Analog input P = Power            |

#### **TABLE 1-6:** PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS (CONTINUED)

CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output PPS = Peripheral Pin Select P = Power I = Input

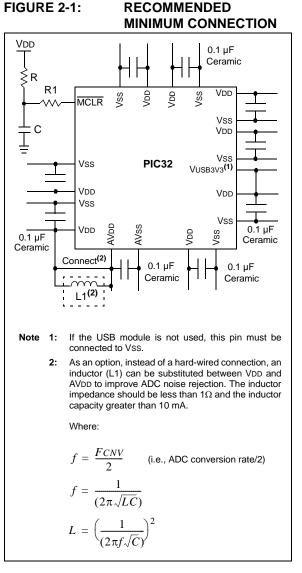

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

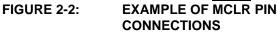

# 2.3 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

Pulling The MCLR pin low generates either a device Reset or a POR, depending on the setting of the SMCLR bit (DEVCFG0<15>). Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

**3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

DS60001320D-page 38

# 3.1.4 FLOATING POINT UNIT (FPU)

The Floating Point Unit (FPU), Coprocessor (CP1), implements the MIPS Instruction Set Architecture for floating point computation. The implementation supports the ANSI/IEEE Standard 754 (IEEE for Binary Floating Point Arithmetic) for 32-bit and 64-bit floating point data formats. The FPU can be programmed to have thirty-two 32-bit or 64-bit floating point registers used for floating point operations.

The performance is optimized for 32-bit formats. Most instructions have one FPU cycle throughput and four FPU cycle latency. The FPU implements the multiply-add (MADD) and multiply-sub (MSUB) instructions with intermediate rounding after the multiply function. The result is guaranteed to be the same as executing a MUL and an ADD instruction separately, but the instruction latency, instruction fetch, dispatch bandwidth, and the total number of register accesses are improved.

IEEE denormalized input operands and results are supported by hardware for some instructions. IEEE denormalized results are not supported by hardware in general, but a fast flush-to-zero mode is provided to optimize performance. The fast flush-to-zero mode is enabled through the FCCR register, and use of this mode is recommended for best performance when denormalized results are generated.

The FPU has a separate pipeline for floating point instruction execution. This pipeline operates in parallel with the integer core pipeline and does not stall when the integer pipeline stalls. This allows long-running FPU operations, such as divide or square root, to be partially masked by system stalls and/or other integer unit instructions. Arithmetic instructions are always dispatched and completed in order, but loads and stores can complete out of order. The exception model is "precise" at all times.

Table 3-4 contains the floating point instruction latencies and repeat rates for the processor core. In this table, 'Latency' refers to the number of FPU cycles necessary for the first instruction to produce the result needed by the second instruction. The "Repeat Rate" refers to the maximum rate at which an instruction can be executed per FPU cycle.

#### TABLE 3-4: FPU INSTRUCTION LATENCIES AND REPEAT RATES

| Op code                                                                                                            | Latency<br>(FPU<br>Cycles) | Repeat<br>Rate<br>(FPU<br>Cycles) |

|--------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------|

| ABS.[S,D], NEG.[S,D],<br>ADD.[S,D], SUB.[S,D],<br>C.cond.[S,D], MUL.S                                              | 4                          | 1                                 |

| MADD.S, MSUB.S,<br>NMADD.S, NMSUB.S,<br>CABS.cond.[S,D]                                                            | 4                          | 1                                 |

| CVT.D.S, CVT.PS.PW,<br>CVT.[S,D].[W,L]                                                                             | 4                          | 1                                 |

| CVT.S.D,<br>CVT.[W,L].[S,D],<br>CEIL.[W,L].[S,D],<br>FLOOR.[W,L].[S,D],<br>ROUND.[W,L].[S,D],<br>TRUNC.[W,L].[S,D] | 4                          | 1                                 |

| MOV.[S,D], MOVF.[S,D],<br>MOVN.[S,D],<br>MOVT.[S,D], MOVZ.[S,D]                                                    | 4                          | 1                                 |

| MUL.D                                                                                                              | 5                          | 2                                 |

| MADD.D, MSUB.D,<br>NMADD.D, NMSUB.D                                                                                | 5                          | 2                                 |

| RECIP.S                                                                                                            | 13                         | 10                                |

| RECIP.D                                                                                                            | 26                         | 21                                |

| RSQRT.S                                                                                                            | 17                         | 14                                |

| RSQRT.D                                                                                                            | 36                         | 31                                |

| DIV.S, SQRT.S                                                                                                      | 17                         | 14                                |

| DIV.D, SQRT.D                                                                                                      | 32                         | 29                                |

| MTC1, DMTC1, LWC1,<br>LDC1, LDXC1, LUXC1,<br>LWXC1                                                                 | 4                          | 1                                 |

| MFC1, DMFC1, SWC1,<br>SDC1, SDXC1, SUXC1,<br>SWXC1                                                                 | 1                          | 1                                 |

Legend: S = Single (32-bit) D = Double (64-bit)W = Word (32-bit) L = Long word (64-bit)

# 4.1.1 BOOT FLASH SEQUENCE AND CONFIGURATION SPACES

Sequence space is used to identify which boot Flash is aliased by aliased regions. If the value programmed into the TSEQ<15:0> bits of the BF1SEQ3 word is equal to or greater than the value programmed into the TSEQ<15:0> bits of the BF2SEQ3 word, boot Flash 1 is aliased by the lower boot alias region, and boot Flash 2 is aliased by the upper boot alias region. If the TSEQ<15:0> bits of the BF2SEQ3 word is greater than the TSEQ<15:0> bits of the BF1SEQ3 word, the opposite is true (see Table 4-2 and Table 4-3 for BFxSEQ3 word memory locations).

The CSEQ<15:0> bits must contain the one's complement value of the TSEQ<15:0> bits; otherwise, the value of the TSEQ<15:0> bits is considered invalid, and an alternate sequence is used. See Section 4.1.2 "Alternate Sequence and Configuration Words" for more information.

Once boot Flash memories are aliased, configuration space located in the lower boot alias region is used as the basis for the Configuration words, DEVSIGNO, DEVCPO, and DEVCFGx (and the associated alternate configuration registers). This means that the boot Flash region to be aliased by lower boot alias region memory must contain configuration values in the appropriate memory locations.

| Note: | Do not use word program operation |

|-------|-----------------------------------|

|       | (NVMOP<3:0> = 0001) when program- |

|       | ming data into the sequence and   |

|       | configuration spaces.             |

# 4.1.2 ALTERNATE SEQUENCE AND CONFIGURATION WORDS

Every word in the configuration space and sequence space has an associated alternate word (designated by the letter A as the first letter in the name of the word). During device start-up, primary words are read and if uncorrectable ECC errors are found, the BCFGERR (RCON<27>) flag is set and alternate words are used. If uncorrectable ECC errors are found in primary and alternate words, the BCFGFAIL (RCON<26>) flag is set and the default configuration is used.

#### **TABLE 4-6:** SYSTEM BUS TARGETS AND ASSOCIATED PROTECTION REGISTERS (CONTINUED)

|                  |                                                                            |            |                                             | SBTxREC                      | Gy Register                                |                |                   |                   | SBTxRD   | y Register                                                      | SBTxWR   | y Register                                                       |

|------------------|----------------------------------------------------------------------------|------------|---------------------------------------------|------------------------------|--------------------------------------------|----------------|-------------------|-------------------|----------|-----------------------------------------------------------------|----------|------------------------------------------------------------------|

| Target<br>Number | Target Description <sup>(5)</sup>                                          | Name       | Region Base<br>(BASE<21:0>)<br>(see Note 2) | Physical<br>Start<br>Address | Region Size<br>(SIZE<4:0>)<br>(see Note 3) | Region<br>Size | Priority<br>(PRI) | Priority<br>Level | Name     | Read<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) | Name     | Write<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) |

|                  | Peripheral Set 2:                                                          | SBT6REG0   | R                                           | 0x1F820000                   | R                                          | 64 KB          | —                 | 0                 | SBT6RD0  | R/W <sup>(1)</sup>                                              | SBT6WR0  | R/W <sup>(1)</sup>                                               |

| 6                | SPI1-SPI6<br>I2C1-I2C5<br>UART1-UART6<br>PMP                               | SBT6REG1   | R/W                                         | R/W                          | R/W                                        | R/W            | _                 | 3                 | SBT6RD1  | R/W <sup>(1)</sup>                                              | SBT6WR1  | R/W <sup>(1)</sup>                                               |

|                  | Peripheral Set 3:                                                          | SBT7REG0   | R                                           | 0x1F840000                   | R                                          | 64 KB          | —                 | 0                 | SBT7RD0  | R/W <sup>(1)</sup>                                              | SBT7WR0  | R/W <sup>(1)</sup>                                               |

| 7                | Timer1-Timer9<br>IC1-IC9<br>OC1-OC9<br>ADC<br>Comparator 1<br>Comparator 2 | SBT7REG1   | R/W                                         | R/W                          | R/W                                        | R/W            | _                 | 3                 | SBT7RD1  | R/W <sup>(1)</sup>                                              | SBT7WR1  | R/W <sup>(1)</sup>                                               |

|                  | Peripheral Set 4:                                                          | SBT8REG0   | R                                           | 0x1F860000                   | R                                          | 64 KB          | —                 | 0                 | SBT8RD0  | R/W <sup>(1)</sup>                                              | SBT8WR0  | R/W <sup>(1)</sup>                                               |

| 8                | PORTA-PORTK                                                                | SBT8REG1   | R/W                                         | R/W                          | R/W                                        | R/W            | —                 | 3                 | SBT8RD1  | R/W <sup>(1)</sup>                                              | SBT8WR1  | R/W <sup>(1)</sup>                                               |

|                  | Peripheral Set 5:                                                          | SBT9REG0   | R                                           | 0x1F880000                   | R                                          | 64 KB          | —                 | 0                 | SBT9RD0  | R/W <sup>(1)</sup>                                              | SBT9WR0  | R/W <sup>(1)</sup>                                               |

| 9                | CAN1<br>CAN2<br>Ethernet Controller                                        | SBT9REG1   | R/W                                         | R/W                          | R/W                                        | R/W            | _                 | 3                 | SBT9RD1  | R/W <sup>(1)</sup>                                              | SBT9WR1  | R/W <sup>(1)</sup>                                               |

| 10               | Peripheral Set 6:<br>USB                                                   | SBT10REG0  | R                                           | 0x1F8E3000                   | R                                          | 4 KB           | _                 | 0                 | SBT10RD0 | R/W <sup>(1)</sup>                                              | SBT10WR0 | R/W <sup>(1)</sup>                                               |

| 11               | External Memory via SQI1 and                                               | SBT11REG0  | R                                           | 0x3000000                    | R                                          | 64 MB          | —                 | 0                 | SBT11RD0 | R/W <sup>(1)</sup>                                              | SBT11WR0 | R/W <sup>(1)</sup>                                               |

| 11               | SQI1 Module                                                                | SBT11REG1  | R                                           | 0x1F8E2000                   | R                                          | 4 KB           | _                 | 3                 | SBT11RD1 | R/W <sup>(1)</sup>                                              | SBT11WR1 | R/W <sup>(1)</sup>                                               |

| 12               | Peripheral Set 7:<br>Crypto Engine                                         | SBT12REG0  | R                                           | 0x1F8E5000                   | R                                          | 4 KB           | _                 | 0                 | SBT12RD0 | R/W <sup>(1)</sup>                                              | SBT12WR0 | R/W <sup>(1)</sup>                                               |

| 13               | Peripheral Set 8:<br>RNG Module                                            | SBT13REG0  | R                                           | 0x1F8E6000                   | R                                          | 4 KB           | _                 | 0                 | SBT13RD0 | R/W <sup>(1)</sup>                                              | SBT13WR0 | R/W <sup>(1)</sup>                                               |

| Legend:          | R = Read; $R/W = R$                                                        | ead/Write; | 'x' in a regist                             | er name = 0-13;              | 'y' ir                                     | a register na  | ame = 0-8.        |                   |          |                                                                 |          |                                                                  |

Reset values for these bits are '0', '1', '1', '1', respectively. Note 1:

2:

The BASE<21:0> bits must be set to the corresponding Physical Address and right shifted by 10 bits. For Read-only bits, this value is set by hardware on Reset. The SIZE<4:0> bits must be set to the corresponding Region Size, based on the following formula: Region Size = 2<sup>(SIZE-1)</sup> x 1024 bytes. For read-only bits, this value is set by hardware on Reset. 3:

Refer to the Device Memory Maps (Figure 4-1 through Figure 4-4) for specific device memory sizes and start addresses. 4:

5: See Table 4-1for information on specific target memory size and start addresses.

6: The SBTxREG1 SFRs are reserved, and therefore, are not listed in this table for this target.

#### 7.3 **Interrupt Control Registers**

#### **TABLE 7-3:** INTERRUPT REGISTER MAP

| ress<br>()                  |                                 | e         |                      |               |             |                 |                       |                         |                       | B                     | its                   |                        |                        |                        |          |                         |                         |                        | s          |

|-----------------------------|---------------------------------|-----------|----------------------|---------------|-------------|-----------------|-----------------------|-------------------------|-----------------------|-----------------------|-----------------------|------------------------|------------------------|------------------------|----------|-------------------------|-------------------------|------------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                | 30/14         | 29/13       | 28/12           | 27/11                 | 26/10                   | 25/9                  | 24/8                  | 23/7                  | 22/6                   | 21/5                   | 20/4                   | 19/3     | 18/2                    | 17/1                    | 16/0                   | All Resets |

|                             |                                 | 31:16     |                      |               |             | NMIK            | EY<7:0>               |                         |                       |                       | —                     | —                      | _                      | _                      | _        | _                       | —                       | _                      | 0000       |

| 0000                        | INTCON                          | 15:0      | _                    | _             | _           | MVEC            | _                     |                         | TPC<2:0>              |                       | —                     | _                      | _                      | INT4EP                 | INT3EP   | INT2EP                  | INT1EP                  | INT0EP                 | 0000       |

| 0010                        |                                 | 31:16     |                      |               |             |                 |                       |                         |                       | 0000                  |                       |                        |                        |                        |          |                         |                         |                        |            |

| 0010                        | PRISS                           | 15:0      |                      | PRI3SS        | S<3:0>      |                 |                       | PRI2SS                  | 8<3:0>                |                       |                       | PRI1S                  | S<3:0>                 |                        | _        | -                       | —                       | SS0                    | 0000       |

| 0020                        | INTSTAT                         | 31:16     | _                    |               | _           | _               |                       | -                       |                       | _                     | _                     | _                      |                        | _                      | _        |                         | _                       | —                      | 0000       |

| 0020                        |                                 | 15:0      | _                    | _             | —           | —               | _                     |                         | SRIPL<2:0>            |                       |                       |                        |                        | SIR                    | Q<7:0>   |                         |                         |                        | 0000       |

| 0030                        | IPTMR                           | 31:16     |                      |               |             |                 |                       |                         |                       | IPTMR                 | <31.0>                |                        |                        |                        |          |                         |                         |                        | 0000       |

| 0000                        |                                 | 15:0      |                      |               |             |                 |                       |                         | 0000                  |                       |                       |                        |                        |                        |          |                         |                         |                        |            |

| 0040                        | IFS0                            | 31:16     | OC6IF                | IC6IF         | IC6EIF      | T6IF            | OC5IF                 | IC5IF                   | IC5EIF                | T5IF                  | INT4IF                | OC4IF                  | IC4IF                  | IC4EIF                 | T4IF     | INT3IF                  | OC3IF                   | IC3IF                  | 0000       |

| 00.0                        |                                 | 15:0      | IC3EIF               | T3IF          | INT2IF      | OC2IF           | IC2IF                 | IC2EIF                  | T2IF                  | INT1IF                | OC1IF                 | IC1IF                  | IC1EIF                 | T1IF                   | INT0IF   | CS1IF                   | CS0IF                   | CTIF                   | 0000       |

| 0050                        | IFS1                            | 31:16     | ADCD4IF              | ADCD3IF       | ADCD2IF     | ADCD1IF         | ADCD0IF               | ADCFLTIF                | ADCDF6IF              | ADCDF5IF              | ADCDF4IF              | ADCDF3IF               | ADCDF2IF               | ADCDF1IF               | ADCDC6IF | ADCDC5IF                | ADCDC4IF                | ADCDC3IF               |            |

|                             |                                 | 15:0      | ADCDC2IF             |               | ADCFIFOIF   | ADCIF           | OC9IF                 | IC9IF                   | IC9EIF                | T9IF                  | OC8IF                 | IC8IF                  | IC8EIF                 | T8IF                   | OC7IF    | IC7IF                   | IC7EIF                  | T7IF                   | 0000       |

| 0060                        | IFS2 <sup>(5)</sup>             | 31:16     | ADCD36IF             | ADCD35IF      | ADCD34IF    | ADCD33IF        | ADCD32IF              | ADCD31IF                | ADCD30IF              | ADCD29IF              | ADCD28IF              | ADCD27IF               | ADCD26IF               | ADCD25IF               | ADCD24IF | ADCD23IF                | ADCD22IF                | ADCD21IF               | -          |

|                             |                                 | 15:0      | ADCD20IF             | ADCD19IF      | ADCD18IF    | ADCD17IF        | ADCD16IF              | ADCD15IF                | ADCD14IF              | ADCD13IF              | ADCD12IF              | ADCD11IF               | ADCD10IF               | ADCD9IF                | ADCD8IF  | ADCD7IF                 | ADCD6IF                 | ADCD5IF                | 0000       |

| 0070                        | IFS3 <sup>(6)</sup>             | 31:16     | CNKIF <sup>(8)</sup> | CNJIF         | CNHIF       | CNGIF           | CNFIF                 | CNEIF                   | CNDIF                 | CNCIF                 | CNBIF                 | CNAIF                  | I2C1MIF                | I2C1SIF                | I2C1BIF  | U1TXIF                  | U1RXIF                  | U1EIF                  | 0000       |

|                             |                                 | 15:0      | SPI1TXIF             | SPI1RXIF      | SPI1EIF     | —               | CRPTIF <sup>(7)</sup> | SBIF                    | CFDCIF                | CPCIF                 | ADCD44IF              | ADCD43IF               | ADCD42IF               | ADCD41IF               | ADCD40IF | ADCD39IF                | ADCD38IF                | ADCD37IF               |            |

| 0080                        | IFS4                            | 31:16     | <b>U3TXIF</b>        | U3RXIF        | U3EIF       | <b>SPI3TXIF</b> | <b>SPI3RXIF</b>       | SPI3EIF                 | ETHIF                 | CAN2IF <sup>(3)</sup> | CAN1IF <sup>(3)</sup> | I2C2MIF <sup>(2)</sup> | 12C2SIF <sup>(2)</sup> | I2C2BIF <sup>(2)</sup> | U2TXIF   | U2RXIF                  | U2EIF                   | SPI2TXIF               | 0000       |

|                             |                                 | 15:0      | SPI2RXIF             | SPI2EIF       | DMA7IF      | DMA6IF          | DMA5IF                | DMA4IF                  | DMA3IF                | DMA2IF                | DMA1IF                | DMA0IF                 | USBDMAIF               | USBIF                  | CMP2IF   | CMP1IF                  | PMPEIF                  | PMPIF                  | 0000       |

| 0090                        | IFS5                            | 31:16     | —                    | U6TXIF        | U6RXIF      | U6EIF           | SPI6TX <sup>(2)</sup> | SPI6RXIF <sup>(2)</sup> | SPI6IF <sup>(2)</sup> | I2C5MIF               | I2C5SIF               | I2C5BIF                | U5TXIF                 | U5RXIF                 | U5EIF    | SPI5TXIF <sup>(2)</sup> | SPI5RXIF <sup>(2)</sup> | SPI5EIF <sup>(2)</sup> |            |

|                             |                                 | 15:0      | I2C4MIF              | I2C4SIF       | I2C4BIF     | U4TXIF          | U4RXIF                | U4EIF                   | SQI1IF                | PREIF                 | FCEIF                 | RTCCIF                 | SPI4TXIF               | SPI4RXIF               | SPI4EIF  | I2C3MIF                 | I2C3SIF                 | I2C3BIF                | 0000       |

| 00A0                        | IFS6                            | 31:16     | _                    | -             | _           | _               | _                     | -                       | _                     | _                     |                       | _                      | ADC7WIF                | _                      | —        | ADC4WIF                 | ADC3WIF                 |                        | 0000       |

|                             |                                 | 15:0      | ADC1WIF              | ADC0WIF       | ADC7EIF     | —               | _                     | ADC4EIF                 | ADC3EIF               | ADC2EIF               | ADC1EIF               | ADC0EIF                | -                      | ADCGRPIF               | —        | ADCURDYIF               |                         | ADCEOSIF               | _          |

| 00C0                        | IEC0                            | 31:16     | OC6IE                | IC6IE         | IC6EIE      | T6IE            | OC5IE                 | IC5IE                   | IC5EIE                | T5IE                  | INT4IE                | OC4IE                  | IC4IE                  | IC4EIE                 | T4IE     | INT3IE                  | OC3IE                   | IC3IE                  | 0000       |

|                             |                                 | 15:0      | IC3EIE               | T3IE          | INT2IE      | OC2IE           | IC2IE                 | IC2EIE                  | T2IE                  | INT1IE                | OC1IE                 | IC1IE                  | IC1EIE                 | T1IE                   | INTOIE   | CS1IE                   | CS0IE                   | CTIE                   | 0000       |

| 00D0                        | IEC1                            | 31:16     | ADCD4IE              | ADCD3IE       | ADCD2IE     | ADCD1IE         | ADCD0IE               | ADCFLTIE                | ADCDF6IE              | ADCDF5IE              | ADCDF4IE              | ADCDF3IE               | ADCDF2IE               | ADCDF1IE               | ADCDC6IE | ADCDC5IE                | ADCDC4IE                | ADCDC3IE               | -          |

|                             |                                 | 15:0      | ADCDC2IE             |               | ADCFIFOIE   | ADCIE           | OC9IE                 | IC9IE                   | IC9EIE                | T9IE                  | OC8IE                 | IC8IE                  | IC8EIE                 | T8IE                   | OC7IE    | IC7IE                   | IC7EIE                  | T7IE                   | 0000       |

| 00E0                        | IEC2 <sup>(5)</sup>             | 31:16     |                      |               | ADCD34IE    | ADCD33IE        | ADCD32IE              | ADCD31IE                | ADCD30IE              | ADCD29IE              | ADCD28IE              | ADCD27IE               | ADCD26IE               | ADCD25IE               | ADCD24IE | ADCD23IE                | ADCD22IE                | ADCD21IE               |            |

|                             |                                 |           | ADCD20IE             | ADCD19IE      | ADCD18IE    | ADCD17IE        | ADCD16IE              | ADCD15IE                | ADCD14IE              | ADCD13IE              | ADCD12IE              | ADCD11IE               | ADCD10IE               | ADCD9IE                | ADCD8IE  | ADCD7IE                 | ADCD6IE                 | ADCD5IE                | 0000       |

| Legei                       | nd: x =                         | unknow    | n value on R         | teset; — = ur | nimplemente | d, read as '0'  | . Reset values        | s are shown ir          | n hexadecima          | l.                    |                       |                        |                        |                        |          |                         |                         |                        |            |

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: Registers" for more information.

This bit or register is not available on 64-pin devices. 2:

3: This bit or register is not available on devices without a CAN module. This bit or register is not available on 100-pin devices.

4:

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. This bit or register is not available on devices without a Crypto module. 6: 7:

8: This bit or register is not available on 124-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31.24        |                   | NMIKEY<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10        |                   | —                 | —                 | —                 | —                 |                   | —                | —                |  |  |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   | —                 | —                 | MVEC              | —                 |                   | TPC<2:0>         |                  |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   | _                 |                   | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |  |  |  |  |

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-24 **NMIKEY<7:0>:** Non-Maskable Interrupt Key bits When the correct key (0x4E) is written, a software NMI will be generated. The status is indicated by the GNMI bit (RNMICON<19>).

#### bit 23-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for multi vectored mode

- 0 = Interrupt controller configured for single vectored mode

#### bit 11 Unimplemented: Read as '0'

- bit 10-8 **TPC<2:0>:** Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

## bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 **INT2EP:** External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| ess                         |                                 |               |        |       |          |       |          |       |      | Bit    | s      |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|----------|-------|----------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13    | 28/12 | 27/11    | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH2CPTR                        | 31:16         | _      |       | —        | _     | —        | _     | —    | —      | —      | _      |        | —      | _      | _      | _      |        | 000        |

| 1200                        | DUHZUFIK                        | 15:0          |        |       |          |       |          |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |        | 000        |

| 1000                        | DCH2DAT                         | 31:16         | _      | _     | _        | _     | _        | —     | _    | _      | _      | _      |        | _      |        |        | —      |        | 000        |

| 290                         | DCH2DAI                         | 15:0          |        |       |          |       |          |       |      | CHPDAT | <15:0> |        |        |        |        |        |        |        | 000        |

| 1240                        | DCH3CON                         | 31:16         |        |       |          | CHPIG | 6N<7:0>  |       |      |        | _      | _      | _      | _      | _      | _      | _      | _      | 000        |

| IZAU                        | DCH3CON                         | 15:0          | CHBUSY |       | CHPIGNEN | _     | CHPATLEN |       | _    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | l<1:0> | 000        |

| 2B0                         | DCH3ECON                        | 31:16         | —      | —     | —        | —     | —        | —     | —    | —      |        |        |        | CHAIR  |        |        |        |        | 00F        |

| 1200                        | DOINCEOUN                       | 15:0          |        |       |          |       | Q<7:0>   |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | —      | —      | _      | FFC        |

| 12C0                        | DCH3INT                         | 31:16         | —      | —     | —        | —     | —        | _     | —    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 000        |

|                             |                                 | 15:0          | —      | _     | —        | _     | —        |       | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 000        |

| 2D0                         | 2D0 DCH3SSA 31:16 CHSSA<31:0>   |               |        |       |          |       |          |       |      |        | 000    |        |        |        |        |        |        |        |            |

|                             |                                 | 15:0<br>31:16 |        |       |          |       |          |       |      |        |        |        |        |        |        |        |        |        | 000        |

| 12E0                        | DCH3DSA                         | 15:0          |        |       |          |       |          |       |      | CHDSA  | <31:0> |        |        |        |        |        |        |        | 000        |

|                             |                                 | 31:16         | _      | _     |          | _     |          | _     | _    | _      | _      | _      | _      | _      | _      | _      | _      | _      | 000        |

| 2F0                         | DCH3SSIZ                        | 15:0          |        |       |          |       |          |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |        | 000        |

|                             |                                 | 31:16         | _      | _     | —        | _     | —        | _     | —    | _      | —      | _      | _      | —      | _      | _      | —      | _      | 000        |

| 300                         | DCH3DSIZ                        | 15:0          | •      |       |          |       |          |       |      | CHDSIZ | <15:0> |        |        | •      |        |        |        |        | 000        |

| 1310                        | DCH3SPTR                        | 31:16         | —      | _     | —        | _     | —        | _     | —    | —      | _      | —      | _      | —      | _      | —      | —      | —      | 000        |

| 1010                        |                                 | 15:0          |        |       |          |       |          |       |      | CHSPTR | <15:0> |        |        |        |        |        |        |        | 000        |

| 320                         | DCH3DPTR                        | 31:16         | —      | _     | —        | _     | —        | _     | —    |        | —      | —      | —      | —      | —      | —      | —      | —      | 000        |

|                             |                                 | 15:0          |        |       |          |       |          |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |        | 000        |

| 330                         | DCH3CSIZ                        | 31:16<br>15:0 | —      |       | —        |       | —        |       | _    | CHCSIZ |        |        | _      | _      | _      | _      | _      | _      | 000        |

|                             |                                 | 31:16         | _      |       | _        |       | [        |       |      |        | <15:0> |        |        |        |        |        |        | _      | 000        |

| 1340                        | DCH3CPTR                        | 15:0          | _      | _     | _        | _     | _        | _     | _    | CHCPTR |        | _      | _      | _      | _      | _      | _      |        | 000        |

|                             |                                 | 31:16         | _      | _     |          | _     |          | _     | _    |        | _      | _      | _      | _      | _      | _      | _      | _      | 000        |

| 1350                        | DCH3DAT                         | 15:0          |        |       |          |       |          |       |      | CHPDAT | <15:0> |        |        |        |        |        |        |        | 000        |

|                             |                                 | 31:16         |        |       |          | CHPIG | N<7:0>   |       |      |        | _      |        | _      | _      | _      |        |        |        | 000        |

| 360                         | DCH4CON                         |               | CHBUSY | _     | CHPIGNEN |       | CHPATLEN | _     |      | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | l<1:0> | 000        |

| 070                         | DOLIAEOON                       | 31:16         | _      | _     | —        | _     | —        | _     | —    | —      |        |        |        | CHAIR  | Q<7:0> |        | •      |        | 00F        |

| 370                         | DCH4ECON                        | 15:0          |        |       |          | CHSIR | Q<7:0>   |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | —      | —      | _      | FF0        |

| 380                         | DCH4INT                         | 31:16         | —      | _     | —        | _     | —        | _     | _    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 000        |

| 1000                        | DOLIHINI                        | 15:0          | —      | _     | —        | _     | —        | _     | —    | -      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

## TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

### REGISTER 11-28: USBLPMR1: USB LINK POWER MANAGEMENT CONTROL REGISTER 1 (CONTINUED)

bit 16 LPMXMT: LPM Transition to the L1 State bit

## When in Device mode:

1 = USB module will transition to the L1 state upon the receipt of the next LPM transaction. LPMEN must be set to `0b11. Both LPMXMT and LPMEN must be set in the same cycle.

#### 0 = Maintain current state

When LPMXMT and LPMEN are set, the USB module can respond in the following ways:

- If no data is pending (all TX FIFOs are empty), the USB module will respond with an ACK. The bit will self clear and a software interrupt will be generated.

- If data is pending (data resides in at least one TX FIFO), the USB module will respond with a NYET. In this case, the bit will not self clear however a software interrupt will be generated.

#### When in Host mode:

- 1 = USB module will transmit an LPM transaction. This bit is self clearing, and will be immediately cleared upon receipt of any Token or three time-outs have occurred.

0 = Maintain current state

- bit 15-12 ENDPOINT<3:0>: LPM Token Packet Endpoint bits

- This is the endpoint in the token packet of the LPM transaction.

- bit 11-9 Unimplemented: Read as '0'

- bit 8 **RMTWAK:** Remote Wake-up Enable bit

This bit is applied on a temporary basis only and is only applied to the current suspend state.

- 1 = Remote wake-up is enabled

- 0 = Remote wake-up is disabled

- bit 7-4 HIRD<3:0>: Host Initiated Resume Duration bits

The minimum time the host will drive resume on the bus. The value in this register corresponds to an actual resume time of:

Resume Time = 50  $\mu$ s + HIRD \* 75  $\mu$ s. The resulting range is 50  $\mu$ s to 1200  $\mu$ s.

#### bit 3-0 LNKSTATE<3:0>: Link State bits

This value is provided by the host to the peripheral to indicate what state the peripheral must transition to after the receipt and acceptance of a LPM transaction. The only valid value for this register is '1' for Sleep State (L1). All other values are reserved.

# REGISTER 11-29: USBLPMR2: USB LINK POWER MANAGEMENT CONTROL REGISTER 2 (CONTINUED)

bit 0 LPMSTIF: LPM STALL Interrupt Flag bit

### When in Device mode:

- 1 = A LPM transaction was received and the USB Module responded with a STALL

- 0 = No Stall condition

#### When in Host mode:

- 1 = A LPM transaction was transmitted and the device responded with a STALL

- 0 = No Stall condition

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | TXDATA<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | TXDATA<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | TXDATA<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | TXDATA            | <7:0>             |                   |                  |                  |  |  |  |  |

## REGISTER 20-10: SQI1TXDATA: SQI TRANSMIT DATA BUFFER REGISTER

| L | _egend:          |                  |                          |                    |

|---|------------------|------------------|--------------------------|--------------------|

| F | R = Readable bit | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| - | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 TXDATA<31:0>: Transmit Command Data bits

Data is loaded into this register before being transmitted. Prior to the data transfer, the data in TXDATA is loaded into the shift register (SFDR).

Multiple writes to TXDATA can occur while a transfer is in progress. There can be a maximum of eight commands that can be queued.

### REGISTER 20-11: SQI1RXDATA: SQI RECEIVE DATA BUFFER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        | RXDATA<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22.10        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | RXDATA<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         | RXDATA<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          | RXDATA<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-0 RXDATA<31:0>: Receive Data Buffer bits

At the end of a data transfer, the data in the shift register is loaded into the RXDATA register. This register works like a FIFO. The depth of the receive buffer is eight words.

#### **UART Control Registers** 22.1

# TABLE 22-1: UART1 THROUGH UART6 REGISTER MAP

| ess                         |                            | â         |        |         |        |       |        |       |       | Bi          | ts          |         |       |          |          |       |        |       |            |

|-----------------------------|----------------------------|-----------|--------|---------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|----------|----------|-------|--------|-------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name           | Bit Range | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0  | All Resets |

|                             | U1MODE <sup>(1)</sup>      | 31:16     | _      | —       | _      | —     | —      | _     | _     | —           | _           | —       | —     | —        | —        | —     | _      | —     | 0000       |

| 2000                        | UTWODE                     | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 2010                        | U1STA <sup>(1)</sup>       | 31:16     | —      | —       | —      | —     | —      | —     | _     | ADM_EN      |             |         |       | ADDR     | <7:0>    |       |        |       | 0000       |

| 2010                        | 2010 01314.7               | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 2020                        | U1TXREG                    | 31:16     | _      | —       | —      | —     | —      | -     | —     | —           | _           | _       | _     | _        | _        | _     | —      | —     | 0000       |

| 2020                        | UTTAKLO                    | 15:0      | _      | _       | _      | _     | —      | _     | _     | TX8         |             |         |       | Transmit | Register |       |        |       | 0000       |

| 2030                        | U1RXREG                    | 31:16     | _      | _       | _      | _     | —      | _     | _     | _           | _           | -       | _     | _        | _        | _     | -      | _     | 0000       |

| 2030                        | UIKAREG                    | 15:0      | _      | —       | —      | —     | —      | -     | —     | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 2040                        | U1BRG <sup>(1)</sup>       | 31:16     | _      | _       | _      | _     | —      | _     | _     | _           | _           | -       | _     | _        | _        | _     | -      | _     | 0000       |

| 2040                        | UIDKG /                    | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |       |        |       | 0000       |

| 2200                        | 2200 U2MODE <sup>(1)</sup> | 31:16     | —      | —       | -      | -     | —      |       |       | —           | —           | -       |       |          |          |       |        | —     | 0000       |

| 2200                        | UZIVIODE ? /               | 15:0      | ON     | _       | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 2210                        | U2STA <sup>(1)</sup>       | 31:16     | —      | _       | _      |       | _      | -     |       | ADM_EN      |             |         |       | ADDR     | <7:0>    |       |        |       | 0000       |

| 2210                        | 0231A.                     | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 2220                        |                            | 31:16     | _      | _       | _      |       | _      | -     |       | _           | _           | _       |       | _        |          | _     |        | _     | 0000       |

| 2220                        | U2TXREG                    | 15:0      | —      | _       | _      |       | —      | _     |       | TX8         |             |         |       | Transmit | Register |       |        |       | 0000       |

| 2230                        | U2RXREG                    | 31:16     | _      | _       | -      | -     | _      | -     |       | _           | _           | _       |       | _        |          | _     |        | _     | 0000       |

| 2230                        | UZRAREG                    | 15:0      | —      | _       | _      |       | —      | _     |       | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 2240                        | U2BRG <sup>(1)</sup>       | 31:16     | —      | —       | —      | —     | —      | —     | —     | —           | —           | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 2240                        | OZDINO                     | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |       |        |       | 0000       |

| 2400                        | U3MODE <sup>(1)</sup>      | 31:16     | —      | —       | —      | —     | —      | —     |       | —           | —           | —       | —     | —        | —        | —     |        | —     | 0000       |

| 2400                        | OSIVIODE                   | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 2410                        | U3STA <sup>(1)</sup>       | 31:16     | —      | —       | —      | —     | —      | —     | —     | ADM_EN      |             |         |       | ADDR     | <7:0>    |       |        | -     | 0000       |

| 2410                        | 03017                      | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 2420                        | <b>U3TXREG</b>             | 31:16     | —      | —       | —      | —     | —      | —     | —     | —           | —           | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 2420                        | OUTAILEO                   | 15:0      | —      | —       | —      | —     | —      | —     | —     | TX8         |             |         |       | Transmit | Register |       |        | -     | 0000       |

| 2430                        | U3RXREG                    | 31:16     | _      | —       | —      | _     | —      | _     | _     | —           | _           | —       | _     | _        | _        | _     | —      |       | 0000       |

| 200                         | CONVILED                   | 15:0      | _      | —       | _      | —     | —      | —     | _     | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 2440                        | U3BRG <sup>(1)</sup>       | 31:16     | —      | _       |        | _     | _      | _     |       | _           | _           | _       | _     | —        | _        | _     | _      |       | 0000       |

| 2440                        | CODICO /                   | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |       |        |       | 0000       |

| Legen                       |                            |           |        |         |        |       |        |       |       |             |             |         |       |          |          |       |        |       |            |

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more informa-Note 1: tion.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 31.24        | —                 |                   |                   |                   | —                       |                   | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 23.10        | —                 |                   |                   |                   | —                       |                   | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 15.6         | —                 |                   |                   |                   |                         | FILHIT<4:0>       |                  |                  |

| 7.0          | U-0               | R-1               | R-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   |                   | CODE<6:0> <sup>(1</sup> | )                 |                  |                  |

# REGISTER 29-4: CiVEC: CAN INTERRUPT CODE REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-13 Unimplemented: Read as '0'

| bit 12-8 | FILHIT<4:0>: Filter Hit Number bit                                                        |

|----------|-------------------------------------------------------------------------------------------|

|          | 11111 = Filter 31                                                                         |

|          | 11110 = Filter 30                                                                         |

|          | •                                                                                         |

|          | •                                                                                         |

|          | •                                                                                         |

|          | 00001 = Filter 1                                                                          |

|          | 00000 = Filter 0                                                                          |

| bit 7    | Unimplemented: Read as '0'                                                                |

| bit 6-0  | ICODE<6:0>: Interrupt Flag Code bits <sup>(1)</sup>                                       |

|          | 1001000-1111111 = Reserved                                                                |

|          | 1001000 = Invalid message received (IVRIF)                                                |

|          | 1000111 = CAN module mode change (MODIF)                                                  |

|          | 1000110 = CAN timestamp timer (CTMRIF)                                                    |

|          | 1000101 = Bus bandwidth error (SERRIF)                                                    |

|          | 1000100 = Address error interrupt (SERRIF)                                                |

|          | 1000011 = Receive FIFO overflow interrupt (RBOVIF)<br>1000010 = Wake-up interrupt (WAKIF) |

|          | 1000001 = Error Interrupt (CERRIF)                                                        |

|          | 1000000 = No interrupt                                                                    |

|          | 0100000-0111111 = Reserved                                                                |

|          | 0011111 = FIFO31 Interrupt (CiFSTAT<31> set)                                              |

|          | 0011110 = FIFO30 Interrupt (CiFSTAT<30> set)                                              |

|          | •                                                                                         |

|          | •                                                                                         |

|          | •                                                                                         |

|          | 0000001 = FIFO1 Interrupt (CiFSTAT<1> set)                                                |

|          | 0000000 = FIFO0 Interrupt (CiFSTAT<0> set)                                                |

|          |                                                                                           |

|          |                                                                                           |