Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

|                           |                                                                                  |

| Product Status            | Obsolete                                                                         |

| Core Processor            | MIPS32® M-Class                                                                  |

| Core Size                 | 32-Bit Single-Core                                                               |

| peed                      | 180MHz                                                                           |

| Connectivity              | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals               | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| lumber of I/O             | 97                                                                               |

| Program Memory Size       | 1MB (1M x 8)                                                                     |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AAM Size                  | 512K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Oata Converters           | A/D 48x12b                                                                       |

| Oscillator Type           | Internal                                                                         |

| perating Temperature      | -40°C ~ 125°C                                                                    |

| Nounting Type             | Surface Mount                                                                    |

| ackage / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                 |

| Supplier Device Package   | 124-VTLA (9x9)                                                                   |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efh124-e-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-6: PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS

|          | Pin Number             |                 |                 |                          |             |                |                                   |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|          |                        |                 |                 |                          | PO          | RTA            |                                   |

| RA0      | _                      | 17              | A11             | 22                       | I/O         | ST             | PORTA is a bidirectional I/O port |

| RA1      | _                      | 38              | B21             | 56                       | I/O         | ST             |                                   |

| RA2      | _                      | 59              | A41             | 85                       | I/O         | ST             |                                   |

| RA3      | _                      | 60              | B34             | 86                       | I/O         | ST             |                                   |

| RA4      | _                      | 61              | A42             | 87                       | I/O         | ST             |                                   |

| RA5      | _                      | 2               | B1              | 2                        | I/O         | ST             |                                   |

| RA6      | _                      | 89              | A61             | 129                      | I/O         | ST             |                                   |

| RA7      | _                      | 90              | B51             | 130                      | I/O         | ST             |                                   |

| RA9      | _                      | 28              | B15             | 39                       | I/O         | ST             |                                   |

| RA10     | _                      | 29              | A20             | 40                       | I/O         | ST             |                                   |

| RA14     | _                      | 66              | B37             | 95                       | I/O         | ST             |                                   |

| RA15     | _                      | 67              | A45             | 96                       | I/O         | ST             |                                   |

|          | •                      | •               | •               |                          | PO          | RTB            |                                   |

| RB0      | 16                     | 25              | A18             | 36                       | I/O         | ST             | PORTB is a bidirectional I/O port |

| RB1      | 15                     | 24              | A17             | 35                       | I/O         | ST             |                                   |

| RB2      | 14                     | 23              | A16             | 34                       | I/O         | ST             |                                   |

| RB3      | 13                     | 22              | A14             | 31                       | I/O         | ST             |                                   |

| RB4      | 12                     | 21              | A13             | 26                       | I/O         | ST             |                                   |

| RB5      | 11                     | 20              | B11             | 25                       | I/O         | ST             |                                   |

| RB6      | 17                     | 26              | B14             | 37                       | I/O         | ST             |                                   |

| RB7      | 18                     | 27              | A19             | 38                       | I/O         | ST             |                                   |

| RB8      | 21                     | 32              | B18             | 47                       | I/O         | ST             |                                   |

| RB9      | 22                     | 33              | A23             | 48                       | I/O         | ST             |                                   |

| RB10     | 23                     | 34              | B19             | 49                       | I/O         | ST             |                                   |

| RB11     | 24                     | 35              | A24             | 50                       | I/O         | ST             |                                   |

| RB12     | 27                     | 41              | A27             | 59                       | I/O         | ST             |                                   |

| RB13     | 28                     | 42              | B23             | 60                       | I/O         | ST             | ]                                 |

| RB14     | 29                     | 43              | A28             | 61                       | I/O         | ST             |                                   |

| RB15     | 30                     | 44              | B24             | 62                       | I/O         | ST             |                                   |

|          |                        |                 |                 |                          | PO          | RTC            |                                   |

| RC1      | _                      | 6               | В3              | 6                        | I/O         | ST             | PORTC is a bidirectional I/O port |

| RC2      | _                      | 7               | A6              | 11                       | I/O         | ST             |                                   |

| RC3      | _                      | 8               | B5              | 12                       | I/O         | ST             | ]                                 |

| RC4      | _                      | 9               | A7              | 13                       | I/O         | ST             | ]                                 |

| RC12     | 31                     | 49              | B28             | 71                       | I/O         | ST             | ]                                 |

| RC13     | 47                     | 72              | B41             | 105                      | I/O         | ST             | ]                                 |

| RC14     | 48                     | 73              | A49             | 106                      | I/O         | ST             | 1                                 |

| RC15     | 32                     | 50              | A33             | 72                       | I/O         | ST             | 1                                 |

|          | CMOC C                 | MOC some        |                 |                          |             | A I            | Analog input D. Dower             |

**Legend:** CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input

O = Output

PPS = Peripheral Pin Select

P = Power I = Input

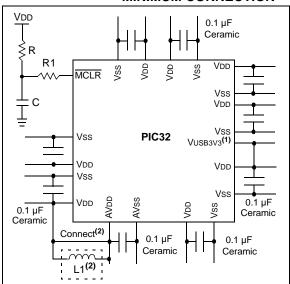

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

Note 1: If the USB module is not used, this pin must be connected to Vss.

2: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than  $1\Omega$  and the inductor capacity greater than 10 mA.

Where:

$$f=\frac{FCNV}{2} \qquad \text{(i.e., ADC conversion rate/2)}$$

$$f=\frac{1}{(2\pi\sqrt{LC})}$$

$$L=\left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

#### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F. This capacitor should be located as close to the device as possible.

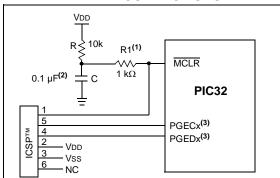

# 2.3 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- · Device programming and debugging

Pulling The MCLR pin low generates either a device Reset or a POR, depending on the setting of the SMCLR bit (DEVCFG0<15>). Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

- Note 1:  $\frac{470\Omega \leq R1 \leq 1 k\Omega \text{ will limit any current flowing into}}{\overline{MCLR}} \text{ from the external capacitor C, in the event of } \overline{MCLR} \text{ pin breakdown, due to Electrostatic Discharge}$  (ESD) or Electrical Overstress (EOS). Ensure that the  $\overline{MCLR} \text{ pin VIH and VIL specifications are met without interfering with the Debug/Programmer tools.}$

- 2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

- No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

REGISTER 4-6: SBTxECLRS: SYSTEM BUS TARGET 'x' SINGLE ERROR CLEAR REGISTER ('x' = 0-13)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 |                   | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 |                   |                   | _                 |                  | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | -                 | _                 | -                 |                   | _                 |                  | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | CLEAR            |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 31-1 Unimplemented: Read as '0'

bit 0 CLEAR: Clear Single Error on Read bit

A single error as reported via SBTxELOG1 and SBTxELOG2 is cleared by a read of this register.

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

REGISTER 4-7: SBTxECLRM: SYSTEM BUS TARGET 'x' MULTIPLE ERROR CLEAR REGISTER ('x' = 0-13)

|              | ,                 | $\mathbf{x} = \mathbf{v} \cdot \mathbf{v}$ |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|--------------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.04        | U-0               | U-0                                        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                                          | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0                                        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                                          | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0                                        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                                          | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0                                        | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 7:0          | _                 | _                                          | _                 | _                 | _                 | _                 | _                | CLEAR            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 31-1 Unimplemented: Read as '0'

bit 0 CLEAR: Clear Multiple Errors on Read bit

Multiple errors as reported via SBTxELOG1 and SBTxELOG2 is cleared by a read of this register.

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

| ٦ | TABLE 7-3: | INTERRUPT REGISTER MAP (CONTINUED |

|---|------------|-----------------------------------|

|   | S          |                                   |

| ress<br>()                  |                                 | Φ         |       |       |       | `     |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

| 0504                        | OFF017                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0564                        | OFFU17                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF018                          | 31:16     | -     | _     | _     | _     |       |       | _    | _          | -    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0366                        | OFFUIO                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0590                        | OFF019                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | -    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0360                        | OFFUIS                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF020                          | 31:16     | _     | _     | _     |       | 1     | 1     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0590                        | OFF020                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0504                        | OFF021                          | 31:16     | -     | _     | _     | _     |       |       | _    | _          | -    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0594                        | OFFUZI                          | 15:0      |       |       | _     |       |       |       | _    | VOFF<15:1> |      | _    | _    | _    |      |      |       | _      | 0000       |

| OE OO                       | OFF022                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | -    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0596                        | OFFUZZ                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF023                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0590                        | OFF023                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 05.40                       | OFF024                          | 31:16     | -     | _     | _     | _     |       |       | _    | _          | -    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| USAU                        | OFFU24                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 05.44                       | OFF025                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | -    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| U5A4                        | OFF025                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0540                        | OFF026                          | 31:16     | _     | _     | _     | -     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| OACU                        | OFF026                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 05.4.0                      | OFF027                          | 31:16     | -     | _     | _     | _     |       |       | _    | _          | -    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| USAC                        | OFFU21                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| OEDO                        | OFF028                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | -    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0580                        | OFF028                          | 15:0      |       |       | •     |       |       |       |      | VOFF<15:1> |      |      |      |      | -    | •    | •     | _      | 0000       |

| OED 4                       | 055000                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0564                        | OFF029                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| OEDO                        | OFF030                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0588                        | OFF030                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | 055004                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 05BC                        | OFF031                          | 15:0      |       |       | •     |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

Point Unit (EF) Family

- 3: This bit or register is not available on devices without a CAN module.

- This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

- 6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

- 7: This bit or register is not available on devices without a Crypto module.

- This bit or register is not available on 124-pin devices.

# REGISTER 11-11: USBIENCSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 1-7) (CONTINUED)

#### bit 15-8 RXINTERV<7:0>: Endpoint RX Polling Interval/NAK Limit bits

For Interrupt and Isochronous transfers, this field defines the polling interval for the endpoint. For Bulk endpoints, this field sets the number of frames/microframes after which the endpoint should time out on receiving a stream of NAK responses.

The following table describes the valid values and meaning for this field:

| Transfer Type | Speed        | Valid Values (m) | Interpretation                                                                                                |

|---------------|--------------|------------------|---------------------------------------------------------------------------------------------------------------|

| Interrupt     | Low/Full     | 0x01 to 0xFF     | Polling interval is 'm' frames.                                                                               |

|               | High         | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames.                                                                |

| Isochronous   | Full or High | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames/microframes.                                                    |

| Bulk          | Full or High | 0x02 to 0x10     | NAK limit is 2 <sup>(m-1)</sup> frames/microframes. A value of '0' or '1' disables the NAK time-out function. |

#### bit 7-6 SPEED<1:0>: RX Endpoint Operating Speed Control bits

- 11 = Low-Speed

- 10 = Full-Speed

- 01 = Hi-Speed

- 00 = Reserved

#### bit 5-4 PROTOCOL<1:0>: RX Endpoint Protocol Control bits

- 11 = Interrupt

- 10 = Bulk

- 01 = Isochronous

- 00 = Control

#### bit 3-0 **TEP<3:0>:** RX Target Endpoint Number bits

This value is the endpoint number contained in the TX endpoint descriptor returned to the USB module during device enumeration.

#### REGISTER 11-17: USBEOFRST: USB END-OF-FRAME/SOFT RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | -                 | 1                 | NRSTX            | NRST             |  |  |  |

| 23:16        | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-0             | R/W-1            | R/W-0            |  |  |  |

| 23.10        | LSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-1             | R/W-1            | R/W-1            |  |  |  |

| 13.6         |                   |                   |                   | FSEO              | F<7:0>            |                   |                  |                  |  |  |  |

| 7.0          | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R.W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | HSEO              | F<7:0>            |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25 NRSTX: Reset of XCLK Domain bit

1 = Reset the XCLK domain, which is clock recovered from the received data by the PHY

0 = Normal operation

bit 24 NRST: Reset of CLK Domain bit

1 = Reset the CLK domain, which is clock recovered from the peripheral bus

0 = Normal operation

bit 23-16 LSEOF<7:0>: Low-Speed EOF bits

These bits set the Low-Speed transaction in units of  $1.067 \mu s$  (default setting is  $121.6 \mu s$ ) prior to the EOF to stop new transactions from beginning.

bit 15-8 FSEOF<7:0>: Full-Speed EOF bits

These bits set the Full-Speed transaction in units of 533.3  $\mu$ s (default setting is 63.46  $\mu$ s) prior to the EOF to stop new transactions from beginning.

bit 7-0 **HSEOF<7:0>:** Hi-Speed EOF bits

These bits set the Hi-Speed transaction in units of 133.3 µs (default setting is 17.07µs) prior to the EOF to stop new transactions from beginning.

#### REGISTER 20-2: SQI1XCON2: SQI XIP CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | -                 | _                 | -                 | _                |                  |

| 22:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | _                 | DEVSE             | EL<1:0>           | MODEBY           | TES<1:0>         |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | MODECO            | DE<7:0>           |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-12 Unimplemented: Read as '0'

bit 11-10 **DEVSEL<1:0>:** Device Select bits

11 = Reserved

10 = Reserved

01 = Device 1 is selected

00 = Device 0 is selected

bit 9-8 MODEBYTES<1:0>: Mode Byte Cycle Enable bits

11 = Three cycles

10 = Two cycles

01 = One cycle

00 = Zero cycles

bit 7-0 MODECODE<7:0>: Mode Code Value bits

These bits contain the 8-bit code value for the mode bits.

#### REGISTER 20-9: SQI1INTSTAT: SQI INTERRUPT STATUS REGISTER (CONTINUED)

- bit 2 **TXTHRIF:** Transmit Buffer Threshold Interrupt Flag bit

- 1 = Transmit buffer has more than TXINTTHR words of space available

- 0 = Transmit buffer has less than TXINTTHR words of space available

- bit 1 TXFULLIF: Transmit Buffer Full Interrupt Flag bit

- 1 = The transmit buffer is full

- 0 = The transmit buffer is not full

- bit 0 TXEMPTYIF: Transmit Buffer Empty Interrupt Flag bit

- 1 = The transmit buffer is empty

- 0 = The transmit buffer has content

- **Note 1:** In Boot/XIP mode, the POR value of the receive buffer threshold is zero. Therefore, this bit will be set to a '1', immediately after a POR until a read request on the System Bus is received.

**Note:** The bits in the register are cleared by writing a '1' to the corresponding bit position.

REGISTER 20-14: SQI1BDCON: SQI BUFFER DESCRIPTOR CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | -                 | _                 | -                 | 1                 |                   |                  | -                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | -                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | -                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 | -                 | START             | POLLEN           | DMAEN            |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-3 Unimplemented: Read as '0'

bit 2 START: Buffer Descriptor Processor Start bit

1 = Start the buffer descriptor processor0 = Disable the buffer descriptor processor

bit 1 POLLEN: Buffer Descriptor Poll Enable bit

1 = BDP poll is enabled

0 = BDP poll is not enabled

bit 0 **DMAEN:** DMA Enable bit

1 = DMA is enabled

0 = DMA is disabled

#### REGISTER 20-15: SQI1BDCURADD: SQI BUFFER DESCRIPTOR CURRENT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24        |                   |                   |                   | BDCURRADI         | DR<31:24>         |                   |                  |                  |  |  |  |

| 22.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16        |                   | BDCURRADDR<23:16> |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | BDCURRADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BDCURRAD          | DDR<7:0>          |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 BDCURRADDR<31:0>: Current Buffer Descriptor Address bits

These bits contain the address of the current descriptor being processed by the Buffer Descriptor Processor.

#### PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED) REGISTER 23-1: bit 7-6

```

CSF<1:0>: Chip Select Function bits(1)

```

- 11 = Reserved

- 10 = PMCS1 and PMCS2 function as Chip Select

- 01 = PMCS2 functions as Chip Select and PMCS1 functions as address bit 14

- 00 = PMCS1 and PMCS2 function as address bit 14 and address bit 15

- ALP: Address Latch Polarity bit(1) bit 5

- 1 = Active-high (PMALL and PMALH)

- $0 = Active-low (\overline{PMALL} \text{ and } \overline{PMALH})$

- CS2P: Chip Select 2 Polarity bit(1) bit 4

- 1 = Active-high (PMCS2)

- $0 = Active-low (\overline{PMCS2})$

- bit 3 CS1P: Chip Select 1 Polarity bit(1)

- 1 = Active-high (PMCS1)

- $0 = Active-low (\overline{PMCS1})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

#### For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

#### For Master mode 1 (MODE<1:0> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

#### For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- $0 = \text{Read Strobe active-low } (\overline{PMRD})$

#### For Master mode 1 (MODE<1:0> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- 0 = Read/write strobe active-low (PMRD/PMWR)

Note 1: These bits have no effect when their corresponding pins are used as address lines.

#### REGISTER 23-9: PMRADDR: PARALLEL PORT READ ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|------------------------|------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04:04        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                      | _                      | _                 | _                 | _                 | -                 | _                | _                |  |

| 00.40        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                        |                        | _                 | _                 | _                 | 1                 | _                | _                |  |

|              | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | RCS2 <sup>(1)</sup>    | RCS1 <sup>(3)</sup>    |                   |                   |                   | .40.0.            |                  |                  |  |

|              | RADDR15 <sup>(2)</sup> | RADDR14 <sup>(4)</sup> | RADDR<13:8>       |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                        | _                      |                   | RADDR<            | 7:0>              |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 RCS2: Chip Select 2 bit<sup>(1)</sup>

1 = Chip Select 2 is active

0 = Chip Select 2 is inactive (RADDR15 function is selected)

bit 15 RADDR<15>: Target Address bit 15<sup>(2)</sup>

bit 14 RCS1: Chip Select 1 bit<sup>(3)</sup>

1 = Chip Select 1 is active

0 = Chip Select 1 is inactive (RADDR14 function is selected)

bit 14 RADDR<14>: Target Address bit 14<sup>(4)</sup>

bit 13-0 RADDR<13:0>: Address bits

**Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

**2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

3: When the CSF<1:0> bits (PMCON<7:6>) = 10.

**4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

#### REGISTER 29-20: CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' ('n' = 0-31)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-----------------------|-----------------------|---------------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0                   | U-0                   | U-0                       | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                     | _                     | _                         | _                 | _                 | 1                | _                |  |  |

| 23:16        | U-0               | U-0                   | U-0                   | R/W-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | _                 | _                     | _                     | FSIZE<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |

| 15:8         | U-0               | S/HC-0                | S/HC-0                | R/W-0                     | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.6         | _                 | FRESET                | UINC                  | DONLY <sup>(1)</sup>      | _                 | _                 | _                | _                |  |  |

| 7:0          | R/W-0             | R-0                   | R-0                   | R-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | TXEN              | TXABAT <sup>(2)</sup> | TXLARB <sup>(3)</sup> | TXERR <sup>(3)</sup>      | TXREQ             | RTREN             | TXPR             | <1:0>            |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-21 Unimplemented: Read as '0'

bit 20-16 FSIZE<4:0>: FIFO Size bits(1)

11111 = FIFO is 32 messages deep

•

•

.

00010 = FIFO is 3 messages deep

00001 = FIFO is 2 messages deep

00000 = FIFO is 1 message deep

bit 15 **Unimplemented:** Read as '0'

bit 14 FRESET: FIFO Reset bits

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset. After setting, the user application should poll whether this bit is clear before taking any action

0 = No effect

bit 13 UINC: Increment Head/Tail bit

$\overline{\text{TXEN}} = 1$ : (FIFO configured as a Transmit FIFO)

When this bit is set, the FIFO head will increment by a single message

TXEN = 0: (FIFO configured as a Receive FIFO)

When this bit is set, the FIFO tail will increment by a single message

bit 12 **DONLY:** Store Message Data Only bit<sup>(1)</sup>

TXEN = 1: (FIFO configured as a Transmit FIFO)

This bit is not used and has no effect.

TXEN = 0: (FIFO configured as a Receive FIFO)

1 = Only data bytes will be stored in the FIFO

0 = Full message is stored, including identifier

bit 11-8 **Unimplemented:** Read as '0'

bit 7 TXEN: TX/RX Buffer Selection bit

1 = FIFO is a Transmit FIFO

0 = FIFO is a Receive FIFO

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

#### REGISTER 30-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1 (CONTINUED)

bit 7 AUTOFC: Automatic Flow Control bit

1 = Automatic Flow Control enabled

0 = Automatic Flow Control disabled

Setting this bit will enable automatic Flow Control. If set, the full and empty watermarks are used to automatically enable and disable the Flow Control, respectively. When the number of received buffers BUFCNT (ETHSTAT<16:23>) rises to the full watermark, Flow Control is automatically enabled. When the BUFCNT falls to the empty watermark, Flow Control is automatically disabled.

This bit is only used for Flow Control operations and affects both TX and RX operations.

bit 6-5 **Unimplemented:** Read as '0'

bit 4 MANFC: Manual Flow Control bit

1 = Manual Flow Control is enabled

0 = Manual Flow Control is disabled

Setting this bit will enable manual Flow Control. If set, the Flow Control logic will send a PAUSE frame using the PAUSE timer value in the PTV register. It will then resend a PAUSE frame every 128 \* PTV<15:0>/2 TX clock cycles until the bit is cleared.

**Note:** For 10 Mbps operation, TX clock runs at 2.5 MHz. For 100 Mbps operation, TX clock runs at

25 MHz.

When this bit is cleared, the Flow Control logic will automatically send a PAUSE frame with a 0x0000 PAUSE timer value to disable Flow Control.

This bit is only used for Flow Control operations and affects both TX and RX operations.

bit 3-1 Unimplemented: Read as '0'

bit 0 BUFCDEC: Descriptor Buffer Count Decrement bit

The BUFCDEC bit is a write-1 bit that reads as '0'. When written with a '1', the Descriptor Buffer Counter, BUFCNT, will decrement by one. If BUFCNT is incremented by the RX logic at the same time that this bit is written, the BUFCNT value will remain unchanged. Writing a '0' will have no effect.

This bit is only used for RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

#### REGISTER 30-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 |                   | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 |                   | _                 | _                 | _                | _                |

| 15:8         | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         | HTEN              | MPEN              |                   | NOTPM             |                   | PMMODE            | <3:0>            |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | CRCERREN          | CRCOKEN           | RUNTERREN         | RUNTEN            | UCEN              | NOTMEEN           | MCEN             | BCEN             |

-n = Value at POR

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 HTEN: Enable Hash Table Filtering bit

1 = Enable Hash Table Filtering

0 = Disable Hash Table Filtering

bit 14 MPEN: Magic Packet™ Enable bit

1 = Enable Magic Packet Filtering

0 = Disable Magic Packet Filtering

bit 13 Unimplemented: Read as '0'

bit 12 NOTPM: Pattern Match Inversion bit

1 = The Pattern Match Checksum must not match for a successful Pattern Match to occur

0 = The Pattern Match Checksum must match for a successful Pattern Match to occur

This bit determines whether Pattern Match Checksum must match in order for a successful Pattern Match to occur.

- bit 11-8 PMMODE<3:0>: Pattern Match Mode bits

- 1001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Packet = Magic Packet)(1,3)

- 1000 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Hash Table Filter match)(1,1)

- 0111 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)(1)

- 0110 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)<sup>(1)</sup>

- 0101 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)<sup>(1)</sup>

- 0100 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)(1)

- 0011 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)(1)

- 0010 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)<sup>(1)</sup>

- 0001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches)<sup>(1)</sup>

- 0000 = Pattern Match is disabled; pattern match is always unsuccessful

- **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

- Note 1: This register is only used for RX operations.

- The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

REGISTER 30-23: EMAC1CFG1: ETHERNET CONTROLLER MAC CONFIGURATION 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   |                   |                   |                   | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   | -                 | 1                 | -                 | _                | _                |

|              | R/W-1             | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | SOFT<br>RESET     | SIM<br>RESET      | _                 | _                 | RESET<br>RMCS     | RESET<br>RFUN     | RESET<br>TMCS    | RESET<br>TFUN    |

|              | U-0               | U-0               | U-0               | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-1            |

| 7:0          | _                 | _                 | _                 | LOOPBACK          | TX<br>PAUSE       | RX<br>PAUSE       | PASSALL          | RX<br>ENABLE     |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SOFTRESET: Soft Reset bit

Setting this bit will put the MACMII in reset. Its default value is '1'.

bit 14 SIMRESET: Simulation Reset bit

Setting this bit will cause a reset to the random number generator within the Transmit Function.

bit 13-12 Unimplemented: Read as '0'

bit 11 RESETRMCS: Reset MCS/RX bit

Setting this bit will put the MAC Control Sub-layer/Receive domain logic in reset.

bit 10 RESETRFUN: Reset RX Function bit

Setting this bit will put the MAC Receive function logic in reset.

bit 9 **RESETTMCS**: Reset MCS/TX bit

Setting this bit will put the MAC Control Sub-layer/TX domain logic in reset.

bit 8 RESETTFUN: Reset TX Function bit

Setting this bit will put the MAC Transmit function logic in reset.

bit 7-5 Unimplemented: Read as '0'

bit 4 LOOPBACK: MAC Loopback mode bit

1 = MAC Transmit interface is loop backed to the MAC Receive interface

0 = MAC normal operation

bit 3 TXPAUSE: MAC TX Flow Control bit

1 = PAUSE Flow Control frames are allowed to be transmitted

0 = PAUSE Flow Control frames are blocked

bit 2 RXPAUSE: MAC RX Flow Control bit

1 = The MAC acts upon received PAUSE Flow Control frames

0 = Received PAUSE Flow Control frames are ignored

bit 1 PASSALL: MAC Pass all Receive Frames bit

1 = The MAC will accept all frames regardless of type (Normal vs. Control)

0 = The received Control frames are ignored

bit 0 RXENABLE: MAC Receive Enable bit

1 = Enable the MAC receiving of frames

0 = Disable the MAC receiving of frames

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

REGISTER 32-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 |                   |                   | _                | _                |

| 22:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | _                 |                   | -                 | -                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | CVROE             | CVRR              | CVRSS             |                   | CVR<              | <3:0>            |                  |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Comparator Voltage Reference On bit

1 = Module is enabled

Setting this bit does not affect other bits in the register.

0 = Module is disabled and does not consume current.

Clearing this bit does not affect the other bits in the register.

bit 14-7 Unimplemented: Read as '0'

bit 6 CVROE: CVREFOUT Enable bit

1 = Voltage level is output on CVREFOUT pin

0 = Voltage level is disconnected from CVREFOUT pin

bit 5 **CVRR:** CVREF Range Selection bit

1 = 0 to 0.67 CVRSRC, with CVRSRC/24 step size

0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size

bit 4 CVRSS: CVREF Source Selection bit

1 = Comparator voltage reference source, CVRSRC = (VREF+) - (VREF-)

0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS

bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR < 3:0 > \le 15$  bits

When CVRR = 1:

$CVREF = (CVR < 3:0 > /24) \bullet (CVRSRC)$

When CVRR = 0:

$CVREF = 1/4 \bullet (CVRSRC) + (CVR<3:0>/32) \bullet (CVRSRC)$

TABLE 37-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHAR                           | ACTERISTICS            |                        | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |                  |                                                 |  |  |  |  |

|-----------------------------------|------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------|--|--|--|--|

| Param.<br>No.                     | Typical <sup>(2)</sup> | Maximum <sup>(5)</sup> | Units                                                                                                                                                                  | Units Conditions |                                                 |  |  |  |  |

| Power-Down Current (IPD) (Note 1) |                        |                        |                                                                                                                                                                        |                  |                                                 |  |  |  |  |

| DC40k                             | 0.7                    | 7                      | mA                                                                                                                                                                     | -40°C            |                                                 |  |  |  |  |

| DC40I                             | 1.5                    | 7                      | mA                                                                                                                                                                     | +25°C            | Base Power-Down Current                         |  |  |  |  |

| DC40n                             | 7                      | 20                     | mA                                                                                                                                                                     | +85°C            |                                                 |  |  |  |  |

| Module Di                         | fferential Curre       | ent                    |                                                                                                                                                                        |                  |                                                 |  |  |  |  |

| DC41e                             | 15                     | 50                     | μΑ                                                                                                                                                                     | 3.6V             | Watchdog Timer Current: ΔIWDT (Note 3)          |  |  |  |  |

| DC42e                             | 25                     | 50                     | μΑ                                                                                                                                                                     | 3.6V             | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |  |

| DC43d                             | 3                      | 3.8                    | mA                                                                                                                                                                     | 3.6V             | ADC: ΔIADC (Notes 3, 4)                         |  |  |  |  |

| DC44                              | 15                     | 50                     | μΑ                                                                                                                                                                     | 3.6V             | Deadman Timer Current: ΔIDMT (Note 3)           |  |  |  |  |

**Note 1:** The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBMD = 1), VUSB3V3 is connected to VSS

- CPU is in Sleep mode

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), and the associated PMD bit is set. All clocks are disabled ON bit (PBxDIV<15>) = 0 (x ≠ 1,7)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD

- · RTCC and JTAG are disabled

- Voltage regulator is in Stand-by mode (VREGS = 0)

- 2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- **4:** Voltage regulator is operational (VREGS = 1).

- 5: Data in the "Maximum" column is at 3.3V, +85°C at specified operating frequency, unless otherwise stated. Parameters are for design guidance only and are not tested.

**TABLE 37-18: SYSTEM TIMING REQUIREMENTS**

| AC CHARACTERISTICS |                          |                           | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |         |         |       |                                                  |  |

|--------------------|--------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|--------------------------------------------------|--|

| Param.<br>No.      | Symbol   Characteristics |                           | Minimum                                                                                                                                                                | Typical | Maximum | Units | Conditions                                       |  |

| OS51               | Fsys                     | System Frequency          | DC                                                                                                                                                                     | _       | 200     | MHz   | USB module disabled                              |  |

|                    |                          |                           | 60                                                                                                                                                                     | _       | 200     | MHz   | USB module enabled                               |  |

| OS55a              | FРВ                      | Peripheral Bus Frequency  | DC                                                                                                                                                                     | _       | 100     | MHz   | For PBCLKx, 'x' $\neq$ 4, 7                      |  |

| OS55b              |                          |                           | DC                                                                                                                                                                     | _       | 200     | MHz   | For PBCLK4, PBCLK7                               |  |

| OS56               | FREF                     | Reference Clock Frequency | _                                                                                                                                                                      | _       | 50      | MHz   | For REFCLKI1, 3, 4<br>and REFCLKO1, 3, 4<br>pins |  |

#### **TABLE 37-19: PLL CLOCK TIMING SPECIFICATIONS**

| AC CHARACTERISTICS              |       |                                                             | Standard<br>(unless of<br>Operating | herwise | ture -40°C | ≤ TA ≤ <b>+</b> | 85°C for | · Industrial<br>or Extended |

|---------------------------------|-------|-------------------------------------------------------------|-------------------------------------|---------|------------|-----------------|----------|-----------------------------|

| Param. No. Symbol Characteristi |       |                                                             | cs <sup>(1)</sup>                   | Min.    | Typical    | Max.            | Units    | Conditions                  |

| OS50                            | FIN   | PLL Input Frequency Range                                   |                                     | 5       | _          | 64              | MHz      | ECPLL, HSPLL, FRCPLL modes  |

| OS52                            | TLOCK | PLL Start-up Time (L                                        | ock Time)                           | _       | _          | 100             | μs       | _                           |

| OS53                            | DCLK  | CLKO Stability <sup>(2)</sup> (Period Jitter or Cumulative) |                                     | -0.25   | _          | +0.25           | %        | Measured over 100 ms period |

| OS54                            | FVco  | PLL Vco Frequency Range                                     |                                     | 350     | _          | 700             | MHz      | _                           |

| OS54a                           | FPLL  | PLL Output Frequen                                          | cy Range                            | 10      | _          | 200             | MHz      | _                           |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{PBCLK2}{CommunicationClock}}}$$

For example, if PBCLK2 = 100 MHz and SPI bit rate = 50 MHz, the effective jitter is as follows:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{100}{50}}} = \frac{D_{CLK}}{1.41}$$

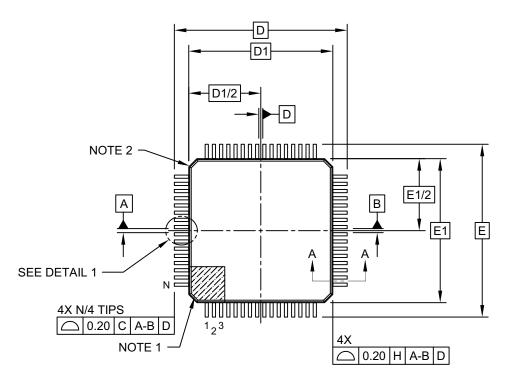

### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2

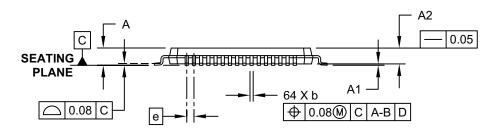

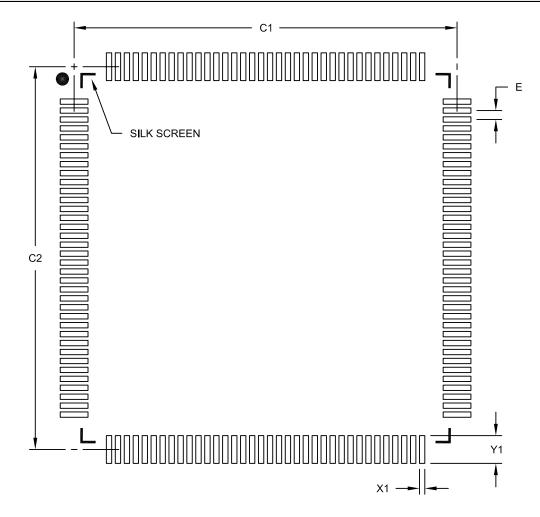

144-Lead Plastic Low Profile Quad Flatpack (PL) - 20x20x1.40 mm Body [LQFP] 2.00 mm Footprint

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                           | MILLIMETERS |     |          |      |

|---------------------------|-------------|-----|----------|------|

| Dimension                 | MIN         | NOM | MAX      |      |

| Contact Pitch             | E           |     | 0.50 BSC |      |

| Contact Pad Spacing       | C1          |     | 21.40    |      |

| Contact Pad Spacing       | C2          |     | 21.40    |      |

| Contact Pad Width (X144)  | X1          |     |          | 0.30 |

| Contact Pad Length (X144) | Y1          |     |          | 1.55 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2044B