#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 97                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 512K × 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                 |

| Supplier Device Package    | 124-VTLA (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efh124-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.1 Architecture Overview

The MIPS32 M-Class Microprocessor core in PIC32MZ EF family devices contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution unit

- General Purpose Register (GPR)

- Multiply/Divide Unit (MDU)

- System control coprocessor (CP0)

- Floating Point Unit (FPU)

- Memory Management Unit (MMU)

- Instruction/Data cache controllers

- Power Management

- Instructions and data caches

- microMIPS support

- Enhanced JTAG (EJTAG) controller

#### 3.1.1 EXECUTION UNIT

The processor core execution unit implements a load/ store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. Seven additional register file shadow sets (containing thirty-two registers) are added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Trap condition comparator

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing arithmetic and bitwise logical operations

- Shifter and store aligner

- DSP ALU and logic block for performing DSP instructions, such as arithmetic/shift/compare operations

#### 3.1.2 MULTIPLY/DIVIDE UNIT (MDU)

The processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations, and DSP ASE multiply instructions. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x32 booth recoded multiplier, four pairs of result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x32) represents the *rs* operand. The second number ('32' of 32x32) represents the *rt* operand.

The MDU supports execution of one multiply or multiply-accumulate operation every clock cycle.

Divide operations are implemented with a simple 1-bitper-clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation has completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the processor core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Opcode                         | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|--------------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU,        | 16 bits                                        | 5       | 1           |

| MSUB/MSUBU (HI/LO destination) | 32 bits                                        | 5       | 1           |

| MUL (GPR destination)          | 16 bits                                        | 5       | 1           |

|                                | 32 bits                                        | 5       | 1           |

| DIV/DIVU                       | 8 bits                                         | 12/14   | 12/14       |

|                                | 16 bits                                        | 20/22   | 20/22       |

|                                | 24 bits                                        | 28/30   | 28/30       |

|                                | 32 bits                                        | 36/38   | 36/38       |

# TABLE 3-1:MIPS32<sup>®</sup> M-CLASS MICROPROCESSOR CORE HIGH-PERFORMANCE INTEGER<br/>MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

#### REGISTER 5-1: NVMCON: FLASH PROGRAMMING CONTROL REGISTER (CONTINUED)

bit 6 **BFSWAP:** Boot Flash Bank Alias Swap Control bit

This bit is only writable when WREN = 0 and the unlock sequence has been performed.

- 1 = Boot Flash Bank 2 is mapped to the lower boot alias and boot Flash Bank 1 is mapped to the upper boot alias

- 0 = Boot Flash Bank 1 is mapped to the lower boot alias and boot Flash Bank 2 is mapped to the upper boot alias

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **NVMOP<3:0>:** NVM Operation bits

These bits are only writable when WREN = 0.

1111 = Reserved

1000 = Reserved

- 0111 = Program erase operation: erase all of program Flash memory (all pages must be unprotected, PWP<23:0> = 0x000000)

- 0110 = Upper program Flash memory erase operation: erases only the upper mapped region of program Flash (all pages in that region must be unprotected)

- 0101 = Lower program Flash memory erase operation: erases only the lower mapped region of program Flash (all pages in that region must be unprotected)

- 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected

- 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected

- 0010 = Quad Word (128-bit) program operation: programs the 128-bit Flash word selected by NVMADDR, if it is not write-protected

- 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<sup>(2)</sup> 0000 = No operation

- Note 1: These bits are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

- 2: This operation results in a "no operation" (NOP) when the Dynamic Flash ECC Configuration bits = 00 (FECCCON<1:0> (DVCFG0<9:8>)), which enables ECC at all times. For all other FECCCON<1:0> bit settings, this command will execute, but will not write the ECC bits for the word and can cause DED errors if dynamic Flash ECC is enabled (FECCCON<1:0> = 01). Refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) for information regarding ECC and Flash programming.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 31:24        | _                 | -                 | _                 | -                 | _                 | _                   | —                | —                |

| 00.40        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 |                   | _                   | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                   | _                | —                |

|              | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 |                   |                   | TUN<              | 5:0> <sup>(1)</sup> |                  |                  |

#### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

#### Legend:

| · J · · ·                         |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized nor tested.

| Note: | Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced |

|-------|-----------------------------------------------------------------------------------------------------|

|       | PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.                               |

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | —                 | _                 | —                 | _                 | _                | -                |

| 00.10     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | —                 |                   | —                 | _                 |                  |                  |

| 45.0      | R/W-y             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | ON <sup>(1)</sup> | —                 | —                 | _                 | —                 | _                 | _                | -                |

| 7:0       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0       |                   | _                 |                   | _                 | _                 | _                 |                  | _                |

#### REGISTER 15-1: DMTCON: DEADMAN TIMER CONTROL REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Deadman Timer Module Enable bit<sup>(1)</sup>

1 = Deadman Timer module is enabled

0 = Deadman Timer module is disabled

The reset value of this bit is determined by the setting of the FDMTEN bit (DEVCFG1<3>).

bit 13-0 Unimplemented: Read as '0'

**Note 1:** This bit only has control when FDMTEN (DEVCFG1<3>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | _                 | _                 | _                 |                   | _                | _                |

| 00:40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 |                   |                   | _                 |                   |                  |                  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | STEP1<7:0>        |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|           |                   |                   | _                 | _                 | _                 | _                 |                  | —                |

#### REGISTER 15-2: DMTPRECLR: DEADMAN TIMER PRECLEAR REGISTER

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

| bit 15-8 | STEP1<7:0>: Preclear Enable bits                                                        |

|----------|-----------------------------------------------------------------------------------------|

|          | 01000000 = Enables the Deadman Timer Preclear (Step 1)                                  |

|          | All other write patterns = Set BAD1 flag.                                               |

|          | These bits are cleared when a DMT reset event occurs. STEP1<7:0> is also cleared if the |

|          | STEP2<7:0> bits are loaded with the correct value in the correct sequence.              |

| bit 7-0  | Unimplemented: Read as '0'                                                              |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 | -                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | _                 | -                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 |                   | _                 | EDGEDETECT        | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   |                  |                  |

#### REGISTER 12-3: CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A - K)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Change Notice (CN) Control ON bit

1 = CN is enabled

0 = CN is disabled

#### bit 14-12 Unimplemented: Read as '0'

- bit 11 EDGEDETECT: Change Notification Style bit

- 1 = Edge Style. Detect edge transitions (CNFx used for CN Event).

- 0 = Mismatch Style. Detect change from last PORTx read (CNSTATx used for CN Event).

- bit 10-0 Unimplemented: Read as '0'

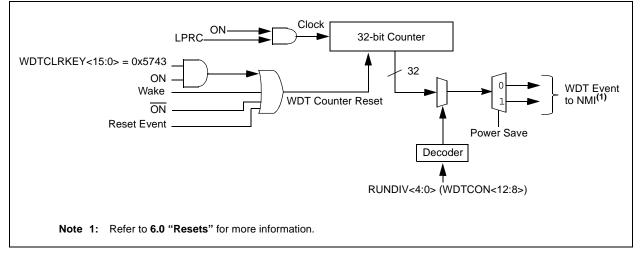

#### 16.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). When enabled, the Watchdog Timer (WDT) operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

#### FIGURE 16-1: WATCHDOG TIMER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |  |  |

|--------------|------------------------|--------------------|-------------------|-----------------------|-------------------|-------------------|------------------|-----------------------|--|--|

| 04.04        | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN                 | FRMSYPW           | FRMCNT<2:0>       |                  |                       |  |  |

| 00.40        | R/W-0                  | U-0                | U-0               | U-0                   | U-0               | U-0               | R/W-0            | R/W-0                 |  |  |

| 23:16        | MCLKSEL <sup>(1)</sup> | _                  |                   | —                     | _                 | _                 | SPIFE            | ENHBUF <sup>(1)</sup> |  |  |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 15:8         | ON                     | _                  | SIDL              | DISSDO <sup>(4)</sup> | MODE32            | MODE16            | SMP              | CKE <sup>(2)</sup>    |  |  |

| 7.0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 7:0          | SSEN                   | CKP <sup>(3)</sup> | MSTEN             | DISSDI <sup>(4)</sup> | STXISEL<1:0>      |                   | SRXISEL<1:0>     |                       |  |  |

#### REGISTER 19-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled ( $\overline{SSx}$  pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support is enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(1)</sup>

- 1 = REFCLKO1 is used by the Baud Rate Generator

- 0 = PBCLK2 is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** This bit can only be written when the ON bit = 0. Refer to **Section 37.0** "**Electrical Characteristics**" for maximum clock frequency requirements.

- 2: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: This bit present for legacy compatibility and is superseded by PPS functionality on these devices (see Section 12.4 "Peripheral Pin Select (PPS)" for more information).

#### REGISTER 20-9: SQI1INTSTAT: SQI INTERRUPT STATUS REGISTER (CONTINUED)

- bit 2 TXTHRIF: Transmit Buffer Threshold Interrupt Flag bit

Transmit buffer has more than TXINTTHR words of space available

Transmit buffer has less than TXINTTHR words of space available

bit 1 TXFULLIF: Transmit Buffer Full Interrupt Flag bit

The transmit buffer is full

The transmit buffer is not full

bit 0 TXEMPTYIF: Transmit Buffer Empty Interrupt Flag bit

The transmit buffer is empty

- 0 = The transmit buffer has content

- **Note 1:** In Boot/XIP mode, the POR value of the receive buffer threshold is zero. Therefore, this bit will be set to a '1', immediately after a POR until a read request on the System Bus is received.

Note: The bits in the register are cleared by writing a '1' to the corresponding bit position.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 |                   | _                 |                   |                   | —                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                 |                   | —                 |                  | _                |

| 45.0         | R-0, HS, HC       | R-0, HS, HC       | R/C-0, HS, HC     | U-0               | U-0               | R/C-0, HS         | R-0, HS, HC      | R-0, HS, HC      |

| 15:8         | ACKSTAT           | TRSTAT            | ACKTIM            | —                 |                   | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS, SC     | R/C-0, HS, SC     | R-0, HS, HC       | R/C-0, HS, HC     | R/C-0, HS, HC     | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

## REGISTER 21-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Legend:           | HS = Hardware Set | HC = Hardware Cleared SC = Software Cleared |                   |  |  |  |  |

|-------------------|-------------------|---------------------------------------------|-------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'          |                   |  |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared                        | C = Clearable bit |  |  |  |  |

#### bit 21 16 Linin nnla tod. De 24 <u>'</u>∩'

| bit 31-16 | Unimplemented: Read as 10 <sup>°</sup>                                                                                                                               |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                          |

|           | 1 = NACK received from slave                                                                                                                                         |

|           | 0 = ACK received from slave                                                                                                                                          |

|           | Hardware set or clear at end of slave Acknowledge.                                                                                                                   |

| bit 14    | <b>TRSTAT:</b> Transmit Status bit (when operating as $I^2C$ master, applicable to master transmit operation)<br>1 = Master transmit is in progress (8 bits + ACK)   |

|           | 0 = Master transmit is not in progress                                                                                                                               |

|           | Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.                                                                        |

| bit 13    | <b>ACKTIM:</b> Acknowledge Time Status bit (Valid in I <sup>2</sup> C Slave mode only)                                                                               |

|           | $1 = I^2C$ bus is in an Acknowledge sequence, set on the eight falling edge of SCL clock<br>0 = Not an Acknowledge sequence, cleared on 9th rising edge of SCL clock |

| bit 12-11 | Unimplemented: Read as '0'                                                                                                                                           |

| bit 10    | BCL: Master Bus Collision Detect bit                                                                                                                                 |

|           | 1 = A bus collision has been detected during a master operation                                                                                                      |

|           | 0 = No collision                                                                                                                                                     |

|           | Hardware set at detection of bus collision.                                                                                                                          |

| bit 9     | GCSTAT: General Call Status bit                                                                                                                                      |

|           | 1 = General call address was received                                                                                                                                |

|           | 0 = General call address was not received                                                                                                                            |

|           | Hardware set when address matches general call address. Hardware clear at Stop detection.                                                                            |

| bit 8     | ADD10: 10-bit Address Status bit                                                                                                                                     |

|           | 1 = 10-bit address was matched                                                                                                                                       |

|           | 0 = 10-bit address was not matched                                                                                                                                   |

|           | Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.                                                                       |

| bit 7     | IWCOL: Write Collision Detect bit                                                                                                                                    |

|           | 1 = An attempt to write the I2CxTRN register failed because the $I^2$ C module is busy                                                                               |

|           | <ul> <li>0 = No collision</li> <li>Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).</li> </ul>                                       |

| L:1.0     |                                                                                                                                                                      |

| bit 6     | I2COV: Receive Overflow Flag bit                                                                                                                                     |

|           | <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> </ul>                                   |

|           | Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                        |

|           |                                                                                                                                                                      |

|           |                                                                                                                                                                      |

|           |                                                                                                                                                                      |

#### **UART Control Registers** 22.1

### TABLE 22-1: UART1 THROUGH UART6 REGISTER MAP

| ess                         |                                                                                                         | â         |        |         |        |       |        |       |       | Bi          | ts          |         |       |          |          |       |        |       |            |

|-----------------------------|---------------------------------------------------------------------------------------------------------|-----------|--------|---------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|----------|----------|-------|--------|-------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name                                                                                        | Bit Range | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0  | All Resets |

|                             | U1MODE <sup>(1)</sup>                                                                                   | 31:16     | _      | —       | _      | —     | —      | _     | _     | —           | _           | —       | —     | —        | —        | —     | _      | —     | 0000       |

| 2000                        | UTWODE                                                                                                  | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 2010                        | U1STA <sup>(1)</sup>                                                                                    | 31:16     | —      | —       | —      | —     | —      | —     | _     | ADM_EN      |             |         |       | ADDR     | <7:0>    |       |        |       | 0000       |

| 2010                        | UISTA                                                                                                   | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 2020                        | U1TXREG                                                                                                 | 31:16     | _      | —       | —      | —     | —      | -     | —     | —           | _           | _       | _     | _        | _        | _     | —      | —     | 0000       |

| 2020                        | UTTAKLO                                                                                                 | 15:0      | _      | _       | _      | _     | _      | _     | _     | TX8         |             |         |       | Transmit | Register |       |        |       | 0000       |

| 2030                        | U1RXREG                                                                                                 | 31:16     | _      | _       | _      | _     | _      | _     | _     | _           | _           | -       | _     | _        | _        | _     | -      | _     | 0000       |

| 2030                        | UIKAREG                                                                                                 | 15:0      | _      | —       | —      | —     | —      | -     | —     | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 2040                        | U1BRG <sup>(1)</sup>                                                                                    | 31:16     | _      | _       | _      | _     | _      | _     | _     | _           | _           | -       | _     | _        | _        | _     | -      | _     | 0000       |

| 2040                        | UIDKG /                                                                                                 | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |       |        |       | 0000       |

| 2200                        | U2MODE <sup>(1)</sup>                                                                                   | 31:16     | —      | —       | -      | -     | —      |       |       | —           | —           | -       |       |          |          |       |        | —     | 0000       |

| 2200                        | UZIVIODE ? /                                                                                            | 15:0      | ON     | _       | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 2210                        | U2STA <sup>(1)</sup>                                                                                    | 31:16     | —      | _       | _      |       | _      | -     |       | ADM_EN      | ADDR<7:0>   |         |       |          |          |       | 0000   |       |            |

| 2210                        | 0231A.                                                                                                  | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 2220                        | U2TXREG                                                                                                 | 31:16     | —      | _       | _      |       | _      | -     |       | _           | _           | _       |       | _        |          | _     |        | _     | 0000       |

| 2220                        | UZTARLO                                                                                                 | 15:0      | —      | _       | _      |       | —      | _     |       | TX8         |             |         |       | Transmit | Register |       |        |       | 0000       |

| 2230                        | U2RXREG                                                                                                 | 31:16     | _      | _       | -      | -     | _      | -     |       | _           | _           | _       |       | _        |          | _     |        | _     | 0000       |

| 2230                        | UZRAREG                                                                                                 | 15:0      | —      | _       | _      |       | —      | _     |       | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 2240                        | U2BRG <sup>(1)</sup>                                                                                    | 31:16     | —      | —       | —      | —     | —      | —     | —     | —           | —           | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 2240                        | OZDINO                                                                                                  | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |       |        |       | 0000       |

| 2400                        | U3MODE <sup>(1)</sup>                                                                                   | 31:16     | —      | —       | —      | —     | —      | —     |       | —           | —           | —       | —     | —        | —        | —     |        | —     | 0000       |

| 2400                        | OSINODE                                                                                                 | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 2410                        | U3STA <sup>(1)</sup>                                                                                    | 31:16     | —      | —       | —      | —     | —      | —     | —     | ADM_EN      |             |         |       | ADDR     | <7:0>    |       |        | -     | 0000       |

| 2410                        | 03017                                                                                                   | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 2420                        | <b>U3TXREG</b>                                                                                          | 31:16     | —      | —       | —      | —     | —      | —     | —     | —           | —           | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 2420                        | OUTAILEO                                                                                                | 15:0      | —      | —       | —      | —     | —      | —     | —     | TX8         |             |         |       | Transmit | Register |       |        | -     | 0000       |

| 2430                        | U3RXREG                                                                                                 | 31:16     | _      | —       | —      | _     | —      | _     | _     | —           | _           | —       | _     | _        | _        | _     | —      |       | 0000       |

| 200                         | CONVILED                                                                                                | 15:0      | _      | —       | _      | —     | —      | —     | _     | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 2440                        | U3BRG <sup>(1)</sup>                                                                                    | 31:16     | —      | _       |        | _     | _      | _     |       | _           | _           | _       | _     | —        | _        | _     | _      |       | 0000       |

| 2440                        | CODICO /                                                                                                | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |       |        |       | 0000       |

| Legen                       | end: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |           |        |         |        |       |        |       |       |             |             |         |       |          |          |       |        |       |            |

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more informa-Note 1: tion.

#### 26.2 Crypto Engine Buffer Descriptors

Host software creates a linked list of buffer descriptors and the hardware updates them. Table 26-3 provides a list of the Crypto Engine buffer descriptors, followed by format descriptions of each buffer descriptor (see Figure 26-2 through Figure 26-9).

| Name (see No | ote 1) | Bit<br>31/2315/7  | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|--------|-------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| BD_CTRL      | 31:24  | DESC_EN           | —                  | (                 | CRY_MODE<2:0      | >                 | —                 | _                | _                |  |  |  |  |

|              | 23:16  | _                 | SA_FETCH_EN        | -                 | _                 | LAST_BD           | LIFM              | PKT_INT_EN       | CBD_INT_EN       |  |  |  |  |

|              | 15:8   |                   |                    |                   | BD_BUFLEN         | <15:8>            | •                 |                  |                  |  |  |  |  |

|              | 7:0    |                   |                    |                   | BD_BUFLEN         | N<7:0>            |                   |                  |                  |  |  |  |  |

| BD_SA_ADDR   | 31:24  |                   |                    |                   | BD_SAADDR         | <31:24>           |                   |                  |                  |  |  |  |  |

|              | 23:16  |                   |                    |                   | BD_SAADDR         | <23:16>           |                   |                  |                  |  |  |  |  |

|              | 15:8   |                   |                    |                   | BD_SAADDR         | <15:8>            |                   |                  |                  |  |  |  |  |

|              | 7:0    |                   |                    |                   | BD_SAADR          | <7:0>             |                   |                  |                  |  |  |  |  |

| BD_SCRADDR   | 31:24  |                   |                    |                   | BD_SRCADDF        | <31:24>           |                   |                  |                  |  |  |  |  |

|              | 23:16  |                   | BD_SRCADDR<23:16>  |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | 15:8   |                   | BD_SRCADDR<15:8>   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | 7:0    |                   | BD_SRCADDR<7:0>    |                   |                   |                   |                   |                  |                  |  |  |  |  |

| BD_DSTADDR   | 31:24  |                   | BD_DSTADDR<31:24>  |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | 23:16  | BD_DSTADDR<23:16> |                    |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | 15:8   | BD_DSTADDR<15:8>  |                    |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | 7:0    | BD_DSTADDR<7:0>   |                    |                   |                   |                   |                   |                  |                  |  |  |  |  |

| BD_NXTPTR    | 31:24  | BD_NXTADDR<31:24> |                    |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | 23:16  | BD_NXTADDR<23:16> |                    |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | 15:8   | BD_NXTADDR<15:8>  |                    |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | 7:0    |                   |                    |                   | BD_NXTADD         | R<7:0>            |                   |                  |                  |  |  |  |  |

| BD_UPDPTR    | 31:24  |                   |                    |                   | BD_UPDADDF        | R<31:24>          |                   |                  |                  |  |  |  |  |

|              | 23:16  |                   |                    |                   | BD_UPDADDF        | R<23:16>          |                   |                  |                  |  |  |  |  |

|              | 15:8   |                   |                    |                   | BD_UPDADDI        | R<15:8>           |                   |                  |                  |  |  |  |  |

|              | 7:0    |                   |                    | BD_UPDADDR<7:0>   |                   |                   |                   |                  |                  |  |  |  |  |

| BD_MSG_LEN   | 31:24  |                   |                    |                   | MSG_LENGTH        | 1<31:24>          |                   |                  |                  |  |  |  |  |

|              | 23:16  |                   |                    |                   | MSG_LENGTH        | 1<23:16>          |                   |                  |                  |  |  |  |  |

|              | 15:8   |                   |                    |                   | MSG_LENGT         | H<15:8>           |                   |                  |                  |  |  |  |  |

|              | 7:0    |                   |                    |                   | MSG_LENGT         | H<7:0>            |                   |                  |                  |  |  |  |  |

| BD_ENC_OFF   | 31:24  |                   | ENCR_OFFSET<31:24> |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | 23:16  |                   |                    |                   | ENCR_OFFSE        | T<23:16>          |                   |                  |                  |  |  |  |  |

|              | 15:8   |                   |                    |                   | ENCR_OFFSE        | T<15:8>           |                   |                  |                  |  |  |  |  |

|              | 7:0    |                   |                    |                   | ENCR_OFFSI        | ET<7:0>           |                   |                  |                  |  |  |  |  |

#### TABLE 26-3: CRYPTO ENGINE BUFFER DESCRIPTORS

**Note** 1: The buffer descriptor must be allocated in memory on a 64-bit boundary.

### 27.1 RNG Control Registers

#### TABLE 27-2: RANDOM NUMBER GENERATOR (RNG) REGISTER MAP

| ess                         |                  |           |       |            |       |       |          |       |      | Bits   | ;     |      |      |        |         |      |      |      |            |

|-----------------------------|------------------|-----------|-------|------------|-------|-------|----------|-------|------|--------|-------|------|------|--------|---------|------|------|------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15 | 30/14      | 29/13 | 28/12 | 27/11    | 26/10 | 25/9 | 24/8   | 23/7  | 22/6 | 21/5 | 20/4   | 19/3    | 18/2 | 17/1 | 16/0 | All Resets |

| 6000                        | RNGVER           | 31:16     |       |            |       |       |          |       |      | ID<15  | :0>   |      |      |        |         |      |      |      | xxxx       |

| 0000                        | RNOVER           | 15:0      |       |            |       | VERS  | ION<7:0> |       |      |        |       |      |      | REVISI | ON<7:0> |      |      |      | xxxx       |

| 6004                        | RNGCON           | 31:16     | _     |            | _     |       | _        | _     | —    | _      |       | —    | —    | —      | —       |      | —    | —    | 0000       |

| 0004                        | KNOCON           | 15:0      | _     |            |       |       |          |       |      |        |       |      |      |        |         |      |      |      |            |

| 6008                        | RNGPOLY1         | 31:16     |       |            |       |       |          |       |      |        | 1.0   |      |      |        |         |      |      |      | FFFF       |

| 0000                        | RINGFOLTT        | 15:0      |       | POLY<31:0> |       |       |          |       |      |        |       |      |      |        |         |      |      |      |            |

| 600C                        | RNGPOLY2         | 31:16     |       |            |       |       |          |       |      | POLY<3 | 1.0   |      |      |        |         |      |      |      | FFFF       |

| 0000                        | KNGFOLI Z        | 15:0      |       |            |       |       |          |       |      | FULIKS | 01.02 |      |      |        |         |      |      |      | 0000       |

| 6010                        | RNGNUMGEN1       | 31:16     |       |            |       |       |          |       |      | RNG<3  | 1.0>  |      |      |        |         |      |      |      | FFFF       |

| 0010                        | RINGINOWIGEINT   | 15:0      |       |            |       |       |          |       |      | KNOC3  | 1.0>  |      |      |        |         |      |      |      | FFFF       |

| 6014                        | RNGNUMGEN2       | 31:16     |       |            |       |       |          |       |      | RNG<3  | 1.0.  |      |      |        |         |      |      |      | FFFF       |

| 0014                        | RINGINUWIGEINZ   | 15:0      |       |            |       |       |          |       |      | RNG<3  | 1.0>  |      |      |        |         |      |      |      | FFFF       |

| 6018                        | RNGSEED1         | 31:16     |       |            |       |       |          |       |      |        | 1.0.  |      |      |        |         |      |      |      | 0000       |

| 6018                        | RINGSEEDT        | 15:0      |       | SEED<31:0> |       |       |          |       |      |        |       |      |      |        |         |      |      |      |            |

| 6010                        | RNGSEED2         | 31:16     |       | SEED<31:0> |       |       |          |       |      |        |       |      |      |        |         |      |      |      |            |

| 601C                        | RINGSEED2        | 15:0      |       |            |       |       |          |       |      | SEED<3 | 01.0> |      |      |        |         |      |      |      | 0000       |

| 6020                        | RNGCNT           | 31:16     | —     | —          | —     | —     | —        | —     | —    | —      | —     | —    | —    | —      | —       | —    | —    | —    | 0000       |

| 6020                        | RINGCINI         | 15:0      | _     | <u> </u>   |       |       |          |       |      |        |       |      |      |        |         |      |      |      |            |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 28-1: ADC REGISTER MAP (CONTINUED)

| es                          |                          |               |       |                                  |       |       |       |       |      | Bit   | s     |      |      |      |      |      |      |      | s          |

|-----------------------------|--------------------------|---------------|-------|----------------------------------|-------|-------|-------|-------|------|-------|-------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF84_#) | Register<br>Name         | Bit Range     | 31/15 | 30/14                            | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7  | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

|                             | ADCDATA32 <sup>(1)</sup> | 31:16         |       |                                  |       |       |       |       |      | DATA< | 1:16> |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                                  |       |       |       |       |      | DATA< | 15:0> |      |      |      |      |      |      |      | 0000       |

| B284                        | ADCDATA33 <sup>(1)</sup> | 31:16         |       |                                  |       |       |       |       |      | DATA< | 1:16> |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       | DATA<15:0> 0000                  |       |       |       |       |      |       |       |      |      |      |      |      |      |      |            |

| B288                        | ADCDATA34 <sup>(1)</sup> | 31:16         |       | DATA<31:16> 0000                 |       |       |       |       |      |       |       |      |      |      |      |      |      |      |            |

|                             |                          | 15:0          |       | DATA<15:0> 0000                  |       |       |       |       |      |       |       |      |      |      |      |      |      |      |            |

| B28C                        | ADCDATA35 <sup>(2)</sup> | 31:16         |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

| B290                        | ADCDATA36 <sup>(2)</sup> | 31:16         |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

|                             | (2)                      | 15:0          |       | DATA<15:0> 0000                  |       |       |       |       |      |       |       |      |      |      |      |      |      |      |            |

| B294                        | ADCDATA37 <sup>(2)</sup> | 31:16         |       | DATA<31:16> 0000                 |       |       |       |       |      |       |       |      |      |      |      |      |      |      |            |

|                             | (2)                      | 15:0          |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

| B298                        | ADCDATA38 <sup>(2)</sup> | 31:16         |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

|                             | (2)                      | 15:0          |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

| B29C                        | ADCDATA39 <sup>(2)</sup> |               |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

|                             |                          | 15:0          |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

| B2A0                        | ADCDATA40 <sup>(2)</sup> | 31:16         |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

| DO A A                      | ADCDATA41(2)             | 15:0          |       |                                  |       |       |       |       |      | DATA< |       |      |      |      |      |      |      |      | 0000       |

| BZA4                        | ADCDATA41-               | 31:16         |       | DATA<31:16> 0000                 |       |       |       |       |      |       |       |      |      |      |      |      |      |      |            |

| DOAD                        | ADCDATA42 <sup>(2)</sup> | 15:0<br>31:16 |       | DATA<15:0> 0000                  |       |       |       |       |      |       |       |      |      |      |      |      |      |      |            |

| DZA0                        | ADCDATA42                | 15:0          |       |                                  |       |       |       |       |      |       |       |      | 0000 |      |      |      |      |      |            |

| BOAC                        | ADCDATA43                | 31:16         |       |                                  |       |       |       |       |      |       |       |      |      | 0000 |      |      |      |      |            |

| DZAC                        | -DCDA1A43                | 15:0          |       | DATA<15:0> 0000                  |       |       |       |       |      |       |       |      | _    |      |      |      |      |      |            |

| B2B0                        | ADCDATA44                | 31:16         |       |                                  |       |       |       |       |      |       |       |      |      |      |      |      |      |      | 0000       |

| 0200                        |                          | 15:0          |       | DATA<31:16> 0000 DATA<15:0> 0000 |       |       |       |       |      |       |       |      |      |      |      |      |      |      |            |

1: 2: 3:

This bit or register is not available on 64-pin devices. This bit or register is not available on 64-pin and 100-pin devices. Before enabling the ADC, the user application must initialize the ADC calibration values by copying them from the factory-programmed DEVADCx Flash registers into the corresponding ADCxCFG registers.

Note

| REGISTER  | 29-10: CIFLTCON0: CAN FILTER CONTROL REGISTER 0 (CONTINUED)                                             |

|-----------|---------------------------------------------------------------------------------------------------------|

| bit 15    | FLTEN1: Filter 1 Enable bit                                                                             |

|           | 1 = Filter is enabled                                                                                   |

|           | 0 = Filter is disabled                                                                                  |

| bit 14-13 | MSEL1<1:0>: Filter 1 Mask Select bits                                                                   |

|           | 11 = Acceptance Mask 3 selected                                                                         |

|           | 10 = Acceptance Mask 2 selected                                                                         |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                      |

| bit 12-8  | FSEL1<4:0>: FIFO Selection bits                                                                         |

| 51(12.0   | 11111 = Message matching filter is stored in FIFO buffer 31                                             |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                             |

|           | •                                                                                                       |

|           | •                                                                                                       |

|           | •                                                                                                       |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                              |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                              |

| bit 7     | FLTEN0: Filter 0 Enable bit                                                                             |

|           | 1 = Filter is enabled                                                                                   |

| 1:0 5     | 0 = Filter is disabled                                                                                  |

| bit 6-5   | MSEL0<1:0>: Filter 0 Mask Select bits                                                                   |

|           | <ul><li>11 = Acceptance Mask 3 selected</li><li>10 = Acceptance Mask 2 selected</li></ul>               |

|           | 01 = Acceptance Mask 2 selected                                                                         |

|           | 00 = Acceptance Mask 0 selected                                                                         |

| bit 4-0   | FSEL0<4:0>: FIFO Selection bits                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                             |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                             |

|           | •                                                                                                       |

|           | •                                                                                                       |

|           | •                                                                                                       |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                              |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                              |

| Note: T   | he bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.   |

| 1010.     | The bits in this register out only be mounded in the corresponding filter enable (I LI LINII) bit is 0. |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0       |

|--------------|-------------------|-------------------|-----------------------|------------------------|-----------------------|-------------------|-----------------------|------------------------|

| 04-04        | U-0               | U-0               | U-0                   | U-0                    | U-0                   | U-0               | R/W-0                 | R/W-0                  |

| 31:24        | —                 | —                 |                       |                        | —                     | —                 | DMAPRI <sup>(1)</sup> | CPUPRI <sup>(1)</sup>  |

| 00.40        | U-0               | U-0               | U-0                   | U-0                    | U-0                   | U-0               | R/W-0                 | R/W-0                  |

| 23:16        | —                 | —                 | —                     | —                      | —                     | —                 | ICACLK <sup>(1)</sup> | OCACLK <sup>(1)</sup>  |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | R/W-0                 | U-0               | U-0                   | R/W-0                  |

| 15:8         | —                 | —                 | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> | PGLOCK <sup>(1)</sup> | _                 | _                     | USBSSEN <sup>(1)</sup> |

| 7.0          | R/W-0             | U-0               | R/W-1                 | R/W-1                  | R/W-1                 | R/W-0             | U-0                   | R/W-1                  |

| 7:0          | IOANCPEN          | —                 | ECCC                  | ON<1:0>                | JTAGEN                | TROEN             | _                     | TDOEN                  |

#### REGISTER 34-7: CFGCON: CONFIGURATION CONTROL REGISTER

#### Legend:

| U                 |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-26 Unimplemented: Read as '0'

| DIT 31-26 | Unimplemented: Read as 10 <sup>°</sup>                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 25    | DMAPRI: DMA Read and DMA Write Arbitration Priority to SRAM bit <sup>(1)</sup>                                                                                                                   |

|           | 1 = DMA gets High Priority access to SRAM                                                                                                                                                        |

|           | 0 = DMA uses Least Recently Serviced Arbitration (same as other initiators)                                                                                                                      |

| bit 24    | <b>CPUPRI:</b> CPU Arbitration Priority to SRAM When Servicing an Interrupt bit <sup>(1)</sup>                                                                                                   |

|           | 1 = CPU gets High Priority access to SRAM                                                                                                                                                        |

|           | 0 = CPU uses Least Recently Serviced Arbitration (same as other initiators)                                                                                                                      |

| bit 23-18 | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 17    | ICACLK: Input Capture Alternate Clock Selection bit <sup>(1)</sup>                                                                                                                               |

|           | <ul> <li>1 = Input Capture modules use an alternative Timer pair as their timebase clock</li> <li>0 = All Input Capture modules use Timer2/3 as their timebase clock</li> </ul>                  |

| bit 16    | OCACLK: Output Compare Alternate Clock Selection bit <sup>(1)</sup>                                                                                                                              |

|           | <ul> <li>1 = Output Compare modules use an alternative Timer pair as their timebase clock</li> <li>0 = All Output Compare modules use Timer2/3 as their timebase clock</li> </ul>                |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 13    | IOLOCK: Peripheral Pin Select Lock bit <sup>(1)</sup>                                                                                                                                            |

|           | <ul> <li>1 = Peripheral Pin Select is locked. Writes to PPS registers are not allowed</li> <li>0 = Peripheral Pin Select is not locked. Writes to PPS registers are allowed</li> </ul>           |

| bit 12    | PMDLOCK: Peripheral Module Disable bit <sup>(1)</sup>                                                                                                                                            |

|           | <ul> <li>1 = Peripheral module is locked. Writes to PMD registers are not allowed</li> <li>0 = Peripheral module is not locked. Writes to PMD registers are allowed</li> </ul>                   |

| bit 11    | PGLOCK: Permission Group Lock bit <sup>(1)</sup>                                                                                                                                                 |

|           | <ul> <li>1 = Permission Group registers are locked. Writes to PG registers are not allowed</li> <li>0 = Permission Group registers are not locked. Writes to PG registers are allowed</li> </ul> |

| bit 10-9  | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 8     | USBSSEN: USB Suspend Sleep Enable bit <sup>(1)</sup>                                                                                                                                             |