Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-TQFP                                                                         |

| Supplier Device Package    | 144-TQFP (16x16)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efh144-i-ph |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                                      |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|--------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                          |

|          |                        |                 |                 | Т                        | imer1 thr   | ough Timer     | 9                                    |

| T1CK     | 48                     | 73              | A49             | 106                      | Ι           | ST             | Timer1 External Clock Input          |

| T2CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer2 External Clock Input          |

| T3CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer3 External Clock Input          |

| T4CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer4 External Clock Input          |

| T5CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer5 External Clock Input          |

| T6CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer6 External Clock Input          |

| T7CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer7 External Clock Input          |

| T8CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer8 External Clock Input          |

| T9CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer9 External Clock Input          |

|          | •                      | •               | •               | Real-                    | Time Clo    | ck and Cale    | endar                                |

| RTCC     | 46                     | 71              | A48             | 104                      | 0           | —              | Real-Time Clock Alarm/Seconds Output |

| Legend:  | CMOS = C               | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power               |

### **TABLE 1-7:** TIMER1 THROUGH TIMER9 AND RTCC PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels

TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select

I = Input

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   | —                 | —                 | -                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | -                 | —                 | —                 | -                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 | -                 | —                 | —                 | -                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-1              |

| 7:0          |                   |                   |                   |                   |                   | _                 |                  | NF               |

### REGISTER 3-4: CONFIG5: CONFIGURATION REGISTER 5; CP0 REGISTER 16, SELECT 5

| Legend:           | r = Reserved     |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-1 Unimplemented: Read as '0'

bit 0 NF: Nested Fault bit

1 = Nested Fault feature is implemented

### REGISTER 3-5: CONFIG7: CONFIGURATION REGISTER 7; CP0 REGISTER 16, SELECT 7

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R-1               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | WII               | —                 |                   | -                 | _                 | _                 | —                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 |                   | -                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.6         | —                 | —                 |                   | -                 | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | —                 | _                 | _                 | _                 | _                 | —                | —                |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 WII: Wait IE Ignore bit

1 = Indicates that this processor will allow an interrupt to unblock a WAIT instruction

bit 30-0 Unimplemented: Read as '0'

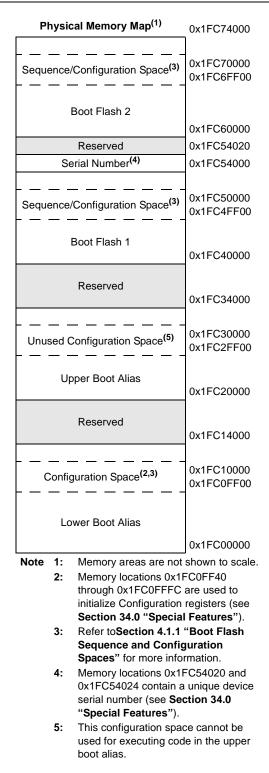

# FIGURE 4-5: BOOT AND ALIAS MEMORY MAP

### TABLE 4-1: SFR MEMORY MAP

|                           | Virtual Ad | dress           |

|---------------------------|------------|-----------------|

| Peripheral                | Base       | Offset<br>Start |

| System Bus <sup>(1)</sup> | 0xBF8F0000 | 0x0000          |

| Prefetch                  |            | 0x0000          |

| EBI                       |            | 0x1000          |

| SQI1                      |            | 0x2000          |

| USB                       | 0xBF8E0000 | 0x3000          |

| Crypto                    |            | 0x5000          |

| RNG                       |            | 0x6000          |

| CAN1 and CAN2             |            | 0x0000          |

| Ethernet                  | 0xBF880000 | 0x2000          |

| USBCR                     |            | 0x4000          |

| PORTA-PORTK               | 0xBF860000 | 0x0000          |

| Timer1-Timer9             |            | 0x0000          |

| IC1-IC9                   |            | 0x2000          |

| OC1-OC9                   | 0xBF840000 | 0x4000          |

| ADC                       |            | 0xB000          |

| Comparator 1, 2           |            | 0xC000          |

| I2C1-I2C5                 |            | 0x0000          |

| SPI1-SPI6                 | 0,000000   | 0x1000          |

| UART1-UART6               | 0xBF820000 | 0x2000          |

| PMP                       |            | 0xE000          |

| Interrupt Controller      | 0xBF810000 | 0x0000          |

| DMA                       | 00000      | 0x1000          |

| Configuration             |            | 0x0000          |

| Flash Controller          |            | 0x0600          |

| Watchdog Timer            |            | 0x0800          |

| Deadman Timer             | 0vPE800000 | 0x0A00          |

| RTCC                      | 0xBF800000 | 0x0C00          |

| CVREF                     |            | 0x0E00          |

| Oscillator                |            | 0x1200          |

| PPS                       |            | 0x1400          |

Note 1: Refer to 4.2 "System Bus Arbitration" for important legal information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | — —               |                   | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 |                   | —                 | —                | —                |

| 45.0         | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | —                 | —                 | T13PGV            | T12PGV            | T11PGV            | T10PGV            | T9PGV            | T8PGV            |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | T7PGV             | T6PGV             | T5PGV             | T4PGV             | T3PGV             | T2PGV             | T1PGV            | T0PGV            |

### REGISTER 4-2: SBFLAG: SYSTEM BUS STATUS FLAG REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-14 Unimplemented: Read as '0'

bit 13-0 **TxPGV:** Target 'x' Permission Group Violation Status bits ('x' = 0-13)

Refer to Table 4-6 for the list of available targets and their descriptions.

- 1 = Target is reporting a Permission Group (PG) violation

- 0 = Target is not reporting a PG violation

Note: All errors are cleared at the source (i.e., SBTxELOG1, SBTxELOG2, SBTxECLRS, or SBTxECLRM registers).

| Interrupt Source <sup>(1)</sup>    | XC22 Vector Name             | IRQ | Veeter #     |          | Interru  | pt Bit Locatior | ı            | Persistent |

|------------------------------------|------------------------------|-----|--------------|----------|----------|-----------------|--------------|------------|

| Interrupt Source /                 | XC32 Vector Name             | #   | Vector #     | Flag     | Enable   | Priority        | Sub-priority | Interrupt  |

| ADC Data 19 <sup>(2)</sup>         | _ADC_DATA19_VECTOR           | 78  | OFF078<17:1> | IFS2<14> | IEC2<14> | IPC19<20:18>    | IPC19<17:16> | Yes        |

| ADC Data 20 <sup>(2)</sup>         | _ADC_DATA20_VECTOR           | 79  | OFF079<17:1> | IFS2<15> | IEC2<15> | IPC19<28:26>    | IPC19<25:24> | Yes        |

| ADC Data 21 <sup>(2)</sup>         | _ADC_DATA21_VECTOR           | 80  | OFF080<17:1> | IFS2<16> | IEC2<16> | IPC20<4:2>      | IPC20<1:0>   | Yes        |

| ADC Data 22 <sup>(2)</sup>         | _ADC_DATA22_VECTOR           | 81  | OFF081<17:1> | IFS2<17> | IEC2<17> | IPC20<12:10>    | IPC20<9:8>   | Yes        |

| ADC Data 23 <sup>(2)</sup>         | _ADC_DATA23_VECTOR           | 82  | OFF082<17:1> | IFS2<18> | IEC2<18> | IPC20<20:18>    | IPC20<17:16> | Yes        |

| ADC Data 24 <sup>(2)</sup>         | _ADC_DATA24_VECTOR           | 83  | OFF083<17:1> | IFS2<19> | IEC2<19> | IPC20<28:26>    | IPC20<25:24> | Yes        |

| ADC Data 25 <sup>(2)</sup>         | _ADC_DATA25_VECTOR           | 84  | OFF084<17:1> | IFS2<20> | IEC2<20> | IPC21<4:2>      | IPC21<1:0>   | Yes        |

| ADC Data 26 <sup>(2)</sup>         | _ADC_DATA26_VECTOR           | 85  | OFF085<17:1> | IFS2<21> | IEC2<21> | IPC21<12:10>    | IPC21<9:8>   | Yes        |

| ADC Data 27 <sup>(2)</sup>         | _ADC_DATA27_VECTOR           | 86  | OFF086<17:1> | IFS2<22> | IEC2<22> | IPC21<20:18>    | IPC21<17:16> | Yes        |

| ADC Data 28 <sup>(2)</sup>         | _ADC_DATA28_VECTOR           | 87  | OFF087<17:1> | IFS2<23> | IEC2<23> | IPC21<28:26>    | IPC21<25:24> | Yes        |

| ADC Data 29 <sup>(2)</sup>         | _ADC_DATA29_VECTOR           | 88  | OFF088<17:1> | IFS2<24> | IEC2<24> | IPC22<4:2>      | IPC22<1:0>   | Yes        |

| ADC Data 30 <sup>(2)</sup>         | _ADC_DATA30_VECTOR           | 89  | OFF089<17:1> | IFS2<25> | IEC2<25> | IPC22<12:10>    | IPC22<9:8>   | Yes        |

| ADC Data 31 <sup>(2)</sup>         | _ADC_DATA31_VECTOR           | 90  | OFF090<17:1> | IFS2<26> | IEC2<26> | IPC22<20:18>    | IPC22<17:16> | Yes        |

| ADC Data 32 <sup>(2)</sup>         | _ADC_DATA32_VECTOR           | 91  | OFF091<17:1> | IFS2<27> | IEC2<27> | IPC22<28:26>    | IPC22<25:24> | Yes        |

| ADC Data 33 <sup>(2)</sup>         | _ADC_DATA33_VECTOR           | 92  | OFF092<17:1> | IFS2<28> | IEC2<28> | IPC23<4:2>      | IPC23<1:0>   | Yes        |

| ADC Data 34 <sup>(2)</sup>         | _ADC_DATA34_VECTOR           | 93  | OFF093<17:1> | IFS2<29> | IEC2<29> | IPC23<12:10>    | IPC23<9:8>   | Yes        |

| ADC Data 35 <sup>(2,3)</sup>       | _ADC_DATA35_VECTOR           | 94  | OFF094<17:1> | IFS2<30> | IEC2<30> | IPC23<20:18>    | IPC23<17:16> | Yes        |

| ADC Data 36 <sup>(2,3)</sup>       | _ADC_DATA36_VECTOR           | 95  | OFF095<17:1> | IFS2<31> | IEC2<31> | IPC23<28:26>    | IPC23<25:24> | Yes        |

| ADC Data 37 <sup>(2,3)</sup>       | _ADC_DATA37_VECTOR           | 96  | OFF096<17:1> | IFS3<0>  | IEC3<0>  | IPC24<4:2>      | IPC24<1:0>   | Yes        |

| ADC Data 38 <sup>(2,3)</sup>       | _ADC_DATA38_VECTOR           | 97  | OFF097<17:1> | IFS3<1>  | IEC3<1>  | IPC24<12:10>    | IPC24<9:8>   | Yes        |

| ADC Data 39 <sup>(2,3)</sup>       | _ADC_DATA39_VECTOR           | 98  | OFF098<17:1> | IFS3<2>  | IEC3<2>  | IPC24<20:18>    | IPC24<17:16> | Yes        |

| ADC Data 40 <sup>(2,3)</sup>       | _ADC_DATA40_VECTOR           | 99  | OFF099<17:1> | IFS3<3>  | IEC3<3>  | IPC24<28:26>    | IPC24<25:24> | Yes        |

| ADC Data 41 <sup>(2,3)</sup>       | _ADC_DATA41_VECTOR           | 100 | OFF100<17:1> | IFS3<4>  | IEC3<4>  | IPC25<4:2>      | IPC25<1:0>   | Yes        |

| ADC Data 42 <sup>(2,3)</sup>       | _ADC_DATA42_VECTOR           | 101 | OFF101<17:1> | IFS3<5>  | IEC3<5>  | IPC25<12:10>    | IPC25<9:8>   | Yes        |

| ADC Data 43                        | _ADC_DATA43_VECTOR           | 102 | OFF102<17:1> | IFS3<6>  | IEC3<6>  | IPC25<20:18>    | IPC25<17:16> | Yes        |

| ADC Data 44                        | _ADC_DATA44_VECTOR           | 103 | OFF103<17:1> | IFS3<7>  | IEC3<7>  | IPC25<28:26>    | IPC25<25:24> | Yes        |

| Core Performance Counter Interrupt | _CORE_PERF_COUNT_VECTOR      | 104 | OFF104<17:1> | IFS3<8>  | IEC3<8>  | IPC26<4:2>      | IPC26<1:0>   | No         |

| Core Fast Debug Channel Interrupt  | _CORE_FAST_DEBUG_CHAN_VECTOR | 105 | OFF105<17:1> | IFS3<9>  | IEC3<9>  | IPC26<12:10>    | IPC26<9:8>   | Yes        |

### TABLE 7-2: INTERRUPT IRQ, VECTOR, AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

3: This interrupt source is not available on 100-pin devices.

4: This interrupt source is not available on 124-pin devices.

### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>)                   |                                 | Ð         |       |       |       |       | -             |                     |          | Bits                  |      |      |      |                |              |                     |          |                       |            |  |  |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------------|---------------------|----------|-----------------------|------|------|------|----------------|--------------|---------------------|----------|-----------------------|------------|--|--|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10               | 25/9     | 24/8                  | 23/7 | 22/6 | 21/5 | 20/4           | 19/3         | 18/2                | 17/1     | 16/0                  | All Resets |  |  |

| 0050                        | 100.44                          | 31:16     | _     | —     | —     |       | FCEIP<2:0>    |                     | FCEIS    | <1:0>                 | _    | _    | —    |                | RTCCIP<2:0   | )>                  | RTCCI    | S<1:0>                | 0000       |  |  |

| 03D0                        | IPC41                           | 15:0      | _     | _     | _     |       | SPI4TXIP<2:0  | )>                  | SPI4TXI  | S<1:0>                | -    | _    | -    | SPI4RXIP<2:0>  |              | SPI4RX              | IS<1:0>  | 0000                  |            |  |  |

| 0250                        | IPC42                           | 31:16     |       | _     | _     |       | U4RXIP<2:0:   | >                   | U4RXIS   | S<1:0>                | _    | _    | _    | U4EIP<2:0>     |              | U4EIS               | S<1:0>   | 0000                  |            |  |  |

| 03E0                        | IPC42                           | 15:0      | _     | _     | —     |       | SQI1IP<2:0>   |                     | SQI1IS   | 5<1:0>                | _    | _    | _    |                | PREIP<2:0    | >                   | PREIS    | S<1:0>                | 0000       |  |  |

| 0250                        | IPC43                           | 31:16     | _     | _     | —     |       | I2C4MIP<2:0>  |                     | I2C4MI   | S<1:0>                | _    | _    | _    |                | I2C4SIP<2:0  | )>                  | I2C4SI   | S<1:0>                | 0000       |  |  |

| 03F0                        | IPC43                           | 15:0      |       | _     | _     |       | I2C4BIP<2:0:  | >                   | I2C4BIS  | S<1:0>                | _    | _    | -    |                | U4TXIP<2:0   | >                   | U4TXI    | S<1:0>                | 0000       |  |  |

| 0.400                       | 10044                           | 31:16     | _     | _     | —     |       | U5EIP<2:0>    |                     | U5EIS    | <1:0>                 | _    | _    | _    | S              | PI5TXIP<2:0  | <sub>&gt;</sub> (2) | SPI5TXIS | S<1:0> <b>(2)</b>     | 0000       |  |  |

| 0400                        | IPC44                           | 15:0      | -     | _     | —     | 5     | SPI5RXIP<2:0: | <sub>&gt;</sub> (2) | SPI5RXIS | S<1:0> <b>(2)</b>     | —    | _    | -    | 5              | SPI5EIP<2:0: | >(2)                | SPI5EIS  | S<1:0> <b>(2)</b>     | 0000       |  |  |

| 0410                        | IPC45                           | 31:16     | _     | _     | _     |       | I2C5SIP<2:0:  | >                   | 12C5S1   | S<1:0>                |      | _    | —    |                | I2C5BIP<2:0  | )>                  | I2C5BI   | S<1:0>                | 0000       |  |  |

| 0410                        | IPC45                           | 15:0      |       | _     | _     |       | U5TXIP<2:0:   | >                   | U5TXIS   | 6<1:0>                | _    | _    | _    |                | U5RXIP<2:0   | )>                  | U5RXI    | S<1:0>                | 0000       |  |  |

| 0420                        | IPC46                           | 31:16     | _     | _     | _     | S     | SPI6TXIP<2:0> | (2)                 | SPI6TXIS | 6<1:0> <sup>(2)</sup> | -    | _    | —    | S              | PI6RXIP<2:0  | )> <sup>(2)</sup>   | SPI6RXI  | S<1:0> <sup>(2)</sup> | 0000       |  |  |

| 0420                        |                                 | 15:0      | _     | _     | _     |       | SPI6EIP<2:0>  | (2)                 | SPI6EIS  | <1:0> <sup>(2)</sup>  |      | _    | —    |                | I2C5MIP<2:0  | )>                  | I2C5MI   | S<1:0>                | 0000       |  |  |

| 0420                        | IPC47                           | 31:16     | _     | —     | —     | —     | _             |                     | -        |                       |      | _    | _    |                | U6TXIP<2:0   | >                   | U6TXI    | S<1:0>                | 0000       |  |  |

| 0430                        | IFC47                           | 15:0      | _     | -     | —     |       | U6RXIP<2:0:   | >                   | U6RXIS   | S<1:0>                |      | _    | —    |                | U6EIP<2:0:   | >                   | U6EIS    | 6<1:0>                | 0000       |  |  |

| 0440                        | IPC48                           | 31:16     | _     | _     | _     | _     | _             |                     | _        |                       |      | _    | —    | ADCURDYIP<2:0> |              | ADCURDYIS<1:0       |          | 0000                  |            |  |  |

| 0440                        | IF U40                          | 15:0      | _     | —     | —     | A     | DCARDYIP<2    | :0>                 | ADCARD   | YIS<1:0>              |      | _    | _    | A              | DCEOSIP<2    | 2:0>                | ADCEOS   | SIS<1:0>              | 0000       |  |  |

| 0450                        | IPC49                           | 31:16     | _     | -     | —     |       | ADC1EIP<2:0   | >                   | ADC1EI   | S<1:0>                |      |      |      | ADC0EIP<2:0>   |              | ADC0E               | IS<1:0>  | 0000                  |            |  |  |

| 0430                        | 1FC49                           | 15:0      | _     | —     | —     | _     | _             | _                   | _        | _                     |      |      |      | A              | DCGRPIP<2    | 2:0>                | ADCGR    | PIS<1:0>              | 0000       |  |  |

| 0460                        | IPC50                           | 31:16     | _     | _     | _     | _     | _             |                     | _        |                       |      |      |      |                | ADC4EIP<2:   | 0>                  | ADC4E    | IS<1:0>               | 0000       |  |  |

| 0400                        | 1FC30                           | 15:0      | _     | _     | _     |       | ADC3EIP<2:0   | >                   | ADC3EI   | S<1:0>                |      |      |      |                | ADC2EIP<2:   | 0>                  | ADC2E    | IS<1:0>               | 0000       |  |  |

| 0470                        | IPC51                           | 31:16     | _     | _     | _     |       | ADC1WIP<2:0   | )>                  | ADC1W    | IS<1:0>               |      |      |      |                | ADC0WIP<2:   | :0>                 | ADC0W    | 'IS<1:0>              | 0000       |  |  |

| 0470                        | IPC51                           | 15:0      |       | _     | _     |       | ADC7EIP<2:0   | >                   | ADC7EI   | S<1:0>                |      |      |      | _              | _            | _                   | -        | _                     | 0000       |  |  |

| 0490                        | IPC52                           | 31:16     | _     | _     | _     | _     | _             | -                   | _        |                       |      |      |      |                | ADC4WIP<2:   | :0>                 | ADC4W    | 'IS<1:0>              | 0000       |  |  |

| 0460                        | IPC52                           | 15:0      |       | —     | _     |       | ADC3WIP<2:0   | )>                  | ADC3W    | IS<1:0>               |      |      |      |                | ADC2WIP<2:   | :0>                 | ADC2W    | 'IS<1:0>              | 0000       |  |  |

| 0400                        | IPC53                           | 31:16     | -     | _     | _     | —     | -             | —                   | -        | _                     |      |      |      | —              | —            | —                   | —        | —                     | 0000       |  |  |

| 0490                        | IPC53                           | 15:0      | _     | _     | —     |       | ADC7WIP<2:0   | )>                  | ADC7W    | IS<1:0>               |      |      |      | _              | _            | —                   | _        | _                     | 0000       |  |  |

| 0540                        | 055000                          | 31:16     | _     | —     | —     | _     | _             | —                   | _        | —                     | _    | —    | -    | _              | —            | —                   | VOFF<    | :17:16>               | 0000       |  |  |

| 0540                        | OFF000                          | 15:0      |       |       |       |       |               |                     |          | VOFF<15:1>            |      |      |      |                |              |                     |          | —                     | 0000       |  |  |

| 0544                        | 055004                          | 31:16     | _     | —     | —     | _     | —             | —                   | —        | —                     | —    | _    | —    | —              | —            | _                   | VOFF<    | :17:16>               | 0000       |  |  |

| 0544                        | OFF001                          | 15:0      |       |       |       | •     |               |                     |          | VOFF<15:1>            |      |      |      |                |              |                     |          |                       | 0000       |  |  |

Legend:

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

3: This bit or register is not available on devices without a CAN module.

4: This bit or register is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

### TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| ss                          |                  |           | Bits       |         |        |       |           |               |         |         |        |        |                       |                       |        |          |        |       |            |

|-----------------------------|------------------|-----------|------------|---------|--------|-------|-----------|---------------|---------|---------|--------|--------|-----------------------|-----------------------|--------|----------|--------|-------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15      | 30/14   | 29/13  | 28/12 | 27/11     | 26/10         | 25/9    | 24/8    | 23/7   | 22/6   | 21/5                  | 20/4                  | 19/3   | 18/2     | 17/1   | 16/0  | All Resets |

| 3340                        | USB              | 31:16     | _          | _       | —      | —     | —         | _             |         | _       | EP7TXD | EP6TXD | EP5TXD                | EP4TXD                | EP3TXD | EP2TXD   | EP1TXD | _     | 0000       |

| 3340                        | DPBFD            | 15:0      | _          | —       | —      | —     | —         | _             | _       | —       | EP7RXD | EP6RXD | EP5RXD                | EP4RXD                | EP3RXD | EP2RXD   | EP1RXD | —     | 0000       |

| 3344                        |                  | JSB 31:16 |            |         |        |       |           | THHSRTN<15:0> |         |         |        |        |                       |                       |        |          |        |       | 05E6       |

| 5544                        | TMCON1           | 15:0      | TUCH<15:0> |         |        |       |           |               |         |         |        |        |                       | 4074                  |        |          |        |       |            |

| 3348                        | 000              | 31:16     | _          |         | —      | _     | —         | —             | _       | —       | _      | —      | —                     | _                     | _      | _        | -      | _     | 0000       |

| 0040                        | TMCON2           | 15:0      | _          | —       | —      | _     | —         | —             | -       | —       |        | —      | —                     | _                     |        | THSBT<3  | 8:0>   |       | 0000       |

|                             |                  | 31:16     |            | _       | LPM    | LPM   |           | LPMNYIE       | LPMSTIE | LPMTOIE |        |        |                       | LPMNAK <sup>(1)</sup> |        | N<1:0>   | LPMRES |       | 0000       |

| 3360                        | USB<br>LPMR1     | 51.10     | _          |         | ERRIE  | RESIE |           |               |         |         |        | _      | _                     | _(2)                  | (2)    | (2)      |        |       | 0000       |

|                             | 2                | 15:0      |            | ENDPOIN | T<3:0> |       | —         | _             | _       | RMTWAK  |        | HIRI   | D<3:0>                |                       |        | LNKSTATE | <3:0>  |       | 0000       |

|                             |                  | 31:16     | _          | —       | _      | _     | —         | _             | _       | _       | _      | —      | —                     | _                     | _      | _        | —      |       | 0000       |

| 3364                        | USB<br>LPMR2     | 15:0      | _          |         |        | LPI   | MFADDR<6: | 0>            |         |         | _      | _      | LPMERR <sup>(1)</sup> | LPMRES                | LPMNC  | LPMACK   | LPMNY  | LPMST | 0000       |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: Device mode.

2: Host mode.

3:

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7). 4:

### TABLE 11-2: USB REGISTER MAP 2

| s                          |                  | Bits      |       |       |       |       |       |       |               |              |         |               |                |                |               |       |        |               |            |

|----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|---------------|--------------|---------|---------------|----------------|----------------|---------------|-------|--------|---------------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9          | 24/8         | 23/7    | 22/6          | 21/5           | 20/4           | 19/3          | 18/2  | 17/1   | 16/0          | All Resets |

|                            |                  | 31:16     | _     | —     | —     | _     | —     | USBIF | USBRF         | USBWKUP      | _       | —             | —              | —              | _             | —     | —      | _             | 0100       |

| 4000                       | USB<br>CRCON     | 15:0      | _     | _     | _     | _     | _     | _     | USB<br>IDOVEN | USB<br>IDVAL | PHYIDEN | VBUS<br>MONEN | ASVAL<br>MONEN | BSVAL<br>MONEN | SEND<br>MONEN | USBIE | USBRIE | USB<br>WKUPEN | 8000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | DATA<31:24>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DATA<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DATA<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | DATA              | <7:0>             |                   |                  |                  |  |  |  |

### REGISTER 11-12: USBFIFOX: USB FIFO DATA REGISTER 'x' ('x' = 0-7)

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-0 DATA<31:0>: USB Transmit/Receive FIFO Data bits

Writes to this register loads data into the TxFIFO for the corresponding endpoint. Reading from this register unloads data from the RxFIFO for the corresponding endpoint.

Transfers may be 8-bit, 16-bit or 32-bit as required, and any combination of access is allowed provided the data accessed is contiguous. However, all transfers associated with one packet must be of the same width so that data is consistently byte-, word- or double-word aligned. The last transfer may contain fewer bytes than the previous transfers in order to complete an odd-byte or odd-word transfer.

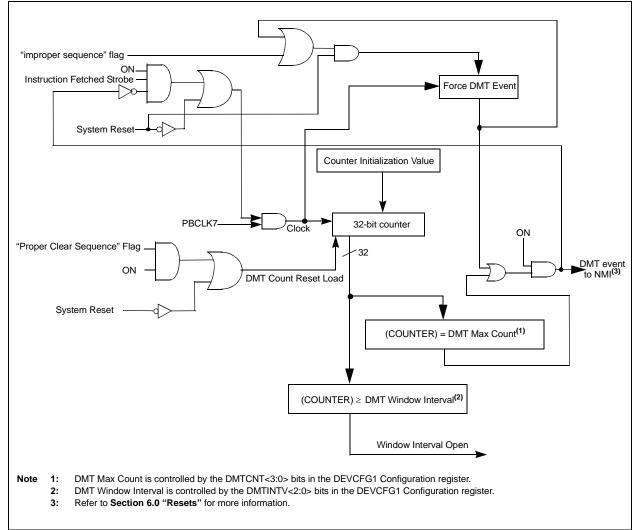

### 15.0 DEADMAN TIMER (DMT)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The primary function of the Deadman Timer (DMT) is to reset the processor in the event of a software malfunction. The DMT is a free-running instruction fetch timer, which is clocked whenever an instruction fetch occurs until a count match occurs. Instructions are not fetched when the processor is in Sleep mode. The DMT consists of a 32-bit counter with a time-out count match value as specified by the DMTCNT<3:0> bits in the DEVCFG1 Configuration register.

A Deadman Timer is typically used in mission critical and safety critical applications, where any single failure of the software functionality and sequencing must be detected.

Figure 15-1 shows a block diagram of the Deadman Timer module.

### FIGURE 15-1: DEADMAN TIMER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0                   | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   | —                    | -                     |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0                   | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | _                     |                   | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0                   | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | SIDL              | —                    | _                     | -                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0                 | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   | OC32              | OCFLT <sup>(1)</sup> | OCTSEL <sup>(2)</sup> |                   | OCM<2:0>         |                  |

### REGISTER 18-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(1)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 OCTSEL: Output Compare Timer Select bit<sup>(2)</sup>

- 1 = Timery is the clock source for this Output Compare module

- 0 = Timerx is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin is enabled

- 110 = PWM mode on OCx; Fault pin is disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

- **2:** Refer to Table 18-1 for Timerx and Timery selections.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24     | _                 |                   |                   |                   |                   |                   |                  | _                |

| 22.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | _                 | _                 | —                 | _                 | LVL11             | LVL10             | LVL9             | LVL8             |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | LVL7              | LVL6              | LVL5              | LVL4              | LVL3              | LVL2              | LVL1             | LVL0             |

### REGISTER 28-26: ADCTRGSNS: ADC TRIGGER LEVEL/EDGE SENSITIVITY REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-12 Unimplemented: Read as '0'

- bit 11 LVL11:LVL0: Trigger Level and Edge Sensitivity bits

- 1 = Analog input is sensitive to the high level of its trigger (level sensitivity implies retriggering as long as the trigger signal remains high)

- 0 = Analog input is sensitive to the positive edge of its trigger (this is the value after a reset)

Note 1: This register specifies the trigger level for analog inputs 0 to 31.

2: The higher analog input ID belongs to Class 3, and therefore, is only scan triggered. All Class 3 analog inputs use the Scan Trigger, for which the level/edge is defined by the STRGLVL bit (ADCCON1<3>).

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 04.04        | U-0                    |

| 31:24        |                        | —                      | —                      | —                      | —                      | —                      | —                      | —                      |

| 22:46        | U-0                    |

| 23:16        | —                      | —                      | _                      | —                      | _                      | —                      | —                      | —                      |

| 45.0         | U-0                    | U-0                    | U-0                    | R-0, HS, HC            |

| 15:8         | —                      | —                      | _                      | EIRDY44 <sup>(2)</sup> | EIRDY43 <sup>(2)</sup> | EIRDY42 <sup>(2)</sup> | EIRDY41 <sup>(2)</sup> | EIRDY40 <sup>(2)</sup> |

| 7.0          | R-0, HS, HC            |

| 7:0          | EIRDY39 <sup>(2)</sup> | EIRDY38 <sup>(2)</sup> | EIRDY37 <sup>(2)</sup> | EIRDY36 <sup>(2)</sup> | EIRDY35 <sup>(2)</sup> | EIRDY34 <sup>(1)</sup> | EIRDY33 <sup>(1)</sup> | EIRDY32 <sup>(1)</sup> |

### REGISTER 28-31: ADCEISTAT2: ADC EARLY INTERRUPT STATUS REGISTER 2

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                    |  |

|-------------------|-------------------|------------------------------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'       |  |

| -n = Value at POR | '1' = Bit is set  | 0' = Bit is cleared $x = Bit is unknown$ |  |

### bit 31-13 Unimplemented: Read as '0'

bit 31-0 **EIRDY44:EIRDY32:** Early Interrupt for Corresponding Analog Input Ready bits

- 1 = This bit is set when the early interrupt event occurs for the specified analog input. An interrupt will be generated if early interrupts are enabled in the ADCEIEN2 register. For the Class 1 analog inputs, this bit will set as per the configuration of the ADCEIS<2:0> bits in the ADCXTIME register. For the shared ADC module, this bit will be set as per the configuration of the ADCEIS<2:0> bits in the ADCEIS<2:0> bits in the ADCCON2 register.

- 0 = Interrupts are disabled

**Note 1:** This bit is not available on 64-pin devices.

2: This bit is not available on 64-pin and 100-pin devices.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04-04     | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24     | —                 | —                 | _                 | _                 | WKUPCLKCNT<3:0>   |                   |                  |                  |  |

| 00.40     | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16     | WKIEN7            | —                 | _                 | WKIEN4            | WKIEN3            | WKIEN2            | WKIEN1           | WKIEN0           |  |

| 45.0      | R-0, HS, HC       | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |

| 15:8      | WKRDY7            | —                 | _                 | WKRDY4            | WKRDY3            | WKRDY2            | WKRDY1           | WKRDY0           |  |

| 7.0       | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0       | ANEN7             | _                 |                   | ANEN4             | ANEN3             | ANEN2             | ANEN1            | ANEN0            |  |

### REGISTER 28-32: ADCANCON: ADC ANALOG WARM-UP CONTROL REGISTER

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                    |

|-------------------|-------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set  | 0' = Bit is cleared $x = Bit is unknown$ |

### bit 31-28 Unimplemented: Read as '0'

### bit 27-24 WKUPCLKCNT<3:0>: Wake-up Clock Count bits

These bits represent the number of ADC clocks required to warm-up the ADC module before it can perform conversion. Although the clocks are specific to each ADC, the WKUPCLKCNT bit is common to all ADC modules.

$1111 = 2^{15} = 32.768$  clocks  $0110 = 2^6 = 64$  clocks  $0101 = 2^5 = 32$  clocks  $0100 = 2^4 = 16$  clocks  $0011 = 2^4 = 16$  clocks  $0010 = 2^4 = 16$  clocks  $0001 = 2^4 = 16$  clocks  $0000 = 2^4 = 16$  clocks bit 23 WKIEN7: Shared ADC (ADC7) Wake-up Interrupt Enable bit 1 = Enable interrupt and generate interrupt when the WKRDY7 status bit is set 0 = Disable interrupt bit 22-21 Unimplemented: Read as '0' bit 20-16 WKIEN4:WKIEN0: ADC4-ADC0 Wake-up Interrupt Enable bit 1 = Enable interrupt and generate interrupt when the WKRDYx status bit is set 0 = Disable interrupt bit 15 WKRDY7: Shared ADC (ADC7) Wake-up Status bit 1 = ADC7 Analog and Bias circuitry ready after the wake-up count number 2<sup>WKUPEXP</sup> clocks after setting ANEN7 to '1' 0 = ADC7 Analog and Bias circuitry is not ready Note: This bit is cleared by hardware when the ANEN7 bit is cleared bit 14-13 Unimplemented: Read as '0' bit 12-8 WKRDY4:WKRDY0: ADC4-ADC0 Wake-up Status bit 1 = ADCx Analog and Bias circuitry ready after the wake-up count number 2<sup>WKUPEXP</sup> clocks after setting ANENx to '1' 0 = ADCx Analog and Bias circuitry is not ready

Note: These bits are cleared by hardware when the ANENx bit is cleared

| REGISTE   | R 29-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3 (CONTINUED)                                          |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 15    | FLTEN13: Filter 13 Enable bit                                                                          |

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 14-13 | MSEL13<1:0>: Filter 13 Mask Select bits                                                                |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 12-8  | FSEL13<4:0>: FIFO Selection bits                                                                       |

| DIL 12-0  | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           |                                                                                                        |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| bit 7     | FLTEN12: Filter 12 Enable bit                                                                          |

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 6-5   | MSEL12<1:0>: Filter 12 Mask Select bits                                                                |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 4-0   | FSEL12<4:0>: FIFO Selection bits                                                                       |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

|           |                                                                                                        |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. |

### **REGISTER 30-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER (CONTINUED)** bit 7 **CRCERREN:** CRC Error Collection Enable bit 1 = The received packet CRC must be invalid for the packet to be accepted 0 = Disable CRC Error Collection filtering This bit allows the user to collect all packets that have an invalid CRC. bit 6 CRCOKEN: CRC OK Enable bit 1 = The received packet CRC must be valid for the packet to be accepted 0 = Disable CRC filtering This bit allows the user to reject all packets that have an invalid CRC. **RUNTERREN:** Runt Error Collection Enable bit bit 5 1 = The received packet must be a runt packet for the packet to be accepted 0 = Disable Runt Error Collection filtering This bit allows the user to collect all packets that are runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes (when CRCOKEN = 0) or any packet with a size of less than 64 bytes that has a valid CRC (when CRCOKEN = 1). RUNTEN: Runt Enable bit bit 4 1 = The received packet must not be a runt packet for the packet to be accepted 0 = Disable Runt filtering This bit allows the user to reject all runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes. bit 3 UCEN: Unicast Enable bit 1 = Enable Unicast Filtering 0 = Disable Unicast Filtering This bit allows the user to accept all unicast packets whose Destination Address matches the Station Address. bit 2 NOTMEEN: Not Me Unicast Enable bit 1 = Enable Not Me Unicast Filtering 0 = Disable Not Me Unicast Filtering This bit allows the user to accept all unicast packets whose Destination Address does not match the Station Address. MCEN: Multicast Enable bit bit 1 1 = Enable Multicast Filtering 0 = Disable Multicast Filtering This bit allows the user to accept all Multicast Address packets. bit 0 BCEN: Broadcast Enable bit 1 = Enable Broadcast Filtering 0 = Disable Broadcast Filtering This bit allows the user to accept all Broadcast Address packets. Note 1: XOR = True when either one or the other conditions are true, but not both. 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

# Note 1: This register is only used for RX operations. 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                            | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0                          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                              | —                 | —                 | —                 | —                 | —                 |                  | —                |

| 15:8         | R/W-0                        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-0            | R/W-1            |

| 10.0         | MACMAXF<15:8> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-1                        | R/W-1             | R/W-1             | R/W-0             | R/W-1             | R/W-1             | R/W-1            | R/W-0            |

|              | MACMAXF<7:0> <sup>(1)</sup>  |                   |                   |                   |                   |                   |                  |                  |

### REGISTER 30-28: EMAC1MAXF: ETHERNET CONTROLLER MAC MAXIMUM FRAME LENGTH REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 **Unimplemented:** Read as '0'

bit 15-0 MACMAXF<15:0>: Maximum Frame Length bits<sup>(1)</sup> These bits reset to 0x05EE, which represents a maximum receive frame o

These bits reset to 0x05EE, which represents a maximum receive frame of 1518 octets. An untagged maximum size Ethernet frame is 1518 octets. A tagged frame adds four octets for a total of 1522 octets. If a shorter/longer maximum length restriction is desired, program this 16-bit field.

**Note 1:** If a proprietary header is allowed, this bit should be adjusted accordingly. For example, if 4-byte headers are prepended to frames, MACMAXF could be set to 1527 octets. This would allow the maximum VLAN tagged frame plus the 4-byte header.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | r-1               | R/P               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

|              | —                 | UPLLFSEL          | _                 | —                 | —                 | _                 | _                | —                |

| 23:16        | r-1               | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |

|              | —                 | —                 | _                 | —                 | —                 | FPLLODIV<2:0>     |                  |                  |

| 15:8         | r-1               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

|              |                   | FPLLMULT<6:0>     |                   |                   |                   |                   |                  |                  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | r-1               | R/P               | R/P              | R/P              |

|              | FPLLICLK          | FPLLRNG<2:0>      |                   |                   |                   | FPLLIDIV<2:0>     |                  |                  |

### REGISTER 34-5: DEVCFG2/ADEVCFG2: DEVICE CONFIGURATION WORD 2

| Legend:           | r = Reserved bit | P = Programmable bit               |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 31 Reserved: Write as '1'

- bit 30 UPLLFSEL: USB PLL Input Frequency Select bit 1 = UPLL input clock is 24 MHz 0 = UPLL input clock is 12 MHz

- bit 29-19 Reserved: Write as '1'

### bit 18-16 FPLLODIV<2:0>: Default System PLL Output Divisor bits

- 111 = PLL output divided by 32

- 110 = PLL output divided by 32

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 2

- bit 15 Reserved: Write as '1'

### bit 14-8 FPLLMULT<6:0>: System PLL Feedback Divider bits

- 1111111 = Multiply by 128 1111110 = Multiply by 127 1111101 = Multiply by 126

- 1111100 = Multiply by 125

- •

- 0000000 = Multiply by 1

- bit 7 FPLLICLK: System PLL Input Clock Select bit

- 1 = FRC is selected as input to the System PLL

- 0 = Posc is selected as input to the System PLL

### bit 6-4 **FPLLRNG<2:0>:** System PLL Divided Input Clock Frequency Range bits

- 111 = Reserved

- 110 = Reserved

- 101 = 34-64 MHz

- 100 = 21-42 MHz

- 011 = 13-26 MHz

- 010 = 8-16 MHz

- 001 = 5-10 MHz

- 000 = Bypass

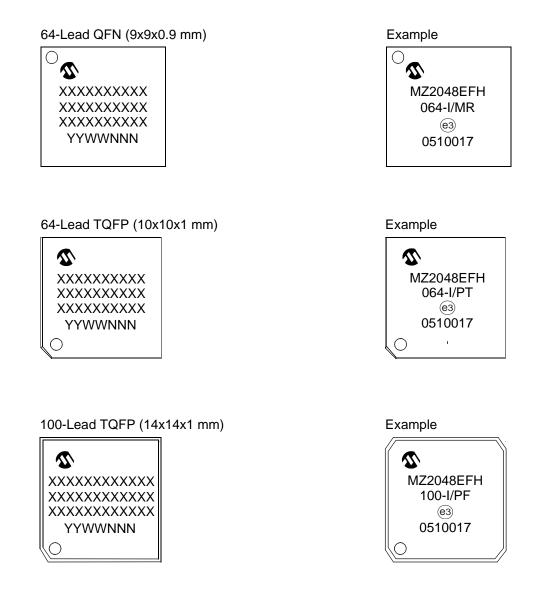

### 41.0 PACKAGING INFORMATION

# 41.1 Package Marking Information

| Legend | XXX                                                                               | Customer-specific information                         |  |  |  |  |  |  |  |

|--------|-----------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|--|

|        | Y                                                                                 | Year code (last digit of calendar year)               |  |  |  |  |  |  |  |

|        | YY                                                                                | Year code (last 2 digits of calendar year)            |  |  |  |  |  |  |  |

|        | WW                                                                                | Week code (week of January 1 is week '01')            |  |  |  |  |  |  |  |

|        | NNN                                                                               | Alphanumeric traceability code                        |  |  |  |  |  |  |  |

|        | Pb-free JEDEC designator for Matte Tin (Sn)                                       |                                                       |  |  |  |  |  |  |  |

|        | * This package is Pb-free. The Pb-free JEDEC designator ( $e_3$ )                 |                                                       |  |  |  |  |  |  |  |

|        |                                                                                   | can be found on the outer packaging for this package. |  |  |  |  |  |  |  |

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will |                                                       |  |  |  |  |  |  |  |

|        | be carried over to the next line, thus limiting the number of available           |                                                       |  |  |  |  |  |  |  |

|        | characters for customer-specific information.                                     |                                                       |  |  |  |  |  |  |  |

| L      |                                                                                   |                                                       |  |  |  |  |  |  |  |

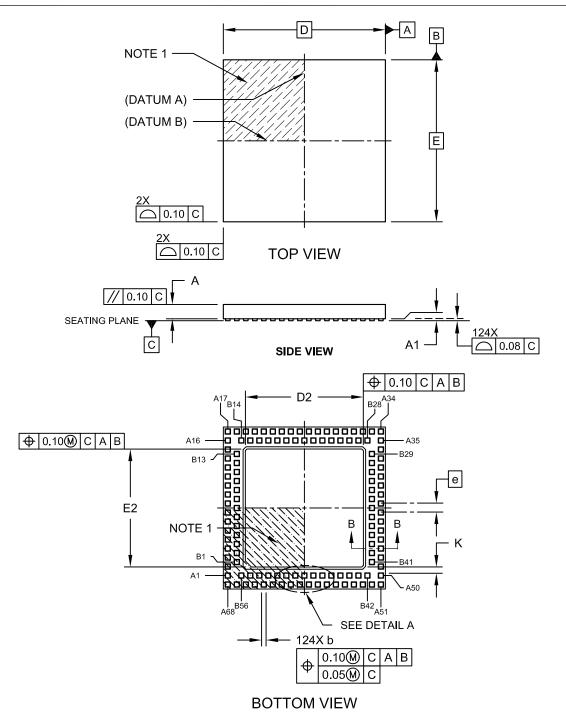

## 124-Terminal Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-193A Sheet 1 of 2

# $\begin{array}{c} \bullet \\ \bullet \\ A2 \\ \bullet \\ A1 \\ \bullet \\ \bullet \\ (L1) \\ \bullet \end{array}$

144-Lead Plastic Thin Quad Flatpack (PH)-16x16x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |      |      |  |

|-------------------------|-------------|-----------|------|------|--|

| Dimensio                | MIN         | NOM       | MAX  |      |  |

| Number of Pins          | Ν           | 144       |      |      |  |

| Lead Pitch              | е           | 0.40 BSC  |      |      |  |

| Overall Height          | А           | -         | -    | 1.20 |  |

| Molded PackageThickness | A2          | 0.95      | 1.00 | 1.05 |  |

| Standoff                | A1          | 0.05      | -    | 0.15 |  |

| Foot Length             | L           | 0.45      | 0.60 | 0.75 |  |

| Footprint               | L1          | 1.00 REF  |      |      |  |

| Overall Width           | D           | 18.00 BSC |      |      |  |

| Overall Length          | E           | 18.00 BSC |      |      |  |

| Molded Body Width       | D1          | 16.00 BSC |      |      |  |

| Molded Body Length      | E1          | 16.00 BSC |      |      |  |

| Lead Thickness          | С           | 0.09      | -    | 0.20 |  |

| Lead Width              | b           | 0.13      | -    | 0.23 |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-155B Sheet 2 of 2