Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efh144-i-pl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 124              | -PIN VTLA (BOTTOM VIEW)                                                                                  | A17       |      | E                | A34<br><sub>313</sub> B29   |     |

|------------------|----------------------------------------------------------------------------------------------------------|-----------|------|------------------|-----------------------------|-----|

|                  | PIC32MZ0512EF(E/F/K)124<br>PIC32MZ1024EF(G/H/M)124<br>PIC32MZ1024EF(E/F/K)124<br>PIC32MZ2048EF(G/H/M)124 |           |      | A1               | B1 B41<br>B56               | A51 |

|                  | Pol                                                                                                      | arity Inc | lica | tor              | A68                         |     |

| Package<br>Pin # | Full Pin Name                                                                                            |           |      | Package<br>Pin # | Full Pin Name               |     |

| B1               | EBIA5/AN34/PMA5/RA5                                                                                      |           |      | B29              | Vss                         |     |

| B2               | EBID6/AN16/PMD6/RE6                                                                                      |           |      | B30              | D+                          |     |

| B3               | EBIA6/AN22/RPC1/PMA6/RC1                                                                                 |           |      | B31              | RPF2/SDA3/RF2               |     |

| B4               | AN36/ETXD1/RJ9                                                                                           |           |      | B32              | ERXD0/RH8                   |     |

| B5               | EBIWE/AN20/RPC3/PMWR/RC3                                                                                 |           |      | B33              | ECOL/RH10                   |     |

| B6               | AN14/C1IND/RPG6/SCK2/RG6                                                                                 |           |      | B34              | EBIRDY1/SDA2/RA3            |     |

| B7               | EBIA3/AN12/C2IND/RPG8/SCL4/PMA3/RG8                                                                      |           |      | B35              | Vdd                         |     |

| B8               | VDD                                                                                                      |           |      | B36              | EBIA9/RPF4/SDA5/PMA9/RF4    |     |

| B9               | EBIA2/AN11/C2INC/RPG9/PMA2/RG9                                                                           |           |      | B37              | RPA14/SCL1/RA14             |     |

| B10              | AN25/RPE8/RE8                                                                                            |           |      | B38              | EBIA15/RPD9/PMCS2/PMA15/RD9 |     |

| B11              | AN45/C1INA/RPB5/RB5                                                                                      |           |      | B39              | EMDC/RPD11/RD11             |     |

| B12              | AN37/ERXCLK/EREFCLK/RJ11                                                                                 |           |      | B40              | ERXDV/ECRSDV/RH13           |     |

| B13              | Vss                                                                                                      |           |      | B41              | SOSCI/RPC13/RC13            |     |

| B14              | PGEC2/AN46/RPB6/RB6                                                                                      |           |      | B42              | EBID14/RPD2/PMD14/RD2       |     |

| B15              | Vref-/CVref-/AN27/RA9                                                                                    |           |      | B43              | EBID12/RPD12/PMD12/RD12     |     |

| B16              | AVdd                                                                                                     |           |      | B44              | ETXERR/RJ0                  |     |

| B17              | AN38/ETXD2/RH0                                                                                           |           |      | B45              | EBIRDY3/RJ2                 |     |

| B18              | EBIA10/AN48/RPB8/PMA10/RB8                                                                               |           |      | B46              | SQICS1/RPD5/RD5             |     |

| B19              | EBIA13/CVREFOUT/AN5/RPB10/PMA13/RB10                                                                     |           |      | B47              | ETXCLK/RPD7/RD7             |     |

| B20              | Vss                                                                                                      |           |      | B48              | Vss                         |     |

| B21              | TCK/EBIA19/AN29/RA1                                                                                      |           |      | B49              | EBID10/RPF1/PMD10/RF1       |     |

| B22              | TDO/EBIA17/AN31/RPF12/RF12                                                                               |           |      | B50              | EBID8/RPG0/PMD8/RG0         |     |

| B23              | AN8/RB13                                                                                                 |           |      | B51              | TRD3/SQID3/RA7              |     |

| B24              | EBIA0/AN10/RPB15/OCFB/PMA0/RB15                                                                          |           |      | B52              | EBID0/PMD0/RE0              |     |

| B25              | Vdd                                                                                                      |           |      | B53              | Vdd                         |     |

| B26              | AN41/ERXD1/RH5                                                                                           |           |      | B54              | TRD2/SQID2/RG14             |     |

| B27              | AN32/AETXD0/RPD14/RD14                                                                                   |           |      | B55              | TRD0/SQID0/RG13             |     |

| B28              | OSC1/CLKI/RC12                                                                                           |           |      | B56              | EBID3/RPE3/PMD3/RE3         |     |

#### TABLE 4: **PIN NAMES FOR 124-PIN DEVICES (CONTINUED)**

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.4 "Peripheral Pin Select (PPS)" for restrictions.

2:

Every I/O port pin (RAx-RJx) can be used as a change notification pin (CNAx-CNJx). See Section 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-1             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | PWPULOCK          | —                 | _                 | —                 | —                 |                   | _                | _                |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | PWP<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   | PWP<              | 15:8>             |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | 7:0 PWP<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### **REGISTER 5-7:** NVMPWP: PROGRAM FLASH WRITE-PROTECT REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 PWPULOCK: Program Flash Memory Page Write-protect Unlock bit

1 = Register is not locked and can be modified

0 = Register is locked and cannot be modified

This bit is only clearable and cannot be set except by any reset.

bit 30-24 Unimplemented: Read as '0'

bit 23-0 PWP<23:0>: Flash Program Write-protect (Page) Address bits

Physical memory below address 0x1Dxxxxxx is write protected, where 'xxxxxx' is specified by PWP<23:0>. When PWP<23:0> has a value of '0', write protection is disabled for the entire program Flash. If the specified address falls within the page, the entire page and all pages below the current page will be protected.

Note: The bits in this register are only writable when the NVMKEY unlock sequence is followed.

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>¢)                  | <b>b</b>                        | e         |       |       |       |       |       | - /   |      | Bi         | ts   |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

| 0864                        | OFF201                          | 31:16     | —     | —     | —     | —     | _     | _     |      | —          |      | —    |      | —    | —    | _    | VOFF< | 17:16> | 0000       |

| 0004                        | 011201                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0868                        | OFF202                          | 31:16     | —     | —     | —     | _     | _     | —     | —    | —          | -    | —    | -    | —    | —    | _    | VOFF< | 17:16> | 0000       |

| 0000                        | 011202                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0874                        | OFF205                          | 31:16     | —     | —     | —     | _     | _     | —     |      | —          |      | —    |      | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0074                        | 011203                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0070                        | OFF206                          | 31:16     | _     | —     | —     | _     | _     | _     |      | _          |      | —    |      | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0878                        | OFF200                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0870                        | OFF207                          | 31:16     | —     | —     | —     | _     | _     | —     | —    | —          | -    | —    | -    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0070                        | 0FF207                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0000                        | OFF208                          | 31:16     | _     | —     | _     | _     | _     | _     |      | _          |      | _    |      | —    | —    | _    | VOFF< | 17:16> | 0000       |

| 0880                        | OFF200                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0004                        | OFF209                          | 31:16     | _     | —     | _     | _     | -     | -     | -    | _          | -    | —    | -    | —    | -    | _    | VOFF< | 17:16> | 0000       |

| 0004                        | 0FF209                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0000                        | OFF210                          | 31:16     | -     | _     | _     | -     | -     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0000                        | OFF210                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0004                        | 055040                          | 31:16     | —     | _     | —     | —     | —     | _     | —    | _          | —    | —    | —    | —    | _    | _    | VOFF< | 17:16> | 0000       |

| 0894                        | OFF213                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

Legend: x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

This bit or register is not available on devices without a CAN module. 3:

This bit or register is not available on 100-pin devices. 4:

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

6: 7: This bit or register is not available on devices without a Crypto module.

8: This bit or register is not available on 124-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 31:24        | _                 |                   | _                 | -                 | _                 | _                   | —                | —                |

| 00.40        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 |                   | _                   | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                   | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 |                   |                   | TUN<              | 5:0> <sup>(1)</sup> |                  |                  |

# REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

# Legend:

| · J · · ·         |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized nor tested.

| Note: | Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced |

|-------|-----------------------------------------------------------------------------------------------------|

|       | PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.                               |

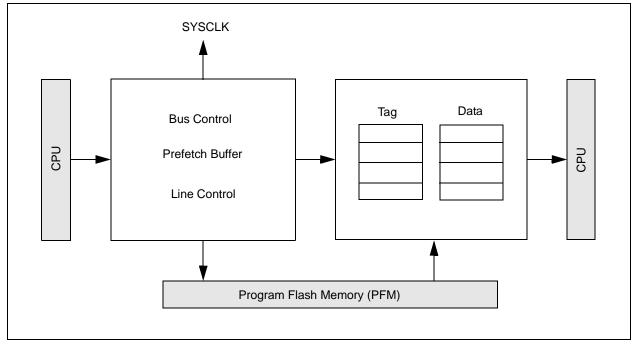

# 9.0 PREFETCH MODULE

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Prefetch module is a performance enhancing module that is included in the PIC32MZ EF family of devices. When running at high-clock rates, Wait states must be inserted into Program Flash Memory (PFM) read transactions to meet the access time of the PFM. Wait states can be hidden to the core by prefetching and storing instructions in a temporary holding area that the CPU can access quickly. Although the data path to the CPU is 32 bits wide, the data path to the PFM is 128 bits wide. This wide data path provides the same bandwidth to the CPU as a 32-bit path running at four times the frequency.

The Prefetch module holds a subset of PFM in temporary holding spaces known as lines. Each line contains a tag and data field. Normally, the lines hold a copy of what is currently in memory to make instructions or data available to the CPU without Flash Wait states.

The following are key features of the Prefetch module:

- 4x16 byte fully-associative lines

- One line for CPU instructions

- · One line for CPU data

- Two lines for peripheral data

- 16-byte parallel memory fetch

- Configurable predictive prefetch

- Error detection and correction

A simplified block diagram of the Prefetch module is shown in Figure 9-1.

## FIGURE 9-1: PREFETCH MODULE BLOCK DIAGRAM

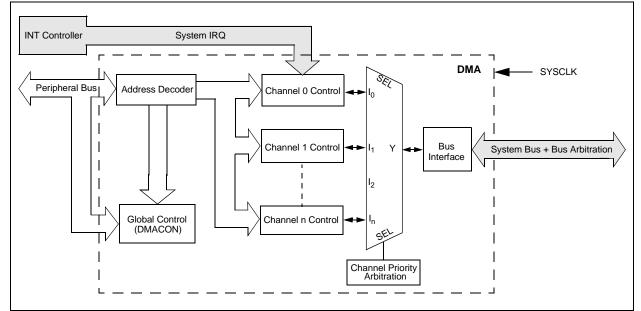

# 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Direct Memory Access (DMA) Controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the device such as SPI, UART, PMP, etc., or memory itself.

The following are key features of the DMA Controller:

- Eight identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

# FIGURE 10-1: DMA BLOCK DIAGRAM

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Up to 2-byte Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent error address accessed by a DMA channel

- Most recent DMA channel to transfer data

- CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | -                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 |                   | —                 |                   |                  | —                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   | _                 | _                 |                   |                  | _                |

## REGISTER 10-1: DMACON: DMA CONTROLLER CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** DMA On bit

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 Unimplemented: Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

- bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active and is transferring data

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

# REGISTER 11-13: USBOTG: USB OTG CONTROL/STATUS REGISTER (CONTINUED)

bit 0 SESSION: Active Session Control/Status bit

- 'A' device:

- 1 = Start a session

- 0 = End a session

'B' device:

1 = (Read) Session has started or is in progress, (Write) Initiate the Session Request Protocol

0 = When USB module is in Suspend mode, clearing this bit will cause a software disconnect

Clearing this bit when the USB module is not suspended will result in undefined behavior.

# TABLE 12-20: PORTJ REGISTER MAP FOR 144-PIN DEVICES ONLY

| ess                         |                                 | 0         |               |               |               |               |                |               |              | Bits         |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|----------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11          | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0800                        | ANSELJ                          | 31:16     |               | _             | _             | _             | _              | —             |              | _            | -            | —            |              | -            | -            | —            | —            | —            | 0000          |

| 0000                        | ANOLLJ                          | 15:0      | —             | —             | —             | —             | ANSJ11         | —             | ANSJ9        | ANSJ8        | _            | —            | _            | _            |              | —            | —            | —            | 0B00          |

| 0810                        | TRISJ                           | 31:16     | —             | —             | —             | —             | _              | —             | _            | _            | _            | —            | _            | _            |              | —            |              | —            | 0000          |

| 0010                        | 11(100                          | 15:0      | TRISJ15       | TRISJ14       | TRISJ13       | TRISJ12       | TRISJ11        | TRISJ10       | TRISJ9       | TRISJ8       | TRISJ7       | TRISJ6       | TRISJ5       | TRISJ4       | TRISJ3       | TRISJ2       | TRISJ1       | TRISJ0       | FFFF          |

| 0820                        | PORTJ                           | 31:16     | —             | —             | —             | —             | _              | —             | _            | _            | _            | —            | _            | _            |              | —            |              | —            | 0000          |

| 0020                        | 1 OKI3                          | 15:0      | RJ15          | RJ14          | RJ13          | RJ12          | RJ11           | RJ10          | RJ9          | RJ8          | RJ7          | RJ6          | RJ5          | RJ4          | RJ3          | RJ2          | RJ1          | RJ0          | xxxx          |

| 0830                        | LATJ                            | 31:16     | —             | —             | —             | —             | —              | —             | -            | _            | _            | —            | -            | —            | -            | —            | —            | —            | 0000          |

| 0000                        | LAIS                            | 15:0      | LATJ15        | LATJ14        | LATJ13        | LATJ12        | LATJ11         | LATJ10        | LATJ9        | LATJ8        | LATJ7        | LATJ6        | LATJ5        | LATJ4        | LATJ3        | LATJ2        | LATJ1        | LATJ0        | xxxx          |

| 0840                        | ODCJ                            | 31:16     | —             | —             | —             | —             | —              | —             | -            | _            | _            | —            | -            | —            | -            | —            | —            | —            | 0000          |

| 0040                        | 0000                            | 15:0      | ODCJ15        | ODCJ14        | ODCJ13        | ODCJ12        | ODCJ11         | ODCJ10        | ODCJ9        | ODCJ18       | ODCJ7        | ODCJ6        | ODCJ5        | ODCJ4        | ODCJ3        | ODCJ2        | ODCJ1        | ODCJ0        | 0000          |

| 0850                        | CNPUJ                           | 31:16     | —             | —             | —             | —             | —              | —             | -            | _            | _            | —            | -            | —            | -            | —            | —            | —            | 0000          |

| 0000                        |                                 | 15:0      | CNPUJ15       | CNPUJ14       | CNPUJ13       | CNPUJ12       | CNPUJ11        | CNPUJ10       | CNPUJ9       | CNPUJ8       | CNPUJ7       | CNPUJ6       | CNPUJ5       | CNPUJ4       | CNPUJ3       | CNPUJ2       | CNPUJ1       | CNPUJ0       | 0000          |

| 0860                        | CNPDJ                           | 31:16     | —             | —             | —             | —             | —              | —             | -            | _            | _            | —            | -            | —            | -            | —            | —            | —            | 0000          |

| 0000                        |                                 | 15:0      | CNPDJ15       | CNPDJ14       | CNPDJ13       | CNPDJ12       | CNPDJ11        | CNPDJ10       | CNPDJ9       | CNPDJ8       | CNPDJ7       | CNPDJ6       | CNPDJ5       | CNPDJ4       | CNPDJ3       | CNPDJ2       | CNPDJ1       | CNPDJ0       | 0000          |

|                             |                                 | 31:16     | —             | —             | —             | —             | —              | —             | -            | _            | _            | —            | -            | —            | -            | —            | —            | —            | 0000          |

| 0870                        | CNCONJ                          | 15:0      | ON            | -             | -             | -             | EDGE<br>DETECT | —             | _            | —            | —            | -            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 31:16     | _             | _             | _             | _             | _              | _             |              | -            |              | _            |              |              |              | —            | _            | _            | 0000          |

| 0880                        | CNENJ                           | 15:0      | CNENJ15       | CNENJ14       | CNENJ13       | CNENJ12       | CNENJ11        | CNENJ10       | CNENJ9       | CNENJ8       | CNENJ7       | CNENJ6       | CNENJ5       | CNENJ4       | CNENJ3       | CNENJ2       | CNENJ1       | CNENJ0       | 0000          |

|                             |                                 | 31:16     | _             | _             | _             | _             | _              | _             |              |              | -            | _            |              | -            | -            | _            | _            | _            | 0000          |

| 0890                        | CNSTATJ                         | 15:0      | CN<br>STATJ15 | CN<br>STATJ14 | CN<br>STATJ13 | CN<br>STATJ12 | CN<br>STATJ11  | CN<br>STATJ10 | CN<br>STATJ9 | CN<br>STATJ8 | CN<br>STATJ7 | CN<br>STATJ6 | CN<br>STATJ5 | CN<br>STATJ4 | CN<br>STATJ3 | CN<br>STATJ2 | CN<br>STATJ1 | CN<br>STATJ0 | 0000          |

| 0040                        |                                 | 31:16     | _             | _             | _             | _             | _              | _             |              | _            | _            | _            |              | -            | -            | _            | _            | _            | 0000          |

| 08A0                        | CNNEJ                           | 15:0      | CNNEJ15       | CNNEJ14       | CNNEJ13       | CNNEJ12       | CNNEJ11        | CNNEJ10       | CNNEJ9       | CNNEJ8       | CNNEJ7       | CNNEJ6       | CNNEJ5       | CNNEJ4       | CNNEJ3       | CNNEJ2       | CNNEJ1       | CNNEJ0       | 0000          |

| 0000                        |                                 | 31:16     | _             | _             | _             | _             |                | _             |              |              |              | _            |              |              |              | _            | _            | _            | 0000          |

| 08B0                        | CNFJ                            | 15:0      | CNFJ15        | CNFJ14        | CNFJ13        | CNFJ12        | CNFJ11         | CNFJ10        | CNFJ9        | CNFJ8        | CNFJ7        | CNFJ6        | CNFJ5        | CNFJ4        | CNFJ3        | CNFJ2        | CNFJ1        | CNFJ0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

# **REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER ('x' = 2-9) (CONTINUED)**

bit 2 Unimplemented: Read as '0'

- bit 1 TCS: Timer Clock Source Select bit<sup>(1)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, Timer5, Timer7, and Timer9). All timer functions are set through the even numbered timers.

- 2: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

- 3: This bit is available only on even numbered timers (Timer2, Timer4, Timer6, and Timer8).

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | —                    | —                 | -                 | —                 | —                        | —                 | _                | —                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | —                    | —                 | -                 | —                 | —                        | —                 | _                | —                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 0.61         | SPISGNEXT            | —                 | -                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

| 7:0          | AUDEN <sup>(1)</sup> | —                 | _                 | —                 | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | <1:0> <sup>(1,2)</sup> |

# REGISTER 19-2: SPIxCON2: SPI CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | SPISGNEXT: Sign Extend Read Data from the RX FIFO bit                                                                                        |

|           | 1 = Data from RX FIFO is sign extended                                                                                                       |

|           | 0 = Data from RX FIFO is not sign extended                                                                                                   |

| bit 14-13 | Unimplemented: Read as '0'                                                                                                                   |

| bit 12    | FRMERREN: Enable Interrupt Events via FRMERR bit                                                                                             |

|           | 1 = Frame Error overflow generates error events                                                                                              |

|           | 0 = Frame Error does not generate error events                                                                                               |

| bit 11    | SPIROVEN: Enable Interrupt Events via SPIROV bit                                                                                             |

|           | 1 = Receive overflow generates error events                                                                                                  |

|           | 0 = Receive overflow does not generate error events                                                                                          |

| bit 10    | SPITUREN: Enable Interrupt Events via SPITUR bit                                                                                             |

|           | 1 = Transmit Underrun Generates Error Events                                                                                                 |

|           | 0 = Transmit Underrun Does Not Generates Error Events                                                                                        |

| bit 9     | IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)                                                                           |

|           | 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data                                            |

|           | 0 = A ROV is a critical error which stop SPI operation                                                                                       |

| bit 8     | IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions)                                                                          |

|           | 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty                                                   |

| 1.1.7     | 0 = A TUR is a critical error which stop SPI operation                                                                                       |

| bit 7     | AUDEN: Enable Audio CODEC Support bit <sup>(1)</sup>                                                                                         |

|           | 1 = Audio protocol is enabled<br>0 = Audio protocol is disabled                                                                              |

| bit 6-5   | ·                                                                                                                                            |

|           | Unimplemented: Read as '0'                                                                                                                   |

| bit 3     | AUDMONO: Transmit Audio Data Format bit <sup>(1,2)</sup>                                                                                     |

|           | <ul> <li>1 = Audio data is mono (Each data word is transmitted on both left and right channels)</li> <li>0 = Audio data is stereo</li> </ul> |

| bit 2     | Unimplemented: Read as '0'                                                                                                                   |

| bit 1-0   | AUDMOD<1:0>: Audio Protocol Mode bit <sup>(1,2)</sup>                                                                                        |

| bit i o   | 11 = PCM/DSP mode                                                                                                                            |

|           | 10 = Right Justified mode                                                                                                                    |

|           | 01 = Left Justified mode                                                                                                                     |

|           | $00 = I^2 S \text{ mode}$                                                                                                                    |

|           |                                                                                                                                              |

|           |                                                                                                                                              |

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

| <b>TABLE 22-1:</b> | UART1 THROUGH UART6 REGISTER MAP (CONTINUED) |

|--------------------|----------------------------------------------|

|--------------------|----------------------------------------------|

| ess                         |                       |           |        |                                                                                    |        |       |        |       |       | Bi          | ts          |         |       |          |          |      |        |       | 6          |

|-----------------------------|-----------------------|-----------|--------|------------------------------------------------------------------------------------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name      | Bit Range | 31/15  | 30/14                                                                              | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 2600                        | U4MODE <sup>(1)</sup> | 31:16     | —      |                                                                                    | _      | _     |        | _     | -     | —           | _           | _       | —     | —        | —        | —    | —      | -     | 0000       |

| 2000                        | OHNODE                | 15:0      | ON     | _                                                                                  | SIDL   | IREN  | RTSMD  | —     | UEN   |             | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 2610                        | U4STA <sup>(1)</sup>  | 31:16     |        | —                                                                                  | —      | —     | —      | —     | _     | ADM_EN      |             |         |       | ADDR     |          | -    | -      |       | 0000       |

| 2010                        | 01017                 | 15:0      | UTXISE | L<1:0>                                                                             | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 2620                        | U4TXREG               | 31:16     | —      | —                                                                                  | —      | —     | —      | —     | _     | —           | —           | —       | —     |          | —        | —    | —      | —     | 0000       |

| 2020                        | OTINILO               | 15:0      | _      | —                                                                                  | —      | —     | —      | —     |       | TX8         |             | -       |       | Transmit | Register | -    | -      |       | 0000       |

| 2630                        | U4RXREG               | 31:16     | _      | —                                                                                  | —      | —     | —      | —     |       | —           | —           | —       | —     |          | —        | —    | —      | —     | 0000       |

| 2030                        | OHININEO              | 15:0      | —      | -                                                                                  | —      | —     | —      | —     | -     | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 2640                        | U4BRG <sup>(1)</sup>  | 31:16     | —      | _                                                                                  | _      | —     | —      | _     | -     | —           | —           | —       | —     | —        | —        | —    | —      | _     | 0000       |

| 2040                        | 040100                | 15:0      |        |                                                                                    |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 2800                        | U5MODE <sup>(1)</sup> | 31:16     | _      |                                                                                    | _      |       | _      | _     |       | —           | —           | _       | _     | _        | _        | _    | _      |       | 0000       |

| 2000                        | 03WODL                | 15:0      | ON     |                                                                                    | SIDL   | IREN  | RTSMD  | Ι     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 2810                        | U5STA <sup>(1)</sup>  | 31:16     | _      | _                                                                                  | -      | —     | —      |       | -     | ADM_EN      |             |         |       | ADDR     | R<7:0>   |      |        |       | 0000       |

| 2010                        | 055TA* 7              | 15:0      | UTXISE | L<1:0>                                                                             | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 2820                        | U5TXREG               | 31:16     | _      | _                                                                                  | —      | _     | —      |       | _     | —           | _           | —       | —     | _        | _        | _    | —      | _     | 0000       |

| 2820                        | USIAREG               | 15:0      | _      | _                                                                                  | —      | —     | —      | —     | _     | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 2020                        | U5RXREG               | 31:16     | _      | _                                                                                  | —      | —     | —      | —     | _     | —           | _           | —       | —     | _        | —        | —    | —      | —     | 0000       |

| 2830                        | USKAREG               | 15:0      | _      | _                                                                                  | _      | —     | —      | _     | _     | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 2840                        | U5BRG <sup>(1)</sup>  | 31:16     | _      | _                                                                                  | —      | —     | —      | —     | _     | —           | _           | —       | —     | _        | —        | —    | —      | —     | 0000       |

| 2840                        | USBKG'                | 15:0      |        |                                                                                    |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| 0.4.00                      | U6MODE <sup>(1)</sup> | 31:16     | _      | —                                                                                  | _      | —     | —      | _     | _     | —           | _           | _       | —     | _        | _        | _    | —      | —     | 0000       |

| 2A00                        | U6MODE                | 15:0      | ON     |                                                                                    | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 2A10                        | U6STA <sup>(1)</sup>  | 31:16     | —      | -                                                                                  | _      | —     | —      | _     |       | ADM_EN      |             |         |       | ADDR     | 8<7:0>   |      |        |       | 0000       |

| 2A 10                       | 0651A.7               | 15:0      | UTXISE | L<1:0>                                                                             | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 0.4.00                      |                       | 31:16     | —      | —                                                                                  | —      | —     | —      | _     |       | —           | —           | —       | —     | —        | —        | —    | —      | -     | 0000       |

| 2A20                        | U6TXREG               | 15:0      | —      | -                                                                                  | _      | _     | —      | _     |       | TX8         |             |         |       | Transmit | Register |      |        |       | 0000       |

| 0.4.00                      |                       | 31:16     | _      | _                                                                                  | —      | —     | —      | _     | _     | —           | —           | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 2A30                        | U6RXREG               | 15:0      | _      | —                                                                                  | _      | —     | _      | _     | _     | RX8         |             |         |       | Receive  | Register |      |        |       | 0000       |

| 04.40                       |                       | 31:16     | _      | _                                                                                  | —      | _     | _      | _     | _     | —           | _           | —       | —     |          | _        | —    | —      |       | 0000       |

| 2A40                        | U6BRG <sup>(1)</sup>  | 15:0      |        |                                                                                    |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |      |        |       | 0000       |

| Legen                       | al                    | - 1       |        | le on Reset: — = unimplemented, read as '0'. Reset values are shown in hexadecimal |        |       |        |       |       |             |             |         |       |          |          |      |        |       |            |

**1**: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                   | —                 | _                 | —                 | _                 | -                 | —                | —                     |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                 | —                 | _                 | —                 | —                 | -                 | —                | —                     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 15:8         |                   | —                 | _                 | _                 | _                 | _                 | —                | —                     |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          |                   |                   |                   | _                 | AREIE             | PKTIE             | BDPIE            | PENDIE <sup>(1)</sup> |

# REGISTER 26-7: CEINTEN: CRYPTO ENGINE INTERRUPT ENABLE REGISTER

## Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-4 Unimplemented: Read as '0'

- bit 3 AREIE: Access Response Error Interrupt Enable bit

- 1 = Access response error interrupts are enabled

- 0 = Access response error interrupts are not enabled

- bit 2 PKTIE: DMA Packet Completion Interrupt Enable bit

- 1 = DMA packet completion interrupts are enabled

- 0 = DMA packet completion interrupts are not enabled

- bit 1 BDPIE: DMA Buffer Descriptor Processor Interrupt Enable bit

- 1 = BDP interrupts are enabled

- 0 = BDP interrupts are not enabled

- bit 0 **PENDIE:** Master Interrupt Enable bit<sup>(1)</sup>

- 1 = Crypto Engine interrupts are enabled

- 0 = Crypto Engine interrupts are not enabled

Note 1: The PENDIE bit is a global enable bit and must be enabled together with the other interrupts desired.

# REGISTER 28-1: ADCCON1: ADC CONTROL REGISTER 1 (CONTINUED)

bit 3 STRGLVL: Scan Trigger High Level/Positive Edge Sensitivity bit

- 1 = Scan trigger is high level sensitive. Once STRIG mode is selected (TRGSRCx<4:0> in the ADCTRGx register), the scan trigger will continue for all selected analog inputs, until the STRIG option is removed.

- 0 = Scan trigger is positive edge sensitive. Once STRIG mode is selected (TRGSRCx<4:0> in the ADCTRGx register), only a single scan trigger will be generated, which will complete the scan of all selected analog inputs.

- bit 2-0 Unimplemented: Read as '0'

# REGISTER 28-6: ADCIMCON2: ADC INPUT MODE CONTROL REGISTER 2 (CONTINUED)

| REGISTER | 20-0. ADCINICONZ. ADC INFUT IN                          |

|----------|---------------------------------------------------------|

| bit 21   | DIFF26: AN26 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN26 is using Differential mode                     |

|          | 0 = AN26 is using Single-ended mode                     |

| bit 20   | <b>SIGN26:</b> AN26 Signed Data Mode bit <sup>(1)</sup> |

|          | 1 = AN26 is using Signed Data mode                      |

|          | 0 = AN26 is using Unsigned Data mode                    |

| bit 19   | DIFF25: AN25 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN25 is using Differential mode                     |

|          | 0 = AN25 is using Single-ended mode                     |

| bit 18   | SIGN25: AN25 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN25 is using Signed Data mode                      |

|          | 0 = AN25 is using Unsigned Data mode                    |

| bit 17   | DIFF24: AN24 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN24 is using Differential mode                     |

|          | 0 = AN24 is using Single-ended mode                     |

| bit 16   | SIGN24: AN24 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN24 is using Signed Data mode                      |

|          | 0 = AN24 is using Unsigned Data mode                    |

| bit 15   | DIFF23: AN23 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN23 is using Differential mode                     |

|          | 0 = AN23 is using Single-ended mode                     |

| bit 14   | SIGN23: AN23 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN23 is using Signed Data mode                      |

|          | 0 = AN23 is using Unsigned Data mode                    |

| bit 13   | DIFF22: AN22 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN22 is using Differential mode                     |

|          | 0 = AN22 is using Single-ended mode                     |

| bit 12   | SIGN22: AN22 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN22 is using Signed Data mode                      |

|          | 0 = AN22 is using Unsigned Data mode                    |

| bit 11   | DIFF21: AN21 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN21 is using Differential mode                     |

|          | 0 = AN21 is using Single-ended mode                     |

| bit 10   | SIGN21: AN21 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN21 is using Signed Data mode                      |

|          | 0 = AN21 is using Unsigned Data mode                    |

| bit 9    | DIFF20: AN20 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN20 is using Differential mode                     |

|          | 0 = AN20 is using Single-ended mode                     |

| bit 8    | SIGN20: AN20 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN20 is using Signed Data mode                      |

|          | 0 = AN20 is using Unsigned Data mode                    |

| bit 7    | DIFF19: AN19 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN19 is using Differential mode                     |

|          | 0 = AN19 is using Single-ended mode                     |

|          |                                                         |

Note 1: This bit is not available on 64-pin devices.

| Peripheral               | PMDx bit Name | Register Name and Bit Location |

|--------------------------|---------------|--------------------------------|

| UART3                    | U3MD          | PMD5<2>                        |

| UART4                    | U4MD          | PMD5<3>                        |

| UART5                    | U5MD          | PMD5<4>                        |

| UART6                    | U6MD          | PMD5<5>                        |

| SPI1                     | SPI1MD        | PMD5<8>                        |

| SPI2                     | SPI2MD        | PMD5<9>                        |

| SPI3                     | SPI3MD        | PMD5<10>                       |

| SPI4                     | SPI4MD        | PMD5<11>                       |

| SPI5                     | SPI5MD        | PMD5<12>                       |

| SPI6                     | SPI6MD        | PMD5<13>                       |

| I2C1                     | I2C1MD        | PMD5<16>                       |

| I2C2                     | I2C2MD        | PMD5<17>                       |

| 12C3                     | I2C3MD        | PMD5<18>                       |

| I2C4                     | I2C4MD        | PMD5<19>                       |

| 12C5                     | I2C5MD        | PMD5<20>                       |

| USB <sup>(2)</sup>       | USBMD         | PMD5<24>                       |

| CAN1                     | CAN1MD        | PMD5<28>                       |

| CAN2                     | CAN2MD        | PMD5<29>                       |

| RTCC                     | RTCCMD        | PMD6<0>                        |

| Reference Clock Output 1 | REFO1MD       | PMD6<8>                        |

| Reference Clock Output 2 | REFO2MD       | PMD6<9>                        |

| Reference Clock Output 3 | REFO3MD       | PMD6<10>                       |

| Reference Clock Output 4 | REFO4MD       | PMD6<11>                       |

| PMP                      | PMPMD         | PMD6<16>                       |

| EBI                      | EBIMD         | PMD6<17>                       |

| SQI1                     | SQI1MD        | PMD6<23>                       |

| Ethernet                 | ETHMD         | PMD6<28>                       |

| DMA                      | DMAMD         | PMD7<4>                        |

| Random Number Generator  | RNGMD         | PMD7<20>                       |

| Crypto                   | CRYPTMD       | PMD7<22>                       |

# TABLE 33-1: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS<sup>(1)</sup> (CONTINUED)

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the lists of available peripherals.

2: Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

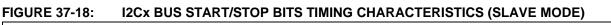

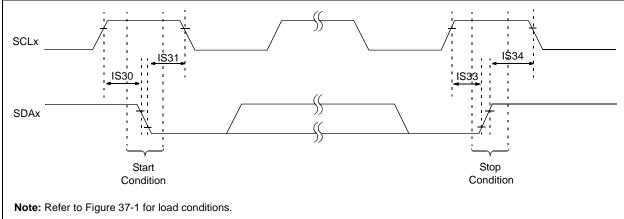

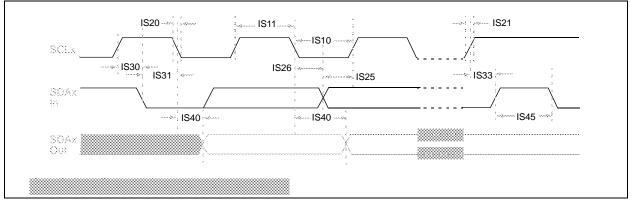

| AC CHARACTERISTICS                   |         |                 |                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |       |                                               |  |  |

|--------------------------------------|---------|-----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------------------|--|--|

| Param.<br>No. Symbol Characteristics |         |                 | eristics               | Min.                                                                                                                                                                                                                                                                                | Max. | Units | Conditions                                    |  |  |

| IS10                                 | TLO:SCL | Clock Low Time  | 100 kHz mode           | 4.7                                                                                                                                                                                                                                                                                 | -    | μs    | PBCLK must operate at a minimum of 800 kHz    |  |  |

|                                      |         |                 | 400 kHz mode           | 1.3                                                                                                                                                                                                                                                                                 | —    | μs    | PBCLK must operate at a<br>minimum of 3.2 MHz |  |  |

|                                      |         |                 | 1 MHz mode<br>(Note 1) | 0.5                                                                                                                                                                                                                                                                                 | —    | μs    | _                                             |  |  |

| IS11                                 | THI:SCL | Clock High Time | 100 kHz mode           | 4.0                                                                                                                                                                                                                                                                                 | _    | μs    | PBCLK must operate at a<br>minimum of 800 kHz |  |  |

|                                      |         |                 | 400 kHz mode           | 0.6                                                                                                                                                                                                                                                                                 | —    | μs    | PBCLK must operate at a minimum of 3.2 MHz    |  |  |

|                                      |         |                 | 1 MHz mode<br>(Note 1) | 0.5                                                                                                                                                                                                                                                                                 | —    | μs    | —                                             |  |  |

| AC CHARACTERISTICS |        |                     | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |            |     |       |               |  |  |

|--------------------|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-------|---------------|--|--|

| Param.<br>No.      | Symbol | Characteristics     | Min.                                                                                                                                                                                                                                                                                           | Conditions |     |       |               |  |  |

| TS10               | Vts    | Rate of Change      | —                                                                                                                                                                                                                                                                                              | +5         | _   | mV/ºC | —             |  |  |

| TS11               | TR     | Resolution          | —                                                                                                                                                                                                                                                                                              | ±5         | —   | °C    | —             |  |  |

| TS12               | IVtemp | Voltage Range       | 0.5                                                                                                                                                                                                                                                                                            | —          | 1.5 | V     | —             |  |  |

| TS13               | TMIN   | Minimum Temperature | —                                                                                                                                                                                                                                                                                              | -40        | _   | °C    | IVTEMP = 0.5V |  |  |

| TS14               | Тмах   | Maximum Temperature |                                                                                                                                                                                                                                                                                                | 160        |     | °C    | IVTEMP = 1.5V |  |  |

# TABLE 37-41: TEMPERATURE SENSOR SPECIFICATIONS

**Note 1:** The temperature sensor is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

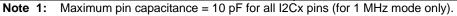

# FIGURE 37-22: PARALLEL MASTER PORT READ TIMING DIAGRAM

## TABLE 37-43: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                      |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |       |            |  |  |  |

|--------------------|---------|----------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min. | Тур.                                                                                                                                                                                                                                                                                | Max. | Units | Conditions |  |  |  |

| PM1                | TLAT    | PMALL/PMALH Pulse Width                                              | —    | 1 TPBCLK2                                                                                                                                                                                                                                                                           | _    | _     |            |  |  |  |