Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efk100-i-pt |

### **Table of Contents**

| 1.0   | Device Overview                                                                             | 15  |

|-------|---------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit Microcontrollers                                 | 37  |

| 3.0   | CPU                                                                                         | 43  |

| 4.0   | Memory Organization                                                                         | 61  |

| 5.0   | Flash Program Memory                                                                        | 99  |

| 6.0   | Resets                                                                                      | 109 |

| 7.0   | CPU Exceptions and Interrupt Controller                                                     | 115 |

| 8.0   | Oscillator Configuration                                                                    | 153 |

| 9.0   | Prefetch Module                                                                             | 169 |

| 10.0  | Direct Memory Access (DMA) Controller                                                       | 173 |

| 11.0  | Hi-Speed USB with On-The-Go (OTG)                                                           | 197 |

| 12.0  | I/O Ports                                                                                   | 247 |

| 13.0  | Timer1                                                                                      | 283 |

| 14.0  | Timer2/3, Timer4/5, Timer6/7, and Timer8/9                                                  | 287 |

| 15.0  | Deadman Timer (DMT)                                                                         | 293 |

| 16.0  | Watchdog Timer (WDT)                                                                        | 301 |

|       | Input Capture                                                                               |     |

| 18.0  | Output Compare                                                                              | 309 |

| 19.0  | Serial Peripheral Interface (SPI) and Inter-IC Sound (I <sup>2</sup> S)                     | 315 |

| 20.0  | Serial Quad Interface (SQI)                                                                 | 325 |

| 21.0  | Inter-Integrated Circuit (I <sup>2</sup> C)                                                 | 353 |

| 22.0  | Universal Asynchronous Receiver Transmitter (UART)                                          | 361 |

| 23.0  | Parallel Master Port (PMP)                                                                  | 369 |

| 24.0  | External Bus Interface (EBI)                                                                | 383 |

| 25.0  | Real-Time Clock and Calendar (RTCC)                                                         | 391 |

| 26.0  | Crypto Engine                                                                               | 401 |

| 27.0  | Random Number Generator (RNG)                                                               | 421 |

|       | 12-bit High-Speed Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) |     |

| 29.0  | Controller Area Network (CAN)                                                               | 485 |

| 30.0  | Ethernet Controller                                                                         | 523 |

| 31.0  | Comparator                                                                                  | 567 |

| 32.0  | Comparator Voltage Reference (CVREF)                                                        | 571 |

| 33.0  | Power-Saving Features                                                                       | 575 |

| 34.0  | Special Features                                                                            | 581 |

| 35.0  | Instruction Set                                                                             | 605 |

| 36.0  | Development Support                                                                         | 607 |

| 37.0  | Electrical Characteristics                                                                  | 611 |

| 38.0  | Extended Temperature Electrical Characteristics                                             | 663 |

| 39.0  | 252 MHz Electrical Characteristics                                                          | 669 |

| 40.0  | AC and DC Characteristics Graphs                                                            | 675 |

| 41.0  | Packaging Information                                                                       | 677 |

| The I | Microchip Web Site                                                                          | 733 |

|       | omer Change Notification Service                                                            |     |

|       | omer Support                                                                                |     |

| Prod  | uct Identification System                                                                   | 734 |

**I2C1 THROUGH I2C5 PINOUT I/O DESCRIPTIONS TABLE 1-10:**

|          |                        | Pin Nu          | mber                                                     |                          |                                            |                |                                            |

|----------|------------------------|-----------------|----------------------------------------------------------|--------------------------|--------------------------------------------|----------------|--------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA                                          | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type                                | Buffer<br>Type | Description                                |

|          |                        |                 |                                                          | Inte                     | er-Integr                                  | ated Circui    | t 1                                        |

| SCL1     | 44                     | 66              | B37                                                      | 95                       | I/O                                        | ST             | I2C1 Synchronous Serial Clock Input/Output |

| SDA1     | 43                     | 67              | A45                                                      | 96                       | I/O                                        | ST             | I2C1 Synchronous Serial Data Input/Output  |

|          |                        |                 |                                                          | Inte                     | er-Integra                                 | ated Circui    | t 2                                        |

| SCL2     | _                      | 59              | A41 85 I/O ST I2C2 Synchronous Serial Clock Input/Output |                          | I2C2 Synchronous Serial Clock Input/Output |                |                                            |

| SDA2     | _                      | 60              | B34                                                      | 86                       | I/O                                        | ST             | I2C2 Synchronous Serial Data Input/Output  |

|          |                        |                 |                                                          | Inte                     | er-Integra                                 | ated Circui    | t 3                                        |

| SCL3     | 51                     | 58              | A39                                                      | 80                       | I/O                                        | ST             | I2C3 Synchronous Serial Clock Input/Output |

| SDA3     | 50                     | 57              | B31                                                      | 79                       | I/O                                        | ST             | I2C3 Synchronous Serial Data Input/Output  |

|          |                        |                 |                                                          | Inte                     | er-Integra                                 | ated Circui    | t 4                                        |

| SCL4     | 6                      | 12              | В7                                                       | 16                       | I/O                                        | ST             | I2C4 Synchronous Serial Clock Input/Output |

| SDA4     | 5                      | 11              | A8                                                       | 15                       | I/O                                        | ST             | I2C4 Synchronous Serial Data Input/Output  |

|          | •                      | •               | •                                                        | Inte                     | er-Integra                                 | ated Circui    | t 5                                        |

| SCL5     | 42                     | 65              | A44                                                      | 91                       | I/O                                        | ST             | I2C5 Synchronous Serial Clock Input/Output |

| SDA5     | 41                     | 64              | B36                                                      | 90                       | I/O                                        | ST             | I2C5 Synchronous Serial Data Input/Output  |

Legend: CMOS = CMOS-compatible input or output Analog = Analog input

P = Power I = Input

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output

PPS = Peripheral Pin Select

**TABLE 1-11: COMPARATOR 1, COMPARATOR 2 AND CVREF PINOUT I/O DESCRIPTIONS**

|          |                        | Pin Nu          | mber            |                          |             |                |                                           |  |  |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-------------------------------------------|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                               |  |  |  |

|          |                        |                 |                 | Comp                     | arator Vo   | Itage Refe     | erence                                    |  |  |  |

| CVREF+   | 16                     | 29              | A20             | 40                       | I           | Analog         | Comparator Voltage Reference (High) Input |  |  |  |

| CVREF-   | 15                     | 28              | B15             | 39                       | I           | Analog         | Comparator Voltage Reference (Low) Input  |  |  |  |

| CVREFOUT | 23                     | 34              | B19             | 49                       | 0           | Analog         | Comparator Voltage Reference Output       |  |  |  |

|          |                        |                 |                 | Comp                     | arator 1    |                |                                           |  |  |  |

| C1INA    | 11                     | 20              | B11             | 25                       | I           | Analog         | Comparator 1 Positive Input               |  |  |  |

| C1INB    | 12                     | 21              | A13             | 26                       | I           | Analog         | Comparator 1 Selectable Negative Input    |  |  |  |

| C1INC    | 5                      | 11              | A8              | 15                       | I           | Analog         |                                           |  |  |  |

| C1IND    | 4                      | 10              | B6              | 14                       | I           | Analog         |                                           |  |  |  |

| C1OUT    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | Comparator 1 Output                       |  |  |  |

|          |                        | •               | •               | •                        | Comp        | arator 2       |                                           |  |  |  |

| C2INA    | 13                     | 22              | A14             | 31                       | I           | Analog         | Comparator 2 Positive Input               |  |  |  |

| C2INB    | 14                     | 23              | A16             | 34                       | I           | Analog         | Comparator 2 Selectable Negative Input    |  |  |  |

| C2INC    | 10                     | 16              | В9              | 21                       | I           | Analog         | 1                                         |  |  |  |

| C2IND    | 6                      | 12              | В7              | 16                       | I           | Analog         | 1                                         |  |  |  |

| C2OUT    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | Comparator 2 Output                       |  |  |  |

CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels Analog = Analog input

P = Power I = Input

TTL = Transistor-transistor Logic input buffer

O = Output

PPS = Peripheral Pin Select

| TABLE 4-9: | SYSTEM BUS TARGET 1 REGISTER MAP     | ) |

|------------|--------------------------------------|---|

| IMDLL 4-3. | SISILIVI DOS TANGLI I NEGISTEN IVIAR |   |

| SS                          |                  |           |       |       |       |          |          |       |       |      | Bits     |       |           |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|----------|-------|-----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5      | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| 8420                        | SBT1ELOG1        | 31:16     | MULTI | _     | _     | _        |          | CODE  | <3:0> |      | _        | _     | _         | _    | _      | _      | _       | _      | 0000          |

| 8420                        | SBITELOGI        | 15:0      |       |       |       | INI      | ΓID<7:0> |       |       |      |          | REGIO | N<3:0>    |      | _      | C      | MD<2:0> |        | 0000          |

| 8424                        | SBT1ELOG2        | 31:16     | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | _      | 0000          |

| 0424                        | SBTTLLOGZ        | 15:0      | 1     | _     | _     | _        | _        | _     | _     | -    | _        | -     | _         | _    | _      | _      | GROU    | P<1:0> | 0000          |

| 8428                        | SBT1ECON         | 31:16     | 1     | _     | _     | _        | _        | _     | _     | ERRP | _        | -     | _         | _    | _      | _      | _       | _      | 0000          |

| 0420                        | SBITECON         | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | _      | 0000          |

| 8430                        | SBT1ECLRS        | 31:16     | 1     | _     | _     | _        | _        | _     | _     | -    | _        | -     | _         | _    | _      | _      | _       | _      | 0000          |

| 0430                        | SBTTECERS        | 15:0      |       | _     | -     | _        | _        | _     | _     | 1    | -        | 1     | _         |      | _      | _      | _       | CLEAR  | 0000          |

| 8438                        | SBT1ECLRM        | 31:16     | I     | _     | -     | -        | _        | _     | _     | I    | _        | 1     | _         | 1    | _      | _      | _       | _      | 0000          |

| 0430                        | OBTILOLINI       | 15:0      |       | _     | -     | _        | _        | _     | _     | 1    | -        | 1     | _         |      | _      | _      | _       | CLEAR  | 0000          |

| 8440                        | SBT1REG0         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

| 0440                        | ODT INLO         | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | -    |          |       | SIZE<4:0: | >    |        | _      | _       | _      | xxxx          |

| 8450                        | SBT1RD0          | 31:16     |       | _     | -     | _        | _        | _     | _     | 1    | -        | 1     | _         |      | _      | _      | _       | _      | xxxx          |

| 0430                        | OBT INDO         | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8458                        | SBT1WR0          | 31:16     | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | _      | xxxx          |

| 0400                        | OBTIVILO         | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8480                        | SBT1REG2         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

| 0400                        | ODTINEOZ         | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | _    |          |       | SIZE<4:0: | >    |        | _      | _       | _      | xxxx          |

| 8490                        | SBT1RD2          | 31:16     | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | _      | xxxx          |

| 0430                        | OBTINDE          | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8498                        | SBT1WR2          | 31:16     | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | _      | _      | _       | _      | xxxx          |

| 0430                        | OBTIVILE         | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 84A0                        | SBT1REG3         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

| 00                          | 02111200         | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | -    |          | 1     | SIZE<4:0: | >    |        | _      | _       | _      | xxxx          |

| 84B0                        | SBT1RD3          | 31:16     | _     | _     | _     | _        | _        | _     | _     | -    | _        | _     | _         | _    | _      | _      | _       | _      | xxxx          |

| 0100                        | OBT INDO         | 15:0      | _     | _     | _     | _        | _        | _     | _     | -    | _        | _     | _         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 84B8                        | SBT1WR3          | 31:16     | _     | _     | _     | _        | _        | _     | _     | -    | _        | _     | _         | _    | _      | _      | _       | _      | xxxx          |

| 0.50                        | 02111110         | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    | _        | _     | _         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 84C0                        | SBT1REG4         | 31:16     |       |       |       |          |          |       |       |      |          | •     | xxxx      |      |        |        |         |        |               |

|                             |                  | 15:0      |       |       |       |          |          |       |       | _    | _        | _     | xxxx      |      |        |        |         |        |               |

| 84D0                        | SBT1RD4          | 31:16     | _     | _     | _     | _        | _        | _     | _     |      | _        |       | _         |      | _      | _      | _       | _      | xxxx          |

|                             |                  | 15:0      | _     | _     | _     | _        | _        | _     | _     |      | _        |       |           |      | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 84D8                        | SBT1WR4          | 31:16     | _     | _     | _     | _        | _        | _     | _     |      | _        |       |           |      | _      | _      | _       | _      | xxxx          |

|                             | 3=::::           | 15:0      | _     |       | _     |          | —        | _     |       | _    | _        | _     | _         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | XXXX          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note:

For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| u             |

|---------------|

| Ś             |

| တ             |

| 0             |

| 0             |

| 0             |

| _             |

| ω             |

| 2             |

| $\overline{}$ |

|               |

| ŏ             |

| ŏ             |

| à             |

| )D-pa         |

| )D-pag        |

| )D-page       |

| ĕ             |

| ĕ             |

| ĕ             |

| ĕ             |

TABLE 4-16: SYSTEM BUS TARGET 8 REGISTER MAP

| ess                         |                  |           |       |       |            |          |          |       |       |      | Bits     |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|------------|----------|----------|-------|-------|------|----------|-------|----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13      | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| A020                        | SBT8ELOG1        | 31:16     | MULTI | _     | _          | _        |          | CODE  | <3:0> |      | _        | _     | _        | _    | _      | _      | _       | _      | 0000          |

| A020                        | SBIGLLOGI        | 15:0      |       |       |            | INIT     | ΓID<7:0> |       |       |      |          | REGIO | N<3:0>   |      | _      | С      | MD<2:0> |        | 0000          |

| A024                        | SBT8ELOG2        | 31:16     | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 7024                        | OBTOLLOGE        | 15:0      | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | _      | _      | GROU    | P<1:0> | 0000          |

| A028                        | SBT8ECON         | 31:16     | _     | _     | _          | _        | _        | _     | _     | ERRP | _        | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 71020                       | OBTOLOGIV        | 15:0      | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | _      | _      | _       | _      | 0000          |

| A030                        | SBT8ECLRS        | 31:16     | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 71000                       | OBTOLOLINO       | 15:0      | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | _      | _      | _       | CLEAR  | 0000          |

| A038                        | SBT8ECLRM        | 31:16     | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 71000                       |                  | 15:0      | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | _      | _      | _       | CLEAR  | 0000          |

| A040                        | SBT8REG0         | 31:16     |       |       |            |          |          |       | 1     | BA   | SE<21:6> |       |          |      |        |        | ı       | 1      | xxxx          |

|                             |                  | 15:0      |       |       | BA         | \SE<5:0> |          | ı     | PRI   |      |          | ı     | SIZE<4:0 | >    |        | _      | _       | _      | xxxx          |

| A050                        | SBT8RD0          | 31:16     | _     |       | _          | _        |          |       | _     |      |          | _     | _        | _    | _      | _      | _       | _      | xxxx          |

|                             |                  | 15:0      | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| A058                        | SBT8WR0          | 31:16     | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | _      | _      | _       | _      | xxxx          |

|                             |                  | 15:0      | _     | _     | _          | _        | _        | _     | _     | _    | _        | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | XXXX          |

| A060                        | SBT8REG1         | 31:16     |       |       |            |          |          |       | ı     |      | SE<21:6> |       |          |      |        |        | 1       |        | xxxx          |

|                             |                  | 15:0      |       |       | B <i>A</i> | \SE<5:0> |          |       | PRI   | _    |          |       | SIZE<4:0 | >    |        | _      |         | _      | xxxx          |

| A070                        | SBT8RD1          | 31:16     | _     | _     | _          | _        |          | _     | _     |      | _        | _     | _        | _    | _      | _      |         | _      | xxxx          |

|                             |                  | 15:0      | _     | _     | _          |          |          |       |       |      |          |       |          |      | GROUP3 | GROUP2 | GROUP1  |        |               |

| A078                        | SBT8WR1          | 31:16     | _     |       |            |          |          |       |       |      |          |       |          |      | -      | -      | -       | _      | xxxx          |

| Lawar                       |                  | 15:0      |       | _     | _          |          | _        | _     | _     | _    | _        | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | XXXX          |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

REGISTER 5-1: NVMCON: FLASH PROGRAMMING CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|----------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0                 | U-0                  | U-0                   | U-0               | U-0               | U-0              | U-0              |

| 31:24        | 1                 | _                   | _                    | _                     | 1                 | _                 | _                | _                |

| 22.40        | U-0               | U-0                 | U-0                  | U-0                   | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                   | _                    | _                     | -                 | _                 | _                | _                |

| 45.0         | R/W-0, HC         | R/W-0               | R-0, HS, HC          | R-0, HS, HC           | U-0               | U-0               | U-0              | U-0              |

| 15:8         | WR <sup>(1)</sup> | WREN <sup>(1)</sup> | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | -                 | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-x               | U-0                  | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | PFSWAP            | BFSWAP              | _                    | _                     |                   | NVMOP             | <3:0>            |                  |

| Legend:           | HC = Hardware Set | HC = Hardware Cleared      |                    |

|-------------------|-------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 WR: Write Control bit<sup>(1)</sup>

This bit cannot be cleared and can be set only when WREN = 1 and the unlock sequence has been performed.

1 = Initiate a Flash operation

0 = Flash operation is complete or inactive

bit 14 WREN: Write Enable bit<sup>(1)</sup>

1 = Enable writes to the WR bit and disables writes to the NVMOP<3:0> bits

0 = Disable writes to WR bit and enables writes to the NVMOP<3:0> bits

bit 13 WRERR: Write Error bit<sup>(1)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

1 = Program or erase sequence did not complete successfully

0 = Program or erase sequence completed normally

bit 12 LVDERR: Low-Voltage Detect Error bit<sup>(1)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

- 1 = Low-voltage detected (possible data corruption, if WRERR is set)

- 0 = Voltage level is acceptable for programming

- bit 11-8 Unimplemented: Read as '0'

- bit 7 **PFSWAP:** Program Flash Bank Swap Control bit

This bit is only writable when WREN = 0 and the unlock sequence has been performed.

- 1 = Program Flash Bank 2 is mapped to the lower mapped region and program Flash Bank 1 is mapped to the upper mapped region

- 0 = Program Flash Bank 1 is mapped to the lower mapped region and program Flash Bank 2 is mapped to the upper mapped region

- Note 1: These bits are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

- 2: This operation results in a "no operation" (NOP) when the Dynamic Flash ECC Configuration bits = 00 (FECCCON<1:0> (DVCFG0<9:8>)), which enables ECC at all times. For all other FECCCON<1:0> bit settings, this command will execute, but will not write the ECC bits for the word and can cause DED errors if dynamic Flash ECC is enabled (FECCCON<1:0> = 01). Refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) for information regarding ECC and Flash programming.

### REGISTER 7-8: OFFx: INTERRUPT VECTOR ADDRESS OFFSET REGISTER (x = 0-190)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | _                 |                   | _                 | _                 |                   |                  | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |  |

| 23.10        | _                 | _                 | _                 | _                 |                   | _                 | VOFF<            | :17:16>          |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | VOFF<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |  |  |  |

| 7.0          |                   |                   | •                 | VOFF<7:1>         |                   |                   |                  | _                |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 17-1 VOFF<17:1>: Interrupt Vector 'x' Address Offset bits

bit 0 Unimplemented: Read as '0'

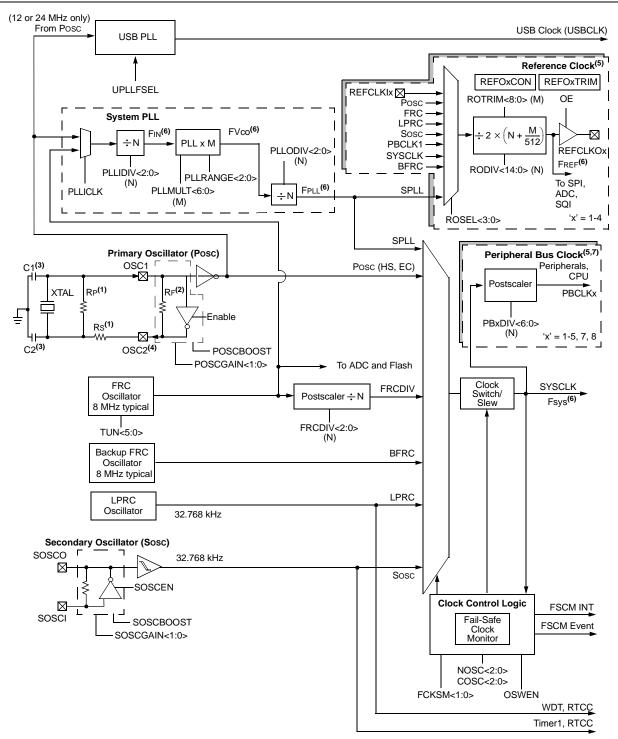

#### FIGURE 8-1: PIC32MZ EF FAMILY OSCILLATOR DIAGRAM

- Notes: 1. A series resistor, Rs, may be required for AT strip cut crystals, or to eliminate clipping. Alternately, to increase oscillator circuit gain, add a parallel resistor, RP.

- 2. The internal feedback resistor, RF, is typically in the range of 2 to 10 M $\Omega$ .

- Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for help in determining the best oscillator components.

- 1. PBCLK1 divided by 2 is available on the OSC2 pin in certain clock modes.

- 5. Shaded regions indicate multiple instantiations of a peripheral or feature.

- 6. Refer to Table 37-19 in Section 37.0 "Electrical Characteristics" for frequency limitations.

- 7. If the DEVCFG registers are configured for a SYSCLK speed greater than 200 MHz, these PBCLKs will be running faster than the maximum rating when the device comes out of Reset. To ensure proper operation, firmware must start the device at a speed less than or equal to 200 MHz, adjust the speed of the PBCLKs, and then raise the SYSCLK speed to the desired speed.

REGISTER 9-1: PRECON: PREFETCH MODULE CONTROL REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | U-0              | U-0              |

| 31.24     | _                 | -                 | _                 | _                 | _                 | PFMSECEN          | _                | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | -                 | 1                 | -                 | _                 | _                 | -                 | 1                | _                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0      | -                 | 1                 | -                 | _                 | _                 | -                 | 1                | _                |

| 7:0       | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7.0       | _                 | _                 | PREFE             | N<1:0>            | _                 | PFI               | MWS<2:0>(        | 1)               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-27 Unimplemented: Read as '0'

bit 26 **PFMSECEN:** Flash SEC Interrupt Enable bit

1 = Generate an interrupt when the PFMSEC bit (PRESTAT<26>) is set

0 = Do not generate an interrupt when the PFMSEC bit is set

bit 25-6 Unimplemented: Read as '0'

bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

11 = Enable predictive prefetch for any address

10 = Enable predictive prefetch for CPU instructions and CPU data

01 = Enable predictive prefetch for CPU instructions only

00 = Disable predictive prefetch

bit 3 Unimplemented: Read as '0'

bit 2-0 **PFMWS<2:0>:** PFM Access Time Defined in Terms of SYSCLK Wait States bits<sup>(1)</sup>

111 = Seven Wait states

•

•

010 Tura

010 = Two Wait states

001 = One Wait state

000 = Zero Wait states

Note 1: For the Wait states to SYSCLK relationship, refer to Table 37-13 in Section37.0 "Electrical Characteristics".

# REGISTER 11-7: USBIE0CSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 0)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R-x               | R-x               | R-0               | R-x               | R-x               | R-x               | R-1              | R-0              |

| 31:24        | MPRXEN            | MPTXEN            | BIGEND            | HBRXEN            | HBTXEN            | DYNFIFOS          | SOFTCONE         | UTMIDWID         |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 13.6         | _                 | -                 | 1                 |                   | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 MPRXEN: Automatic Amalgamation Option bit

1 = Automatic amalgamation of bulk packets is done

0 = No automatic amalgamation

bit 30 MPTXEN: Automatic Splitting Option bit

1 = Automatic splitting of bulk packets is done

0 = No automatic splitting

bit 29 BIGEND: Byte Ordering Option bit

1 = Big Endian ordering

0 = Little Endian ordering

bit 28 HBRXEN: High-bandwidth RX ISO Option bit

1 = High-bandwidth RX ISO endpoint support is selected

0 = No High-bandwidth RX ISO support

bit 27 HBTXEN: High-bandwidth TX ISO Option bit

1 = High-bandwidth TX ISO endpoint support is selected

0 = No High-bandwidth TX ISO support

bit 26 DYNFIFOS: Dynamic FIFO Sizing Option bit

1 = Dynamic FIFO sizing is supported

0 = No Dynamic FIFO sizing

bit 25 **SOFTCONE:** Soft Connect/Disconnect Option bit

1 = Soft Connect/Disconnect is supported

0 = Soft Connect/Disconnect is not supported

bit 24 **UTMIDWID:** UTMI+ Data Width Option bit

Always '0', indicating 8-bit UTMI+ data width

bit 23-0 Unimplemented: Read as '0'

#### REGISTER 11-19: USBEXRXA: USB ENDPOINT 'x' RECEIVE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | 1                 |                   |                   | R                 | XHUBPRT<6:0       | >                 |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | MULTTRAN          |                   |                   | R                 | XHUBADD<6:0       | )>                |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 |                   | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 |                   |                   | F                 | RXFADDR<6:0:      | >                 |                  |                  |

Legend:HC = Hardware ClearedHS = Hardware SetR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 Unimplemented: Read as '0'

bit 30-24 RXHUBPRT<6:0>: RX Hub Port bits (Host mode)

When a Low-Speed or Full-Speed device is connected to this endpoint via a Hi-Speed USB 2.0 hub, this field records the port number of that USB 2.0 hub.

bit 23 MULTTRAN: RX Hub Multiple Translators bit (Host mode)

1 = The USB 2.0 hub has multiple transaction translators

0 = The USB 2.0 hub has a single transaction translator

bit 22-16 **TXHUBADD<6:0>:** RX Hub Address bits (*Host mode*)

When a Low-Speed or Full-Speed device is connected to this endpoint via a Hi-Speed USB 2.0 hub, these bits record the address of the USB 2.0 hub.

bit 15-7 Unimplemented: Read as '0'

bit 6-0 **RXFADDR<6:0>:** RX Functional Address bits (*Host mode*)

Specifies the address for the target function that is be accessed through the associated endpoint. It needs to be defined for each RX endpoint that is used.

TABLE 12-16: PORTG REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                         | 4         |       |       |       |       |                |       |              | Ві           | ts           |              |      |      |      |      |      |      |               |

|-----------------------------|-----------------------------------------|-----------|-------|-------|-------|-------|----------------|-------|--------------|--------------|--------------|--------------|------|------|------|------|------|------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup>         | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All<br>Resets |

| 0600                        | ANSELG                                  | 31:16     | _     | _     | _     | _     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | _    | 0000          |

| 0000                        | ANOLLO                                  | 15:0      | _     | _     | _     | _     | _              | _     | ANSG9        | ANSG8        | ANSG7        | ANSG6        | _    | _    | _    | _    | _    | _    | 03C0          |

| 0610                        | TRISG                                   | 31:16     | _     | _     | _     | _     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | _    | 0000          |

| 0010                        | 111100                                  | 15:0      | _     | _     | _     | _     | _              | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       |      | _    | _    | _    | _    | _    | 03C0          |

| 0620                        | PORTG                                   | 31:16     | _     | _     | _     | -     | _              | _     | _            | _            | _            | _            |      | _    | _    |      | _    | _    | 0000          |

| 0020                        | 1 01110                                 | 15:0      | _     | _     | _     | -     | _              | _     | RG9          | RG8          | RG7          | RG6          | _    | _    | _    | _    | _    | _    | xxxx          |

| 0630                        | LATG                                    | 31:16     | _     | _     | _     | -     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | _    | 0000          |

| 0000                        |                                         | 15:0      | _     | _     | _     | I     | _              | _     | LATG9        | LATG8        | LATG7        | LATG6        | _    | _    | _    | _    | _    | _    | xxxx          |

| 0640                        | ODCG                                    | 31:16     | _     | _     | _     | I     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | _    | 0000          |

| 00.0                        | 0200                                    | 15:0      | _     | _     | _     | I     | _              | _     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | _    | _    | _    | _    | _    | 0000          |

| 0650                        | CNPUG                                   | 31:16     | _     | _     | _     | I     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | _    | 0000          |

| 0000                        | 0 00                                    | 15:0      | _     | _     | _     | I     | _              | _     | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _    | _    | _    | _    | _    | _    | 0000          |

| 0660                        | CNPDG                                   | 31:16     |       |       | _     | _     | _              |       | _            | _            | _            | _            |      | _    |      |      | _    | _    | 0000          |

|                             | • • • • • • • • • • • • • • • • • • • • | 15:0      | _     |       | _     | _     | _              |       | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       |      |      |      |      | _    | _    | 0000          |

|                             |                                         | 31:16     | _     |       | _     | _     | _              |       | _            | _            |              | _            |      | _    |      |      | _    | _    | 0000          |

| 0670                        | CNCONG                                  | 15:0      | ON    | _     | -     | -     | EDGE<br>DETECT | _     | _            | _            | -            | _            | _    | -    | -    | -    | _    | _    | 0000          |

| 0680                        | CNENG                                   | 31:16     | _     | _     | _     | 1     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | _    | 0000          |

| 0000                        | CIVLING                                 | 15:0      | _     | _     | _     |       | _              |       | CNENG9       | CNENG8       | CNENG7       | CNENG6       |      | _    |      | _    | _    | _    | 0000          |

|                             |                                         | 31:16     | _     | _     | _     |       | _              |       | _            | _            | _            | _            |      | _    | _    |      | _    | _    | 0000          |

| 0690                        | CNSTATG                                 | 15:0      | _     | _     | _     | _     | _              | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | _    | _    | _    | _    | _    | _    | 0000          |

| 06A0                        | CNNEG                                   | 31:16     | _     | 1     | -     | _     | _              | _     | _            | _            | _            | _            | _    | -    | _    | _    | _    | _    | 0000          |

| UBAU                        | CININEG                                 | 15:0      | _     | _     | _     | _     | _              | _     | CNNEG9       | CNNEG8       | CNNEG7       | CNNEG6       | _    | _    | _    | _    | _    | _    | 0000          |

| OCDO                        | CNFG                                    | 31:16     | _     | -     | _     | _     | _              |       | _            | _            | _            | _            | _    | _    | _    | _    | _    | _    | 0000          |

| 06B0                        | CNFG                                    | 15:0      | _     | _     |       | I     | _              | _     | CNFG9        | CNFG8        | CNFG7        | CNFG6        | _    |      |      |      | _    | _    | 0000          |

| 0600                        | SRCON0G                                 | 31:16     | _     | _     | _     | _     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | _    | 0000          |

| 0000                        | SKCONUG                                 | 15:0      | _     | _     |       | I     | _              | _     | SR0G9        | _            |              | SR0G6        | _    |      |      |      | _    | _    | 0000          |

| 06D0                        | SRCON1G                                 | 31:16     | _     | _     | _     | _     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | _    | 0000          |

| טטטט                        | SKCONIG                                 | 15:0      | _     | _     | _     | 1     | _              | _     | SR1G9        | _            | -            | SR1G6        | _    | -    | -    | _    | _    | _    | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

TABLE 12-17: PORTH REGISTER MAP FOR 124-PIN DEVICES ONLY

| The late of the    | ess                         | _                               | ø,        |       |       |         |         |       |         |        | Bits   |      |        |        |        |      |      |        |        |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|-----------|-------|-------|---------|---------|-------|---------|--------|--------|------|--------|--------|--------|------|------|--------|--------|---------------|

| 0700   0700   0700   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710   0710      | Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13   | 28/12   | 27/11 | 26/10   | 25/9   | 24/8   | 23/7 | 22/6   | 21/5   | 20/4   | 19/3 | 18/2 | 17/1   | 16/0   | All<br>Resets |

| 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0700                        | ANSELH                          | -         | _     | _     | _       | _       |       | _       | _      | _      | _    |        |        |        | _    | _    |        |        |               |

| 0710 TRISH   15.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0700                        | 7(IVOLLII                       | _         | _     | _     | _       | _       | Ι     | _       |        | _      | _    | ANSH6  | ANSH5  | ANSH4  | _    | _    | ANSH1  | ANSH0  |               |

| 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0710                        | TRISH                           | -         | _     | _     |         |         | 1     |         |        |        | _    |        |        |        | _    | _    |        |        |               |

| 0720 PORTH 15:0 - RH13 RH12 - RH10 RH9 RH8 - RH6 RH5 RH4 - RH1 RH0 xxxx  0730 LATH 15:0 - LATH113 LATH12 - LATH10 LATH9 LATH8 - LATH6 LATH5 LATH4 - LATH1 LATH0 xxxx  0740 DCH 15:0 - LATH31 LATH12 - LATH10 DCH9 DCH8 - DCH6 DCH5 DCH4 - DCH11 DCH0 0000  0750 CNPUH 15:0 - DCNPUH 15:0 - CNPUH 15 | 00                          |                                 |           |       |       | TRISH13 | TRISH12 | _     | TRISH10 | TRISH9 | TRISH8 |      | TRISH6 | TRISH5 | TRISH4 |      |      | TRISH1 | TRISH0 |               |

| 15.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0720                        | PORTH                           | -         | _     |       |         |         | _     |         |        |        |      |        |        |        |      |      |        |        | _             |

| OTA    |                             |                                 | _         |       |       | RH13    |         | _     | RH10    |        |        |      | RH6    |        |        |      |      | RH1    |        | _             |

| 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0730                        | LATH                            | -         | _     |       |         |         | _     |         |        |        |      |        |        |        |      |      |        |        | _             |

| ODCH   15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                             |                                 |           |       |       | LATH13  | LATH12  | _     | LATH10  | LATH9  | LATH8  |      | LATH6  | LATH5  | LATH4  |      | _    | LATH1  | LATH0  |               |