Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efk100t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |                        | Pin Nu          | mber            |                          |             |                |                                   |

|-----------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name        | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|                 |                        |                 | •               |                          | PO          | RTA            | ·                                 |

| RA0             | _                      | 17              | A11             | 22                       | I/O         | ST             | PORTA is a bidirectional I/O port |

| RA1             | —                      | 38              | B21             | 56                       | I/O         | ST             |                                   |

| RA2             | —                      | 59              | A41             | 85                       | I/O         | ST             |                                   |

| RA3             | —                      | 60              | B34             | 86                       | I/O         | ST             |                                   |

| RA4             | —                      | 61              | A42             | 87                       | I/O         | ST             |                                   |

| RA5             | —                      | 2               | B1              | 2                        | I/O         | ST             |                                   |

| RA6             | —                      | 89              | A61             | 129                      | I/O         | ST             |                                   |

| RA7             | —                      | 90              | B51             | 130                      | I/O         | ST             |                                   |

| RA9             | —                      | 28              | B15             | 39                       | I/O         | ST             |                                   |

| RA10            | _                      | 29              | A20             | 40                       | I/O         | ST             | ]                                 |

| RA14            | _                      | 66              | B37             | 95                       | I/O         | ST             |                                   |

| RA15            | _                      | 67              | A45             | 96                       | I/O         | ST             |                                   |

|                 |                        |                 |                 |                          | PO          | RTB            |                                   |

| RB0             | 16                     | 25              | A18             | 36                       | I/O         | ST             | PORTB is a bidirectional I/O port |

| RB1             | 15                     | 24              | A17             | 35                       | I/O         | ST             |                                   |

| RB2             | 14                     | 23              | A16             | 34                       | I/O         | ST             |                                   |

| RB3             | 13                     | 22              | A14             | 31                       | I/O         | ST             |                                   |

| RB4             | 12                     | 21              | A13             | 26                       | I/O         | ST             |                                   |

| RB5             | 11                     | 20              | B11             | 25                       | I/O         | ST             |                                   |

| RB6             | 17                     | 26              | B14             | 37                       | I/O         | ST             |                                   |

| RB7             | 18                     | 27              | A19             | 38                       | I/O         | ST             |                                   |

| RB8             | 21                     | 32              | B18             | 47                       | I/O         | ST             |                                   |

| RB9             | 22                     | 33              | A23             | 48                       | I/O         | ST             |                                   |

| RB10            | 23                     | 34              | B19             | 49                       | I/O         | ST             | _                                 |

| RB11            | 24                     | 35              | A24             | 50                       | I/O         | ST             | _                                 |

| RB12            | 27                     | 41              | A27             | 59                       | I/O         | ST             | _                                 |

| RB13            | 28                     | 42              | B23             | 60                       | I/O         | ST             | -                                 |

| RB14            | 29                     | 43              | A28             | 61                       | I/O         | ST             | -                                 |

| RB15            | 30                     | 44              | B24             | 62                       | I/O         | ST             |                                   |

| <b>D</b> O1     |                        | -               |                 |                          |             | RTC            |                                   |

| RC1             | —                      | 6               | B3              | 6                        | I/O         | ST             | PORTC is a bidirectional I/O port |

| RC2             |                        | 7               | A6              | 11                       | I/O         | ST             | 4                                 |

| RC3             |                        | 8               | B5              | 12                       | I/O         | ST             | 4                                 |

| RC4             | -                      | 9               | A7              | 13                       | I/O         | ST             | 4                                 |

| RC12            | 31                     | 49              | B28             | 71                       | I/O         | ST             | 4                                 |

| RC13            | 47                     | 72              | B41             | 105                      | I/O         | ST             | 4                                 |

| RC14            | 48                     | 73              | A49             | 106                      | I/O         | ST             | 4                                 |

| RC15<br>Legend: | 32                     | 50<br>MOS-comp  | A33             | 72                       | I/O         | ST             | Analog input P = Power            |

#### **TABLE 1-6:** PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select I = Input

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24 U-0    |                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | —                 |                   | —                 | —                 | —                |                  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 15:8         | —                 | —                 | T13PGV            | T12PGV            | T11PGV            | T10PGV            | T9PGV            | T8PGV            |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          | T7PGV             | T6PGV             | T5PGV             | T4PGV             | T3PGV             | T2PGV             | T1PGV            | T0PGV            |  |  |  |  |  |

#### REGISTER 4-2: SBFLAG: SYSTEM BUS STATUS FLAG REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-14 Unimplemented: Read as '0'

bit 13-0 **TxPGV:** Target 'x' Permission Group Violation Status bits ('x' = 0-13)

Refer to Table 4-6 for the list of available targets and their descriptions.

- 1 = Target is reporting a Permission Group (PG) violation

- 0 = Target is not reporting a PG violation

Note: All errors are cleared at the source (i.e., SBTxELOG1, SBTxELOG2, SBTxECLRS, or SBTxECLRM registers).

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>f)                  | <b>N</b> -                      | Ð         |       |       |       |       |       |       |      | Bi         | s    |      |      |      |      |      |       |         | Ś          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|---------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0    | All Resets |

|                             | 055077(2)                       | 31:16     | _     | _     | _     | _     |       | _     | —    | _          | _    | _    | _    | _    | _    | _    | VOFF. | :17:16> | 0000       |

| 0674                        | OFF077 <sup>(2)</sup>           | 15:0      |       |       | •     |       |       | •     | •    | VOFF<15:1> |      |      | •    |      |      | •    | •     | —       | 0000       |

| 0670                        | OFF078 <sup>(2)</sup>           | 31:16     | _     | _     | _     | _     | —     | —     | _    | _          | _    | _    | -    | _    | _    | _    | VOFF. | :17:16> | 0000       |

| 0070                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0670                        | OFF079 <sup>(2)</sup>           | 31:16     | _     | —     | —     | _     | _     | —     | —    | _          | _    | -    | —    | _    | _    | _    | VOFF. | :17:16> | 0000       |

| 0070                        | 011073.7                        | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      | -    |      |      | -    | -     | —       | 0000       |

| 0880                        | OFF080 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | _     | —     | —    | —          | _    | —    | —    | —    | —    |      | VOFF. | :17:16> | 0000       |

| 0000                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0684                        | OFF081 <sup>(2)</sup>           | 31:16     | —     | —     | _     | —     | —     | —     |      | —          | —    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

| 0004                        | 011001                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      | •    |      |      |      |       | —       | 0000       |

| 0688                        | OFF082 <sup>(2)</sup>           | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

| 0000                        | 011002                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0680                        | OFF083 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | _     | —     | _    | —          | _    | —    | —    | —    | —    |      | VOFF. | :17:16> | 0000       |

| 0000                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0690                        | OFF084 <sup>(2)</sup>           | 31:16     | —     | —     | _     | —     | —     | —     |      | —          | —    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

| 0000                        | 011004                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0694                        | OFF085 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | _     | —     | —    |            | _    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

| 0004                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      | -    |      |      |      |       |         | 0000       |

| 0698                        | OFF086 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | _     | —     | —    |            | _    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

|                             | 0.1000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0690                        | OFF087 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

|                             | 0.1.001                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      | -    |      |      |      |       |         | 0000       |

| 0640                        | OFF088 <sup>(2)</sup>           | 31:16     | _     | —     | -     | —     | _     | —     | —    | —          | _    | —    | -    | —    | —    | —    | VOFF. | :17:16> | 0000       |

| 00,10                       | 0.1000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 06A4                        | OFF089 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | -    | —    | -    | —    | —    | —    | VOFF. | :17:16> | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 06A8                        | OFF090 <sup>(2)</sup>           | 31:16     | _     | —     | —     | —     | —     | —     | —    | _          | _    | —    | —    | —    | —    | _    | VOFF. | :17:16> | 0000       |

| 00/10                       | 0.7000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0640                        | OFF091 <sup>(2)</sup>           | 31:16     | _     | —     | -     | —     | —     | —     | —    | —          | _    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

|                             | 011001                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

DS60001320D-page 136

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

3: This bit or register is not available on devices without a CAN module.

4: This bit or register is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

# 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the           |

|-------|------------------------------------------|

|       | features of the PIC32MZ EF family of     |

|       | devices. It is not intended to be a      |

|       | comprehensive reference source. To       |

|       | complement the information in this data  |

|       | sheet, refer to Section 42. "Oscillators |

|       | with Enhanced PLL" (DS60001250) in       |

|       | the "PIC32 Family Reference Manual",     |

|       | which is available from the Microchip    |

|       | web site (www.microchip.com/PIC32).      |

The PIC32MZ EF oscillator system has the following modules and features:

- A total of five external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown with dedicated Back-up FRC (BFRC)

- Dedicated On-Chip PLL for USB peripheral

- Flexible reference clock output

- Multiple clock branches for peripherals for better performance flexibility

- · Clock switch/slew control with output divider

A block diagram of the oscillator system is shown in Figure 8-1. The clock distribution is provided in Table 8-1.

Note: Devices that support 252 MHz operation should be configured for SYSCLK <= 200 MHz operation. Adjust the dividers of the PBCLKs, and then increase the SYSCLK to the desired speed.

# TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| ŝ        |                  |               |                                        |               |       |       |           |       |      |             | Bits            |              |      |      |           |      |      |              |            |  |  |    |    |

|----------|------------------|---------------|----------------------------------------|---------------|-------|-------|-----------|-------|------|-------------|-----------------|--------------|------|------|-----------|------|------|--------------|------------|--|--|----|----|

| (BF8E_#) | Register<br>Name | Bit Range     | 31/15                                  | 30/14         | 29/13 | 28/12 | 27/11     | 26/10 | 25/9 | 24/8        | 23/7            | 22/6         | 21/5 | 20/4 | 19/3      | 18/2 | 17/1 | 16/0         | All Recete |  |  |    |    |

|          | USB              | 31:16         | _                                      |               |       | RX    | HUBPRT<6  | :0>   |      |             | MULTTRAN        |              |      | RXHU | BADD<6:0> |      |      |              | 00         |  |  |    |    |

| 09C      | E3RXA            | 15:0          |                                        | _             | —     | _     | _         |       | _    | _           | _               |              |      | RXFA | DDR<6:0>  |      |      |              | 00         |  |  |    |    |

| 0A0      | US               | 31:16         | 1                                      |               |       | ТХ    | HUBPRT<6  | :0>   | -    | -           | MULTTRAN        |              |      | TXHU | BADD<6:0> |      |      |              | 0 0        |  |  |    |    |

|          | BE4TXA           | 15:0          | -                                      | _             | —     | —     | —         | —     | —    | —           | —               |              |      |      | DDR<6:0>  |      |      |              | 00         |  |  |    |    |

| 0A4      | USB              | 31:16         | _                                      |               |       | RX    | HUBPRT<6  | :0>   |      | 1           | MULTTRAN        |              |      |      | BADD<6:0> |      |      |              | 00         |  |  |    |    |

|          | E4RXA            | 15:0          | _                                      | -             | -     | —     | —         |       | -    | -           | —               |              |      |      | DDR<6:0>  |      |      |              | 00         |  |  |    |    |

| 0A8      | USB              | 31:16         | —                                      |               |       |       | HUBPRT<6  |       |      | -           | MULTTRAN        |              |      |      | BADD<6:0> |      |      |              | 00         |  |  |    |    |

|          | E5TXA            | 15:0          | _                                      | -             | —     | -     | —         | _     | -    | -           | —               |              |      |      | DDR<6:0>  |      |      |              | 00         |  |  |    |    |

| DAC      | USB<br>E5RXA     | 31:16         | _                                      |               |       | RX    | HUBPRT<6  | :0>   |      |             | MULTTRAN        |              |      |      | BADD<6:0> |      |      |              | 00         |  |  |    |    |

|          |                  | 15:0          |                                        |               | —     |       | -         |       | _    | -           | -               |              |      |      | DDR<6:0>  |      |      |              | 00         |  |  |    |    |

| 0В0      | USB<br>E6TXA     | 31:16         |                                        |               |       |       | HUBPRT<6: |       |      | 1           | MULTTRAN        |              |      |      | BADD<6:0> |      |      |              | 00         |  |  |    |    |

|          |                  | 15:0          | _                                      | _             | -     |       | HUBPRT<6  | -     | _    | —           |                 |              |      |      | DDR<6:0>  |      |      |              | 00         |  |  |    |    |

| 0B4      | USB<br>E6RXA     | 31:16<br>15:0 | _                                      | <u> </u>      |       | r     | HUBPRIS   |       |      |             | MULTTRAN        |              |      |      | BADD<6:0> |      |      |              | 00         |  |  |    |    |

|          |                  | 31:16         |                                        |               | —     | —<br> | HUBPRT<6  | -     | _    | —           | —<br>MULTTRAN   | RXFADDR<6:0> |      |      |           |      |      | 00           |            |  |  |    |    |

| 0B8      | USB<br>E7TXA     | 15:0          |                                        |               | _     |       |           | .0>   |      | _           | MULTIRAN        |              |      |      |           |      |      | TXFADDR<6:0> |            |  |  |    | 00 |

|          |                  | 31:16         |                                        |               |       | RX    | HUBPRT<6  | ·0>   |      | _           | MULTTRAN        |              |      |      |           |      |      |              |            |  |  |    |    |

| 0BC      | USB<br>E7RXA     | 15:0          |                                        |               | _     | _     | _         |       | _    | _           |                 |              |      |      |           |      |      | RXFADDR<6:0> |            |  |  | 00 |    |

|          | USB              | 31:16         |                                        |               |       |       |           |       |      |             |                 |              |      |      |           |      |      |              | 00         |  |  |    |    |

| 100      | E0CSR0           | 15:0          |                                        |               |       |       |           |       | Inde | exed by the | same bits in U  | SBIE0CSR0    |      |      |           |      |      |              | 00         |  |  |    |    |

| 3108     | USB              | 31:16         |                                        |               |       |       |           |       | Ind  | avad by the | oomo hito in Ll |              |      |      |           |      |      |              | 00         |  |  |    |    |

| 108      | E0CSR2           | 15:0          |                                        |               |       |       |           |       | Inde | exed by the | same bits in U  | SBIEUCSKZ    |      |      |           |      |      |              | 00         |  |  |    |    |

| 10C      | USB              | 31:16         |                                        |               |       |       |           |       | Inde | aved by the | same bits in U  | SBIEOCSR3    |      |      |           |      |      |              | 00         |  |  |    |    |

| 100      | E0CSR3           | 15:0          |                                        |               |       |       |           |       | Inde | sked by the | Same bits in O  | SDIE0001(3   |      |      |           |      |      |              | 00         |  |  |    |    |

| 3110     | USB              | 31:16         |                                        |               |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR0    |      |      |           |      |      |              | 00         |  |  |    |    |

| /0       | E1CSR0           | 15:0          |                                        |               |       |       |           |       |      | 5,00 5) 110 |                 | 00.2.100.10  |      |      |           |      |      |              | 00         |  |  |    |    |

| 3114     | USB              | 31:16         |                                        |               |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR1    |      |      |           |      |      |              | 00         |  |  |    |    |

|          | E1CSR1           | 15:0          |                                        |               |       |       |           |       |      |             |                 |              |      |      |           |      |      |              | 00         |  |  |    |    |

| 3118     | USB              | 31:16         |                                        |               |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR2    |      |      |           |      |      |              | 00         |  |  |    |    |

|          | E1CSR2           | 15:0          |                                        |               |       |       |           |       |      | ,           |                 |              |      |      |           |      |      |              | 00         |  |  |    |    |

| 11C      | USB<br>E1CSR3    | 31:16         |                                        |               |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR3    |      |      |           |      |      |              | 00         |  |  |    |    |

|          |                  | 15:0          |                                        | 000           |       |       |           |       |      |             |                 |              |      |      |           |      |      |              |            |  |  |    |    |

| 120      | USB<br>E2CSR0    | 31:16         | Indexed by the same bits in USBIE2CSR0 |               |       |       |           |       |      |             |                 |              |      |      |           |      |      |              |            |  |  |    |    |

|          |                  | 15:0          |                                        |               |       |       |           |       |      |             |                 |              |      |      |           |      |      |              | 000        |  |  |    |    |

| 3124     | USB<br>E2CSR1    | 31:16         |                                        |               |       |       |           |       | Inde | exed by the | same bits in U  | SBIE2CSR1    |      |      |           |      |      |              | 000        |  |  |    |    |

|          |                  | 15:0          |                                        | Reset; — = un |       |       |           |       |      |             |                 |              |      |      |           |      |      |              | 000        |  |  |    |    |

2: 3: 4:

Host mode.

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | RXFIFOAD<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.0         |                   | _                 | _                 |                   | TΣ                | (FIFOAD<12:       | 8>               |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | TXFIFO            | AD<7:0>           |                   |                  |                  |  |  |

#### REGISTER 11-14: USBFIFOA: USB FIFO ADDRESS REGISTER

# Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

bit 28-16 **RXFIFOAD<12:0>:** Receive Endpoint FIFO Address bits

Start address of the endpoint FIFO in units of 8 bytes as follows:

111111111111 = 0xFFF8

- •

- •

bit 15-13 Unimplemented: Read as '0'

#### bit 12-0 TXFIFOAD<12:0>: Transmit Endpoint FIFO Address bits

Start address of the endpoint FIFO in units of 8 bytes as follows:

1111111111111 = 0xFFF8

•

•

•

| SSS                         |                  |           |       |       |       |       |       |       |      | B    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 4444                        | IC4R             | 31:16     | —     | —     | -     | —     | -     | —     | —    | —    | —    | -    | —    | —    | —    | -     | -      | —    | 0000       |

| 1444                        | IC4R             | 15:0      |       | _     | —     | _     |       | _     | _    | _    | _    | —    | —    | —    |      | IC4R  | <3:0>  |      | 0000       |

| 1448                        | IC5R             | 31:16     |       | —     | —     | _     |       | —     | —    |      | —    | _    | _    | _    | _    | _     | _      |      | 0000       |

| 1440                        | 10.51            | 15:0      |       | —     | —     | —     |       | —     | —    | —    | _    | _    | —    | —    |      | IC5R  | <3:0>  |      | 0000       |

| 144C                        | IC6R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1440                        | ICOIX            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | IC6R  | <3:0>  |      | 0000       |

| 1450                        | IC7R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1430                        | 10/10            | 15:0      | _     | _     | —     | —     | _     | _     | —    | _    | _    | —    | _    | —    |      | IC7R  | <3:0>  |      | 0000       |

| 1454                        | IC8R             | 31:16     | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1-0-1                       | 10011            | 15:0      | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | IC8R  | <3:0>  |      | 0000       |

| 1458                        | IC9R             | 31:16     | -     | —     | —     | —     | _     | —     | —    | _    | _    | —    | _    | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | -     | —     |       | —     | _     | _     | —    | —    | _    |      |      | _    |      | IC9R  | <3:0>  |      | 0000       |

| 1460                        | OCFAR            | 31:16     | _     | —     |       | —     | —     | —     | —    | _    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     |       | —     |       | —     | —    |      | _    | —    | —    | —    |      | OCFA  | R<3:0> |      | 0000       |

| 1468                        | U1RXR            | 31:16     | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |      | —     | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |      | U1RXI | R<3:0> |      | 0000       |

| 146C                        | U1CTSR           | 31:16     | _     |       |       | —     | _     | —     | —    | —    | _    |      |      | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | —     | —     | _     | —     | _     | —     | —    | —    | —    | —    | —    | —    |      | U1CTS |        |      | 0000       |

| 1470                        | U2RXR            | 31:16     | _     | —     |       | _     | _     | —     | —    | —    | _    | —    | _    | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | -     | —     | —     | —     | —    | _    | _    | —    | —    | —    |      | U2RXI |        |      | 0000       |

| 1474                        | U2CTSR           | 31:16     | _     | _     |       |       | _     | _     | _    |      | _    |      |      | _    | _    |       | —      | —    | 0000       |

|                             |                  | 15:0      | _     | _     | -     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2CTS |        |      | 0000       |

| 1478                        | <b>U3RXR</b>     | 31:16     | _     |       | -     | _     | _     |       | _    | _    | _    | —    |      | _    | —    |       | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     |       | _     |       | _     | _    | _    | _    | _    |      | _    |      | U3RXI |        |      | 0000       |

| 147C                        | <b>U3CTSR</b>    | 31:16     | _     | _     |       | _     | _     | _     | _    | _    | _    |      |      | _    | —    |       | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     |       | _     |       | _     | _    | _    | _    | _    | _    | _    |      | U3CTS | R<3:0> |      | 0000       |

| 1480                        | U4RXR            | 31:16     |       | —     | _     | _     | _     | —     | _    |      | _    | _    | _    | _    | _    |       |        | _    | 0000       |

|                             |                  | 15:0      |       | —     |       | _     | _     | —     | —    |      | _    | _    | _    | _    |      | U4RXI |        |      | 0000       |

| 1484                        | U4CTSR           | 31:16     |       | —     |       | _     | _     | —     | —    |      | _    | _    | _    | _    |      | -     | —      | _    | 0000       |

|                             |                  | 15:0      |       | —     | —     | —     | -     | —     | —    | —    | —    |      | _    | —    |      | U4CTS | R<3:0> |      | 0000       |

# TABLE 12-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | —                 | —                | _                |  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | —                 | —                 | —                 | _                 | DEVSE             | EL<1:0>           | MODEBYTES<1:0>   |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | MODECO            | DE<7:0>           |                   |                  |                  |  |  |  |  |  |  |

## REGISTER 20-2: SQI1XCON2: SQI XIP CONTROL REGISTER 2

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-12 Unimplemented: Read as '0'

#### bit 11-10 **DEVSEL<1:0>:** Device Select bits

- 11 = Reserved

- 10 = Reserved

- 01 = Device 1 is selected

- 00 = Device 0 is selected

#### bit 9-8 MODEBYTES<1:0>: Mode Byte Cycle Enable bits

- 11 = Three cycles

- 10 =Two cycles

- 01 = One cycle

- 00 = Zero cycles

#### bit 7-0 MODECODE<7:0>: Mode Code Value bits

These bits contain the 8-bit code value for the mode bits.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | _                 |                   | TXINTTHR<4:0>     |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   | R                 | XINTTHR<4:0       | >                |                  |

## REGISTER 20-7: SQI1INTTHR: SQI INTERRUPT THRESHOLD REGISTER

## Legend:

| 3                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-13 Unimplemented: Read as '0'

bit 12-8 **TXINTTHR<4:0>:** Transmit Interrupt Threshold bits A transmit interrupt is set when the transmit FIFO has more space than the set number of bytes. For 16-bit mode, the value should be a multiple of 2.

bit 7-5 Unimplemented: Read as '0'

#### bit 4-0 RXINTTHR<4:0>: Receive Interrupt Threshold bits

A receive interrupt is set when the receive FIFO count is larger than or equal to the set number of bytes. For 16-bit mode, the value should be multiple of 2.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | TXDATA<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 22.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | TXDATA<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   |                   |                   | TXDATA            | <15:8>            |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | TXDATA            | <7:0>             |                   |                  |                  |  |  |

### REGISTER 20-10: SQI1TXDATA: SQI TRANSMIT DATA BUFFER REGISTER

| L | _egend:          |                  |                          |                    |

|---|------------------|------------------|--------------------------|--------------------|

| F | R = Readable bit | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| - | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 TXDATA<31:0>: Transmit Command Data bits

Data is loaded into this register before being transmitted. Prior to the data transfer, the data in TXDATA is loaded into the shift register (SFDR).

Multiple writes to TXDATA can occur while a transfer is in progress. There can be a maximum of eight commands that can be queued.

#### REGISTER 20-11: SQI1RXDATA: SQI RECEIVE DATA BUFFER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        |                   |                   |                   | RXDATA<           | :31:24>           |                   |                  |                  |  |  |

| 22.10        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | RXDATA<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | RXDATA<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | RXDATA            | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 RXDATA<31:0>: Receive Data Buffer bits

At the end of a data transfer, the data in the shift register is loaded into the RXDATA register. This register works like a FIFO. The depth of the receive buffer is eight words.

| Bit<br>Range | Bit<br>31/23/15/7             | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0                           | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | —                             | —                 | _                 | INIT2SCHECK       | INIT2CO           | UNT<1:0>          | INIT2TY          | PE<1:0>          |  |

| 00.40        | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | INIT2CMD3<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | INIT2CMD2<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                               |                   |                   | INIT2CMD1<        | 7:0> <b>(1)</b>   |                   |                  |                  |  |

#### REGISTER 20-26: SQI1XCON4: SQI XIP CONTROL REGISTER 4

# Legend:

| · <b>J</b> · · ·  |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

- bit 28 INIT2SCHECK: Flash Initialization 2 Command Status Check bit 1 = Check the status after executing the INIT2 command 0 = Do not check the status

- bit 27-26 INIT2COUNT<1:0>: Flash Initialization 2 Command Count bits

- 11 = INIT2CMD1, INIT2CMD2, and INIT2CMD3 are sent

- 10 = INIT2CMD1 and INIT2CMD2 are sent, but INIT2CMD3 is still pending

- 01 = INIT2CMD1 is sent, but INIT2CMD2 and INIT2CMD3 are still pending

- 00 = No commands are sent

- bit 25-24 INIT2TYPE<1:0>: Flash Initialization 2 Command Type bits

- 11 = Reserved

- 10 = INIT2 commands are sent in Quad Lane mode

- 01 = INIT2 commands are sent in Dual Lane mode

- 00 = INIT2 commands are sent in Single Lane mode

- bit 24-16 **INIT2CMD3<7:0>:** Flash Initialization Command 3 bits<sup>(1)</sup> Third command of the Flash initialization.

- bit 15-8 **INIT2CMD2<7:0>:** Flash Initialization Command 2 bits<sup>(1)</sup> Second command of the Flash initialization.

- bit 7-0 **INIT2CMD1<7:0>:** Flash Initialization Command 1 bits<sup>(1)</sup> First command of the Flash initialization.

- **Note 1:** INIT2CMD1 can be WEN and INIT2CMD2 can be SECTOR UNPROTECT.

**Note:** Some Flash devices require Write Enable and Sector Unprotect commands before read/write operations and this register is useful in working with those Flash types (XIP mode only)

| Bit<br>Range     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

|                  | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24            |                   | HR10              | <3:0>             |                   |                   | HR01              | <3:0>            |                  |  |  |

| 22.46            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16            | MIN10<3:0>        |                   |                   |                   | MIN01<3:0>        |                   |                  |                  |  |  |

| 45.0             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8             |                   | SEC10<3:0>        |                   |                   |                   | SEC01<3:0>        |                  |                  |  |  |

| 7.0              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0              | —                 | —                 | —                 | _                 | —                 | —                 | _                | —                |  |  |

|                  |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:          |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| R = Readable bit |                   |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |  |

0' = Bit is cleared

x = Bit is unknown

## REGISTER 25-3: RTCTIME: REAL-TIME CLOCK TIME VALUE REGISTER

'1' = Bit is set

| bit 31-28 | HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10 digits; contains a value from 0 to 2    |

|-----------|-------------------------------------------------------------------------------------------------|

| bit 27-24 | HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1 digit; contains a value from 0 to 9      |

| bit 23-20 | MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10 digits; contains a value from 0 to 5 |

| bit 19-16 | MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1 digit; contains a value from 0 to 9   |

| bit 15-12 | SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10 digits; contains a value from 0 to 5 |

| bit 11-8  | SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1 digit; contains a value from 0 to 9   |

bit 7-0 Unimplemented: Read as '0'

-n = Value at POR

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

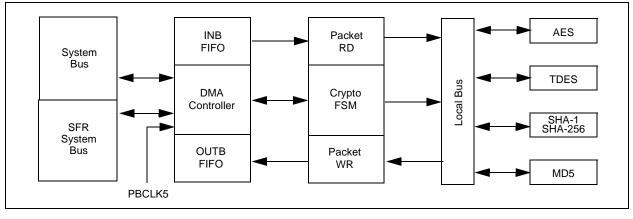

# 26.0 CRYPTO ENGINE

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246) in the "PIC32 Family Reference Manual". which is available from the Microchip web site (www.microchip.com/PIC32).

The Crypto Engine is intended to accelerate applications that need cryptographic functions. By executing these functions in the hardware module, software overhead is reduced and actions, such as encryption, decryption, and authentication can execute much more quickly.

The Crypto Engine uses an internal descriptor-based DMA for efficient programming of the security association data and packet pointers (allowing scatter/ gather data fetching). An intelligent state machine schedules the Crypto Engines based on the protocol selection and packet boundaries. The hardware engines can perform the encryption and authentication in sequence or in parallel.

The following are key features of the Crypto Engine:

- Bulk ciphers and hash engines

- Integrated DMA to off-load processing:

- Buffer descriptor-based

- Secure association per buffer descriptor

- Some functions can execute in parallel

Bulk ciphers that are handled by the Crypto Engine include:

- AES:

- 128-bit, 192-bit, and 256-bit key sizes

- CBC, ECB, CTR, CFB, and OFB modes

- DES/TDES:

- CBC, ECB, CFB, and OFB modes

Authentication engines that are available through the Crypto Engine include:

- SHA-1

- SHA-256

- MD-5

- AES-GCM

- HMAC operation (for all authentication engines)

The rate of data that can be processed by the Crypto Engine depends on these factors:

- Which engine is in use

- Whether the engines are used in parallel or in series

- The demands on source and destination memories by other parts of the system (i.e., CPU, DMA, etc.)

- The speed of PBCLK5, which drives the Crypto Engine

Table 26-1 shows typical performance for various engines.

#### TABLE 26-1: CRYPTO ENGINE PERFORMANCE

| Engine/<br>Algorithm | Performance<br>Factor<br>(Mbps/MHz) | Maximum Mbps<br>(PBCLK5 = 100 MHz) |

|----------------------|-------------------------------------|------------------------------------|

| DES                  | 14.4                                | 1440                               |

| TDES                 | 6.6                                 | 660                                |

| AES-128              | 9.0                                 | 900                                |

| AES-192              | 7.9                                 | 790                                |

| AES-256              | 7.2                                 | 720                                |

| MD5                  | 15.6                                | 1560                               |

| SHA-1                | 13.2                                | 1320                               |

| SHA-256              | 9.3                                 | 930                                |

## FIGURE 26-1: CRYPTO ENGINE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 51.24        |                   | _                 |                   | —                 | —                 |                   |                  | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |  |

| 15.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |

| 15:8         | STNADDR6<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |

| 7:0          |                   |                   |                   | STNADDR5<         | :7:0>             |                   |                  |                  |  |

### REGISTER 30-37: EMAC1SA0: ETHERNET CONTROLLER MAC STATION ADDRESS 0 REGISTER

| Legend:           |                  | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15-8 **STNADDR6<7:0>:** Station Address Octet 6 bits These bits hold the sixth transmitted octet of the station address.

- bit 7-0 **STNADDR5<7:0>:** Station Address Octet 5 bits These bits hold the fifth transmitted octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

### REGISTER 34-4: DEVCFG1/ADEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FNOSC<2:0>: Oscillator Selection bits

- 111 = FRC divided by FRCDIV<2:0> bits (FRCDIV)

- 110 = Reserved

- 101 = LPRC

- 100 **= S**OSC

- 011 = Reserved

- 010 = Posc (HS, EC)

- 001 = SPLL

- 000 = FRC divided by FRCDIV<2:0> bits (FRCDIV)

| REGISTI   | ER 34-9: CFGEBIC: EXTERNAL BUS INTERFACE CONTROL PIN CONFIGURATION<br>REGISTER (CONTINUED)                                                          |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 12    | EBIOEEN: EBIOE Pin Enable bit                                                                                                                       |  |

|           | $1 = \overline{\text{EBIOE}}$ pin is enabled for use by the EBI module                                                                              |  |

|           | $0 = \overline{EBIOE}$ pin is available for general use                                                                                             |  |

| bit 11-10 | Unimplemented: Read as '0'                                                                                                                          |  |

| bit 9     | EBIBSEN1: EBIBS1 Pin Enable bit                                                                                                                     |  |

|           | 1 = EBIBS1 pin is enabled for use by the EBI module<br>0 = EBIBS1 pin is available for general use                                                  |  |

| bit 8     | EBIBSEN1: EBIBSO Pin Enable bit                                                                                                                     |  |

| bit 0     | $1 = \overline{\text{EBIBS0}}$ pin is enabled for use by the EBI module                                                                             |  |

|           | 0 = EBIBS0 pin is available for general use                                                                                                         |  |

| bit 7     | EBICSEN3: EBICS3 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{EBICS3}$ pin is enabled for use by the EBI module                                                                                    |  |

|           | 0 = EBICS3 pin is available for general use                                                                                                         |  |

| bit 6     | EBICSEN2: EBICS2 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{\text{EBICS2}}$ pin is enabled for use by the EBI module                                                                             |  |

|           | 0 = EBICS2 pin is available for general use                                                                                                         |  |

| bit 5     | EBICSEN1: EBICS1 Pin Enable bit                                                                                                                     |  |

|           | 1 = EBICS1 pin is enabled for use by the EBI module                                                                                                 |  |

|           | 0 = EBICS1 pin is available for general use                                                                                                         |  |

| bit 4     | EBICSEN0: EBICS0 Pin Enable bit                                                                                                                     |  |

|           | 1 = EBICS0 pin is enabled for use by the EBI module                                                                                                 |  |

| 1         | 0 = EBICS0 pin is available for general use                                                                                                         |  |

| bit 3-2   | Unimplemented: Read as '0'                                                                                                                          |  |

| bit 1     | EBIDEN1: EBI Data Upper Byte Pin Enable bit                                                                                                         |  |

|           | <ul> <li>1 = EBID&lt;15:8&gt; pins are enabled for use by the EBI module</li> <li>0 = EBID&lt;15:8&gt; pins have reverted to general use</li> </ul> |  |

| bit 0     | <b>EBIDENO:</b> EBI Data Lower Byte Pin Enable bit                                                                                                  |  |

| DIL U     | 1 = EBID<7:0> pins are enabled for use by the EBI module                                                                                            |  |

|           | 0 = EBID < 7:0 >  pins have reverted to general use                                                                                                 |  |

|           | -                                                                                                                                                   |  |

| Note:     | When EBIMD = 1, the bits in this register are ignored and the pins are available for general use.                                                   |  |

# 37.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MZ EF electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MZ EF devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

Specifications for Extended Temperature devices (-40°C to +125°C) that are different from the specifications in this section are provided in **38.0** "Extended Temperature Electrical Characteristics".

# Absolute Maximum Ratings

## (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +85°C            |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                              | 0.3V to +4.0V            |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to VSS when $VDD \ge 2.1V$ (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to VSS when VDD < 2.1V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                               | 200 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                        | 200 mA                   |

| Maximum current sunk/sourced by any 4x I/O pin (Note 4)                         | 15 mA                    |

| Maximum current sunk/sourced by any 8x I/O pin (Note 4)                         | 25 mA                    |

| Maximum current sunk/sourced by any 12x I/O pin (Note 4)                        |                          |

| Maximum current sunk by all ports                                               | 150 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 150 mA                   |

|                                                                                 |                          |

- **Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 37-2).

- 3: See the pin name tables (Table 2 through Table 4) for the 5V tolerant pins.

- 4: Characterized, but not tested. Refer to parameters DO10, DO20, and DO20a for the 4x, 8x, and 12x I/O pin lists.

# 39.0 252 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MZ EF electrical characteristics for devices running at 252 MHz. Additional information will be provided in future revisions of this document as it becomes available.

The specifications for 252 MHz are identical to those shown in **37.0** "Electrical Characteristics" including absolute maximum ratings, with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 252 MHz operation. For example, parameter DC27a in **37.0** "Electrical Characteristics", is the up to 200 MHz operation equivalent for MDC27a.