Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------|

| roduct Status             | Active                                                                            |

| Core Processor            | MIPS32® M-Class                                                                   |

| Core Size                 | 32-Bit Single-Core                                                                |

| ipeed                     | 180MHz                                                                            |

| Connectivity              | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| eripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| lumber of I/O             | 120                                                                               |

| rogram Memory Size        | 1MB (1M x 8)                                                                      |

| rogram Memory Type        | FLASH                                                                             |

| EPROM Size                | -                                                                                 |

| AAM Size                  | 256K x 8                                                                          |

| oltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Oata Converters           | A/D 48x12b                                                                        |

| Scillator Type            | Internal                                                                          |

| perating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Nounting Type             | Surface Mount                                                                     |

| ackage / Case             | 144-TFBGA                                                                         |

| Supplier Device Package   | 144-TFBGA (7x7)                                                                   |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efk144-e-jwx |

### 3.0 CPU

- Note 1: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 50. "CPU for Devices with MIPS32® microAptiv™ and M-Class Cores" (DS60001192) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: The Series 5 Warrior M-class CPU core resources are available at: www.imgtec.com.

The MIPS32<sup>®</sup> M-Class Core is the heart of the PIC32MZ EF family device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

Key features include:

- · 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 5):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- Virtual memory support

- microMIPS™ compatible instruction set:

- Improves code size density over MIPS32, while maintaining MIPS32 performance.

- Supports all MIPS32 instructions (except branch-likely instructions)

- Fifteen additional 32-bit instructions and 39 16-bit instructions corresponding to commonly-used MIPS32 instructions

- Stack pointer implicit in instruction

- MIPS32 assembly and ABI compatible

- MMU with Translation Lookaside Buffer (TLB) mechanism:

- 16 dual-entry fully associative Joint TLB

- 4-entry fully associative Instruction and Data TLB

- 4 KB pages

- Separate L1 data and instruction caches:

- 16 KB 4-way Instruction Cache (I-Cache)

- 4 KB 4-way Data Cache (D-Cache)

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x32 multiply per clock

- Early-in iterative divide. Minimum 12 and maximum 38 clock latency (dividend (rs) sign extension-dependent)

- Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value breakpoints

- Hardware breakpoint supports both address match and address range triggering.

- Eight instruction and four data complex breakpoints

- iFlowtrace® version 2.0 support:

- Real-time instruction program counter

- Special events trace capability

- Two performance counters with 34 userselectable countable events

- Disabled if the processor enters Debug mode

- Program Counter sampling

- Four Watch registers:

- Instruction, Data Read, Data Write options

- Address match masking options

- DSP ASE Extension:

- Native fractional format data type operations

- Register Single Instruction Multiple Data (SIMD) operations (add, subtract, multiply, shift)

- GPR-based shift

- Bit manipulation

- Compare-Pick

- DSP Control Access

- Indexed-Load

- Branch

- Multiplication of complex operands

- Variable bit insertion and extraction

- Virtual circular buffers

- Arithmetic saturation and overflow handling

- Zero-cycle overhead saturation and rounding operations

- Floating Point Unit (FPU):

- 1985 IEEE-754 compliant Floating Point Unit

- Supports single and double precision datatypes

- 2008 IEEE-754 compatibility control of NaN handling and Abs/Neg instructions

- Runs at 1:1 core/FPU clock ratio

### REGISTER 5-8: NVMBWP: FLASH BOOT (PAGE) WRITE-PROTECT REGISTER

- bit 4 **UBWP4:** Upper Boot Alias Page 4 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC30000 through 0x1FC33FFF enabled

- 0 = Write protection for physical address 0x01FC30000 through 0x1FC33FFF disabled

- bit 3 **UBWP3:** Upper Boot Alias Page 3 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC2C000 through 0x1FC2FFFF enabled

- 0 = Write protection for physical address 0x01FC2C000 through 0x1FC2FFFF disabled

- bit 2 **UBWP2:** Upper Boot Alias Page 2 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC28000 through 0x1FC2BFFF enabled

- 0 = Write protection for physical address 0x01FC28000 through 0x1FC2BFFF disabled

- bit 1 **UBWP1:** Upper Boot Alias Page 1 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC24000 through 0x1FC27FFF enabled

- 0 = Write protection for physical address 0x01FC24000 through 0x1FC27FFF disabled

- bit 0 **UBWP0:** Upper Boot Alias Page 0 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC20000 through 0x1FC23FFF enabled

- 0 = Write protection for physical address 0x01FC20000 through 0x1FC23FFF disabled

- **Note 1:** These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (LBWPULOCK or UBWPULOCK) is set.

Note: The bits in this register are only writable when the NVMKEY unlock sequence is followed.

### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        | _                 | _                     | BYTO              | >1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO             |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                     | _                 | _                 | _                  | _                 | _                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | _                  | (                 | CRCCH<2:0>       |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

These bits are unused.

When CRCTYP ( $\underline{DCRCCON<15>}$ ) = 0 (CRC module is in LFSR mode):

Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

#### REGISTER 11-17: USBEOFRST: USB END-OF-FRAME/SOFT RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | -                 | 1                 | NRSTX            | NRST             |  |  |  |  |

| 23:16        | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-0             | R/W-1            | R/W-0            |  |  |  |  |

| 23.10        | LSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15:8         | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 15.6         |                   |                   |                   | FSEO              | F<7:0>            |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R.W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | HSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25 NRSTX: Reset of XCLK Domain bit

1 = Reset the XCLK domain, which is clock recovered from the received data by the PHY

0 = Normal operation

bit 24 NRST: Reset of CLK Domain bit

1 = Reset the CLK domain, which is clock recovered from the peripheral bus

0 = Normal operation

bit 23-16 LSEOF<7:0>: Low-Speed EOF bits

These bits set the Low-Speed transaction in units of  $1.067 \mu s$  (default setting is  $121.6 \mu s$ ) prior to the EOF to stop new transactions from beginning.

bit 15-8 FSEOF<7:0>: Full-Speed EOF bits

These bits set the Full-Speed transaction in units of 533.3  $\mu$ s (default setting is 63.46  $\mu$ s) prior to the EOF to stop new transactions from beginning.

bit 7-0 **HSEOF<7:0>:** Hi-Speed EOF bits

These bits set the Hi-Speed transaction in units of 133.3 µs (default setting is 17.07µs) prior to the EOF to stop new transactions from beginning.

# REGISTER 11-28: USBLPMR1: USB LINK POWER MANAGEMENT CONTROL REGISTER 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 | _                 | LPMERRIE          | LPMRESIE          | LPMACKIE          | LPMNYIE           | LPMSTIE          | LPMTOIE          |

| 22.46        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC        | R/W-0, HC        |

| 23:16        | _                 | _                 | _                 | LPMNAK            | LPME              | N<1:0>            | LPMRES           | LPMXMT           |

| 15.0         | R-0               | R-0               | R-0               | R-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         |                   | ENDPOI            | NT<3:0>           |                   | _                 | _                 | _                | RMTWAK           |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   | HIRD              | <3:0>             |                   |                   | LNKSTA            | TE<3:0>          |                  |

Legend: HC = Hardware Cleared

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29 LPMERRIE: LPM Error Interrupt Enable bit

1 = LPMERR interrupt is enabled0 = LPMERR interrupt is disabled

bit 28 LPMRESIE: LPM Resume Interrupt Enable bit

1 = LPMRES interrupt is enabled0 = LPMRES interrupt is disabled

bit 27 LPMACKIE: LPM Acknowledge Interrupt Enable bit

1 = Enable the LPMACK Interrupt 0 = Disable the LPMACK Interrupt

bit 26 LPMNYIE: LPM NYET Interrupt Enable bit

1 = Enable the LPMNYET Interrupt0 = Disable the LPMNYET Interrupt

bit 25 LPMSTIE: LPM STALL Interrupt Enable bit

1 = Enable the LPMST Interrupt0 = Disable the LPMST Interrupt

bit 24 LPMTOIE: LPM Time-out Interrupt Enable bit

1 = Enable the LPMTO Interrupt0 = Disable the LPMTO Interrupt

bit 23-21 Unimplemented: Read as '0'

bit 20 LPMNAK: LPM-only Transaction Setting bit

1 = All endpoints will respond to all transactions other than a LPM transaction with a NAK

0 = Normal transaction operation

Setting this bit to '1' will only take effect after the USB module as been LPM suspended.

bit 19-18 LPMEN<1:0>: LPM Enable bits (Device mode)

11 = LPM Extended transactions are supported

10 = LPM and Extended transactions are not supported

01 = LPM mode is not supported but Extended transactions are supported

00 = LPM Extended transactions are supported

bit 17 LPMRES: LPM Resume bit

1 = Initiate resume (remote wake-up). Resume signaling is asserted for 50  $\mu$ s.

0 = No resume operationThis bit is self-clearing.

TABLE 12-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SSS                         |                      |           |       |       |       |       |       |       |      | E    | Bits |      |      |      |      |        |          |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|--------|----------|------|------------|

| Virtual Address<br>(BF80_#) |                      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2   | 17/1     | 16/0 | All Resets |

| 1400                        | SS6R <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _      | _        | _    | 0000       |

| 14DC                        | 550K' /              | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SS6R   | <3:0>    |      | 0000       |

| 14E0                        | C1RXR <sup>(2)</sup> | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _      | _        | _    | 0000       |

| 1460                        | CIKAK                | 15:0      | 1     | _     | _     | _     | _     | _     | _    | 1    | _    | _    | _    | _    |      | C1RX   | R<3:0>   |      | 0000       |

| 14E4                        | C2RXR <sup>(2)</sup> | 31:16     | 1     | _     | _     | _     | _     | _     | _    | 1    | _    | _    | _    | _    | _    | 1      | _        | I    | 0000       |

| 1464                        | UZKAK',              | 15:0      | 1     | _     | _     | _     | _     | _     | _    | 1    | _    | _    | _    | _    |      | C2RX   | R<3:0>   |      | 0000       |

| 14E8                        | REFCLKI1R            | 31:16     | 1     | _     | _     | _     | _     | _     | _    | 1    | _    | _    | _    | _    | _    | 1      | _        | I    | 0000       |

| 140                         | KEFCLKIIK            | 15:0      | 1     | _     | _     | _     | _     | _     | _    | 1    | _    | _    | _    | _    |      | REFCLK | I1R<3:0> |      | 0000       |

| 14F0                        | REFCLKI3R            | 31:16     | 1     | _     | _     | _     | _     | _     | _    | 1    | _    | _    | _    | _    | _    | 1      | _        | I    | 0000       |

| 1470                        | KLI CLKISK           | 15:0      | _     | _     | _     | _     | _     | _     | _    | 1    | _    | _    | _    | _    |      | REFCLK | I3R<3:0> |      | 0000       |

| 14F4                        | REFCLKI4R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | 1    | _    | _    | _    | _    | _    | 1      | _        | 1    | 0000       |

| 14F4                        | NLI OLNIAN           | 15:0      |       | _     | _     | _     | _     | -     | _    |      | _    | _    | _    | _    |      | REFCLK | I4R<3:0> |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

| ŭ            |

|--------------|

| 60           |

| JS60001320D- |

| 320          |

| ç            |

| page         |

| 77           |

| _            |

TABLE 20-1: SERIAL QUADRATURE INTERFACE (SQI) REGISTER MAP (CONTINUED)

|                             | LL 20-1          |           |       | Q O A D I | .,    |                 | /        | ٠, ٠٠٠         | O.O . E.      |               |                 | 0LD,           |              |               |                |              |               |                |            |

|-----------------------------|------------------|-----------|-------|-----------|-------|-----------------|----------|----------------|---------------|---------------|-----------------|----------------|--------------|---------------|----------------|--------------|---------------|----------------|------------|

| ess                         |                  | 0         |       |           |       |                 |          |                |               | В             | its             |                |              |               |                |              |               |                | "          |

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15 | 30/14     | 29/13 | 28/12           | 27/11    | 26/10          | 25/9          | 24/8          | 23/7            | 22/6           | 21/5         | 20/4          | 19/3           | 18/2         | 17/1          | 16/0           | All Resets |

| 2044                        | SQI1BD<br>STAT   | 31:16     | _     | _         | _     | _               | _        | _              | _             | _             | _               | _              |              | BDSTA         | ΓE<3:0>        |              | DMA<br>START  | DMAACTV        | 0000       |

|                             | SIAI             | 15:0      |       |           |       |                 |          |                |               | BDCON         | N<15:0>         |                |              |               |                |              |               |                | 0000       |

| 2048                        | SQI1BD           | 31:16     | _     | _         | _     | _               | _        | _              | _             | -             |                 | _              | _            | _             | _              | -            | -             | _              | 0000       |

| 2046                        | POLLCON          | 15:0      |       |           |       |                 |          |                |               | POLLCC        | )N<15:0>        |                |              |               |                |              |               |                | 0000       |

| 204C                        | SQI1BD           | 31:16     | 1     | _         | -     |                 | TXSTAT   | ΓE<3:0>        |               | I             |                 | I              |              |               | TX             | BUFCNT<4:    | :0>           |                | 0000       |

| 2040                        | TXDSTAT          | 15:0      | 1     | _         | -     |                 | _        |                | _             | I             |                 |                |              | TXCURBU       | FLEN<7:0>      |              |               |                | 0000       |

| 2050                        |                  | 31:16     | 1     | _         | _     |                 | RXSTA    | ΓE<3:0>        |               | I             | _               | 1              | _            |               | RX             | BUFCNT<4     | :0>           |                | 0000       |

| 2000                        | RXDSTAT          | 15:0      | _     | _         | _     | _               | _        | _              | _             | ı             |                 |                |              | RXCURBU       | FLEN<7:0>      |              |               |                | 0000       |

| 2054                        | SQI1THR          | 31:16     | _     | _         | _     | _               | _        | _              | _             |               | _               | _              | _            | _             | _              | _            | _             | _              | 0000       |

| 2004                        | OQIIIIIN         | 15:0      | _     | _         | _     | _               | _        | _              | _             |               | _               | _              | _            |               | 7              | THRES<4:0>   | >             |                | 0000       |

|                             | SQI1INT          | 31:16     | _     | _         | _     | _               | _        | _              | _             | _             | _               | _              | _            | _             | _              | _            | _             | _              | 0000       |

| 2058                        | SIGEN            | 15:0      | _     | _         | _     | _               | DMAEISE  | PKT<br>DONEISE | BD<br>DONEISE | CON<br>THRISE | CON<br>EMPTYISE | CON<br>FULLISE | RX<br>THRISE | RX<br>FULLISE | RX<br>EMPTYISE | TX<br>THRISE | TX<br>FULLISE | TX<br>EMPTYISE | 0000       |

| 205C                        |                  | 31:16     | -     | _         | _     | _               | _        | _              | _             | I             | _               | _              | _            | _             | _              | I            | -             | _              | 0000       |

| 2030                        | TAPCON           | 15:0      | -     | _         |       |                 | CLKIND   | LY<5:0>        |               |               |                 | DATAOUT        | DLY<3:0>     |               |                | CLKOUT       | DLY<3:0>      |                | 0000       |

| 2060                        | OGII             | 31:16     | 1     | _         | -     |                 | _        |                | _             | I             |                 | I              |              | STATPOS       | TYPEST         | AT<1:0>      | STATBY        | TES<1:0>       | 0000       |

| 2000                        | MEMSTAT          | 15:0      |       |           |       |                 |          |                |               | STATDA        | TA<15:0>        |                |              |               |                |              |               |                | 0000       |

| 2064                        | SQI1<br>XCON3    | 31:16     | -     | _         | -     | INIT1<br>SCHECK | INIT1COL | JNT<1:0>       | INIT1TY       | PE<1:0>       |                 |                |              | INIT1CM       | 1D3<7:0>       |              |               |                | 0000       |

|                             | ACONS            | 15:0      |       |           |       | INIT1CM         | ID2<7:0> |                |               |               |                 |                |              | INIT1CM       | 1D1<7:0>       |              |               |                | 0000       |

| 2068                        | SQI1<br>XCON4    | 31:16     |       | _         | _     | INIT2<br>SCHECK | INIT2COL | JNT<1:0>       | INIT2TY       | PE<1:0>       |                 |                |              | INIT2CM       | 1D3<7:0>       |              |               |                | 0000       |

|                             | ACCIN4           | 15:0      |       | •         |       | INIT2CM         | ID2<7:0> |                |               | •             |                 | •              | •            | INIT2CM       | 1D1<7:0>       | •            | •             | •              | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

### REGISTER 23-9: PMRADDR: PARALLEL PORT READ ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|------------------------|------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04:04        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                      | _                      | _                 | _                 | _                 | -                 | _                | _                |

| 00.40        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                        |                        | _                 | _                 | _                 | 1                 | _                | _                |

|              | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | RCS2 <sup>(1)</sup>    | RCS1 <sup>(3)</sup>    |                   |                   |                   | .40.0.            |                  |                  |

|              | RADDR15 <sup>(2)</sup> | RADDR14 <sup>(4)</sup> |                   |                   | RADDF             | (<13.8>           |                  |                  |

| 7:0          | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                        | _                      |                   | RADDR<            | 7:0>              |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 RCS2: Chip Select 2 bit<sup>(1)</sup>

1 = Chip Select 2 is active

0 = Chip Select 2 is inactive (RADDR15 function is selected)

bit 15 RADDR<15>: Target Address bit 15<sup>(2)</sup>

bit 14 RCS1: Chip Select 1 bit<sup>(3)</sup>

1 = Chip Select 1 is active

0 = Chip Select 1 is inactive (RADDR14 function is selected)

bit 14 RADDR<14>: Target Address bit 14<sup>(4)</sup>

bit 13-0 RADDR<13:0>: Address bits

**Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

**2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

3: When the CSF<1:0> bits (PMCON<7:6>) = 10.

**4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

### REGISTER 28-3: ADCCON3: ADC CONTROL REGISTER 3 (CONTINUED)

bit 18 DIGEN2: ADC2 Digital Enable bit

1 = ADC2 is digital enabled

0 = ADC2 is digital disabled

bit 17 **DIGEN1:** ADC1 Digital Enable bit

1 = ADC1 is digital enabled

0 = ADC1 is digital disabled

bit 16 **DIGENO:** ADC0 Digital Enable bit

1 = ADC0 is digital enabled

0 = ADC0 is digital disabled

bit 15-13 VREFSEL<2:0>: Voltage Reference (VREF) Input Selection bits

| VREFSEL<2:0> | ADREF+               | ADREF-         |  |  |  |  |

|--------------|----------------------|----------------|--|--|--|--|

| 1xx          | Reserved; do not use |                |  |  |  |  |

| 011          | External VREFH       | External VREFL |  |  |  |  |

| 010          | AVDD                 | External VREFL |  |  |  |  |

| 001          | External VREFH       | AVss           |  |  |  |  |

| 000          | AVDD                 | AVss           |  |  |  |  |

### bit 12 TRGSUSP: Trigger Suspend bit

1 = Triggers are blocked from starting a new analog-to-digital conversion, but the ADC module is not disabled

0 = Triggers are not blocked

bit 11 **UPDIEN:** Update Ready Interrupt Enable bit

1 = Interrupt will be generated when the UPDRDY bit is set by hardware

0 = No interrupt is generated

bit 10 UPDRDY: ADC Update Ready Status bit

1 = ADC SFRs can be updated

0 = ADC SFRs cannot be updated

**Note:** This bit is only active while the TRGSUSP bit is set and there are no more running conversions of any ADC modules.

bit 9 SAMP: Class 2 and Class 3 Analog Input Sampling Enable bit (1,2,3,4)

1 = The ADC S&H amplifier is sampling

0 = The ADC S&H amplifier is holding

bit 8 RQCNVRT: Individual ADC Input Conversion Request bit

This bit and its associated ADINSEL<5:0> bits enable the user to individually request an analog-to-digital conversion of an analog input through software.

- 1 = Trigger the conversion of the selected ADC input as specified by the ADINSEL<5:0> bits

- 0 = Do not trigger the conversion

**Note:** This bit is automatically cleared in the next ADC clock cycle.

### bit 7 GLSWTRG: Global Level Software Trigger bit

- 1 = Trigger conversion for ADC inputs that have selected the GLSWTRG bit as the trigger signal, either through the associated TRGSRC<4:0> bits in the ADCTRGx registers or through the STRGSRC<4:0> bits in the ADCCON1 register

- 0 = Do not trigger an analog-to-digital conversion

- **Note 1:** The SAMP bit has the highest priority and setting this bit will keep the S&H circuit in Sample mode until the bit is cleared. Also, usage of the SAMP bit will cause settings of SAMC<9:0> bits (ADCCON2<25:16>) to be ignored.

- 2: The SAMP bit only connects Class 2 and Class 3 analog inputs to the shared ADC, ADC7. All Class 1 analog inputs are not affected by the SAMP bit.

- **3:** The SAMP bit is not a self-clearing bit and it is the responsibility of application software to first clear this bit and only after setting the RQCNVRT bit to start the analog-to-digital conversion.

- **4:** Normally, when the SAMP and RQCNVRT bits are used by software routines, all TRGSRCx<4:0> bits and STRGSRC<4:0> bits should be set to '00000' to disable all external hardware triggers and prevent them from interfering with the software-controlled sampling command signal SAMP and with the software-controlled trigger RQCNVRT.

### REGISTER 28-4: ADCTRGMODE: ADC TRIGGERING MODE FOR DEDICATED ADC REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 31:24        | _                 |                   | _                 | _                 | _                 | _                 | SH4AL            | .T<1:0>          |

| 22.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | SH3ALT<1:0>       |                   | SH2ALT<1:0>       |                   | SH1ALT<1:0>       |                   | SH0ALT<1:0>      |                  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | STRGEN4           | STRGEN3           | STRGEN2           | STRGEN1          | STRGEN0          |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 |                   | _                 | SSAMPEN4          | SSAMPEN3          | SSAMPEN2          | SSAMPEN1         | SSAMPEN0         |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25-24 SH4ALT<1:0>: ADC4 Analog Input Select bit

11 = Reserved

10 = Reserved

01 = AN49

00 = AN4

bit 23-22 SH3ALT<1:0>: ADC3 Analog Input Select bit

11 = Reserved

10 = Reserved

01 = AN48

00 = AN3

bit 21-20 SH2ALT<1:0>: ADC2 Analog Input Select bit

11 = Reserved

10 = Reserved

01 = AN47

00 = AN2

bit 19-18 SH1ALT<1:0>: ADC1 Analog Input Select bit

11 = Reserved

10 = Reserved

01 = AN46

00 = AN1

bit 17-16 SH0ALT<1:0>: ADC0 Analog Input Select bit

11 = Reserved

10 = Reserved

01 = AN45

00 = AN0

bit 15-13 Unimplemented: Read as '0'

bit 12 STRGEN4: ADC4 Presynchronized Triggers bit

1 = ADC4 uses presynchronized triggers

0 = ADC4 does not use presynchronized triggers

bit 11 STRGEN3: ADC3 Presynchronized Triggers bit

1 = ADC3 uses presynchronized triggers

0 = ADC3 does not use presynchronized triggers

bit 10 STRGEN2: ADC2 Presynchronized Triggers bit

1 = ADC2 uses presynchronized triggers

0 = ADC2 does not use presynchronized triggers

### REGISTER 28-17: ADCTRG1: ADC TRIGGER SOURCE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | _                 | _                 | _                 | TRGSRC3<4:0>      |                   |                   |                  |                  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | _                 | -                 | _                 | TRGSRC2<4:0>      |                   |                   |                  |                  |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | _                 | _                 | _                 |                   | Т                 | RGSRC1<4:0        | )>               |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | _                 |                   | _                 | TRGSRC0<4:0>      |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-24 TRGSRC3<4:0>: Trigger Source for Conversion of Analog Input AN3 Select bits

11111 = Reserved

•

01101 = Reserved

01100 = Comparator 2 (COUT)

01011 = Comparator 1 (COUT)

01010 = OCMP5

01001 = OCMP3

01000 = OCMP1

00111 = TMR5 match

00110 = TMR3 match

00101 = TMR1 match

00100 = INT0 External interrupt

00011 = STRIG

00010 = Global level software trigger (GLSWTRG)

00001 = Global software edge Trigger (GSWTRG)

00000 = No Trigger

For STRIG, in addition to setting the trigger, it also requires programming of the STRGSRC<4:0> bits (ADCCON1<20:16>) to select the trigger source, and requires the appropriate CSS bits to be set in the ADCCSSx registers.

bit 23-21 Unimplemented: Read as '0'

bit 20-16 **TRGSRC2<4:0>:** Trigger Source for Conversion of Analog Input AN2 Select bits See bits 28-24 for bit value definitions.

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **TRGSRC1<4:0>:** Trigger Source for Conversion of Analog Input AN1 Select bits See bits 28-24 for bit value definitions.

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **TRGSRC0<4:0>:** Trigger Source for Conversion of Analog Input AN0 Select bits See bits 28-24 for bit value definitions.

### REGISTER 28-28: ADCEIEN1: ADC EARLY INTERRUPT ENABLE REGISTER 1

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 04:04        | R/W-0                 |

| 31:24        | EIEN31 <sup>(1)</sup> | EIEN30 <sup>(1)</sup> | EIEN29 <sup>(1)</sup> | EIEN28 <sup>(1)</sup> | EIEN27 <sup>(1)</sup> | EIEN26 <sup>(1)</sup> | EIEN25 <sup>(1)</sup> | EIEN24 <sup>(1)</sup> |

| 00:40        | R/W-0                 |

| 23:16        | EIEN23 <sup>(1)</sup> | EIEN22 <sup>(1)</sup> | EIEN21 <sup>(1)</sup> | EIEN20 <sup>(1)</sup> | EIEN19 <sup>(1)</sup> | EIEN18                | EIEN17                | EIEN16                |

| 45.0         | R/W-0                 |

| 15:8         | EIEN15                | EIEN14                | EIEN13                | EIEN12                | EIEN11                | EIEN10                | EIEN9                 | EIEN8                 |

| 7.0          | R/W-0                 |

| 7:0          | EIEN7                 | EIEN6                 | EIEN5                 | EIEN4                 | EIEN3                 | EIEN2                 | EIEN1                 | EIEN0                 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 **EIEN31:EIEN0:** Early Interrupt Enable for Analog Input bits

- 1 = Early Interrupts are enabled for the selected analog input. The interrupt is generated after the early interrupt event occurs (indicated by the EIRDYx bit ('x' = 31-0) of the ADCEISTAT1 register)

- 0 = Interrupts are disabled

Note 1: This bit is not available on 64-pin devices.

### **REGISTER 28-29: ADCEIEN2: ADC EARLY INTERRUPT ENABLE REGISTER 2**

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 24.24        | U-0                   |

| 31:24        |                       | _                     | _                     | _                     | _                     | 1                     | -                     | _                     |

| 22.40        | U-0                   |

| 23:16        | -                     | _                     | _                     | _                     | _                     | 1                     |                       |                       |

| 45.0         | U-0                   | U-0                   | U-0                   | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

| 15:8         |                       | _                     | -                     | EIEN44 <sup>(2)</sup> | EIEN43 <sup>(2)</sup> | EIEN42 <sup>(2)</sup> | EIEN41 <sup>(2)</sup> | EIEN40 <sup>(2)</sup> |

| 7.0          | R/W-0                 |

| 7:0          | EIEN39 <sup>(2)</sup> | EIEN38 <sup>(2)</sup> | EIEN37 <sup>(2)</sup> | EIEN36 <sup>(2)</sup> | EIEN35 <sup>(2)</sup> | EIEN34 <sup>(1)</sup> | EIEN33 <sup>(1)</sup> | EIEN32 <sup>(1)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-13 Unimplemented: Read as '0'

bit 12-0 EIEN44:EIEN32: Early Interrupt Enable for Analog Input bits

- 1 = Early Interrupts are enabled for the selected analog input. The interrupt is generated after the early interrupt event occurs (indicated by the EIRDYx bit ('x' = 44-32) of the ADCEISTAT2 register)

- 0 = Interrupts are disabled

- Note 1: This bit is not available on 64-pin devices.

- 2: This bit is not available on 64-pin and 100-pin devices.

# REGISTER 30-17: ETHFRMTXOK: ETHERNET CONTROLLER FRAMES TRANSMITTED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | -                | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | -                | _                |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 13.6         |                   | FRMTXOKCNT<15:8>  |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          |                   |                   |                   | FRMTXOK           | (CNT<7:0>         |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **FRMTXOKCNT<15:0>:** Frame Transmitted OK Count bits Increment counter for frames successfully transmitted.

Note 1: This register is only used for TX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- 3: It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

## REGISTER 30-26: EMAC1IPGR: ETHERNET CONTROLLER MAC NON-BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        |                   | _                 | -                 | _                 | -                 | _                 | _                | _                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 15:8         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |  |  |  |  |

| 15.6         | _                 |                   | NB2BIPKTGP1<6:0>  |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |  |  |  |  |

| 7.0          | _                 |                   |                   | NB2E              | 3IPKTGP2<6:       | 0>                |                  |                  |  |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-15 Unimplemented: Read as '0'

### bit 14-8 NB2BIPKTGP1<6:0>: Non-Back-to-Back Interpacket Gap Part 1 bits

This is a programmable field representing the optional carrierSense window referenced in section 4.2.3.2.1 "Deference" of the IEEE 80.23 Specification. If carrier is detected during the timing of IPGR1, the MAC defers to carrier. If, however, carrier becomes after IPGR1, the MAC continues timing IPGR2 and transmits, knowingly causing a collision, thus ensuring fair access to medium. Its range of values is 0x0 to IPGR2. Its recommend value is 0xC (12d).

bit 7 Unimplemented: Read as '0'

### bit 6-0 NB2BIPKTGP2<6:0>: Non-Back-to-Back Interpacket Gap Part 2 bits

This is a programmable field representing the non-back-to-back Inter-Packet-Gap. Its recommended value is 0x12 (18d), which represents the minimum IPG of  $0.96 \mu s$  (in 100 Mbps) or  $9.6 \mu s$  (in 10 Mbps).

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

### REGISTER 30-38: EMAC1SA1: ETHERNET CONTROLLER MAC STATION ADDRESS 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 | -                 | _                 | _                 | -                 |                  | -                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 | -                 | _                 | _                 | -                 |                  | -                |  |  |

| 15:8         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |

| 15.6         | STNADDR4<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |

| 7.0          |                   |                   |                   | STNADD            | R3<7:0>           |                   |                  |                  |  |  |

| Legend:           |                  | P = Programmable bit |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-8 STNADDR4<7:0>: Station Address Octet 4 bits

These bits hold the fourth transmitted octet of the station address.

bit 7-0 STNADDR3<7:0>: Station Address Octet 3 bits

These bits hold the third transmitted octet of the station address.

**Note 1:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

**2:** This register is loaded at reset from the factory preprogrammed station address.

TABLE 33-2: PERIPHERAL MODULE DISABLE REGISTER SUMMARY

| ess                         |                                 |           |       | Bits  |        |        |         |         |         |         |        |         |       |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|--------|--------|---------|---------|---------|---------|--------|---------|-------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13  | 28/12  | 27/11   | 26/10   | 25/9    | 24/8    | 23/7   | 22/6    | 21/5  | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 0040                        | PMD1                            | 31:16     | _     | ı     | _      | _      | I       | _       | _       | _       |        | _       | _     |        | _      | _      | _      | I      | 0000       |

| 0040                        | TIMET                           | 15:0      | _     | _     | _      | CVRMD  | _       | _       | _       | _       | _      | _       |       | _      | _      | _      | _      | ADCMD  | 0000       |

| 0050                        | PMD2                            | 31:16     | _     |       | _      | _      |         | _       | _       | _       | _      | _       | _     | _      | _      | _      | _      | -      | 0000       |

| 0030                        | FIVIDZ                          | 15:0      | _     |       | _      | _      | I       | _       | _       | _       | _      | _       | _     | _      |        | _      | CMP2MD | CMP1MD | 0000       |

| 0060                        | PMD3                            | 31:16     | _     | 1     |        | -      | -       | _       | _       | OC9MD   | OC8MD  | OC7MD   | OC6MD | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000       |

| 0000                        | FIVIDS                          | 15:0      | _     | 1     |        | -      | -       | _       | _       | IC9MD   | IC8MD  | IC7MD   | IC6MD | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD  | 0000       |

| 0070                        | PMD4                            | 31:16     | _     | _     | _      | _      | _       | _       | _       | _       | _      | _       | _     | _      | _      | _      | _      | -      | 0000       |

| 0070                        | FIVID4                          | 15:0      | _     |       | _      | _      |         | _       | _       | T9MD    | T8MD   | T7MD    | T6MD  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | 0000       |

| 0080                        | PMD5                            | 31:16     | _     | 1     | CAN2MD | CAN1MD | -       | _       | _       | USBMD   | _      | _       | _     | I2C5MD | I2C4MD | I2C3MD | I2C2MD | I2C1MD | 0000       |

| 0000                        | PIVIDS                          | 15:0      | -     | _     | SPI6MD | SPI5MD | SPI4MD  | SPI3MD  | SPI2MD  | SPI1MD  | _      | _       | U6MD  | U5MD   | U4MD   | U3MD   | U2MD   | U1MD   | 0000       |

| 0000                        | PMD6                            | 31:16     | _     | -     | _      | ETHMD  | _       | _       | _       | _       | SQI1MD | _       |       | _      | 1      | _      | EBIMD  | PMPMD  | 0000       |

| 0090                        | PIVIDO                          | 15:0      | _     | ı     | _      | _      | REFO4MD | REFO3MD | REFO2MD | REFO1MD | _      | _       | _     | _      | _      | _      | _      | RTCCMD | 0000       |

| 0040                        | PMD7                            | 31:16     | _     |       | _      | _      | 1       | _       | _       | _       |        | CRYPTMD | _     | RNGMD  | _      | _      | _      | 1      | 0000       |

| 00A0                        | PIVID/                          | 15:0      | _     | _     | _      | _      | _       | _       | _       | _       | _      | _       | _     | DMAMD  | _      | _      | _      | _      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

TABLE 37-23: I/O TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated)                                                                                                      |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |  |  |  |  |

|               | I                                                               |                                                                                                                                      | 40 0 2 IA 2 1 120 0 101 Externada |                     |      |       |               |  |  |

|---------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|------|-------|---------------|--|--|

| Param.<br>No. | Symbol                                                          | Characteristics <sup>(2)</sup>                                                                                                       | Min.                              | Typ. <sup>(1)</sup> | Max. | Units | Conditions    |  |  |

| DO32          | TIOF                                                            | Port Output Fall Time I/O Pins: 4x Source Driver Pins - RA3, RA9, RA10, RA14, RA15 RB0-RB2, RB4, RB6-RB7, RB11, RB13                 | _                                 | _                   | 9.5  | ns    | CLOAD = 50 pF |  |  |

|               |                                                                 | RC12-RC15<br>RD0, RD6-RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8<br>RG15<br>RH0, RH1, RH4-RH6, RH8-RH13<br>RJ0-RJ2, RJ8, RJ9, RJ11 | ı                                 | _                   | 6    | ns    | CLOAD = 20 pF |  |  |

|               |                                                                 | Port Output Fall Time I/O Pins: 8x Source Driver Pins - RA0-RA2, RA4, RA5 RB3, RB5, RB8-RB10, RB12, RB14, RB15 RC1-RC4               | -                                 | _                   | 8    | ns    | CLOAD = 50 pF |  |  |

|               | RD15<br>RE4-RE7<br>RF0, RF4, RF<br>RG0, RG1, RG<br>RH2, RH3, RF | RE4-RE7<br>RF0, RF4, RF5, RF12, RF13<br>RG0, RG1, RG6-RG9<br>RH2, RH3, RH7, RH14, RH15<br>RJ3-RJ7, RJ10, RJ12-RJ15                   | ĺ                                 |                     | 6    | ns    | CLOAD = 20 pF |  |  |

|               |                                                                 | Port Output Fall Time I/O Pins: 12x Source Driver Pins - RA6, RA7                                                                    | _                                 | _                   | 3.5  | ns    | CLOAD = 50 pF |  |  |

|               |                                                                 | RE0-RE3<br>RF1<br>RG12-RG14                                                                                                          | _                                 | _                   | 2    | ns    | CLOAD = 20 pF |  |  |

| DI35          | TINP                                                            | INTx Pin High or Low Time                                                                                                            | 5                                 | _                   | _    | ns    | _             |  |  |

| DI40          | TRBP                                                            | CNx High or Low Time (input)                                                                                                         | 5                                 | _                   |      | ns    | _             |  |  |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

<sup>2:</sup> This parameter is characterized, but not tested in manufacturing.

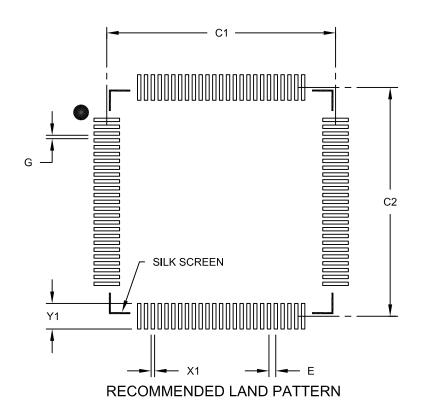

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | N   | MILLIMETERS |          |      |  |

|---------------------------|-----|-------------|----------|------|--|

| Dimension                 | MIN | NOM         | MAX      |      |  |

| Contact Pitch             | E   |             | 0.40 BSC |      |  |

| Contact Pad Spacing       | C1  |             | 13.40    |      |  |

| Contact Pad Spacing       | C2  |             | 13.40    |      |  |

| Contact Pad Width (X100)  | X1  |             |          | 0.20 |  |

| Contact Pad Length (X100) | Y1  |             |          | 1.50 |  |

| Distance Between Pads     | G   | 0.20        |          |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

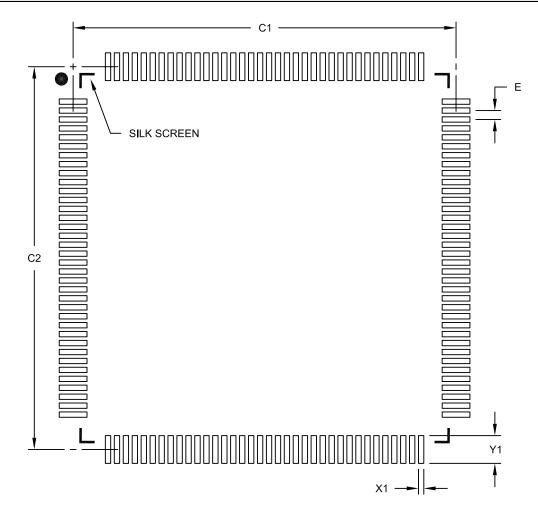

144-Lead Plastic Low Profile Quad Flatpack (PL) - 20x20x1.40 mm Body [LQFP] 2.00 mm Footprint

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                           | M   | MILLIMETERS |          |      |  |

|---------------------------|-----|-------------|----------|------|--|

| Dimension                 | MIN | NOM         | MAX      |      |  |

| Contact Pitch             | E   |             | 0.50 BSC |      |  |

| Contact Pad Spacing       | C1  |             | 21.40    |      |  |

| Contact Pad Spacing       | C2  |             | 21.40    |      |  |

| Contact Pad Width (X144)  | X1  |             |          | 0.30 |  |

| Contact Pad Length (X144) | Y1  |             |          | 1.55 |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2044B

### A.4 Resets

The PIC32MZ EF family of devices has updated the resets modules to incorporate the new handling of NMI resets from the WDT, DMT, and the FSCM. In addition, some bits have been moved, as summarized in Table A-5.

TABLE A-5: RESET DIFFERENCES

| PIC32MX5XX/6XX/7XX Feature                                                | PIC32MZ EF Feature                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Power Reset                                                               |                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                                                                           | The VREGS bit, which controls whether the internal regulator is enabled in Sleep mode, has been moved from RCON in PIC32MX5XX/6XX/7XX devices to a new PWRCON register in PIC32MZ EF devices.                               |  |  |  |  |  |  |  |

| VREGS (RCON<8>)                                                           | VREGS (PWRCON<0>)                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 1 = Regulator is enabled and is on during Sleep mode                      | 1 = Voltage regulator will remain active during Sleep                                                                                                                                                                       |  |  |  |  |  |  |  |

| 0 = Regulator is disabled and is off during Sleep mode                    | 0 = Voltage regulator will go to Stand-by mode during Sleep                                                                                                                                                                 |  |  |  |  |  |  |  |

| Watchdog Timer Reset                                                      |                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| On PIC32MX devices, a WDT expiration immediately triggers a device reset. | On PIC32MZ EF devices, the WDT expiration now causes a NMI. The WDTO bit in RNMICON indicates that the WDT caused the NMI. A new timer, NMICNT, runs when the WDT NMI is triggered, and if it expires, the device is reset. |  |  |  |  |  |  |  |

| WDT expiration immediately causes a device reset.                         | WDT expiration causes a NMI, which can then trigger the device reset. WDTO (RNMICON<24>) 1 = WDT time-out has occurred and caused a NMI 0 = WDT time-out has not occurred                                                   |  |  |  |  |  |  |  |

|                                                                           | NMICNT<7:0> (RNMICON<7:0>)                                                                                                                                                                                                  |  |  |  |  |  |  |  |

### A.5 USB

The PIC32MZ EF family of devices has a new Hi-Speed USB module, which requires the updated USB stack from Microchip. In addition, the USB PLL was also updated. See **A.1** "Oscillator and PLL Configuration" for more information and Table A-6 for a list of additional differences.

TABLE A-6: USB DIFFERENCES

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                            | PIC32MZ EF Feature                                                                                                |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Debug Mode                                                                                                                                                                            |                                                                                                                   |  |  |  |  |  |  |

| On PIC32MX devices, when stopping on a breakpoint during debugging, the USB module can be configured to stop or continue execution from the Freeze Peripherals dialog in MPLAB X IDE. | 1, 0                                                                                                              |  |  |  |  |  |  |

| VBUSC                                                                                                                                                                                 | Pin                                                                                                               |  |  |  |  |  |  |

| PIC32MX devices feature a VBUSON pin for controlling the external transceiver power supply.                                                                                           | On PIC32MZ EF devices, the VBUSON pin is not available. A port pin can be used to achieve the same functionality. |  |  |  |  |  |  |