Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32 <sup>®</sup> M-Class                                                      |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-TQFP                                                                         |

| Supplier Device Package    | 144-TQFP (16x16)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efk144-i-ph |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                                                                                           |             |                |                                                                                           |  |  |  |  |  |

|----------|------------------------|-----------------|-----------------|-------------------------------------------------------------------------------------------|-------------|----------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP                                                                  | Pin<br>Type | Buffer<br>Type | Description                                                                               |  |  |  |  |  |

| PMA0     | 30                     | 44              | B24             | 30                                                                                        | I/O         | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |  |  |  |  |  |

| PMA1     | 29                     | 43              | A28             | Parallel Master Port Address bit 1 Input (Buffered Slave modes) and Output (Master modes) |             |                |                                                                                           |  |  |  |  |  |

| PMA2     | 10                     | 16              | B9              | 21                                                                                        | 0           | _              | Parallel Master Port Address (Demultiplexed Master                                        |  |  |  |  |  |

| PMA3     | 6                      | 12              | B7              | 52                                                                                        | 0           | _              | modes)                                                                                    |  |  |  |  |  |

| PMA4     | 5                      | 11              | A8              | 68                                                                                        | 0           | _              |                                                                                           |  |  |  |  |  |

| PMA5     | 4                      | 2               | B1              | 2                                                                                         | 0           | _              | 1                                                                                         |  |  |  |  |  |

| PMA6     | 16                     | 6               | B3              | 6                                                                                         | 0           | —              |                                                                                           |  |  |  |  |  |

| PMA7     | 22                     | 33              | A23             | 48                                                                                        | 0           | _              | 1                                                                                         |  |  |  |  |  |

| PMA8     | 42                     | 65              | A44             | 91                                                                                        | 0           | _              |                                                                                           |  |  |  |  |  |

| PMA9     | 41                     | 64              | B36             | 90                                                                                        | 0           | _              |                                                                                           |  |  |  |  |  |

| PMA10    | 21                     | 32              | B18             | 47                                                                                        | 0           | _              |                                                                                           |  |  |  |  |  |

| PMA11    | 27                     | 41              | A27             | 29                                                                                        | 0           | _              | 1                                                                                         |  |  |  |  |  |

| PMA12    | 24                     | 7               | A6              | 11                                                                                        | 0           | _              |                                                                                           |  |  |  |  |  |

| PMA13    | 23                     | 34              | B19             | 28                                                                                        | 0           | _              |                                                                                           |  |  |  |  |  |

| PMA14    | 45                     | 61              | A42             | 87                                                                                        | 0           | _              |                                                                                           |  |  |  |  |  |

| PMA15    | 43                     | 68              | B38             | 97                                                                                        | 0           |                |                                                                                           |  |  |  |  |  |

| PMCS1    | 45                     | 61              | A42             | 87                                                                                        | 0           | _              | Parallel Master Port Chip Select 1 Strobe                                                 |  |  |  |  |  |

| PMCS2    | 43                     | 68              | B38             | 97                                                                                        | 0           | _              | Parallel Master Port Chip Select 2 Strobe                                                 |  |  |  |  |  |

| PMD0     | 58                     | 91              | B52             | 135                                                                                       | I/O         | TTL/ST         | Parallel Master Port Data (Demultiplexed Master                                           |  |  |  |  |  |

| PMD1     | 61                     | 94              | A64             | 138                                                                                       | I/O         | TTL/ST         | mode) or Address/Data (Multiplexed Master modes)                                          |  |  |  |  |  |

| PMD2     | 62                     | 98              | A66             | 142                                                                                       | I/O         | TTL/ST         | 4                                                                                         |  |  |  |  |  |

| PMD3     | 63                     | 99              | B56             | 143                                                                                       | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |  |

| PMD4     | 64                     | 100             | A67             | 144                                                                                       | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |  |

| PMD5     | 1                      | 3               | A3              | 3                                                                                         | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |  |

| PMD6     | 2                      | 4               | B2              | 4                                                                                         | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |  |

| PMD7     | 3                      | 5               | A4              | 5                                                                                         | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |  |

| PMD8     |                        | 88              | B50             | 128                                                                                       | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |  |

| PMD9     |                        | 87              | A60             | 120                                                                                       | I/O         | TTL/ST         | 4                                                                                         |  |  |  |  |  |

| PMD10    |                        | 86              | B49             | 127                                                                                       | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |  |

| PMD11    |                        | 85              | A59             | 123                                                                                       | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |  |

| PMD12    |                        | 79              | B43             | 112                                                                                       | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |  |

| PMD13    |                        | 80              | A54             | 112                                                                                       | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |  |

| PMD13    |                        | 77              | B42             | 110                                                                                       | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |  |

| PMD15    |                        | 78              | A53             | 110                                                                                       | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |  |

| PMALL    | 30                     | 44              | B24             | 30                                                                                        | 0           |                | Parallel Master Port Address Latch Enable Low Byte (Multiplexed Master modes)             |  |  |  |  |  |

| PMALH    | 29                     | 43              | A28             | 51                                                                                        | 0           |                | Parallel Master Port Address Latch Enable High Byte<br>(Multiplexed Master modes)         |  |  |  |  |  |

| PMRD     | 53                     | 9               | A7              | 13                                                                                        | 0           |                | Parallel Master Port Read Strobe                                                          |  |  |  |  |  |

| PMWR     | 52                     | 8               | B5              | 10                                                                                        | 0           | <u> </u>       | Parallel Master Port Write Strobe                                                         |  |  |  |  |  |

|          |                        | MOS-comp        |                 |                                                                                           |             | Analog –       | Analog input P = Power                                                                    |  |  |  |  |  |

#### TABLE 1-12: PMP PINOUT I/O DESCRIPTIONS

egend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

PPS = Peripheral Pin Select

Analog = Analog input O = Output

I = Input

| REGISTER 4-8: | SBTxREGy: SYSTEM BUS TARGET 'x' REGION 'y' REGISTER |  |

|---------------|-----------------------------------------------------|--|

|               | (x' = 0.13; y' = 0.8)                               |  |

|              |                   | (x = 0 - 13;      | y = 0-o)          |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | BASE              | <21:14>           |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | BASE              | =<13:6>           |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | U-0              |

| 15:8         |                   |                   | BAS               | E<5:0>            |                   |                   | PRI              | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 7:0          |                   |                   | SIZE<4:0>         |                   |                   | _                 | _                | —                |

#### Legend:

| 3                 |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

more information.

| bit 31-10 | BASE<21:0>: Region Base Address bits                                                                                            |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| bit 9     | PRI: Region Priority Level bit                                                                                                  |

|           | 1 = Level 2                                                                                                                     |

|           | 0 = Level 1                                                                                                                     |

| bit 8     | Unimplemented: Read as '0'                                                                                                      |

| bit 7-3   | SIZE<4:0>: Region Size bits                                                                                                     |

|           | Permissions for a region are only active is the SIZE is non-zero.<br>11111 = Region size = $2^{(SIZE - 1)} \times 1024$ (bytes) |

|           | •                                                                                                                               |

|           | •                                                                                                                               |

|           | •                                                                                                                               |

|           | 00001 = Region size = 2 <sup>(SIZE - 1)</sup> x 1024 (bytes)                                                                    |

|           | 00000 = Region is not present                                                                                                   |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                      |

|           |                                                                                                                                 |

Note 1: Refer to Table 4-6 for the list of available targets and their descriptions. 2: For some target regions, certain bits in this register are read-only with preset values. See Table 4-6 for

|                  | Clock Source     |      |                  |                  |               |                       |        |                  |        |                  |        |        |                 |          |                 |

|------------------|------------------|------|------------------|------------------|---------------|-----------------------|--------|------------------|--------|------------------|--------|--------|-----------------|----------|-----------------|

| Peripheral       | FRC              | LPRC | SOSC             | SYSCLK           | <b>USBCLK</b> | PBCLK1 <sup>(1)</sup> | PBCLK2 | <b>PBCLK3</b>    | PBCLK4 | PBCLK5           | PBCLK7 | PBCLK8 | <b>REFCLK01</b> | REFCLK02 | <b>REFCLK03</b> |

| CPU              |                  |      |                  |                  |               |                       |        |                  |        |                  | Х      |        |                 |          |                 |

| WDT              |                  | Х    |                  |                  |               | X <sup>(2)</sup>      |        |                  |        |                  |        |        |                 |          |                 |

| Deadman Timer    |                  |      |                  |                  |               | X <sup>(2)</sup>      |        |                  |        |                  | Х      |        |                 |          |                 |

| Flash            | X <sup>(2)</sup> |      |                  | X <sup>(2)</sup> |               | X <sup>(2)</sup>      |        |                  |        |                  |        |        |                 |          |                 |

| ADC              | Х                |      |                  | Х                |               |                       |        | χ <sup>(3)</sup> |        |                  |        |        |                 |          | Х               |

| Comparator       |                  |      |                  |                  |               |                       |        | Х                |        |                  |        |        |                 |          |                 |

| Crypto           |                  |      |                  |                  |               |                       |        |                  |        | Х                |        |        |                 |          |                 |

| RNG              |                  |      |                  |                  |               |                       |        |                  |        | Х                |        |        |                 |          |                 |

| USB              |                  |      |                  |                  | Х             |                       |        |                  |        | X <sup>(3)</sup> |        |        |                 |          |                 |

| CAN              |                  |      |                  |                  |               |                       |        |                  |        | Х                |        |        |                 |          |                 |

| Ethernet         |                  |      |                  |                  |               |                       |        |                  |        | χ(3)             |        |        |                 |          |                 |

| PMP              |                  |      |                  |                  |               |                       | Х      |                  |        |                  |        |        |                 |          |                 |

| I <sup>2</sup> C |                  |      |                  |                  |               |                       | Х      |                  |        |                  |        |        |                 |          |                 |

| UART             |                  |      |                  |                  |               |                       | Х      |                  |        |                  |        |        |                 |          |                 |

| RTCC             |                  | Х    | Х                |                  |               | X <sup>(2)</sup>      |        |                  |        |                  |        |        |                 |          |                 |

| EBI              |                  |      |                  |                  |               |                       |        |                  |        |                  |        | Х      |                 |          |                 |

| SQI              |                  |      |                  |                  |               |                       |        |                  |        | χ(3)             |        |        |                 | Х        |                 |

| SPI              |                  |      |                  |                  |               |                       | Х      |                  |        |                  |        |        | Х               |          |                 |

| Timers           |                  |      | X <sup>(4)</sup> |                  |               |                       |        | Х                |        |                  |        |        |                 |          |                 |

| Output Compare   |                  |      |                  |                  |               |                       |        | Х                |        |                  |        |        |                 |          |                 |

| Input Capture    |                  |      |                  |                  |               |                       |        | Х                |        |                  |        |        |                 |          |                 |

| Ports            |                  |      |                  |                  |               |                       |        |                  | Х      |                  |        |        |                 |          |                 |

| DMA              |                  |      |                  | Х                |               |                       |        |                  |        |                  |        |        |                 |          |                 |

| Interrupts       |                  |      |                  | Х                |               |                       |        |                  |        |                  |        |        |                 |          |                 |

| Prefetch         |                  |      |                  | Х                |               |                       |        |                  |        |                  |        |        |                 |          |                 |

| OSC2 Pin         |                  |      |                  |                  |               | χ(5)                  |        |                  |        |                  |        |        |                 |          |                 |

#### TABLE 8-1: SYSTEM AND PERIPHERAL CLOCK DISTRIBUTION

Note 1: PBCLK1 is used by system modules and cannot be turned off.

2: SYSCLK/PBCLK1 is used to fetch data from/to the Flash Controller, while the FRC clock is used for programming.

- **3:** Special Function Register (SFR) access only.

- 4: Timer1 only.

- 5: PBCLK1 divided by 2 is available on the OSC2 pin in certain clock modes.

### 8.1 Fail-Safe Clock Monitor (FSCM)

The PIC32MZ EF oscillator system includes a Fail-safe Clock Monitor (FSCM). The FSCM monitors the SYSCLK for continuous operation. If it detects that the SYSCLK has failed, it switches the SYSCLK over to the BFRC oscillator and triggers a NMI. The BFRC is an untuned 8 MHz oscillator that will drive the SYSCLK during FSCM event. When the NMI is executed, software can attempt to restart the main oscillator or shut down the system.

In Sleep mode both the SYSCLK and the FSCM halt, which prevents FSCM detection.

| REGISTE  | ER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER                                                                                                                           |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10-8 | NOSC<2:0>: New Oscillator Selection bits                                                                                                                              |

|          | 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                                                          |

|          | 110 = Reserved                                                                                                                                                        |

|          | 101 = Internal Low-Power RC (LPRC) Oscillator                                                                                                                         |

|          | 100 = Secondary Oscillator (Sosc)<br>011 = Reserved                                                                                                                   |

|          | 010 = Primary Oscillator (Posc) (HS or EC)                                                                                                                            |

|          | 001 = System PLL (SPLL)                                                                                                                                               |

|          | 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                                                          |

|          | On Reset, these bits are set to the value of the FNOSC<2:0> Configuration bits (DEVCFG1<2:0>).                                                                        |

| bit 7    | CLKLOCK: Clock Selection Lock Enable bit                                                                                                                              |

|          | 1 = Clock and PLL selections are locked                                                                                                                               |

|          | 0 = Clock and PLL selections are not locked and may be modified                                                                                                       |

| bit 6-5  | Unimplemented: Read as '0'                                                                                                                                            |

| bit 4    | SLPEN: Sleep Mode Enable bit                                                                                                                                          |

|          | <ul> <li>1 = Device will enter Sleep mode when a WAIT instruction is executed</li> <li>0 = Device will enter Idle mode when a WAIT instruction is executed</li> </ul> |

| hi+ 0    | <b>CF:</b> Clock Fail Detect bit                                                                                                                                      |

| bit 3    |                                                                                                                                                                       |

|          | <ul> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> </ul>                                                             |

| bit 2    | Unimplemented: Read as '0'                                                                                                                                            |

| bit 1    | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                                                                        |

|          | 1 = Enable Secondary Oscillator                                                                                                                                       |

|          | 0 = Disable Secondary Oscillator                                                                                                                                      |

| bit 0    | OSWEN: Oscillator Switch Enable bit <sup>(1)</sup>                                                                                                                    |

|          | 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits                                                                                            |

|          | 0 = Oscillator switch is complete                                                                                                                                     |

| Note 1:  | The reset value for this bit depends on the setting of the IESO bit (DEVCFG1<7>). When IESO = 1, the                                                                  |

| NOLE I.  | reset value is '1'. When IESO = 0, the reset value is '0'.                                                                                                            |

Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

#### REGISTER 8-3: SPLLCON: SYSTEM PLL CONTROL REGISTER

bit 10-8 PLLIDIV<2:0>: System PLL Input Clock Divider bits

- 111 =Divide by 8

- 110 = Divide by 7

- 101 =Divide by 6

- 100 =Divide by 5

- 011 = Divide by 4

- 010 = Divide by 3

- 001 = Divide by 2

- 000 = Divide by 1

The default setting is specified by the FPLLIDIV<2:0> Configuration bits in the DEVCFG2 register. If the PLLICLK is set for FRC, this setting is ignored by the PLL and the divider is set for Divide-by-1. Refer to Register 34-5 in **Section 34.0** "**Special Features**" for information.

- bit 7 PLLICLK: System PLL Input Clock Source bit

- 1 = FRC is selected as the input to the System PLL

- 0 = Posc is selected as the input to the System PLL

The POR default is specified by the FPLLICLK Configuration bit in the DEVCFG2 register. Refer to

Register 34-5 in Section 34.0 "Special Features" for information.

- bit 6-3 Unimplemented: Read as '0'

#### bit 2-0 PLLRANGE<2:0>: System PLL Frequency Range Selection bits

111 = Reserved 110 = Reserved 101 = 34-64 MHz 100 = 21-42 MHz 011 = 13-26 MHz 010 = 8-16 MHz 001 = 5-10 MHz 000 = Bypass The default setting

The default setting is specified by the FPLLRNG<2:0> Configuration bits in the DEVCFG2 register. Refer to Register 34-5 in **Section 34.0** "**Special Features**" for information.

- Note 1: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

- 2: Writes to this register are not allowed if the SPLL is selected as a clock source (COSC<2:0> = 001).

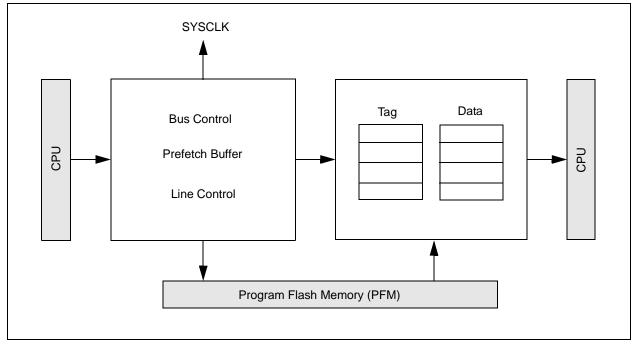

## 9.0 PREFETCH MODULE

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Prefetch module is a performance enhancing module that is included in the PIC32MZ EF family of devices. When running at high-clock rates, Wait states must be inserted into Program Flash Memory (PFM) read transactions to meet the access time of the PFM. Wait states can be hidden to the core by prefetching and storing instructions in a temporary holding area that the CPU can access quickly. Although the data path to the CPU is 32 bits wide, the data path to the PFM is 128 bits wide. This wide data path provides the same bandwidth to the CPU as a 32-bit path running at four times the frequency.

The Prefetch module holds a subset of PFM in temporary holding spaces known as lines. Each line contains a tag and data field. Normally, the lines hold a copy of what is currently in memory to make instructions or data available to the CPU without Flash Wait states.

The following are key features of the Prefetch module:

- 4x16 byte fully-associative lines

- One line for CPU instructions

- · One line for CPU data

- Two lines for peripheral data

- 16-byte parallel memory fetch

- Configurable predictive prefetch

- Error detection and correction

A simplified block diagram of the Prefetch module is shown in Figure 9-1.

#### FIGURE 9-1: PREFETCH MODULE BLOCK DIAGRAM

| IABL                     | LE 10-3:                        | וט        |       | ANNEL | J THROU | JGH CH | ANNEL | 7 REGI |      | AP   |      |      |      |   |

|--------------------------|---------------------------------|-----------|-------|-------|---------|--------|-------|--------|------|------|------|------|------|---|

| ess                      |                                 | Ð         |       |       |         |        |       |        |      | Bit  | s    |      |      |   |

| /irtual Addr<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13   | 28/12  | 27/11 | 26/10  | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | I |

#### A TUDOUCU CUANNEL 7 DE

| ess                         |                                 |               |                  |             |           |       |          |       |      | Bit    | s      |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|------------------|-------------|-----------|-------|----------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15            | 30/14       | 29/13     | 28/12 | 27/11    | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DOLIGOON                        | 31:16         |                  |             |           | CHPIG | SN<7:0>  |       |      |        | _      | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 1060                        | DCH0CON                         | 15:0          | CHBUSY           | _           | CHPIGNEN  | _     | CHPATLEN | _     | —    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | l<1:0> | 0000       |

| 1070                        | DCH0ECON                        | 31:16         | _                | _           | —         | _     | —        | _     | _    | —      |        |        |        | CHAIR  | Q<7:0> |        |        |        | OOFF       |

| 1070                        |                                 | 15:0          |                  |             |           | CHSIR | Q<7:0>   |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | —      | _      |        | FF00       |

| 1080                        | DCH0INT                         | 31:16         | —                | —           | —         | —     | —        | —     | —    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 1000                        | Derioitti                       | 15:0          | —                | —           | —         | _     | —        | —     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 1090                        | DCH0SSA                         | 31:16<br>15:0 |                  | CHSSA<31:0> |           |       |          |       |      |        |        |        |        |        |        |        |        |        |            |

| 10A0                        | DCH0DSA                         | 31:16<br>15:0 |                  | CHDSA<31:0> |           |       |          |       |      |        |        |        |        |        |        |        |        |        |            |

|                             |                                 | 31:16         |                  |             |           |       | _        |       |      |        |        |        |        |        |        |        |        |        | 0000       |

| 10B0                        | DCH0SSIZ                        | 15:0          |                  |             |           |       |          |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         |                  | _           | _         | _     | _        | _     | _    | _      | _      |        | _      | _      |        |        | _      |        | 0000       |

| 10C0                        | DCH0DSIZ                        | 15:0          |                  |             |           |       |          |       |      | CHDSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _                | _           | _         | _     | —        | _     | _    | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 10D0                        | DCH0SPTR                        | 15:0          |                  |             |           |       |          |       |      | CHSPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 4050                        |                                 | 31:16         | _                | _           | _         | _     | _        | _     | _    | _      | _      | —      | _      | _      | —      | _      | _      |        | 0000       |

| 10E0                        | DCH0DPTR                        | 15:0          |                  |             |           |       |          |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 10E0                        | DCH0CSIZ                        | 31:16         | —                | —           | —         | _     | —        | —     | _    | _      |        |        |        |        | -      | _      |        | _      | 0000       |

| 101.0                       | DCI IOCOIZ                      | 15:0          |                  |             |           |       |          |       |      | CHCSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1100                        | DCH0CPTR                        | 31:16         | —                | —           | —         | —     | —        | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      | —      | 0000       |

| 1100                        |                                 | 15:0          |                  |             | · · · · · |       |          |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1110                        | DCH0DAT                         | 31:16         | —                | _           | —         | _     | —        | —     | —    | —      | —      | —      | —      | —      | —      | —      | —      |        | 0000       |

| -                           |                                 | 15:0          |                  |             |           |       |          |       |      | CHPDAT | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1120                        | DCH1CON                         | 31:16         |                  |             |           | CHPIG | N<7:0>   |       |      |        |        | —      | _      | _      | —      |        | _      |        | 0000       |

| -                           |                                 | 15:0          | CHBUSY           | —           | CHPIGNEN  | —     | CHPATLEN | —     | —    | CHCHNS | CHEN   | CHAED  | CHCHN  | CHAEN  | —      | CHEDET | CHPR   | l<1:0> | 0000       |

| 1130                        | DCH1ECON                        | 31:16         | —                | _           | —         | _     | —        | —     | —    | _      |        |        |        | CHAIR  |        |        |        |        | 00FF       |

|                             |                                 | 15:0          |                  |             |           |       | Q<7:0>   |       |      |        | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | —      | —      | -      | FF00       |

| 1140                        | DCH1INT                         | 31:16         | _                |             | -         |       |          |       | _    | _      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0          | —                | —           | _         | —     | —        | _     |      | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 1150                        | DCH1SSA                         | 31:16<br>15:0 | CHSSA<31:0> 0000 |             |           |       |          |       |      |        |        |        |        |        |        |        |        |        |            |

| 1100                        |                                 | 31:16         |                  |             |           |       |          |       |      |        | .24.0. |        |        |        |        |        |        |        | 0000       |

| 1160                        | DCH1DSA                         | 15:0          |                  | CHDSA<31:0> |           |       |          |       |      |        |        |        |        |        |        |        |        |        |            |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information. Note 1:

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

### TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |        |                   |             |       |                    |       |            | Bit    | 5      |            |        |            |         |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------------------|-------------|-------|--------------------|-------|------------|--------|--------|------------|--------|------------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14             | 29/13       | 28/12 | 27/11              | 26/10 | 25/9       | 24/8   | 23/7   | 22/6       | 21/5   | 20/4       | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 1440                        | DCH5DPTR                        | 31:16         | _      | _                 | —           |       | —                  |       | —          | —      |        | _          |        | _          | _       |        |        | _      | 0000       |

| 1 // 10                     | DONODI III                      | 15:0          |        | CHDPTR<15:0> 0000 |             |       |                    |       |            |        |        |            |        |            |         |        |        |        |            |

| 14B0                        | DCH5CSIZ                        | 31:16         | _      | —                 | —           | _     | —                  | _     | —          | —      |        | -          | —      | _          | —       | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        |                   |             |       |                    |       |            | CHCSIZ | <15:0> |            |        |            |         |        |        |        | 0000       |

| 14C0                        | DCH5CPTR                        | 31:16         | —      | _                 | —           | _     |                    | _     |            |        | 45:0   | —          | —      | —          | —       | —      | —      |        | 0000       |

|                             |                                 | 15:0          |        |                   |             |       |                    |       |            | CHCPTR |        |            |        |            |         |        |        |        | 0000       |

| 14D0                        | DCH5DAT                         | 31:16<br>15:0 | —      | _                 | —           |       |                    | _     |            | CHPDAT |        | —          | _      | _          | —       | —      | —      | —      | 0000       |

|                             |                                 |               |        |                   |             |       | N 7.0              |       |            | CHEDAI | <13.0> |            |        |            |         |        |        |        |            |

| 14E0                        | DCH6CON                         | 31:16<br>15:0 | CHBUSY |                   | CHPIGNEN    | CHPIG | N<7:0><br>CHPATLEN |       |            | CHCHNS | CHEN   | —<br>CHAED | CHCHN  | —<br>CHAEN |         |        | CHPR   | -      | 0000       |

|                             |                                 | 31:16         |        |                   | CHPIGNEN    |       |                    |       | _          |        | CHEN   | CHAED      | СПСПИ  | CHAEN      |         | CHEDEI | СПРК   | 1<1:0> | 0000       |

| 14F0                        | DCH6ECON                        | 15:0          |        |                   |             |       | <br>Q<7:0>         | _     |            | _      | CFORCE | CABORT     | PATEN  | SIRQEN     | AIRQEN  | _      | _      | —      | FF00       |

|                             |                                 | 31:16         | _      | _                 | _           | _     | _                  | _     |            | _      | CHSDIE | CHSHIE     | CHDDIE | CHDHIE     | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 1500                        | DCH6INT                         | 15:0          | _      | _                 | _           | _     |                    | _     | _          | _      | CHSDIE | CHSHIF     | CHDDIE | CHDHIF     | CHBCIE  | CHCCIF | CHTAIF | CHERIF | 0000       |

|                             |                                 | 31:16         |        |                   |             |       |                    |       |            |        |        | 01101111   | 0.1551 | 0.15111    | 0.12011 | 0.1001 | 0      | 0.1210 | 0000       |

| 1510                        | DCH6SSA                         | 15:0          |        |                   |             |       |                    |       |            | CHSSA< | :31:0> |            |        |            |         |        |        |        | 0000       |

| 4500                        | DOLIODOA                        | 31:16         |        |                   |             |       |                    |       |            |        |        |            |        |            |         |        |        |        | 0000       |

| 1520                        | DCH6DSA                         | 15:0          |        |                   |             |       |                    |       |            | CHDSA< | :31:0> |            |        |            |         |        |        |        | 0000       |

| 1520                        | DCH6SSIZ                        | 31:16         | —      | —                 | —           | _     |                    | _     | _          | _      | _      | _          | —      | —          | _       | _      | _      | _      | 0000       |

| 1550                        | DCH033IZ                        | 15:0          |        |                   |             |       |                    |       |            | CHSSIZ | <15:0> |            |        |            |         |        |        |        | 0000       |

| 1540                        | DCH6DSIZ                        | 31:16         | _      | _                 | —           | _     |                    | _     | —          | —      | _      | _          | _      | _          | _       | _      | _      | _      | 0000       |

| 1340                        | DOI IODOIZ                      | 15:0          |        |                   |             |       |                    |       |            | CHDSIZ | <15:0> |            |        |            |         |        |        |        | 0000       |

| 1550                        | DCH6SPTR                        | 31:16         | —      | —                 | —           | —     |                    | —     | —          | —      | —      | —          | —      | —          | —       | —      | —      | —      | 0000       |

|                             | 5 011001 111                    | 15:0          |        |                   |             |       |                    |       |            | CHSPTR | <15:0> |            |        |            |         |        |        |        | 0000       |

| 1560                        | DCH6DPTR                        | 31:16         | —      | —                 | —           | —     |                    | —     | —          | —      | _      | —          | —      | —          | —       | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        |                   | 1           |       |                    |       |            | CHDPTR | <15:0> |            |        |            |         |        |        |        | 0000       |

| 1570                        | DCH6CSIZ                        | 31:16         |        | _                 | —           | _     |                    | _     | _          | —      | -      | _          | _      | _          | _       | —      | _      |        | 0000       |

|                             |                                 | 15:0          |        |                   | г г         |       |                    |       |            | CHCSIZ | <15:0> |            |        |            |         |        |        |        | 0000       |

| 1580                        | DCH6CPTR                        | 31:16         | _      |                   | —           | _     |                    | _     | _          |        | -15:0: | —          | -      | —          | -       | —      | -      | —      | 0000       |

|                             |                                 | 15:0<br>31:16 |        |                   |             |       |                    |       |            | CHCPTR | <15:0> |            |        |            |         |        |        |        | 0000       |

| 1590                        | DCH6DAT                         | 15:0          | _      |                   | _           |       | _                  | _     |            | CHPDAT | -15:0> |            |        |            |         |        |        | _      | 0000       |

|                             |                                 | 31:16         |        |                   |             | CHPIG | N-7:0-             |       |            | OTFDAT | <13.02 |            |        |            |         |        |        |        | 0000       |

| 15A0                        | DCH7CON                         |               | CHBUSY |                   | CHPIGNEN    |       | N<7:0><br>CHPATLEN |       |            | CHCHNS | CHEN   | —<br>CHAED | CHCHN  | —<br>CHAEN |         |        |        |        | 0000       |

| Leger                       |                                 |               |        |                   | unimplement |       |                    |       | hown in ho |        | OHLIN  | UTALD      | GHGHN  | UNALIN     | _       | UNEDET | UNFR   |        | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 04.04        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        |                     |                   |                   | CHPIG             | N<7:0>            |                   |                  |                       |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | _                   | _                 | —                 | —                 | —                 | -                 | —                | —                     |

| 45.0         | R/W-0               | U-0               | R/W-0             | U-0               | R/W-0             | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | _                 | CHIPGNEN          | _                 | CHPATLEN          |                   | —                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

#### REGISTER 10-7: DCHxCON: DMA CHANNEL x CONTROL REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-24 CHPIGN<7:0>: Channel Register Data bits

Pattern Terminate mode:

Any byte matching these bits during a pattern match may be ignored during the pattern match determination when the CHPIGNEN bit is set. If a byte is read that is identical to this data byte, the pattern match logic will treat it as a "don't care" when the pattern matching logic is enabled and the CHPIGEN bit is set.

#### bit 23-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **CHPIGNEN:** Enable Pattern Ignore Byte bit

- 1 = Treat any byte that matches the CHPIGN<7:0> bits as a "don't care" when pattern matching is enabled

0 = Disable this feature

- bit 12 Unimplemented: Read as '0'

- bit 11 CHPATLEN: Pattern Length bit

- 1 = 2 byte length

- 0 = 1 byte length

#### bit 10-9 Unimplemented: Read as '0'

- bit 8 **CHCHNS:** Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

bit 7

- 0 = Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

- bit 5 CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

#### REGISTER 11-11: USBIENCSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 1-7) (CONTINUED)

#### bit 15-8 **RXINTERV<7:0>:** Endpoint RX Polling Interval/NAK Limit bits

For Interrupt and Isochronous transfers, this field defines the polling interval for the endpoint. For Bulk endpoints, this field sets the number of frames/microframes after which the endpoint should time out on receiving a stream of NAK responses.

The following table describes the valid values and meaning for this field:

| Transfer Type | Speed        | Valid Values (m) | Interpretation                                                                                                |

|---------------|--------------|------------------|---------------------------------------------------------------------------------------------------------------|

| Interrupt     | Low/Full     | 0x01 to 0xFF     | Polling interval is 'm' frames.                                                                               |

|               | High         | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames.                                                                |

| Isochronous   | Full or High | 0x01 to 0x10     | Polling interval is 2 <sup>(m-1)</sup> frames/microframes.                                                    |

| Bulk          | Full or High | 0x02 to 0x10     | NAK limit is 2 <sup>(m-1)</sup> frames/microframes. A value of '0' or '1' disables the NAK time-out function. |

bit 7-6 **SPEED<1:0>:** RX Endpoint Operating Speed Control bits

- 11 = Low-Speed

- 10 = Full-Speed

- 01 = Hi-Speed

00 = Reserved

#### bit 5-4 **PROTOCOL<1:0>:** RX Endpoint Protocol Control bits

- 11 = Interrupt

- 10 = Bulk

- 01 = Isochronous

- 00 = Control

#### bit 3-0 **TEP<3:0>:** RX Target Endpoint Number bits

This value is the endpoint number contained in the TX endpoint descriptor returned to the USB module during device enumeration.

#### **REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER ('x' = 2-9) (CONTINUED)**

bit 2 Unimplemented: Read as '0'

- bit 1 TCS: Timer Clock Source Select bit<sup>(1)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, Timer5, Timer7, and Timer9). All timer functions are set through the even numbered timers.

- 2: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

- 3: This bit is available only on even numbered timers (Timer2, Timer4, Timer6, and Timer8).

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | —                 | —                 | -                 | _                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   |                   | —                 |                   |                  | -                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   | _                 |                   | AREIF             | PKTIF             | CBDIF            | PENDIF           |

#### REGISTER 26-6: CEINTSRC: CRYPTO ENGINE INTERRUPT SOURCE REGISTER

#### Legend:

| 5                 |                  |                                             |                    |  |

|-------------------|------------------|---------------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | able bit U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                        | x = Bit is unknown |  |

#### bit 31-4 Unimplemented: Read as '0'

- bit 3 AREIF: Access Response Error Interrupt bit

- 1 = Error occurred trying to access memory outside the Crypto Engine

- 0 = No error has occurred

- bit 2 **PKTIF:** DMA Packet Completion Interrupt Status bit

- 1 = DMA packet was completed

- 0 = DMA packet was not completed

#### bit 1 CBDIF: BD Transmit Status bit

- 1 = Last BD transmit was processed

- 0 = Last BD transmit has not been processed

- bit 0 PENDIF: Crypto Engine Interrupt Pending Status bit

- 1 = Crypto Engine interrupt is pending (this value is the result of an OR of all interrupts in the Crypto Engine)

- 0 = Crypto Engine interrupt is not pending

|              |                   | $\mathbf{x} = 1 \text{ OR } \mathbf{z}$ |                   |                   |                   |                   |                    |                  |

|--------------|-------------------|-----------------------------------------|-------------------|-------------------|-------------------|-------------------|--------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

| 04-04        | R/W-1             | R/W-1                                   | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1              | R/W-1            |

| 31:24        |                   |                                         |                   | POLY<3            | 31:24>            |                   |                    |                  |

| 00.40        | R/W-1             | R/W-1                                   | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1              | R/W-1            |

| 23:16        |                   |                                         |                   | POLY<2            | 3:16>             |                   | 25/17/9/1<br>R/W-1 |                  |

| 45.0         | R/W-0             | R/W-0                                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0              | R/W-0            |

| 15:8         |                   |                                         |                   | POLY<             | 15:8>             |                   |                    |                  |

| 7.0          | R/W-0             | R/W-0                                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0              | R/W-0            |

| 7:0          |                   |                                         |                   | POLY<             | :7:0>             |                   |                    |                  |

# REGISTER 27-3: RNGPOLYX: RANDOM NUMBER GENERATOR POLYNOMIAL REGISTER 'x'

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 POLY<31:0>: PRNG LFSR Polynomial MSb/LSb bits (RNGPOLY1 = LSb, RNGPOLY2 = MSb)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|------------------|

| 04-04        | R/W-1              | R/W-1            |

| 31:24        |                   |                   |                   | RNG<3             | 1:24>             |                   |                    |                  |

| / -          | R/W-1              | R/W-1            |

| 23:16        |                   |                   |                   | RNG<2             | 3:16>             |                   | 25/17/9/1<br>R/W-1 |                  |

| 45.0         | R/W-1              | R/W-1            |

| 15:8         | RNG<15:8>         |                   |                   |                   |                   |                   |                    |                  |

|              | R/W-1              | R/W-1            |

| 7:0          |                   |                   | •                 | RNG<              | 7:0>              |                   | R/W-1<br>R/W-1     | •                |

| <b>REGISTER 27-4:</b> | RNGNUMGENX: RANDOM NUMBER GENERATOR REGISTER 'x' ('x' = 1 OR 2) |

|-----------------------|-----------------------------------------------------------------|

|-----------------------|-----------------------------------------------------------------|

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 RNG<31:0>: Current PRNG MSb/LSb Value bits (RNGNUMGEN1 = LSb, RNGNUMGEN2 = MSb)

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 04.04        | U-0                    |

| 31:24        |                        | —                      | —                      | —                      | —                      | —                      | —                      | —                      |

| 22:46        | U-0                    |

| 23:16        | —                      | —                      | _                      | —                      | _                      | —                      | —                      | —                      |

| 45.0         | U-0                    | U-0                    | U-0                    | R-0, HS, HC            |

| 15:8         | —                      | —                      | _                      | EIRDY44 <sup>(2)</sup> | EIRDY43 <sup>(2)</sup> | EIRDY42 <sup>(2)</sup> | EIRDY41 <sup>(2)</sup> | EIRDY40 <sup>(2)</sup> |

| 7.0          | R-0, HS, HC            |

| 7:0          | EIRDY39 <sup>(2)</sup> | EIRDY38 <sup>(2)</sup> | EIRDY37 <sup>(2)</sup> | EIRDY36 <sup>(2)</sup> | EIRDY35 <sup>(2)</sup> | EIRDY34 <sup>(1)</sup> | EIRDY33 <sup>(1)</sup> | EIRDY32 <sup>(1)</sup> |

#### REGISTER 28-31: ADCEISTAT2: ADC EARLY INTERRUPT STATUS REGISTER 2

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                    |  |  |

|-------------------|-------------------|------------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'       |  |  |

| -n = Value at POR | '1' = Bit is set  | 0' = Bit is cleared $x = Bit is unknown$ |  |  |

#### bit 31-13 Unimplemented: Read as '0'

bit 31-0 **EIRDY44:EIRDY32:** Early Interrupt for Corresponding Analog Input Ready bits

- 1 = This bit is set when the early interrupt event occurs for the specified analog input. An interrupt will be generated if early interrupts are enabled in the ADCEIEN2 register. For the Class 1 analog inputs, this bit will set as per the configuration of the ADCEIS<2:0> bits in the ADCXTIME register. For the shared ADC module, this bit will be set as per the configuration of the ADCEIS<2:0> bits in the ADCEIS<2:0> bits in the ADCCON2 register.

- 0 = Interrupts are disabled

**Note 1:** This bit is not available on 64-pin devices.

2: This bit is not available on 64-pin and 100-pin devices.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1        | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|------------------|--|--|

| 04-04     | R-y                     | R-y              |  |  |

| 31:24     |                   |                   |                   | AN<3              | 1:23>             |                   |                         |                  |  |  |

|           | R-y               | R-y               | R-y               | R-y               | R-y               | R-1               | R-1                     | R-1              |  |  |

| 23:16     |                   |                   |                   | AN<2              | 3:16>             |                   | <b>25/17/9/1</b><br>R-y |                  |  |  |

| 45.0      | R-1                     | R-1              |  |  |

| 15:8      | AN<15:8>          |                   |                   |                   |                   |                   |                         |                  |  |  |

| 7.0       | R-1                     | R-1              |  |  |

| 7:0       |                   |                   |                   | AN<               | 7:0>              |                   |                         |                  |  |  |

#### REGISTER 28-34: ADCSYSCFG1: ADC SYSTEM CONFIGURATION REGISTER 1

| Legend:           |                  | y = POR value is deter | y = POR value is determined by the specific device |  |  |  |

|-------------------|------------------|------------------------|----------------------------------------------------|--|--|--|