Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efm100-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-13: SYSTEM BUS TARGET 5 REGISTER MAP

| sse                         |                  |           |       |       |       |          |          |       |       |      | Bits      |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|-----------|-------|----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7      | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             |                  | 31:16     | MULTI | _     |       | _        |          | CODE  | <3:0> |      | _         |       | _        | _    | _      | _      | _       | _      | 0000          |

| 9420                        | SBT5ELOG1        | 15:0      |       |       |       | INI      | ΓID<7:0> |       |       |      | •         | REGIO | N<3:0>   | •    | —      | C      | MD<2:0> | •      | 0000          |

| 0424                        |                  | 31:16     | _     | —     | _     | —        | _        | _     | _     | _    | _         | _     | _        | —    | _      | _      | —       | _      | 0000          |

| 9424                        | 9424 SBT5ELOG2   | 15:0      | _     | _     | _     | —        | _        | _     | _     | _    | _         | _     | _        | —    | _      | _      | GROU    | P<1:0> | 0000          |

| 0.400                       | SBT5ECON         | 31:16     |       | _     | _     | _        | _        | _     | _     | ERRP | -         | _     | _        | _    | _      | _      | —       | _      | 0000          |

| 9428                        | SBISECON         | 15:0      | _     | —     | _     | _        | —        |       | _     | —    | _         |       | —        | _    | —      | _      | —       | —      | 0000          |

| 9430                        | SBT5ECLRS        | 31:16     | -     | _     |       | —        | _        |       | _     | -    | _         |       | _        | _    | _      | _      | —       | -      | 0000          |

| 9430                        | SBISECLKS        | 15:0      | -     | _     |       | —        | _        |       | _     | -    | _         |       | _        | _    | _      | _      | —       | CLEAR  | 0000          |

| 0/38                        | 9438 SBT5ECLRM   | 31:16     | _     | —     | _     | —        | —        | —     | —     | —    | _         | _     | —        | —    | —      | —      |         | —      | 0000          |

| 9430                        |                  | 15:0      | _     | —     | _     | _        | —        | _     | —     | _    | _         | _     |          | —    | —      | _      | —       | CLEAR  | 0000          |

| 9440                        | SBT5REG0         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6>  |       |          |      |        |        |         |        | xxxx          |

| 3440                        | OBTOREOU         | 15:0      |       | _     | BA    | ASE<5:0> | -        |       | PRI   | —    |           |       | SIZE<4:0 | >    | _      | —      |         | —      | xxxx          |

| 9450                        | SBT5RD0          | 31:16     | —     | —     | _     | _        | _        |       | —     | _    | —         | _     |          | —    | —      | _      | —       | _      | xxxx          |

| 0 100                       | SBISKDU          | 15:0      | —     | —     | —     | —        | —        | —     | —     | —    | —         | —     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9458                        | SBT5WR0          | 31:16     | _     | —     | -     | —        | —        |       | —     | —    | —         |       | —        | —    | —      | _      | —       | —      | xxxx          |

| 0 100                       | obronnic         | 15:0      | _     | —     | —     | —        | —        |       |       | —    | —         | _     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9460                        | SBT5REG1         | 31:16     |       |       |       |          |          |       | 1     | BA   | SE<21:6>  |       |          |      |        |        |         |        | xxxx          |

|                             |                  | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | —    |           |       | SIZE<4:0 | >    |        | —      |         | —      | xxxx          |

| 9470                        | SBT5RD1          | 31:16     | —     | _     |       | _        |          | _     | _     |      | _         | _     |          | _    | -      | _      |         | _      | XXXX          |

|                             |                  | 15:0      | —     | —     |       | —        |          |       | _     |      | _         |       |          | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | XXXX          |

| 9478                        | SBT5WR1          | 31:16     | —     | —     |       | —        |          |       | _     |      | _         |       |          | _    | _      | _      |         |        | XXXX          |

|                             |                  | 15:0      | —     | —     | —     | _        | —        |       |       | —    | _         | _     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9480                        | SBT5REG2         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6>  |       |          |      |        |        |         |        | XXXX          |

|                             |                  | 15:0      |       |       | BA    | ASE<5:0> |          |       | PRI   | —    | SIZE<4:0> |       |          |      |        | —      |         | —      | XXXX          |

| 9490                        | SBT5RD2          | 31:16     | _     | _     | —     | —        | —        | —     | —     | —    | _         | —     | —        | —    | —      | —      | —       | —      | XXXX          |

|                             |                  | 15:0      | _     | _     | —     | —        | —        | —     | —     | —    | _         | —     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9498                        | SBT5WR2          | 31:16     |       | _     | —     | —        | —        | _     |       | —    | _         | _     | —        | _    | —      | —      | —       | —      | XXXX          |

|                             |                  | 15:0      | —     | —     | —     | —        | —        | —     | —     | —    | —         | —     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

DS60001320D-page 82

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

|              |                   | ('x' = 0-13)      |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

| 04.04        | R/W-0, C          | U-0               | U-0               | U-0               | R/W-0, C          | R/W-0, C          | R/W-0, C         | R/W-0, C         |  |  |  |  |  |  |

| 31:24        | MULTI             | —                 | —                 | —                 |                   | CODE<3:0>         |                  |                  |  |  |  |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        |                   |                   | —                 | —                 |                   | —                 |                  | _                |  |  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 15:8         | INITID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 7:0          |                   | REGIO             | N<3:0>            |                   |                   | – CMD<2:0>        |                  |                  |  |  |  |  |  |  |

# REGISTER 4-3: SBTxELOG1: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 1

| Legend:           | C = Clearable bit |                                    |

|-------------------|-------------------|------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               |

bit 31 MULTI: Multiple Permission Violations Status bit

This bit is cleared by writing a '1'.

1 = Multiple errors have been detected

0 = No multiple errors have been detected

bit 30-28 Unimplemented: Read as '0'

bit 27-24 CODE<3:0>: Error Code bits

Indicates the type of error that was detected. These bits are cleared by writing a '1'.

- 1111 = Reserved

- 1101 = Reserved

- •

- •

- 0011 = Permission violation

- 0010 = Reserved

- 0001 = Reserved

- 0000 = No error

- bit 23-16 Unimplemented: Read as '0'

- bit 15-8 INITID<7:0>: Initiator ID of Requester bits

- 11111111 = Reserved

- 00001111 = Reserved 00001110 = Crypto Engine 00001101 = Flash Controller 00001100 = SQI1 00001011 = CAN2 00001010 = CAN1 00001001 = Ethernet Write 00001000 = Ethernet Read 00000111 = USB 00000110 = DMA Write (DMAPRI (CFGCON<25>) = 1) 00000101 = DMA Write (DMAPRI (CFGCON<25>) = 0) 00000100 = DMA Read (DMAPRI (CFGCON<25>) = 1) 00000011 = DMA Read (DMAPRI (CFGCON<25>) = 0) 00000010 = CPU (CPUPRI (CFGCON<24>) = 1) 00000001 = CPU (CPUPRI (CFGCON<25>) = 0) 00000000 = Reserved

#### Note: Refer to Table 4-6 for the list of available targets and their descriptions.

#### REGISTER 11-11: USBIENCSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 1-7)

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |        | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|----------------------------------|--------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R-x                              | R-x    | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |  |  |  |  |

| 31:24        |                                  | RXFIFC | )SZ<3:0>          |                   | TXFIFOSZ<3:0>     |                   |                  |                  |  |  |  |  |  |

| 23:16        | U-0                              | U-0    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10        | —                                | —      | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |  |

| 15:8         | R/W-0                            | R/W-0  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 10.0         | RXINTERV<7:0>                    |        |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0                            | R/W-0  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | SPEEI                            | D<1:0> | PROTO             | COL<1:0>          | TEP<3:0>          |                   |                  |                  |  |  |  |  |  |

# Leaend:

| Logena.           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

## bit 31-28 RXFIFOSZ<3:0>: Receive FIFO Size bits

|           | 1111 = Reserved<br>1110 = Reserved<br>1101 = 8192 bytes                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|

|           | 1101 = 4096 bytes                                                                                                                  |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | 0011 = 8 bytes<br>0010 = Reserved<br>0001 = Reserved<br>0000 = Reserved or endpoint has not been configured                        |

|           | This register only has this interpretation when dynamic sizing is not selected. It is not valid where dynamic FIFO sizing is used. |

| bit 27-24 | TXFIFOSZ<3:0>: Transmit FIFO Size bits<br>1111 = Reserved<br>1110 = Reserved<br>1101 = 8192 bytes<br>1100 = 4096 bytes             |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | 0011 = 8 bytes<br>0010 = Reserved<br>0001 = Reserved<br>0000 = Reserved or endpoint has not been configured                        |

|           |                                                                                                                                    |

This register only has this interpretation when dynamic sizing is not selected. It is not valid where dynamic

FIFO sizing is used.

# bit 23-16 Unimplemented: Read as '0'

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 22:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 7.0       | R-0, HC, HS       | R-0, HC, HS       | R-0, HC, HS       | U-0               | U-0               | U-0               | U-0              | R-0, HC, HS      |

| 7:0       | BAD1              | BAD2              | DMTEVENT          | _                 |                   | _                 | _                | WINOPN           |

## REGISTER 15-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:           | HC = Hardware Cleared | HS = Hardware Set                |            |

|-------------------|-----------------------|----------------------------------|------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as   | '0'        |

| -n = Value at POR | '1' = Bit is set      | 0' = Bit is cleared $x = Bit is$ | is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP1<7:0> value was not detected                                                                                     |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer even was not detected                                                                                             |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

NOTES:

#### **SQI Control Registers** 20.1

# TABLE 20-1: SERIAL QUADRATURE INTERFACE (SQI) REGISTER MAP

| ess                         |                    |                           |       |       |       |         |          |               |              | В            | its            |               |               |              |                |               |               |               | s          |  |

|-----------------------------|--------------------|---------------------------|-------|-------|-------|---------|----------|---------------|--------------|--------------|----------------|---------------|---------------|--------------|----------------|---------------|---------------|---------------|------------|--|

| Virtual Address<br>(BF8E_#) | Register<br>Name   | Bit Range                 | 31/15 | 30/14 | 29/13 | 28/12   | 27/11    | 26/10         | 25/9         | 24/8         | 23/7           | 22/6          | 21/5          | 20/4         | 19/3           | 18/2          | 17/1          | 16/0          | All Resets |  |

| 2000                        | SQI1               | 31:16                     | _     | —     |       | —       | _        | —             | —            | —            | DUN            | IMYBYTES<     | :2:0>         | AD           | DRBYTES<2      | 2:0>          | READOPC       | CODE<7:6>     | 0000       |  |

| 2000                        | XCON1              | 15:0                      |       |       |       |         |          |               |              | MD<1:0>      | 0000           |               |               |              |                |               |               |               |            |  |

| 2004                        | SQI1               | 31:16                     | —     | —     | _     | —       | _        | —             | —            | —            | —              | —             | _             | —            | —              | —             | _             | —             | 0000       |  |

|                             | XCON2              | 15:0                      | _     | _     | _     | _       | DEVSE    | L<1:0>        | MODEBY       | TES<1:0>     |                |               |               | MODECO       | DDE<7:0>       |               |               |               | 0000       |  |

| 2008                        | SQI1CFG            | 31:16                     | -     | _     | _     | -       | —        | _             | CSEN         | l<1:0>       | SQIEN          | —             | DATAE         | N<1:0>       | CON<br>FIFORST | RXFIFO<br>RST | TXFIFO<br>RST | RESET         | 0000       |  |

|                             |                    | 15:0                      | _     | —     | —     | BURSTEN | _        | HOLD          | WP           | —            | —              | —             | LSBF          | CPOL         | CPHA           |               | MODE<2:0>     | •             | 0000       |  |

| 200C                        | SQI1CON            | 31:16                     | —     | —     | —     | -       | —        | —             | —            | SCHECK       | —              | DASSERT       | DEVSE         | L<1:0>       | LANEMC         | DE<1:0>       | CMDIN         | IT<1:0>       | 0000       |  |

|                             |                    | 15:0                      |       |       |       |         |          |               |              | TXRXCOL      | JNT<15:0>      |               |               |              |                |               |               |               | 0000       |  |

| 2010                        | SQI1               | 31:16                     | —     | —     | —     | -       | —        | —             | —            | —            | _              | _             | _             | _            | _              |               | LKDIV<10:8    |               | 0000       |  |

|                             | CLKCON             | 15:0                      |       |       |       | CLKDI   | V<7:0>   |               |              |              | —              | —             | —             | _            | _              | —             | STABLE        | EN            | 0000       |  |

| 2014                        | SQI1               | 31:16                     | —     | _     |       | -       | —        | —             | —            | —            | _              | _             | —             | —            | —              | —             | —             | —             | 0000       |  |

|                             | 2014 CMDTHR 15:0 — |                           | _     | _     |       | TX      | CMDTHR<4 | :0>           | >            |              |                | _             | RXCMDTHR<4:0> |              |                | 4:0>          |               | 0000          |            |  |

| 2018                        | SQI1               | 31:16                     | —     | _     | _     | -       |          | —             | _            | —            | —              | _             | _             | —            | —              | —             | -             | —             | 0000       |  |

|                             | INTTHR             | 15:0                      | —     | -     | -     |         |          | (INTTHR<4:    |              |              | _              | _             | _             |              |                | (INTTHR<4:    |               |               |            |  |

| 201C                        | SQI1               | 31:16                     | _     | _     | _     | _       | _        | -             | -            | -            | -              | -             | —             | -            | -              | -             | —<br>—        | —<br>—        | 0000       |  |

| 2010                        | INTEN              | 15:0                      | _     | _     | _     | _       | DMAEIE   | PKT<br>COMPIE | BD<br>DONEIE | CON<br>THRIE | CON<br>EMPTYIE | CON<br>FULLIE | RX<br>THRIE   | RX<br>FULLIE | RX<br>EMPTYIE  | TX<br>THRIE   | TX<br>FULLIE  | TX<br>EMPTYIE | 0000       |  |

| 0000                        | SQI1               | 31:16                     | —     | —     | —     | _       | —        | —             | —            | —            | —              | —             | —             | —            | —              | —             | —             | —             | 0000       |  |

| 2020                        | INTSTAT            | 15:0                      | —     | _     | —     | -       | DMAEIF   | PKT<br>COMPIF | BD<br>DONEIF | CON<br>THRIF | CON<br>EMPTYIF | CON<br>FULLIF | RX<br>THRIF   | RX<br>FULLIF | RX<br>EMPTYIF  | TX<br>THRIF   | TX<br>FULLIF  | TX<br>EMPTYIF | 0000       |  |

| 2024                        | SQI1               | 31:16                     |       |       |       |         |          |               |              | TXDATA       |                |               |               |              |                |               |               |               | 0000       |  |

|                             | TXDATA             | 15:0                      |       |       |       |         |          |               |              | TXDAT        |                |               |               |              |                |               |               |               | 0000       |  |

| 2028                        | SQI1               | 31:16                     |       |       |       |         |          |               |              | RXDATA       |                |               |               |              |                |               |               |               | 0000       |  |

|                             | RXDATA             | 15:0                      |       |       | i     |         |          | i             |              | RXDAT        | A<15:0>        |               |               |              |                |               |               |               | 0000       |  |

| 202C                        | SQI1<br>STAT1      | 31:16                     | _     | _     | _     |         | _        | _             | _            | _            |                |               |               |              | REE<7:0>       |               |               |               | 0000       |  |

|                             | -                  | 15:0                      | _     | _     | _     |         | _        | _             | _            | _            |                |               |               |              | CNT<7:0>       |               | 0,4507        |               | 0000       |  |

| 2030                        | SQI1<br>STAT2      | 31:16                     | _     | —     |       | _       | —        | -             |              |              | —              |               |               |              |                | _             |               | AT<1:0>       | 0000       |  |

|                             | -                  | 15:0                      | —     | _     |       | _       |          |               | ONAVAIL<4:   |              |                | SDID3         | SDID2         | SDID1        | SDID0          |               | RXUN          | TXOV          | 00x0       |  |

| 2034                        | SQI1<br>BDCON      | 31:16<br>15:0             |       |       | _     | _       | _        |               |              | _            | _              |               | _             |              |                | —<br>START    | POLLEN        | —<br>DMAEN    | 0000       |  |

|                             |                    | 31:16                     | _     | _     | _     | _       | _        | _             | _            |              | DP-31-16-      | _             | _             | —            | _              | SIARI         | POLLEN        | DIVIAEN       | 0000       |  |

| 2038                        | SQI1BD<br>CURADD   | 15:0                      |       |       |       |         |          |               |              |              |                |               |               |              |                |               |               |               |            |  |

|                             |                    | 31:16                     |       |       |       |         |          |               |              |              | R<31:16>       |               |               |              |                |               |               |               | 0000       |  |

| 2040                        | SQI1BD<br>BASEADD  | 15:0                      |       |       |       |         |          |               |              |              |                |               |               |              |                |               |               |               | 0000       |  |

|                             |                    | BASEADD 15:0 BDADDR<15:0> |       |       |       |         |          |               |              |              |                | 0000          |               |              |                |               |               |               |            |  |

## REGISTER 20-3: SQI1CFG: SQI CONFIGURATION REGISTER (CONTINUED)

| bit 12  | BURSTEN: Burst Configuration bit <sup>(1)</sup>                                                                                                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Burst is enabled                                                                                                                                                                                                              |

|         | 0 = Burst is not enabled                                                                                                                                                                                                          |

| bit 11  | Reserved: Must be programmed as '0'                                                                                                                                                                                               |

| bit 10  | HOLD: Hold bit                                                                                                                                                                                                                    |

|         | In Single Lane or Dual Lane mode, this bit is used to drive the SQID3 pin, which can be used for devices with a HOLD input pin. The meaning of the values for this bit will depend on the device to which SQID3 is connected.     |

| bit 9   | WP: Write Protect bit                                                                                                                                                                                                             |

|         | In Single Lane or Dual Lane mode, this bit is used to drive the SQID2 pin, which can be used with devices with a write-protect pin. The meaning of the values for this bit will depend on the device to which SQID2 is connected. |

| bit 8-6 | Unimplemented: Read as '0'                                                                                                                                                                                                        |

| bit 5   | LSBF: Data Format Select bit                                                                                                                                                                                                      |

|         | <ul> <li>1 = LSB is sent or received first</li> <li>0 = MSB is sent or received first</li> </ul>                                                                                                                                  |

| bit 4   | CPOL: Clock Polarity Select bit                                                                                                                                                                                                   |

|         | <ul><li>1 = Active-low SQICLK (SQICLK high is the Idle state)</li><li>0 = Active-high SQICLK (SQICLK low is the Idle state)</li></ul>                                                                                             |

| bit 3   | CPHA: Clock Phase Select bit                                                                                                                                                                                                      |

|         | <ul> <li>1 = SQICLK starts toggling at the start of the first data bit</li> <li>0 = SQICLK starts toggling at the middle of the first data bit</li> </ul>                                                                         |

| bit 2-0 | MODE<2:0>: Mode Select bits                                                                                                                                                                                                       |

|         | 111 = Reserved                                                                                                                                                                                                                    |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 100 = Reserved                                                                                                                                                                                                                    |

|         | 011 = XIP mode is selected (when this mode is entered, the module behaves as if executing in place (XIP),<br>but uses the register data to control timing)                                                                        |

|         | 010 = DMA mode is selected                                                                                                                                                                                                        |

- 010 = DMA mode is selected

- 001 = CPU mode is selected (the module is controlled by the CPU in PIO mode. This mode is entered when leaving Boot or XIP mode)

- 000 = Reserved

- Note 1: This bit must be programmed as '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | _                 | _                 | -                 | -                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | _                 | _                 | —                 | -                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 | _                 | _                 | START             | POLLEN           | DMAEN            |

#### REGISTER 20-14: SQI1BDCON: SQI BUFFER DESCRIPTOR CONTROL REGISTER

#### Legend:

bit 0

| R = Readable bit  | = Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|---------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-3 Unimplemented: Read as '0'

- bit 2 START: Buffer Descriptor Processor Start bit

- 1 = Start the buffer descriptor processor

- 0 = Disable the buffer descriptor processor

- bit 1 **POLLEN:** Buffer Descriptor Poll Enable bit

- 1 = BDP poll is enabled

- 0 = BDP poll is not enabled

- DMAEN: DMA Enable bit

- 1 = DMA is enabled

- 0 = DMA is disabled

#### REGISTER 20-15: SQI1BDCURADD: SQI BUFFER DESCRIPTOR CURRENT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        |                   |                   |                   | BDCURRAD          | DR<31:24>         |                   |                  |                  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | BDCURRADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | BDCURRADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BDCURRAD          | DDR<7:0>          |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 BDCURRADDR<31:0>: Current Buffer Descriptor Address bits

These bits contain the address of the current descriptor being processed by the Buffer Descriptor Processor.

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------------|----------------------|--------------------|-------------------|---------------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0                      | U-0                  | U-0                | U-0               | U-0                       | U-0               | U-0              | U-0              |  |

| 31.24        | —                        |                      | —                  | -                 | —                         |                   | —                |                  |  |

| 00.40        | U-0                      | U-0                  | U-0                | U-0               | U-0                       | U-0               | U-0              | U-0              |  |

| 23:16        | —                        | —                    | —                  | —                 | —                         | —                 | —                | _                |  |

| 45.0         | R/W-0                    | R/W-0                | R/W-0              | R-0               | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC          | AMASK<3:0> <sup>(2)</sup> |                   |                  |                  |  |

| 7.0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0             | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | ARPT<7:0> <sup>(2)</sup> |                      |                    |                   |                           |                   |                  |                  |  |

#### REGISTER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER

#### Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

# bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is more than 32 real-time clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved

- 1011 = Reserved

- 11xx = Reserved

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

#### **Note:** This register is reset only on a Power-on Reset (POR).

© 2015-2016 Microchip Technology Inc.

# PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

| REGIST  | ER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER (CONTINUED)                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-0 | ARPT<7:0>: Alarm Repeat Counter Value bits <sup>(2)</sup>                                                                                        |

|         | 11111111 = Alarm will trigger 256 times                                                                                                          |

|         | •                                                                                                                                                |

|         |                                                                                                                                                  |

|         | 00000000 = Alarm will trigger one time<br>The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1. |

| Note 1: | Hardware clears the ALRMEN bit anytime the alarm event occurs, when $ARPT < 7:0 > = 0.0$ and $CHIME = 0.$                                        |

| 2:      | This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.                                                       |

|         |                                                                                                                                                  |

Note: This register is reset only on a Power-on Reset (POR).

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6    | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |

|-----------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| 04.04     | R/W-0                |

| 31:24     | CSS31 <sup>(1)</sup> | CSS30 <sup>(1)</sup> | CSS29 <sup>(1)</sup> | CSS28 <sup>(1)</sup> | CSS27 <sup>(1)</sup> | CSS26 <sup>(1)</sup> | CSS25 <sup>(1)</sup> | CSS24 <sup>(1)</sup> |

| 00.40     | R/W-0                |

| 23:16     | CSS23 <sup>(1)</sup> | CSS22 <sup>(1)</sup> | CSS21 <sup>(1)</sup> | CSS20 <sup>(1)</sup> | CSS19 <sup>(1)</sup> | CSS18                | CSS17                | CSS16                |

| 45.0      | R/W-0                |

| 15:8      | CSS15                | CSS14                | CSS13                | CSS12                | CSS11                | CSS10                | CSS9                 | CSS8                 |

| 7:0       | R/W-0                |

|           | CSS7                 | CSS6                 | CSS5                 | CSS4                 | CSS3                 | CSS2                 | CSS1                 | CSS0                 |

#### REGISTER 28-10: ADCCSS1: ADC COMMON SCAN SELECT REGISTER 1

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CSS31:CSS0: Analog Common Scan Select bits<sup>(2,3)</sup>

1 =Select ANx for input scan

0 =Skip ANx for input scan

**Note 1:** This bit is not available on 64-pin devices.

2: In addition to setting the appropriate bits in this register, Class 1 and Class 2 analog inputs must select the STRIG input as the trigger source if they are to be scanned through the CSS*x* bits. Refer to the bit descriptions in the ADCTRGx registers for selecting the STRIG option.

3: If a Class 1 or Class 2 input is included in the scan by setting the CSSx bit to '1' and by setting the TRGSRCx<4:0> bits to STRIG mode (`0b11), the user application must ensure that no other triggers are generated for that input using the RQCNVRT bit in the ADCCON3 register or the hardware input or any digital filter. Otherwise, the scan behavior is unpredictable.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | _                 |                   | —                 |                   | TRGSRC3<4:0>      |                   |                  |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | _                 | _                 | —                 | TRGSRC2<4:0>      |                   |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | —                 | —                 | —                 |                   | Т                 | RGSRC1<4:0        | )>               |                  |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                 | _                 | _                 |                   | Т                 | RGSRC0<4:0        | )>               |                  |  |

## REGISTER 28-17: ADCTRG1: ADC TRIGGER SOURCE 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

- bit 28-24 TRGSRC3<4:0>: Trigger Source for Conversion of Analog Input AN3 Select bits

- 11111 = Reserved . . 01101 = Reserved 01100 = Comparator 2 (COUT) 01011 = Comparator 1 (COUT) 01010 = OCMP5 01001 = OCMP3 01000 = OCMP1 00111 = TMR5 match 00100 = TMR3 match 00101 = TMR1 match 00100 = INT0 External interrupt 00011 = STRIG 00010 = Global level software trigger (GLSWTRG) 00001 = Global software edge Trigger (GSWTRG) 00000 = No Trigger

For STRIG, in addition to setting the trigger, it also requires programming of the STRGSRC<4:0> bits (ADCCON1<20:16>) to select the trigger source, and requires the appropriate CSS bits to be set in the ADCCSSx registers.

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TRGSRC2<4:0>:** Trigger Source for Conversion of Analog Input AN2 Select bits See bits 28-24 for bit value definitions.

- bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **TRGSRC1<4:0>:** Trigger Source for Conversion of Analog Input AN1 Select bits See bits 28-24 for bit value definitions.

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **TRGSRC0<4:0>:** Trigger Source for Conversion of Analog Input AN0 Select bits See bits 28-24 for bit value definitions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | —                 | —                 | _                 | _                 | —                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | —                 | —                 | _                 | _                 | —                | —                |  |

| 15:8         | U-0               | U-0               | R/W-1             | R/W-1             | R/W-0             | R/W-1             | R/W-1            | R/W-1            |  |

| 10.0         | —                 | —                 |                   |                   | CWINDO            | W<5:0>            |                  |                  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 7.0          | _                 | _                 | _                 | _                 |                   | RETX<             | <3:0>            |                  |  |

# REGISTER 30-27: EMAC1CLRT: ETHERNET CONTROLLER MAC COLLISION WINDOW/RETRY LIMIT REGISTER

#### Legend:

| Logona.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

bit 13-8 **CWINDOW<5:0>:** Collision Window bits

This is a programmable field representing the slot time or collision window during which collisions occur in properly configured networks. Since the collision window starts at the beginning of transmission, the preamble and SFD is included. Its default of 0x37 (55d) corresponds to the count of frame bytes at the end of the window.

bit 7-4 Unimplemented: Read as '0'

#### bit 3-0 RETX<3:0>: Retransmission Maximum bits

This is a programmable field specifying the number of retransmission attempts following a collision before aborting the packet due to excessive collisions. The Standard specifies the maximum number of attempts (attemptLimit) to be 0xF (15d). Its default is '0xF'.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|

| 31:24        | U-0                      | U-0                     |

| 31.24        | —                 | —                 | —                 | —                 | _                 |                   | —                        | —                       |

| 23:16        | U-0                      | U-0                     |

| 23.10        | —                 | —                 | —                 | —                 | _                 |                   | —                        | _                       |

| 15:8         | U-0                      | U-0                     |

| 15.0         | —                 | —                 | —                 | —                 | _                 |                   | —                        | _                       |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   |

| 7.0          |                   |                   | _                 | _                 | _                 | TESTBP            | TESTPAUSE <sup>(1)</sup> | SHRTQNTA <sup>(1)</sup> |

## REGISTER 30-30: EMAC1TEST: ETHERNET CONTROLLER MAC TEST REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-3 Unimplemented: Read as '0'

- bit 2 TESTBP: Test Backpressure bit

- 1 = The MAC will assert backpressure on the link. Backpressure causes preamble to be transmitted, raising carrier sense. A transmit packet from the system will be sent during backpressure.

0 = Normal operation

#### bit 1 **TESTPAUSE:** Test PAUSE bit<sup>(1)</sup>

1 = The MAC Control sub-layer will inhibit transmissions, just as if a PAUSE Receive Control frame with a non-zero pause time parameter was received

0 = Normal operation

### bit 0 SHRTQNTA: Shortcut PAUSE Quanta bit<sup>(1)</sup>

1 = The MAC reduces the effective PAUSE Quanta from 64 byte-times to 1 byte-time

0 = Normal operation

**Note 1:** This bit is only used for testing purposes.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

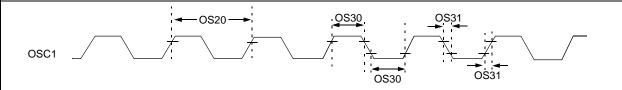

# FIGURE 37-2: EXTERNAL CLOCK TIMING

#### TABLE 37-17: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                  |              |                        |         |       |                                           |

|--------------------|---------------|--------------------------------------------------------------------------------------------------------|--------------|------------------------|---------|-------|-------------------------------------------|

| Param.<br>No.      | Symbol        | Characteristics                                                                                        | Minimum      | Typical <sup>(1)</sup> | Maximum | Units | Conditions                                |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                     | DC           |                        | 64      | MHz   | EC <b>(Note 2,3)</b>                      |

| OS13               |               | Oscillator Crystal Frequency                                                                           | 4            | —                      | 32      | MHz   | HS (Note 2,3)                             |

| OS15               |               |                                                                                                        | 32           | 32.768                 | 100     | kHz   | Sosc (Note 2)                             |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                                          | _            |                        | —       | _     | See parameter<br>OS10 for Fosc<br>value   |

| OS30               | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                           | 0.375 x Tosc | —                      | _       | ns    | EC (Note 2)                               |

| OS31               | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                          | —            | —                      | 7.5     | ns    | EC (Note 2)                               |

| OS40               | Тоѕт          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>and Sosc Clock Oscillator<br>modes) | _            | 1024                   | _       | Tosc  | (Note 2)                                  |

| OS41               | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                             | —            | 2                      | _       | ms    | (Note 2)                                  |

| OS42               | Gм            | External Oscillator<br>Transconductance                                                                | —            | 400                    | _       | µA/V  | VDD = 3.3V,<br>TA = +25°C, HS<br>(Note 2) |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are characterized but are not tested.

**2:** This parameter is characterized, but not tested in manufacturing.

3: See parameter OS50 for PLL input frequency limitations.

| DC CHARACTERISTICS                                             |                        |                        | (unless ot | <b>Operating Conditions: 2.1V to 3.6V</b><br>herwise stated)<br>temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |  |

|----------------------------------------------------------------|------------------------|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Maximum <sup>(4)</sup> | Units      | Conditions                                                                                                                       |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |                        |            |                                                                                                                                  |  |

| EDC30a                                                         | 7                      | 52                     | mA         | 4 MHz (Note 3)                                                                                                                   |  |

| EDC31a                                                         | 8                      | 56                     | mA         | 10 MHz                                                                                                                           |  |

| EDC32a                                                         | 13                     | 66                     | mA         | 60 MHz <b>(Note 3)</b>                                                                                                           |  |

| EDC33a                                                         | 21                     | 86                     | mA         | 130 MHz <b>(Note 3)</b>                                                                                                          |  |

| EDC34                                                          | 26                     | 96                     | mA         | 180 MHz <b>(Note 3)</b>                                                                                                          |  |

#### TABLE 38-3: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE current measurements are as follows:

• Oscillator mode is EC+PLL with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBPMD = 1), VUSB3V3 is connected to VSS, PBCLKx divisor = 1:128 ('x' ≠ 7)

- CPU is in Idle mode (CPU core Halted)

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared (except USBPMD)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: Data in the "Maximum" column is at 3.3V, +125°C at specified operating frequency. Parameters are for design guidance only and are not tested.

## 38.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MZ EF device AC characteristics and timing parameters.

| TABLE 38-5: | SYSTEM TIMING REQUIREMENTS |

|-------------|----------------------------|

|-------------|----------------------------|

| AC CHARACTERISTICS |        |                           | Standard Operating Conditions: 2.1V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |      |       |                                                  |

|--------------------|--------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics           | Min.                                                                                                                                           | Тур. | Max. | Units | Conditions                                       |

| EOS51              | Fsys   | System Frequency          | DC                                                                                                                                             |      | 180  | MHz   | USB module disabled                              |

|                    |        |                           | 30                                                                                                                                             | _    | 180  | MHz   | USB module enabled                               |

| EOS55a             | Fpb    | Peripheral Bus Frequency  | DC                                                                                                                                             | _    | 90   | MHz   | For PBCLKx, 'x' $\neq$ 4, 7                      |

| EOS55b             |        |                           | DC                                                                                                                                             |      | 180  | MHz   | For PBCLK4, PBCLK7                               |

| EOS56              | Fref   | Reference Clock Frequency | _                                                                                                                                              | _    | 45   | MHz   | For REFCLKI1, 3, 4<br>and REFCLKO1, 3, 4<br>pins |

### TABLE 38-6: PLL CLOCK TIMING SPECIFICATIONS

| Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended    | d         |

|-------------------------------------------------------------------------------|-----------|

| Param.<br>No.SymbolCharacteristics <sup>(1)</sup> Min.TypicalMax.UnitsControl | onditions |

| EOS54a FPLL PLL Output Frequency Range 10 — 180 MHz                           | —         |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{PBCLK2}{\sqrt{CommunicationClock}}}}$$

For example, if PBCLK2 = 100 MHz and SPI bit rate = 50 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{100}{50}}} = \frac{D_{CLK}}{1.41}$$

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                                 | PIC32MZ EF Feature                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fail-Safe Clock                                                                                                                                                                            | Monitor (FSCM)                                                                                                                                                                                                                                                                                                                                                      |

| On PIC32MX devices, the internal FRC became the clock source on a failure of the clock source.                                                                                             | On PIC32MZ EF devices, a separate internal Backup FRC (BFRC) becomes the clock source upon a failure at the clock source.                                                                                                                                                                                                                                           |

| On PIC32MX devices, a clock failure resulted in the triggering of a specific interrupt when the switchover was complete.                                                                   | On PIC32MZ EF devices, a NMI is triggered instead, and must be handled by the NMI routine.                                                                                                                                                                                                                                                                          |

| FSCM generates an interrupt.                                                                                                                                                               | FSCM generates a NMI.                                                                                                                                                                                                                                                                                                                                               |