#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

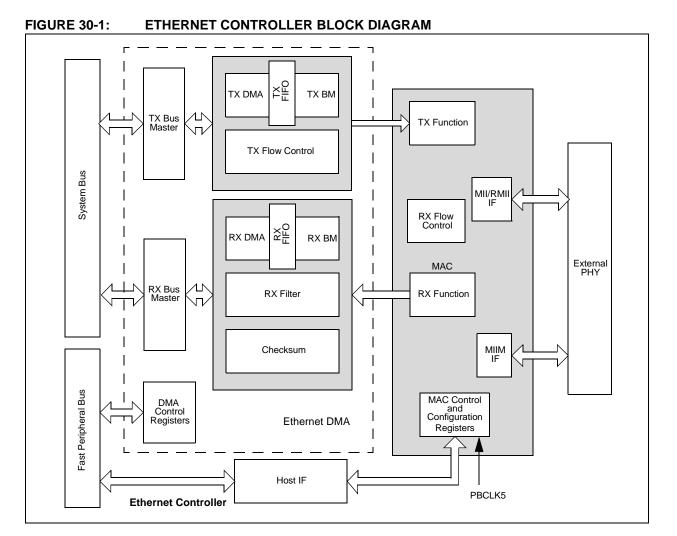

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 97                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

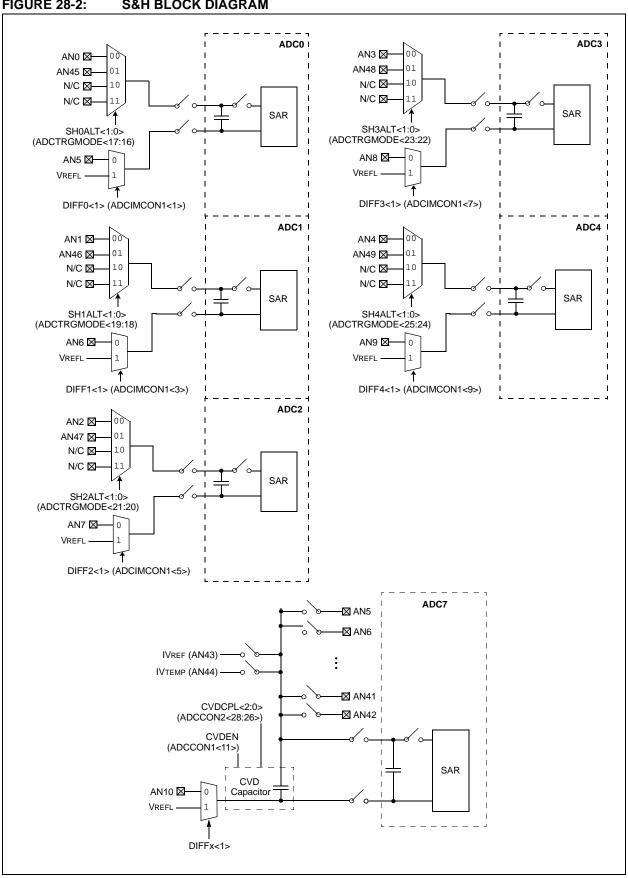

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

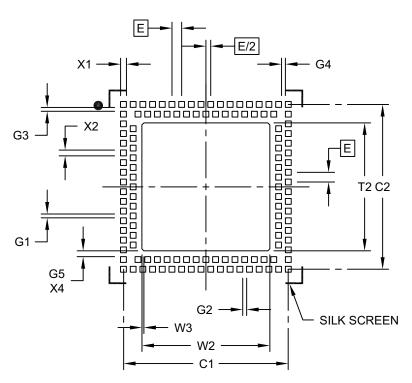

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                 |

| Supplier Device Package    | 124-VTLA (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efm124-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                                                                                           |  |  |  |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                                                               |  |  |  |  |

| PMA0     | 30                     | 44              | B24             | 30                       | I/O         | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |  |  |  |  |

| PMA1     | 29                     | 43              | A28             | 51                       | I/O         | TTL/ST         | Parallel Master Port Address bit 1 Input (Buffered Slave modes) and Output (Master modes) |  |  |  |  |

| PMA2     | 10                     | 16              | B9              | 21                       | 0           | _              | Parallel Master Port Address (Demultiplexed Master                                        |  |  |  |  |

| PMA3     | 6                      | 12              | B7              | 52                       | 0           | _              | modes)                                                                                    |  |  |  |  |

| PMA4     | 5                      | 11              | A8              | 68                       | 0           | _              |                                                                                           |  |  |  |  |

| PMA5     | 4                      | 2               | B1              | 2                        | 0           | _              | 1                                                                                         |  |  |  |  |

| PMA6     | 16                     | 6               | B3              | 6                        | 0           | —              |                                                                                           |  |  |  |  |

| PMA7     | 22                     | 33              | A23             | 48                       | 0           | _              | 1                                                                                         |  |  |  |  |

| PMA8     | 42                     | 65              | A44             | 91                       | 0           | _              |                                                                                           |  |  |  |  |

| PMA9     | 41                     | 64              | B36             | 90                       | 0           | _              |                                                                                           |  |  |  |  |

| PMA10    | 21                     | 32              | B18             | 47                       | 0           | _              | 1                                                                                         |  |  |  |  |

| PMA11    | 27                     | 41              | A27             | 29                       | 0           | _              | 1                                                                                         |  |  |  |  |

| PMA12    | 24                     | 7               | A6              | 11                       | 0           | _              |                                                                                           |  |  |  |  |

| PMA13    | 23                     | 34              | B19             | 28                       | 0           | _              |                                                                                           |  |  |  |  |

| PMA14    | 45                     | 61              | A42             | 87                       | 0           | _              |                                                                                           |  |  |  |  |

| PMA15    | 43                     | 68              | B38             | 97                       | 0           |                |                                                                                           |  |  |  |  |

| PMCS1    | 45                     | 61              | A42             | 87                       | 0           | _              | Parallel Master Port Chip Select 1 Strobe                                                 |  |  |  |  |

| PMCS2    | 43                     | 68              | B38             | 97                       | 0           | _              | Parallel Master Port Chip Select 2 Strobe                                                 |  |  |  |  |

| PMD0     | 58                     | 91              | B52             | 135                      | I/O         | TTL/ST         | Parallel Master Port Data (Demultiplexed Master                                           |  |  |  |  |

| PMD1     | 61                     | 94              | A64             | 138                      | I/O         | TTL/ST         | mode) or Address/Data (Multiplexed Master modes)                                          |  |  |  |  |

| PMD2     | 62                     | 98              | A66             | 142                      | I/O         | TTL/ST         | 4                                                                                         |  |  |  |  |

| PMD3     | 63                     | 99              | B56             | 143                      | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |

| PMD4     | 64                     | 100             | A67             | 144                      | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |

| PMD5     | 1                      | 3               | A3              | 3                        | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |

| PMD6     | 2                      | 4               | B2              | 4                        | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |

| PMD7     | 3                      | 5               | A4              | 5                        | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |

| PMD8     |                        | 88              | B50             | 128                      | I/O         | TTL/ST         | -                                                                                         |  |  |  |  |

| PMD9     |                        | 87              | A60             | 120                      | I/O         | TTL/ST         | 4                                                                                         |  |  |  |  |

| PMD10    |                        | 86              | B49             | 127                      | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |

| PMD11    |                        | 85              | A59             | 123                      | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |

| PMD12    |                        | 79              | B43             | 112                      | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |

| PMD13    |                        | 80              | A54             | 112                      | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |

| PMD13    |                        | 77              | B42             | 110                      | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |

| PMD15    |                        | 78              | A53             | 110                      | 1/O         | TTL/ST         | 4                                                                                         |  |  |  |  |

| PMALL    | 30                     | 44              | B24             | 30                       | 0           |                | Parallel Master Port Address Latch Enable Low Byte (Multiplexed Master modes)             |  |  |  |  |

| PMALH    | 29                     | 43              | A28             | 51                       | 0           |                | Parallel Master Port Address Latch Enable High Byte<br>(Multiplexed Master modes)         |  |  |  |  |

| PMRD     | 53                     | 9               | A7              | 13                       | 0           |                | Parallel Master Port Read Strobe                                                          |  |  |  |  |

| PMWR     | 52                     | 8               | B5              | 10                       | 0           | <u> </u>       | Parallel Master Port Write Strobe                                                         |  |  |  |  |

|          |                        | MOS-comp        |                 |                          |             | Analog –       | Analog input P = Power                                                                    |  |  |  |  |

# TABLE 1-12: PMP PINOUT I/O DESCRIPTIONS

egend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

PPS = Peripheral Pin Select

Analog = Analog input O = Output

I = Input

# 2.9 Designing for High-Speed Peripherals

The PIC32MZ EF family devices have peripherals that operate at frequencies much higher than typical for an embedded environment. Table 2-1 lists the peripherals that produce high-speed signals on their external pins:

## TABLE 2-1: PERIPHERALS THAT PRODUCE HS SIGNALS ON EXTERNAL PINS

| Peripheral | High-Speed<br>Signal Pins   | Maximum<br>Speed on<br>Signal Pin |

|------------|-----------------------------|-----------------------------------|

| EBI        | EBIAx,<br>EBIDx             | 50 MHz                            |

| SQI1       | SQICLK,<br>SQICSx,<br>SQIDx | 50 MHz                            |

| HS USB     | D+, D-                      | 480 MHz                           |

Due to these high-speed signals, it is important to consider several factors when designing a product that uses these peripherals, as well as the PCB on which these components will be placed. Adhering to these recommendations will help achieve the following goals:

- Minimize the effects of electromagnetic interference to the proper operation of the product

- Ensure signals arrive at their intended destination at the same time

- Minimize crosstalk

- Maintain signal integrity

- Reduce system noise

- Minimize ground bounce and power sag

# 2.9.1 SYSTEM DESIGN

# 2.9.1.1 Impedance Matching

When selecting parts to place on high-speed buses, particularly the SQI bus, if the impedance of the peripheral device does not match the impedance of the pins on the PIC32MZ EF device to which it is connected, signal reflections could result, thereby degrading the quality of the signal.

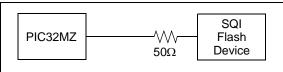

If it is not possible to select a product that matches impedance, place a series resistor at the load to create the matching impedance. See Figure 2-4 for an example.

## FIGURE 2-4: SERIES RESISTOR

# 2.9.1.2 PCB Layout Recommendations

The following list contains recommendations that will help ensure the PCB layout will promote the goals previously listed.

#### Component Placement

- Place bypass capacitors as close to their component power and ground pins as possible, and place them on the same side of the PCB

- Devices on the same bus that have larger setup times should be placed closer to the PIC32MZ EF device

## • Power and Ground

- Multi-layer PCBs will allow separate power and ground planes

- Each ground pin should be connected to the ground plane individually

- Place bypass capacitor vias as close to the pad as possible (preferably inside the pad)

- If power and ground planes are not used, maximize width for power and ground traces

- Use low-ESR, surface-mount bypass capacitors

#### • Clocks and Oscillators

- Place crystals as close as possible to the PIC32MZ EF device OSC/SOSC pins

- Do not route high-speed signals near the clock or oscillator

- Avoid via usage and branches in clock lines (SQICLK)

- Place termination resistors at the end of clock lines

- Traces

- Higher-priority signals should have the shortest traces

- Match trace lengths for parallel buses (EBIAx, EBIDx, SQIDx)

- Avoid long run lengths on parallel traces to reduce coupling

- Make the clock traces as straight as possible

- Use rounded turns rather than right-angle turns

- Have traces on different layers intersect on right angles to minimize crosstalk

- Maximize the distance between traces, preferably no less than three times the trace width

- Power traces should be as short and as wide as possible

- High-speed traces should be placed close to the ground plane

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>f)                  | <b>b</b> -                      | Ð         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | Ś          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Recete |

|                             | 055000                          | 31:16     | _     | _     | —     | _     | _     | _     | —    | _          |      | _    | _    | _    | —    | _    | VOFF< | 17:16> | 00         |

| 0548                        | OFF002                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 0540                        | OFF003                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | —          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 000        |

| J54C                        | 0FF003                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 000        |

| 0550                        | OFF004                          | 31:16     | _     | _     | —     | —     |       | -     | _    | _          |      | _    |      | _    | _    | _    | VOFF< | 17:16> | 000        |

| 0550                        | 011004                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 0554                        | OFF005                          | 31:16     | _     | -     | —     | —     | -     | -     | —    | —          | _    | —    | -    | -    | —    | -    | VOFF< | 17:16> | 000        |

| 0554                        | 011005                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 00         |

| 0558                        | OFF006                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 000        |

| 0550                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 155C                        | OFF007                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 00         |

|                             | 011007                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 00         |

| 0560                        | OFF008                          | 31:16     | _     | -     | —     | —     | -     | -     | —    | —          | _    | —    | -    | -    | —    | -    | VOFF< | 17:16> | 00         |

| 0500                        | 011000                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 000        |

| 0564                        | OFF009                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 00         |

| 0004                        | 011005                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 00         |

| 0568                        | OFF010                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 00         |

| 0000                        | 011010                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       |        | 000        |

| 156C                        | OFF011                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 000        |

| 0000                        | onioni                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0570                        | OFF012                          | 31:16     | —     | —     | —     | —     | —     | —     |      | —          | —    | —    | _    | —    | —    | —    | VOFF< | 17:16> | 00         |

| 0010                        | 011012                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0574                        | OFF013                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          |      | —    | —    | —    | —    | —    | VOFF< | 17:16> | 00         |

| 0374                        | 011013                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0578                        | OFF014                          | 31:16     | —     | —     | —     | —     | _     | _     | _    | —          |      | —    | —    | —    |      | —    | VOFF< | 17:16> | 000        |

| 0070                        | 011014                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0570                        | OFF015                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 000        |

|                             | 0.7010                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0580                        | OFF016                          | 31:16     | _     | _     | —     | —     | —     | —     | —    | —          | —    | —    | —    | _    | —    | —    | VOFF< | 17:16> | 000        |

| 0000                        | 011010                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 000        |

© 2015-2016 Microchip Technology Inc.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

- Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

- Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

<sup>2:</sup>

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>()                  |                                 | Ð         | Bits  |       |       |       |       |       |      |            |      |      |      |      |      |      |       |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

|                             | OFF032                          | 31:16     | _     | _     | -     | —     | -     | _     | -    | _          | _    | _    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0500                        | OFF032                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0504                        | OFF033                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0504                        | 066033                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF034                          | 31:16     | —     |       | —     | _     | _     | -     | _    |            | —    |      | _    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0508                        | 0FF034                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF035                          | 31:16     | —     |       | _     | _     |       |       |      | —          | _    |      | —    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0500                        | 0FF035                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF036                          | 31:16     | —     |       | —     | _     |       |       |      |            | —    |      | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0500                        | 066030                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 05D4                        | OFF037                          | 31:16     | —     |       | —     | _     |       |       |      | —          | —    |      | —    | —    | _    | _    | VOFF< | 17:16> | 0000       |

| 0304                        | 011037                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0508                        | OFF038                          | 31:16     | _     | -     | —     | —     | -     | -     | -    | _          | _    | -    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0300                        | 011030                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     | —      | 0000       |

| 05DC                        | OFF039                          | 31:16     | _     | —     | -     | —     | _     | —     | _    | —          | _    |      | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0300                        | 011039                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0550                        | OFF040                          | 31:16     | _     | _     |       |       |       |       |      | —          | _    |      | —    | _    |      |      | VOFF< | 17:16> | 0000       |

| 0520                        | 011040                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     |        | 0000       |

| 05E4                        | OFF041                          | 31:16     | _     | —     | -     | —     | _     | —     | _    | —          | _    |      | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0564                        | 011041                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 05E8                        | OFF042                          | 31:16     | _     | —     | -     | —     | _     | —     | _    | —          | _    |      | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0520                        | 011042                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     |        | 0000       |

| 05EC                        | OFF043                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0520                        | 011043                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 05E0                        | OFF044                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 001 0                       | 011044                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     | —      | 0000       |

| 05F4                        | OFF045                          | 31:16     | —     | —     | —     | _     | _     | _     | _    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0014                        | 011040                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      | -    | -     |        | 0000       |

| 0558                        | OFF046                          | 31:16     | —     | _     | -     |       | _     | _     | —    | —          | —    | _    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 05-0                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

© 2015-2016 Microchip Technology Inc.

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

- Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

- Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

<sup>2:</sup>

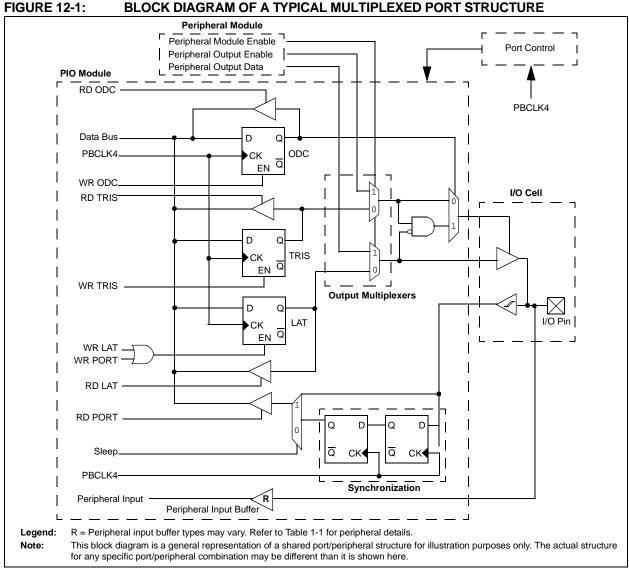

#### 12.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC32MZ EF family device to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Some of the key features of the I/O ports are:

- Individual output pin open-drain enable/disable

- Individual input pin weak pull-up and pull-down

- · Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- · Fast bit manipulation using CLR, SET and INV registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

BLOCK DIAGRAM OF A TYPICAL MULTIPLEXED PORT STRUCTURE

|                     |                             |                                       | [pin name]R Value to                                        |

|---------------------|-----------------------------|---------------------------------------|-------------------------------------------------------------|

| Peripheral Pin      | [pin name]R SFR             | [pin name]R bits                      | RPn Pin Selection                                           |

| INT3                | INT3R                       | INT3R<3:0>                            | 0000 = RPD2                                                 |

| T2CK                | T2CKR                       | T2CKR<3:0>                            | 0001 = RPG8                                                 |

| T6CK                | T6CKR                       | T6CKR<3:0>                            | 0010 = RPF4                                                 |

| IC3                 | IC3R                        | IC3R<3:0>                             | 0011 = RPD10<br>0100 = RPF1                                 |

| IC7                 | IC7R                        | IC7R<3:0>                             | 0101 = RPB9                                                 |

| U1RX                | U1RXR                       | U1RXR<3:0>                            | 0110 = RPB10                                                |

| U2CTS               | U2CTSR                      | U2CTSR<3:0>                           | 0111 = RPC14                                                |

| U5RX                | U5RXR                       | U5RXR<3:0>                            | 1000 = RPB5                                                 |

| U6CTS               | U6CTSR                      | U6CTSR<3:0>                           | 1001 = Reserved<br>1010 = RPC1 <sup>(1)</sup>               |

| SDI1                | SDI1R                       | SDI1R<3:0>                            | 1010 = RPC(1)<br>$1011 = \text{RPD}(14^{(1)})$              |

| SDI3                | SDI3R                       | SDI3R<3:0>                            | $1100 = \text{RPG1}^{(1)}$                                  |

| SDI5 <sup>(1)</sup> | SDI5R <sup>(1)</sup>        | SDI5R<3:0> <sup>(1)</sup>             | 1101 = RPA14 <sup>(1)</sup>                                 |

| SS6 <sup>(1)</sup>  | SS6R <sup>(1)</sup>         | SS6R<3:0> <sup>(1)</sup>              | 1110 = RPD6 <sup>(2)</sup>                                  |

| REFCLKI1            | REFCLKI1R                   | REFCLKI1R<3:0>                        | 1111 = Reserved                                             |

| INT4                | INT4R                       | INT4R<3:0>                            | 0000 <b>= RPD3</b>                                          |

| T5CK                | T5CKR                       | T5CKR<3:0>                            | 0001 = RPG7                                                 |

| T7CK                | T7CKR                       | T7CKR<3:0>                            | 0010 = RPF5<br>0011 = RPD11                                 |

| IC4                 | IC4R                        | IC4R<3:0>                             | 0100 = RPF0                                                 |

| IC8                 | IC8R                        | IC8R<3:0>                             |                                                             |

| U3RX                | U3RXR                       | U3RXR<3:0>                            | 0111 = RPC13                                                |

| U4CTS               | U4CTSR                      | U4CTSR<3:0>                           | 1000 = RPB3<br>1001 = Reserved                              |

| SDI2                | SDI2R                       | SDI2R<3:0>                            | 1010 = RPC4 <sup>(1)</sup>                                  |

| SDI4                | SDI4R                       | SDI4R<3:0>                            | $- 1011 = \text{RPD15}^{(1)}$<br>1100 = RPG0 <sup>(1)</sup> |

| C1RX <sup>(3)</sup> | C1RXR <sup>(3)</sup>        | C1RXR<3:0> <sup>(3)</sup>             | 1101 = RPA15 <sup>(1)</sup>                                 |

| REFCLKI4            | REFCLKI4R                   | REFCLKI4R<3:0>                        |                                                             |

| INT2                | INT2R                       | INT2R<3:0>                            | 0000 = RPD9                                                 |

| T3CK                | T3CKR                       | T3CKR<3:0>                            | 0001 = RPG6                                                 |

| T8CK                | T8CKR                       | T8CKR<3:0>                            | 0010 = RPB8                                                 |

| IC2                 | IC2R                        | IC2R<3:0>                             |                                                             |

| IC5                 | IC5R                        | IC5R<3:0>                             | 0100 = RPD4<br>0101 = RPB0                                  |

| IC9                 | IC9R                        | IC9R<3:0>                             | 0110 = RPE3                                                 |

| U1CTS               | U1CTSR                      | U1CTSR<3:0>                           | 0111 = RPB7                                                 |

| U2RX                | U2RXR                       | U2RXR<3:0>                            | 1000 = Reserved                                             |

| USCTS               | U5CTSR                      | U5CTSR<3:0>                           | $-1001 = \text{RPF12}^{(1)}$                                |

| <u> </u>            | SS1R                        | SS1R<3:0>                             | 1010 = RPD12 <sup>(1)</sup><br>1011 = RPF8 <sup>(1)</sup>   |

| <u> </u>            | SSTR<br>SS3R                | SS3R<3:0>                             | $1011 = RPF8^{(1)}$<br>$1100 = RPC3^{(1)}$                  |

|                     |                             |                                       | 1100 = RPC3(7)<br>1101 = RPE9 <sup>(1)</sup>                |

| <u> </u>            | SS4R<br>SS5R <sup>(1)</sup> | SS4R<3:0><br>SS5R<3:0> <sup>(1)</sup> | 1110 = Reserved                                             |

|                     |                             |                                       | 1111 = Reserved                                             |

| C2RX <sup>(3)</sup> | C2RXR <sup>(3)</sup>        | C2RXR<3:0> <sup>(3)</sup>             |                                                             |

TABLE 12-2: INPUT PIN SELECTION

**Note 1:** This selection is not available on 64-pin devices.

2: This selection is not available on 64-pin or 100-pin devices.

3: This selection is not available on devices without a CAN module.

# TABLE 12-16: PORTG REGISTER MAP FOR 64-PIN DEVICES ONLY

| SSS                         |                                 |           |       |       |       |       |                |       |              | Bi           | ts           |              |      |      |      |      |      |      |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|--------------|--------------|--------------|--------------|------|------|------|------|------|------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All<br>Resets |

| 0600                        | ANSELG                          | 31:16     | _     | —     | —     | -     | —              | —     | —            | —            | —            |              | -    | —    | -    | —    | _    | —    | 0000          |

| 0000                        | ANGLEG                          | 15:0      | _     | _     | _     | _     | _              | _     | ANSG9        | ANSG8        | ANSG7        | ANSG6        | _    | _    | _    | _    | _    | —    | 03C0          |

| 0610                        | TRISG                           | 31:16     | —     | _     | —     | _     | —              | _     | —            | _            | _            | _            | _    | —    | _    | _    |      | —    | 0000          |

| 0010                        | 11100                           | 15:0      | —     | _     | —     | _     | —              | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | —    | _    | _    |      | —    | 03C0          |

| 0620                        | PORTG                           | 31:16     | —     | _     | —     | _     | —              | _     | —            | _            | _            | _            | _    | —    | _    | _    |      | —    | 0000          |

| 0020                        | TOKIO                           | 15:0      | —     | _     | —     | _     | —              | _     | RG9          | RG8          | RG7          | RG6          | _    | —    | _    | _    |      | —    | xxxx          |

| 0630                        | LATG                            | 31:16     | —     | _     | —     | _     | —              | _     | —            | _            | _            | —            | _    | —    | _    | _    |      | —    | 0000          |

| 0000                        | DAIO                            | 15:0      | —     | _     | —     | _     | —              | _     | LATG9        | LATG8        | LATG7        | LATG6        | _    | —    | _    | —    |      | —    | xxxx          |

| 0640                        | ODCG                            | 31:16     | —     | _     | —     | _     | —              | _     | —            |              |              | —            | _    | —    | _    | —    |      | —    | 0000          |

| 0040                        | 0000                            | 15:0      | —     | _     | —     | _     | —              | _     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | —    | _    | —    |      | —    | 0000          |

| 0650                        | CNPUG                           | 31:16     | —     | —     | —     | —     | —              | —     | —            | —            | —            | —            | —    | —    | —    | —    | _    | —    | 0000          |

| 0000                        |                                 | 15:0      | _     | _     | —     | —     | —              | _     | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | —    | —    | —    | —    | _    | —    | 0000          |

| 0660                        | CNPDG                           | 31:16     | _     | -     | —     | -     | —              | _     | —            | _            | _            |              | -    | —    | -    | —    | _    | -    | 0000          |

|                             | 0.1. 20                         | 15:0      | _     | -     | —     | -     | —              | _     | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | -    | —    | -    | —    | _    | -    | 0000          |

|                             |                                 | 31:16     | —     | -     | —     | -     | —              | _     | —            | _            | _            |              | -    | —    | -    | —    | _    | -    | 0000          |

| 0670                        | CNCONG                          | 15:0      | ON    | _     | _     |       | EDGE<br>DETECT | —     | —            | —            | —            | _            |      | —    | -    | —    | _    | _    | 0000          |

| 0680                        | CNENG                           | 31:16     | -     |       | _     |       | _              | _     | —            |              |              |              |      | _    |      | -    |      | —    | 0000          |

| 0000                        | CINEINO                         | 15:0      | _     | -     | _     | -     | —              | _     | CNENG9       | CNENG8       | CNENG7       | CNENG6       | -    | _    | _    | _    | _    | —    | 0000          |

|                             |                                 | 31:16     | —     | -     | —     | -     | —              | —     | —            | _            | _            | —            | -    | —    | -    | —    | -    | —    | 0000          |

| 0690                        | CNSTATG                         | 15:0      | —     | -     | _     | _     | —              | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 |      | —    |      | —    |      | —    | 0000          |

| 0640                        |                                 | 31:16     |       | _     | _     | _     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | —    | 0000          |

| 06A0                        | CNNEG                           | 15:0      | _     | _     | —     | _     | —              | —     | CNNEG9       | CNNEG8       | CNNEG7       | CNNEG6       | _    | _    |      | —    | _    | —    | 0000          |

| 06B0                        | CNFG                            | 31:16     | _     | _     |       |       |                |       | —            | —            | —            | —            |      | —    |      | —    |      | —    | 0000          |

| 0000                        | UNFG                            | 15:0      | _     | _     | _     | _     | —              | _     | CNFG9        | CNFG8        | CNFG7        | CNFG6        | _    | —    |      | _    | -    | —    | 0000          |

| 0600                        | SRCON0G                         | 31:16     | —     | _     | —     | _     | —              | _     | —            | _            | _            |              | _    | —    | _    | —    | _    | —    | 0000          |

|                             | GREUNUG                         | 15:0      | _     | _     | _     |       | —              | _     | SR0G9        | _            | _            | SR0G6        | _    | —    |      | —    | -    | —    | 0000          |

|                             | SRCON1G                         | 31:16     | _     | _     | —     | _     | —              | —     | -            | —            | —            |              | _    | —    | _    | —    | _    | —    | 0000          |

|                             | SILCONIG                        | 15:0      | _     | _     | _     | _     | _              | _     | SR1G9        | _            |              | SR1G6        | _    | _    | _    |      | _    | —    | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

# TABLE 12-21: PORTK REGISTER MAP FOR 144-PIN DEVICES ONLY

| Bits                        |                                 |           |       |       |       |       |                |       |      |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9 | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0910                        | TRISK                           | 31:16     | _     | -     | —     | —     | —              | _     | _    | —    | -            | —            | _            |              | —            | —            | —            | —            | 0000          |

| 0010                        | INION                           | 15:0      | —     | _     | —     | —     | —              | —     | —    | —    | TRISK7       | TRISK6       | TRISK5       | TRISK4       | TRISK3       | TRISK2       | TRISK1       | TRISK0       | OOFF          |

| 0920                        | PORTK                           | 31:16     | —     | _     | —     | —     | —              | —     | —    | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0020                        |                                 | 15:0      | —     | _     | —     | —     | —              | —     | —    | —    | RK7          | RK6          | RK5          | RK4          | RK3          | RK2          | RK1          | RK0          | xxxx          |

| 0930                        | LATK                            | 31:16     | —     | —     | —     | —     | —              | _     | —    | —    | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

|                             |                                 | 15:0      | _     | _     | —     | _     | —              | _     | _    | _    | LATK7        | LATK6        | LATK5        | LATK4        | LATK3        | LATK2        | LATK1        | LATK0        | XXXX          |

| 0940                        | ODCK                            | 31:16     | _     | _     | —     | _     | _              | _     | —    | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | —     | _     | _              | _     | _    | _    | ODCK7        | ODCK6        | ODCK5        | ODCK4        | ODCK3        | ODCK2        | ODCK1        | ODCK0        | 0000          |

| 0950                        | CNPUK                           | 31:16     | _     | _     | _     | _     | _              | _     | _    | _    | -            | -            | -            | —            | -            | -            | -            | -            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | CNPUK7       | CNPUK6       | CNPUK5       | CNPUK4       | CNPUK3       | CNPUK2       | CNPUK1       | CNPUK0       | 0000          |

| 0960                        | CNPDK                           | 31:16     |       |       | -     |       |                |       |      |      | -            |              |              |              |              |              |              |              | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _              | _     |      | _    | CNPDK7       | CNPDK6       | CNPDK5       | CNPDK4       | CNPDK3       | CNPDK2       | CNPDK1       | CNPDK0       | 0000          |

| 0070                        | CNCONK                          | 31:16     | _     | _     | —     | —     | -              |       |      | _    |              | _            | _            | _            | _            |              |              |              | 0000          |

| 0070                        | onconin                         | 15:0      | ON    | —     | —     | —     | EDGE<br>DETECT | —     | —    | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0980                        | CNENK                           | 31:16     | -     |       | _     | _     | _              | _     | _    | _    | ١            | _            |              |              | -            | -            | -            | _            | 0000          |

| 0900                        | CINLINK                         | 15:0      | _     | _     | —     | —     | _              | _     | _    | _    | CNENK7       | CNENK6       | CNENK5       | CNENK4       | CNENK3       | CNENK2       | CNENK1       | CNENK0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | —     | —              | —     | —    | —    | -            | —            | —            | -            | —            | —            | —            | _            | 0000          |

| 0990                        | CNSTATK                         | 15:0      | -     | _     | -     | -     | -              | -     | _    | —    | CN<br>STATK7 | CN<br>STATK6 | CN<br>STATK5 | CN<br>STATK4 | CN<br>STATK3 | CN<br>STATK2 | CN<br>STATK1 | CN<br>STATK0 | 0000          |

| 0040                        | CNNEK                           | 31:16     | —     | _     | —     | _     | _              | _     | _    | _    | _            | —            | _            | _            | _            | —            | _            | _            | 0000          |

| 09A0                        | CININER                         | 15:0      | _     |       |       |       |                |       |      |      | CNNEK7       | CNNEK6       | CNNEK5       | CNNEK4       | CNNEK3       | CNNEK2       | CNNEK1       | CNNEK0       | 0000          |

| 09B0                        | CNFK                            | 31:16     | _     | _     | —     | —     | _              | _     | _    | _    | _            | —            | _            |              |              | —            | —            |              | 0000          |

| 0900                        | UNER                            | 15:0      | _     | -     | _     | _     | _              | _     | _    | _    | CNFK7        | CNFK6        | CNFK5        | CNFK4        | CNFK3        | CNFK2        | CNFK1        | CNFK0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

|              |                   | -                 | -                 |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | _                 | _                 | _                 | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                   | -                 |                   |                   | _                 |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | ?]R<3:0>         |                  |

#### **REGISTER 12-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 12-2 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

## REGISTER 12-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | -                 | -                 |                   | _                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 12-3 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     | —                    | —                 | —                 | —                 | —                 | _                 | _                | _                |  |  |

| 00.40     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | —                    | —                 | —                 | —                 | —                 | _                 | _                | _                |  |  |

| 45.0      | R/W-0                | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |

| 15:8      | ON                   | —                 | SIDL              | —                 | —                 | _                 | FEDGE            | C32              |  |  |

| 7.0       | R/W-0                | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | ICTMR <sup>(1)</sup> | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |  |  |

# REGISTER 17-1: ICXCON: INPUT CAPTURE X CONTROL REGISTER

# Legend:

| R = Readabl   | le bit W = Writable bit                                                                                             | U = Unimplemented bit                                      |

|---------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| -n = Bit Valu | e at POR: ('0', '1', x = unknown)                                                                                   | P = Programmable bit r = Reserved bit                      |

| 1 :: 04 40    |                                                                                                                     |                                                            |

| bit 31-16     | Unimplemented: Read as '0'                                                                                          |                                                            |

| bit 15        | <b>ON:</b> Input Capture Module Enable bit                                                                          |                                                            |

|               | 1 = Module is enabled                                                                                               | disable interrupt generation and allow CED modifications   |

| <b>L:</b> 4 4 |                                                                                                                     | , disable interrupt generation and allow SFR modifications |

| bit 14        | Unimplemented: Read as '0'                                                                                          |                                                            |

| bit 13        | SIDL: Stop in Idle Control bit                                                                                      |                                                            |

|               | 1 = Halt in CPU Idle mode                                                                                           |                                                            |

| 1 1 40 40     | 0 = Continue to operate in CPU Idle mode                                                                            |                                                            |

| bit 12-10     | Unimplemented: Read as '0'                                                                                          |                                                            |

| bit 9         | FEDGE: First Capture Edge Select bit (only u                                                                        | used in mode 6, ICM<2:0> = $110$ )                         |

|               | 1 = Capture rising edge first                                                                                       |                                                            |

| L:1.0         | 0 = Capture falling edge first                                                                                      |                                                            |

| bit 8         | <b>C32:</b> 32-bit Capture Select bit                                                                               |                                                            |

|               | 1 = 32-bit timer resource capture                                                                                   |                                                            |

| hit 7         | 0 = 16-bit timer resource capture                                                                                   | r coloction when C22 (ICyCON (9. ) is (1/)(1)              |

| bit 7         | ICTMR: Timer Select bit (Does not affect time                                                                       | er selection when C32 (ICXCON<8>) is 1)(**                 |

|               | <ul><li>0 = Timery is the counter source for capture</li><li>1 = Timerx is the counter source for capture</li></ul> |                                                            |

| bit 6-5       | ICI<1:0>: Interrupt Control bits                                                                                    |                                                            |

| DIL 0-5       | 11 = Interrupt on every fourth capture event                                                                        |                                                            |

|               | 10 = Interrupt on every third capture event<br>10 = Interrupt on every third capture event                          |                                                            |

|               | 01 = Interrupt on every second capture even                                                                         | nt                                                         |

|               | 00 = Interrupt on every capture event                                                                               |                                                            |

| bit 4         | <b>ICOV:</b> Input Capture Overflow Status Flag bit                                                                 | (read-only)                                                |

|               | 1 = Input capture overflow is occurred                                                                              |                                                            |

|               | 0 = No input capture overflow is occurred                                                                           |                                                            |

| bit 3         | ICBNE: Input Capture Buffer Not Empty State                                                                         | us bit (read-only)                                         |

|               | 1 = Input capture buffer is not empty; at least                                                                     |                                                            |

|               | 0 = Input capture buffer is empty                                                                                   | ·                                                          |

| bit 2-0       | ICM<2:0>: Input Capture Mode Select bits                                                                            |                                                            |

|               | 111 = Interrupt-Only mode (only supported v                                                                         | while in Sleep mode or Idle mode)                          |

|               |                                                                                                                     | edge, specified edge first and every edge thereafter       |

|               | 101 = Prescaled Capture Event mode - eve                                                                            |                                                            |

|               | 100 = Prescaled Capture Event mode - eve                                                                            | ry fourth rising edge                                      |

|               | 011 = Simple Capture Event mode – every r                                                                           | ising edge                                                 |

|               | 010 = Simple Capture Event mode – every f                                                                           |                                                            |

|               | 001 = Edge Detect mode – every edge (risin                                                                          | ng and falling)                                            |

|               | 000 = Input Capture module is disabled                                                                              |                                                            |

**Note 1:** Refer to Table 17-1 for Timerx and Timery selections.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-----------------------|-------------------|-------------------|------------------|-----------------------|

| 04.04        | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN                 | FRMSYPW           | F                 | RMCNT<2:0        | )>                    |

| 00.40        | R/W-0                  | U-0                | U-0               | U-0                   | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(1)</sup> | _                  |                   | —                     | _                 | _                 | SPIFE            | ENHBUF <sup>(1)</sup> |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON                     | _                  | SIDL              | DISSDO <sup>(4)</sup> | MODE32            | MODE16            | SMP              | CKE <sup>(2)</sup>    |

| 7.0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN                   | CKP <sup>(3)</sup> | MSTEN             | DISSDI <sup>(4)</sup> | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

# REGISTER 19-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled ( $\overline{SSx}$  pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support is enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(1)</sup>

- 1 = REFCLKO1 is used by the Baud Rate Generator

- 0 = PBCLK2 is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** This bit can only be written when the ON bit = 0. Refer to **Section 37.0** "**Electrical Characteristics**" for maximum clock frequency requirements.

- 2: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: This bit present for legacy compatibility and is superseded by PPS functionality on these devices (see Section 12.4 "Peripheral Pin Select (PPS)" for more information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|