Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efm144-i-pl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                                   |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|          |                        |                 |                 |                          | PO          | RTG            |                                   |

| RG0      | _                      | 88              | B50             | 128                      | I/O         | ST             | PORTG is a bidirectional I/O port |

| RG1      | —                      | 87              | A60             | 127                      | I/O         | ST             |                                   |

| RG6      | 4                      | 10              | B6              | 14                       | I/O         | ST             |                                   |

| RG7      | 5                      | 11              | A8              | 15                       | I/O         | ST             |                                   |

| RG8      | 6                      | 12              | B7              | 16                       | I/O         | ST             |                                   |

| RG9      | 10                     | 16              | B9              | 21                       | I/O         | ST             |                                   |

| RG12     | —                      | 96              | A65             | 140                      | I/O         | ST             |                                   |

| RG13     | —                      | 97              | B55             | 141                      | I/O         | ST             |                                   |

| RG14     | —                      | 95              | B54             | 139                      | I/O         | ST             |                                   |

| RG15     | —                      | 1               | A2              | 1                        | I/O         | ST             |                                   |

|          |                        |                 |                 |                          | PO          | RTH            |                                   |

| RH0      | —                      | _               | B17             | 43                       | I/O         | ST             | PORTH is a bidirectional I/O port |

| RH1      | —                      | —               | A22             | 44                       | I/O         | ST             |                                   |

| RH2      |                        |                 |                 | 45                       | I/O         | ST             |                                   |

| RH3      | —                      | —               | _               | 46                       | I/O         | ST             |                                   |

| RH4      | —                      | —               | A30             | 65                       | I/O         | ST             |                                   |

| RH5      | —                      | —               | B26             | 66                       | I/O         | ST             |                                   |

| RH6      | —                      | —               | A31             | 67                       | I/O         | ST             |                                   |

| RH7      | —                      | —               | _               | 68                       | I/O         | ST             |                                   |

| RH8      | —                      | —               | B32             | 81                       | I/O         | ST             |                                   |

| RH9      | —                      | —               | A40             | 82                       | I/O         | ST             |                                   |

| RH10     | —                      | —               | B33             | 83                       | I/O         | ST             |                                   |

| RH11     | —                      | —               | —               | 84                       | I/O         | ST             |                                   |

| RH12     | —                      | —               | A47             | 100                      | I/O         | ST             |                                   |

| RH13     | —                      | —               | B40             | 101                      | I/O         | ST             |                                   |

| RH14     | —                      | —               | —               | 102                      | I/O         | ST             |                                   |

| RH15     | —                      | —               |                 | 103                      | I/O         | ST             |                                   |

|          |                        |                 | -               |                          |             | RTJ            | -                                 |

| RJ0      | —                      | _               | B44             | 114                      | I/O         | ST             | PORTJ is a bidirectional I/O port |

| RJ1      | —                      |                 | A55             | 115                      | I/O         | ST             | 1                                 |

| RJ2      | —                      |                 | B45             | 116                      | I/O         | ST             | 1                                 |

| RJ3      | —                      |                 | —               | 117                      | I/O         | ST             | 1                                 |

| RJ4      |                        |                 | A62             | 131                      | I/O         | ST             | 1                                 |

| RJ5      |                        |                 | —               | 132                      | I/O         | ST             | 1                                 |

| RJ6      | —                      |                 | —               | 133                      | I/O         | ST             | 1                                 |

| RJ7      |                        |                 | —               | 134                      | I/O         | ST             | 1                                 |

| RJ8      |                        |                 | A5              | 7                        | I/O         | ST             | 1                                 |

| RJ9      |                        |                 | B4              | 8                        | I/O         | ST             | 1                                 |

| RJ10     | —                      |                 |                 | 10                       | I/O         | ST             | 4                                 |

| RJ11     | —                      | —               | B12             | 27                       | I/O         | ST             | 1                                 |

| RJ12     | —                      | —               | —               | 9                        | I/O         | ST             |                                   |

| RJ13     | —                      | —               | —               | 28                       | I/O         | ST             | 1                                 |

| RJ14     |                        | —               | —               | 29                       | I/O         | ST             | 1                                 |

| RJ15     | —                      | —               | —               | 30                       | I/O         | ST             |                                   |

#### TABLE 1-6: PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input O = Output P = Power

## REGISTER 3-10: FCSR: FLOATING POINT CONTROL AND STATUS REGISTER; CP1 REGISTER 31

- bit 16 V: Invalid Operation bit

- bit 15 Z: Divide-by-Zero bit

- bit 14 **O:** Overflow bit

- bit 13 U: Underflow bit

- bit 12 I: Inexact bit

- bit 11-7 ENABLES<4:0>: FPU Exception Enable bits

These bits control whether or not a trap is taken when an IEEE exception condition occurs for any of the five conditions. The trap occurs when both an enable bit and its corresponding cause bit are set either during an FPU arithmetic operation or by moving a value to the FCSR or one of its alternative representations.

- bit 11 V: Invalid Operation bit

- bit 10 Z: Divide-by-Zero bit

- bit 9 Overflow bit

- bit 8 U: Underflow bit

- bit 7 I: Inexact bit

- bit 6-2 **FLAGS<4:0>:** FPU Flags bits These bits show any exception conditions that have occurred for completed instructions since the flag was last reset by software.

- bit 6 V: Invalid Operation bit

- bit 5 **Z:** Divide-by-Zero bit

- bit 4 **O:** Overflow bit

- bit 3 U: Underflow bit

- bit 2 I: Inexact bit

- bit 1-0 **RM<1:0>:** Rounding Mode control bits

- 11 = Round towards Minus Infinity  $(-\infty)$

- 10 = Round towards Plus Infinity (+  $\infty$ )

- 01 = Round toward Zero (0)

- 00 = Round to Nearest

# TABLE 4-12: SYSTEM BUS TARGET 4 REGISTER MAP

| ess                         |                  | 0         |       |       |          |          |          |       |       |      | Bits     |       |           |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|----------|----------|----------|-------|-------|------|----------|-------|-----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13    | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5      | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| 9020                        | SBT4ELOG1        | 31:16     | MULTI | —     | —        | _        |          | CODE  | <3:0> |      | _        | _     | —         |      | —      | _      | —       | —      | 0000          |

| 9020                        | 361422001        | 15:0      |       |       |          | INI      | ۲ID<7:0> |       |       |      |          | REGIO | N<3:0>    |      | —      | C      | MD<2:0> |        | 0000          |

| 9024                        | SBT4ELOG2        | 31:16     | _     | _     | —        | —        | _        | -     | —     | _    | _        | —     | —         | _    | —      | _      | —       | —      | 0000          |

| 9024                        | 361422002        | 15:0      | _     | _     | —        | —        | _        | -     | —     | _    | _        | —     | —         | _    | —      | _      | GROU    | P<1:0> | 0000          |

| 9028                        | SBT4ECON         | 31:16     | _     | _     | —        | —        | _        | -     | —     | ERRP | _        | —     | —         | _    | —      | _      | —       | —      | 0000          |

| 9020                        | 3BT4LCON         | 15:0      | _     | _     | —        | —        | _        | -     | —     | _    | _        | —     | —         | _    | —      | _      | —       | —      | 0000          |

| 9030                        | SBT4ECLRS        | 31:16     | _     | _     | —        | —        | _        | -     | —     | _    | _        | —     | —         | _    | —      | _      | —       | —      | 0000          |

| 9030                        | 3BT4ECEK3        | 15:0      | _     | _     | —        | —        | _        | -     | —     | _    | _        | —     | —         | _    | —      | _      | —       | CLEAR  | 0000          |

| 9038                        | SBT4ECLRM        | 31:16     | _     | _     | —        | —        | —        | _     | —     | _    | _        | —     | —         | _    | —      | _      | —       | —      | 0000          |

| 9030                        | 3B14ECERW        | 15:0      | _     | _     | —        | —        | _        | -     | —     | _    | _        | —     | —         | _    | —      | _      | —       | CLEAR  | 0000          |

| 9040                        | SBT4REG0         | 31:16     |       |       |          |          |          |       |       | BAS  | SE<21:6> |       |           |      |        |        |         |        | xxxx          |

| 9040                        | 3B14REG0         | 15:0      |       |       | BA       | \SE<5:0> |          |       | PRI   | _    |          |       | SIZE<4:0: | >    |        | _      | —       | —      | xxxx          |

| 9050                        | SBT4RD0          | 31:16     | _     | —     | —        | —        | —        | _     | —     | —    | —        | —     | —         | _    | —      | —      | —       | —      | xxxx          |

| 3030                        | 00141000         | 15:0      | _     | —     | —        | —        | —        | _     | —     | —    | —        | —     | —         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9058                        | SBT4WR0          | 31:16     | _     | —     | —        | —        | —        | _     | —     | —    | —        | —     | —         | _    | —      | —      | —       | —      | xxxx          |

| 3030                        | 3014010          | 15:0      | _     |       | _        | —        | —        | —     | _     | —    | —        |       |           | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9080 SBT4REG2 31:16 BASE    |                  |           |       |       | SE<21:6> |          |          |       |       | -    |          |       | xxxx      |      |        |        |         |        |               |

| 3000                        | 3DT4ICEO2        | 15:0      |       | -     | BA       | SE<5:0>  |          |       | PRI   | —    |          | -     | SIZE<4:0: | >    |        | —      | —       | —      | xxxx          |

| 9090                        | SBT4RD2          | 31:16     | _     | —     | —        | —        | —        | _     | —     | —    | —        | —     | —         | _    | —      | —      | —       | —      | xxxx          |

| 9090                        | 3B14KD2          | 15:0      | _     | _     | —        | —        | _        | -     | —     | _    | _        | —     | —         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9098                        | SBT4WR2          | 31:16     | _     | _     | —        | —        | —        | _     | —     | _    | _        | —     | —         | _    | _      | _      | —       | —      | xxxx          |

| 3080                        | 0014WKZ          | 15:0      | _     | _     | _        | —        | —        | —     | —     | _    | _        | —     | —         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0                  | U-0                  | U-0                  | U-0                  | U-0                  |

| 31:24        | —                 | —                 | _                 | —                    | —                    | —                    | _                    | —                    |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0                  | U-0                  | U-0                  | U-0                  |

| 23:16        | —                 | —                 | _                 | —                    | _                    |                      | _                    | _                    |

| 45.0         | R/W-1             | U-0               | U-0               | R/W-1                | R/W-1                | R/W-1                | R/W-1                | R/W-1                |

| 15:8         | LBWPULOCK         | —                 | _                 | LBWP4 <sup>(1)</sup> | LBWP3 <sup>(1)</sup> | LBWP2 <sup>(1)</sup> | LBWP1 <sup>(1)</sup> | LBWP0 <sup>(1)</sup> |

| 7.0          | R/W-1             | r-1               | U-0               | R/W-1                | R/W-1                | R/W-1                | R/W-1                | R/W-1                |

| 7:0          | UBWPULOCK         | _                 |                   | UBWP4 <sup>(1)</sup> | UBWP3 <sup>(1)</sup> | UBWP2 <sup>(1)</sup> | UBWP1 <sup>(1)</sup> | UBWP0 <sup>(1)</sup> |

## REGISTER 5-8: NVMBWP: FLASH BOOT (PAGE) WRITE-PROTECT REGISTER

| Legend:           |                  | r = Reserved             |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| bit 15  |     | LBWPULOCK: Lower Boot Alias Write-protect Unlock bit                                                                                                                                                            |

|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |     | 1 = LBWPx bits are not locked and can be modified                                                                                                                                                               |

|         |     | 0 = LBWPx bits are locked and cannot be modified                                                                                                                                                                |

|         |     | This bit is only clearable and cannot be set except by any reset.                                                                                                                                               |

| bit 14- | -13 | Unimplemented: Read as '0'                                                                                                                                                                                      |

| bit 12  |     | LBWP4: Lower Boot Alias Page 4 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC10000 through 0x1FC13FFF enabled</li> <li>0 = Write protection for physical address 0x01FC10000 through 0x1FC13FFF disabled</li> </ul>                 |

| bit 11  |     | LBWP3: Lower Boot Alias Page 3 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC0C000 through 0x1FC0FFFF enabled</li> <li>0 = Write protection for physical address 0x01FC0C000 through 0x1FC0FFFF disabled</li> </ul>                 |

| bit 10  |     | LBWP2: Lower Boot Alias Page 2 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC08000 through 0x1FC0BFFF enabled</li> <li>0 = Write protection for physical address 0x01FC08000 through 0x1FC0BFFF disabled</li> </ul>                 |

| bit 9   |     | LBWP1: Lower Boot Alias Page 1 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC04000 through 0x1FC07FFF enabled</li> <li>0 = Write protection for physical address 0x01FC04000 through 0x1FC07FFF disabled</li> </ul>                 |

| bit 8   |     | LBWP0: Lower Boot Alias Page 0 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC00000 through 0x1FC03FFF enabled</li> <li>0 = Write protection for physical address 0x01FC00000 through 0x1FC03FFF disabled</li> </ul>                 |

| bit 7   |     | UBWPULOCK: Upper Boot Alias Write-protect Unlock bit                                                                                                                                                            |

|         |     | <ul> <li>1 = UBWPx bits are not locked and can be modified</li> <li>0 = UBWPx bits are locked and cannot be modified</li> <li>This bit is only user-clearable and cannot be set except by any reset.</li> </ul> |

| bit 6   |     | Reserved: This bit is reserved for use by development tools                                                                                                                                                     |

| bit 5   |     | Unimplemented: Read as '0'                                                                                                                                                                                      |

|         |     |                                                                                                                                                                                                                 |

| Note    | 1:  | These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (LBWPULOCK or UBWPULOCK) is set.                                                                         |

Note: The bits in this register are only writable when the NVMKEY unlock sequence is followed.

| REGISTE | R 10-9: DCHxINT: DMA CHANNEL x INTERRUPT CONTROL REGISTER (CONTINUED)                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | CHDDIF: Channel Destination Done Interrupt Flag bit                                                                                               |

|         | <ul> <li>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)</li> <li>0 = No interrupt is pending</li> </ul>         |

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                          |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>  |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                        |

|         | 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs                 |

| 1.11.0  | 0 = No interrupt is pending                                                                                                                       |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                         |

|         | <ul> <li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li> <li>0 = No interrupt is pending</li> </ul>              |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                 |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                  |

|         | 1 = A channel address error has been detected                                                                                                     |

|         | Either the source or the destination address is invalid.<br>0 = No interrupt is pending                                                           |

|         |                                                                                                                                                   |

| ŝ                           |                                                      |                                                                    |                                       |                |         |       |                     |        |         |       | Bits                    |            |          |          |                       |          |       |      |            |

|-----------------------------|------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------|----------------|---------|-------|---------------------|--------|---------|-------|-------------------------|------------|----------|----------|-----------------------|----------|-------|------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name                                     | Bit Range                                                          | 31/15                                 | 30/14          | 29/13   | 28/12 | 27/11               | 26/10  | 25/9    | 24/8  | 23/7                    | 22/6       | 21/5     | 20/4     | 19/3                  | 18/2     | 17/1  | 16/0 | All Resets |

| 3028                        | USB                                                  | 31:16                                                              |                                       |                |         |       |                     |        |         |       | ATA<31:16>              |            |          |          |                       |          |       |      | 00         |

| 020                         | FIFO2                                                | 15:0                                                               |                                       |                |         |       |                     |        |         |       | ATA<15:0>               |            |          |          |                       |          |       |      | 00         |

| 02C                         | USB<br>FIFO3                                         | 31:16                                                              |                                       |                |         |       |                     |        |         |       | ATA<31:16>              |            |          |          |                       |          |       |      | 00         |

|                             |                                                      | 15:0                                                               |                                       |                |         |       |                     |        |         |       | ATA<15:0><br>ATA<31:16> |            |          |          |                       |          |       |      | 00         |

| 8030                        | USB<br>FIFO4                                         | 31:16<br>15:0                                                      |                                       |                |         |       |                     |        |         |       | ATA<31:16><br>ATA<15:0> |            |          |          |                       |          |       |      | 00         |

|                             | USB                                                  | 31:16                                                              |                                       | DATA<31:16> 00 |         |       |                     |        |         |       |                         |            |          |          |                       |          |       |      |            |

| 3034                        | FIFO5                                                | 15:0                                                               |                                       | DATA<15:0> 00  |         |       |                     |        |         |       |                         |            |          |          |                       |          |       |      |            |

|                             | USB                                                  | 31:16                                                              |                                       | DATA<31:16> 00 |         |       |                     |        |         |       |                         |            |          |          |                       |          |       |      |            |

| 3038                        | FIFO6                                                | 15:0                                                               |                                       | DATA<15:0> 000 |         |       |                     |        |         |       |                         |            |          |          |                       |          |       |      |            |

|                             | USB                                                  | 31:16                                                              |                                       |                |         |       |                     |        |         | D     | ATA<31:16>              |            |          |          |                       |          |       |      | 0(         |

| 03C                         | FIF07                                                | 15:0                                                               | DATA<15:0> 00                         |                |         |       |                     |        |         |       |                         |            |          |          |                       |          |       |      |            |

|                             | USBOTG 31:16 RXDPB RXFIFOSZ<3:0> TXDPB TXFIFOSZ<3:0> |                                                                    |                                       |                | 0 (     |       |                     |        |         |       |                         |            |          |          |                       |          |       |      |            |

| 8060                        | USBOIG                                               | 15:0 TXEDMA RXEDMA BDEV FSDEV LSDEV VBUS<1:0> HOSTMODE HOSTREQ SES |                                       |                |         |       |                     | SESSIO | N 00    |       |                         |            |          |          |                       |          |       |      |            |

| 8064                        | USB                                                  | 31:16                                                              | _                                     |                |         |       |                     |        |         |       |                         | 0(         |          |          |                       |          |       |      |            |

| 004                         | FIFOA                                                | 15:0                                                               | —                                     | -              | —       |       |                     |        |         |       |                         | TXFIFOAD<1 | 2:0>     |          |                       |          |       |      | 00         |

| 806C                        | USB                                                  |                                                                    |                                       | —              | —       | 00    |                     |        |         |       |                         |            |          |          |                       |          |       |      |            |

|                             | HWVER                                                | 15:0                                                               | RC                                    |                |         |       |                     |        |         |       |                         | 08         |          |          |                       |          |       |      |            |

| 3078                        | USB                                                  | 31:16                                                              |                                       |                |         | VPLEN | l<7:0>              |        |         |       |                         |            | DN<3:0>  |          |                       | WTID<3   |       |      | 30         |

|                             | INFO                                                 | 15:0                                                               |                                       | DMACHAN        | IS<3:0> |       |                     | RAMBI  | TS<3:0> | · · · |                         | RXEND      | PTS<3:0> |          |                       | TXENDPTS | <3:0> |      | 8C         |

| 307C                        | USB<br>EOFRST                                        | 31:16                                                              | —                                     | _              | _       | -     |                     | -      | NRSTX   | NRST  |                         |            |          | LSEOF<7: |                       |          |       |      | 00         |

|                             |                                                      | 15:0                                                               |                                       |                |         | FSEOF | -<7:0><br>(HUBPRT<6 |        |         |       |                         |            |          | HSEOF<7: |                       |          |       |      | 77         |

| 3080                        | USB<br>E0TXA                                         | 31:16<br>15:0                                                      |                                       |                | _       |       |                     | >      | _       | _     | MULTTRAN                |            |          |          | BADD<6:0><br>DDR<6:0> |          |       |      | 00         |

|                             |                                                      | 31:16                                                              |                                       | _              | _       |       | HUBPRT<6            |        | _       | _     | —<br>MULTTRAN           |            |          |          | BADD<6:0>             |          |       |      | 00         |

| 3084                        | USB<br>E0RXA                                         | 15:0                                                               |                                       |                | _       | _     |                     |        | _       | _     |                         | _          | _        | _        |                       | _        | _     | _    | 00         |

|                             | USB                                                  | 31:16                                                              | _                                     |                |         | ТХ    | HUBPRT<6            | :0>    |         |       | MULTTRAN                |            |          | TXHU     | BADD<6:0>             |          |       |      | 0.0        |

| 3088                        | E1TXA                                                | 15:0                                                               | _                                     | _              | _       | _     | _                   | _      |         | _     | _                       |            |          |          | DDR<6:0>              |          |       |      | 0.0        |

|                             | USB                                                  | 31:16                                                              | _                                     |                |         | RX    | HUBPRT<6            | 6:0>   |         |       | MULTTRAN                |            |          | RXHU     | BADD<6:0>             |          |       |      | 00         |

| 08C                         | E1RXA                                                | 15:0                                                               | 15:0 — — — — — — — — — — RXFADDR<6:0> |                |         |       |                     |        |         | 0.0   |                         |            |          |          |                       |          |       |      |            |

| 0000                        | USB                                                  | 31:16                                                              | _                                     |                | •       | ТХ    | HUBPRT<6            | :0>    |         |       | MULTTRAN                |            |          | TXHU     | BADD<6:0>             |          |       |      | 0.0        |

| 3090                        | E2TXA                                                | 15:0                                                               | _                                     | _              | _       | _     | —                   | —      | _       | —     |                         |            |          | TXFA     | DDR<6:0>              |          |       |      | 0.0        |

| 3094                        | USB                                                  | 31:16                                                              | —                                     |                |         | RX    | (HUBPRT<6           | 6:0>   |         |       | MULTTRAN                |            |          | RXHU     | BADD<6:0>             |          |       |      | 00         |

| JU 34                       | E2RXA                                                | 15:0                                                               | —                                     |                | —       | —     | —                   | -      | —       | _     | _                       |            |          |          | DDR<6:0>              |          |       |      | 00         |

| 3098                        | USB                                                  | 31:16                                                              | _                                     |                |         | ТХ    | HUBPRT<6            | :0>    |         |       | MULTTRAN                |            |          |          | BADD<6:0>             |          |       |      | 00         |

|                             | E3TXA                                                | 15:0                                                               | _                                     | _              | _       | _     |                     | _      | _       |       |                         |            |          | TXFA     | DDR<6:0>              |          |       |      | 00         |

#### TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24        | DATA<31:24>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23.10        |                   | DATA<23:16>       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | DATA              | <15:8>            |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | DATA              | <7:0>             |                   |                  |                  |  |  |  |  |  |  |  |

## REGISTER 11-12: USBFIFOX: USB FIFO DATA REGISTER 'x' ('x' = 0-7)

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-0 DATA<31:0>: USB Transmit/Receive FIFO Data bits

Writes to this register loads data into the TxFIFO for the corresponding endpoint. Reading from this register unloads data from the RxFIFO for the corresponding endpoint.

Transfers may be 8-bit, 16-bit or 32-bit as required, and any combination of access is allowed provided the data accessed is contiguous. However, all transfers associated with one packet must be of the same width so that data is consistently byte-, word- or double-word aligned. The last transfer may contain fewer bytes than the previous transfers in order to complete an odd-byte or odd-word transfer.

# TABLE 12-9: PORTD REGISTER MAP FOR 100-PIN DEVICES ONLY

| ess                         |                                 | 0         |               |               |               |               |               |               |              | Bits |      |      |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8 | 23/7 | 22/6 | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0300                        | ANSELD                          | 31:16     | _             | _             |               | —             | _             | _             | —            | _    | _    | _    | —            | —            |              |              |              |              | 0000          |

| 0000                        | -                               | 15:0      | ANSD15        | ANSD14        | -             | —             | —             | —             | —            | —    | —    | —    | —            | —            | -            | _            | -            | _            | C000          |

| 0310                        | TRISD                           | 31:16     | _             | —             | —             | _             | —             | _             | —            | -    | _    | _    | _            | _            | —            | _            | _            | —            | 0000          |

| 00.0                        |                                 | 15:0      | TRISD15       | TRISD14       | TRISD13       | TRISD12       | TRISD11       | TRISD10       | TRISD9       | —    | —    | —    | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | FE3F          |

| 0320                        | PORTD                           | 31:16     | —             |               | -             | _             |               | —             |              | —    |      | —    | _            | —            | —            | _            | —            | _            | 0000          |

|                             |                                 | 15:0      | RD15          | RD14          | RD13          | RD12          | RD11          | RD10          | RD9          | —    | _    | _    | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | XXXX          |

| 0330                        | LATD                            | 31:16     |               |               |               |               |               |               | —            | —    | —    | _    | —            | _            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | LATD15        | LATD14        | LATD13        | LATD12        | LATD11        | LATD10        | LATD9        | _    | —    | —    | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | XXXX          |

| 0340                        | ODCD                            | 31:16     | _             | —             | —             | —             | —             | _             | —            | _    | _    | —    | —            | _            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | ODCD15        | ODCD14        | ODCD13        | ODCD12        | ODCD11        | ODCD10        | ODCD9        | _    | _    | —    | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | 0000          |

| 0350                        | CNPUD                           | 31:16     |               | -             | —             | —             | -             | -             | —            | -    |      | _    | —            | -            | —            | —            | -            | —            | 0000          |

|                             |                                 |           | CNPUD15       | CNPUD14       | CNPUD13       | CNPUD12       | CNPUD11       | CNPUD10       | CNPUD9       | _    | _    |      | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | 0000          |

| 0360                        | CNPDD                           | 31:16     |               |               |               |               | -             |               |              | _    | _    |      | -            | -            | -            | -            | -            | -            | 0000          |

|                             |                                 |           | CNPDD15       | CNPDD14       | CNPDD13       | CNPDD12       | CNPDD11       | CNPDD10       | CNPDD9       | _    | _    |      | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | 0000          |

| 0370                        | CNCOND                          | 31:16     | -             |               |               | _             | —<br>EDGE     | _             |              |      | _    | _    | _            |              |              | _            |              | _            | 0000          |

|                             |                                 | 15:0      | ON            | _             | _             |               | DETECT        | _             | —            | —    | —    | -    | —            |              |              | _            |              | _            | 0000          |

| 0380                        | CNEND                           | 31:16     | —             | —             | —             | —             | —             | —             | —            | —    | —    | _    | —            | —            | -            | -            | -            | -            | 0000          |

| 0300                        | CINEIND                         | 15:0      | CNEND15       | CNEND14       | CNEND13       | CNEND12       | CNEND11       | CNEND10       | CNEND9       | —    | _    | _    | CNEND5       | CNEND4       | CNEND3       | CNEND2       | CNEND1       | CNEND0       | 0000          |

|                             |                                 | 31:16     | —             | —             | _             | —             | —             | —             | —            | —    | —    |      | —            | _            | _            | _            | _            |              | 0000          |

| 0390                        | CNSTATD                         | 15:0      | CN<br>STATD15 | CN<br>STATD14 | CN<br>STATD13 | CN<br>STATD12 | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | _    | _    | —    | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | 0000          |

| 00.4.0                      |                                 | 31:16     | _             | _             |               | _             | _             | _             | —            |      | _    | _    | _            | _            | -            | -            | _            | -            | 0000          |

| 03A0                        | CNNED                           | 15:0      | CNNED15       | CNNED14       | CNNED13       | CNNED12       | CNNED11       | CNNED10       | CNNED9       | _    | _    | _    | CNNED5       | CNNED4       | CNNED3       | CNNED2       | CNNED1       | CNNED0       | 0000          |

| 0200                        | CNFD                            | 31:16     | _             | _             | _             | —             | —             | _             | —            | _    | —    | _    | —            | —            | _            |              | _            |              | 0000          |

| 03B0                        | CNFD                            | 15:0      | CNFD15        | CNFD14        | CNFD13        | CNFD12        | CNFD11        | CNFD10        | CNFD9        | _    | —    | _    | CNFD5        | CNFD4        | CNFD3        | CNFD2        | CNFD1        | CNFD0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

## **REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER ('x' = 2-9) (CONTINUED)**

bit 2 Unimplemented: Read as '0'

- bit 1 TCS: Timer Clock Source Select bit<sup>(1)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, Timer5, Timer7, and Timer9). All timer functions are set through the even numbered timers.

- 2: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

- 3: This bit is available only on even numbered timers (Timer2, Timer4, Timer6, and Timer8).

| REGISTE   |                                                                                                                           | SPI CONTROL REGISTER (CONTINUED)                                                                               |  |  |  |  |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| bit 17    |                                                                                                                           | lse Edge Select bit (Framed SPI mode only)                                                                     |  |  |  |  |  |  |  |  |

|           |                                                                                                                           | tion pulse coincides with the first bit clock                                                                  |  |  |  |  |  |  |  |  |

|           | -                                                                                                                         | tion pulse precedes the first bit clock                                                                        |  |  |  |  |  |  |  |  |

| bit 16    | ENHBUF: Enhanced Bu                                                                                                       |                                                                                                                |  |  |  |  |  |  |  |  |

|           | 1 = Enhanced Buffer me                                                                                                    |                                                                                                                |  |  |  |  |  |  |  |  |

|           | 0 = Enhanced Buffer me                                                                                                    |                                                                                                                |  |  |  |  |  |  |  |  |

| bit 15    | <b>ON:</b> SPI/I <sup>2</sup> S Module On                                                                                 |                                                                                                                |  |  |  |  |  |  |  |  |

|           | $1 = SPI/I^2S$ module is e<br>$0 = SPI/I^2S$ module is c                                                                  |                                                                                                                |  |  |  |  |  |  |  |  |

| 1.1.4.4   |                                                                                                                           |                                                                                                                |  |  |  |  |  |  |  |  |

| bit 14    | Unimplemented: Read                                                                                                       |                                                                                                                |  |  |  |  |  |  |  |  |

| bit 13    | SIDL: Stop in Idle Mode                                                                                                   |                                                                                                                |  |  |  |  |  |  |  |  |

|           |                                                                                                                           | ion when CPU enters in Idle mode                                                                               |  |  |  |  |  |  |  |  |

| h:+ 40    | 0 = Continue operation                                                                                                    |                                                                                                                |  |  |  |  |  |  |  |  |

| bit 12    | DISSDO: Disable SDO                                                                                                       |                                                                                                                |  |  |  |  |  |  |  |  |

|           | 1 = SDOx pin is not use 0 = SDOx pin is control                                                                           | ed by the module. Pin is controlled by associated PORT register                                                |  |  |  |  |  |  |  |  |

| hi+ 11 10 |                                                                                                                           | -                                                                                                              |  |  |  |  |  |  |  |  |

| bit 11-10 | •                                                                                                                         | Bit Communication Select bits                                                                                  |  |  |  |  |  |  |  |  |

|           | When AUDEN = 1:                                                                                                           | Communication                                                                                                  |  |  |  |  |  |  |  |  |

|           | MODE32 MODE16                                                                                                             | Communication                                                                                                  |  |  |  |  |  |  |  |  |

|           | 1 1<br>1 0                                                                                                                | 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame<br>32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame |  |  |  |  |  |  |  |  |

|           | 0 1                                                                                                                       | 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                          |  |  |  |  |  |  |  |  |

|           | 0 0                                                                                                                       | 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                          |  |  |  |  |  |  |  |  |

|           |                                                                                                                           | · · · · · · · · · · · · · · · · · · ·                                                                          |  |  |  |  |  |  |  |  |

|           | When AUDEN = 0:                                                                                                           |                                                                                                                |  |  |  |  |  |  |  |  |

|           | MODE32 MODE16                                                                                                             | Communication                                                                                                  |  |  |  |  |  |  |  |  |

|           | 1 x                                                                                                                       | 32-bit                                                                                                         |  |  |  |  |  |  |  |  |

|           | 0 1                                                                                                                       | 16-bit                                                                                                         |  |  |  |  |  |  |  |  |

|           | 0 0                                                                                                                       | 8-bit                                                                                                          |  |  |  |  |  |  |  |  |

| bit 9     | SMP: SPI Data Input Sa                                                                                                    | ample Phase bit                                                                                                |  |  |  |  |  |  |  |  |

|           | Master mode (MSTEN =                                                                                                      |                                                                                                                |  |  |  |  |  |  |  |  |

|           |                                                                                                                           | at end of data output time                                                                                     |  |  |  |  |  |  |  |  |

|           | Slave mode (MSTEN =                                                                                                       | at middle of data output time                                                                                  |  |  |  |  |  |  |  |  |

|           |                                                                                                                           | <u>o).</u><br>hen SPI is used in Slave mode. The module always uses SMP = 0.                                   |  |  |  |  |  |  |  |  |

| bit 8     | CKE: SPI Clock Edge S                                                                                                     |                                                                                                                |  |  |  |  |  |  |  |  |

| DILO      |                                                                                                                           | changes on transition from active clock state to Idle clock state (see CKP bit)                                |  |  |  |  |  |  |  |  |

|           | •                                                                                                                         | changes on transition from Idle clock state to active clock state (see CKP bit)                                |  |  |  |  |  |  |  |  |

| bit 7     | SSEN: Slave Select En                                                                                                     |                                                                                                                |  |  |  |  |  |  |  |  |

|           | $1 = \overline{SSx}$ pin is used for                                                                                      |                                                                                                                |  |  |  |  |  |  |  |  |

|           |                                                                                                                           | for Slave mode, pin is controlled by the port function.                                                        |  |  |  |  |  |  |  |  |

| bit 6     | CKP: Clock Polarity Sel                                                                                                   | ect bit <sup>(3)</sup>                                                                                         |  |  |  |  |  |  |  |  |

|           |                                                                                                                           | s a high level; active state is a low level                                                                    |  |  |  |  |  |  |  |  |

|           | 0 = Idle state for clock                                                                                                  | s a low level; active state is a high level                                                                    |  |  |  |  |  |  |  |  |

|           |                                                                                                                           |                                                                                                                |  |  |  |  |  |  |  |  |

| Note 1:   | •                                                                                                                         | tten when the ON bit = 0. Refer to <b>Section 37.0 "Electrical Characteristics"</b> for                        |  |  |  |  |  |  |  |  |

| 0         | maximum clock frequer                                                                                                     |                                                                                                                |  |  |  |  |  |  |  |  |

| 2:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1). |                                                                                                                |  |  |  |  |  |  |  |  |

| э.        |                                                                                                                           | SPI/I <sup>2</sup> S module functions as if the CKP bit is equal to '1', regardless of the actual              |  |  |  |  |  |  |  |  |

| 3:        | value of the CKP bit.                                                                                                     | Single of the difference of the the one of the equal to $\pm$ , regardless of the actual                       |  |  |  |  |  |  |  |  |

| 4:        |                                                                                                                           | acy compatibility and is superseded by PPS functionality on these devices (see                                 |  |  |  |  |  |  |  |  |

| 7.        |                                                                                                                           | ral Pin Select (PPS)" for more information).                                                                   |  |  |  |  |  |  |  |  |

|           |                                                                                                                           |                                                                                                                |  |  |  |  |  |  |  |  |

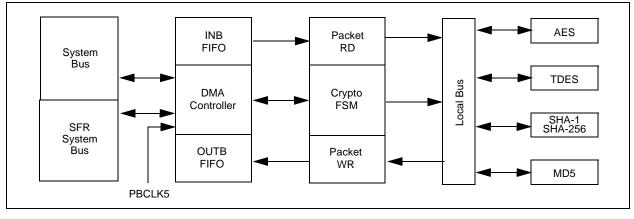

# 26.0 CRYPTO ENGINE

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246) in the "PIC32 Family Reference Manual". which is available from the Microchip web site (www.microchip.com/PIC32).

The Crypto Engine is intended to accelerate applications that need cryptographic functions. By executing these functions in the hardware module, software overhead is reduced and actions, such as encryption, decryption, and authentication can execute much more quickly.

The Crypto Engine uses an internal descriptor-based DMA for efficient programming of the security association data and packet pointers (allowing scatter/ gather data fetching). An intelligent state machine schedules the Crypto Engines based on the protocol selection and packet boundaries. The hardware engines can perform the encryption and authentication in sequence or in parallel.

The following are key features of the Crypto Engine:

- Bulk ciphers and hash engines

- Integrated DMA to off-load processing:

- Buffer descriptor-based

- Secure association per buffer descriptor

- Some functions can execute in parallel

Bulk ciphers that are handled by the Crypto Engine include:

- AES:

- 128-bit, 192-bit, and 256-bit key sizes

- CBC, ECB, CTR, CFB, and OFB modes

- DES/TDES:

- CBC, ECB, CFB, and OFB modes

Authentication engines that are available through the Crypto Engine include:

- SHA-1

- SHA-256

- MD-5

- AES-GCM

- HMAC operation (for all authentication engines)

The rate of data that can be processed by the Crypto Engine depends on these factors:

- Which engine is in use

- Whether the engines are used in parallel or in series

- The demands on source and destination memories by other parts of the system (i.e., CPU, DMA, etc.)

- The speed of PBCLK5, which drives the Crypto Engine

Table 26-1 shows typical performance for various engines.

#### TABLE 26-1: CRYPTO ENGINE PERFORMANCE

| Engine/<br>Algorithm | Performance<br>Factor<br>(Mbps/MHz) | Maximum Mbps<br>(PBCLK5 = 100 MHz) |

|----------------------|-------------------------------------|------------------------------------|

| DES                  | 14.4                                | 1440                               |

| TDES                 | 6.6                                 | 660                                |

| AES-128              | 9.0                                 | 900                                |

| AES-192              | 7.9                                 | 790                                |

| AES-256              | 7.2                                 | 720                                |

| MD5                  | 15.6                                | 1560                               |

| SHA-1                | 13.2                                | 1320                               |

| SHA-256              | 9.3                                 | 930                                |

# FIGURE 26-1: CRYPTO ENGINE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                   | —                 | _                 | —                 | _                 | -                 | —                | —                     |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                 | —                 | _                 | -                 | —                 | -                 | —                | —                     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 15:8         |                   | —                 | _                 | _                 | _                 | _                 | —                | —                     |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

|              |                   |                   |                   | _                 | AREIE             | PKTIE             | BDPIE            | PENDIE <sup>(1)</sup> |

## REGISTER 26-7: CEINTEN: CRYPTO ENGINE INTERRUPT ENABLE REGISTER

#### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-4 Unimplemented: Read as '0'

- bit 3 AREIE: Access Response Error Interrupt Enable bit

- 1 = Access response error interrupts are enabled

- 0 = Access response error interrupts are not enabled

- bit 2 **PKTIE:** DMA Packet Completion Interrupt Enable bit

- 1 = DMA packet completion interrupts are enabled

- 0 = DMA packet completion interrupts are not enabled

- bit 1 BDPIE: DMA Buffer Descriptor Processor Interrupt Enable bit

- 1 = BDP interrupts are enabled

- 0 = BDP interrupts are not enabled

- bit 0 **PENDIE:** Master Interrupt Enable bit<sup>(1)</sup>

- 1 = Crypto Engine interrupts are enabled

- 0 = Crypto Engine interrupts are not enabled

Note 1: The PENDIE bit is a global enable bit and must be enabled together with the other interrupts desired.