Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-TQFP                                                                          |

| Supplier Device Package    | 144-TQFP (16x16)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efm144t-i-ph |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | RDWR              | _                 | _                 | _                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   |                   | —                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   |                   |                   | [                 | DMACH<2:0>       | <b>&gt;</b>      |

#### REGISTER 10-2: DMASTAT: DMA STATUS REGISTER

## Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 RDWR: Read/Write Status bit

1 = Last DMA bus access when an error was detected was a read 0 = Last DMA bus access when an error was detected was a write

bit 30-3 Unimplemented: Read as '0'

bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel when an error was detected.

#### REGISTER 10-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        |                   |                   |                   | DMAADDR           | <31:24>           |                   |                  |                  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   |                   |                   | DMAADDR           | <23:16>           |                   |                  |                  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |

# Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access when an error was detected.

#### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

- bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 CRCTYP: CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

# TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| ŝ        |                  |               |       |                                        |       |       |           |       |      |             | Bits            |             |      |      |           |      |      |      |            |

|----------|------------------|---------------|-------|----------------------------------------|-------|-------|-----------|-------|------|-------------|-----------------|-------------|------|------|-----------|------|------|------|------------|

| (BF8E_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                                  | 29/13 | 28/12 | 27/11     | 26/10 | 25/9 | 24/8        | 23/7            | 22/6        | 21/5 | 20/4 | 19/3      | 18/2 | 17/1 | 16/0 | All Recete |

|          | USB              | 31:16         | _     | - RXHUBPRT<6:0> MULTTRAN RXHUBADD<6:0> |       |       |           |       |      |             |                 |             |      |      | 00        |      |      |      |            |

| 09C      | E3RXA            | 15:0          |       | RXFADDR<6:0>                           |       |       |           |       |      |             |                 |             |      |      |           | 00   |      |      |            |

| 0A0      | US               | 31:16         | 1     | TXHUBPRT<6:0> MULTTRAN TXHUBADD<6:0>   |       |       |           |       |      |             |                 |             |      |      |           | 0 0  |      |      |            |

|          | BE4TXA           | 15:0          | -     | TXFADDR<6:0>                           |       |       |           |       |      |             |                 |             |      |      |           | 00   |      |      |            |

| 0A4      | USB              | 31:16         | _     |                                        |       | RX    | HUBPRT<6  | :0>   |      | 1           | MULTTRAN        |             |      |      | BADD<6:0> |      |      |      | 00         |

|          | E4RXA            | 15:0          | _     | -                                      | -     | —     | —         |       | -    | -           | —               |             |      |      | DDR<6:0>  |      |      |      | 00         |

| 0A8      | USB              | 31:16         | —     |                                        |       |       | HUBPRT<6  |       |      | -           | MULTTRAN        |             |      |      | BADD<6:0> |      |      |      | 00         |

|          | E5TXA            | 15:0          | _     | -                                      | —     | -     | —         | _     | -    | -           | —               |             |      |      | DDR<6:0>  |      |      |      | 00         |

| DAC      | USB<br>E5RXA     | 31:16         | _     |                                        |       | RX    | HUBPRT<6  | :0>   |      |             | MULTTRAN        |             |      |      | BADD<6:0> |      |      |      | 00         |

|          |                  | 15:0          |       |                                        | —     |       | -         |       | _    | -           | -               |             |      |      | DDR<6:0>  |      |      |      | 00         |

| 0В0      | USB<br>E6TXA     | 31:16         |       |                                        |       |       | HUBPRT<6: |       |      | 1           | MULTTRAN        |             |      |      | BADD<6:0> |      |      |      | 00         |

|          |                  | 15:0          | _     | _                                      | -     |       | HUBPRT<6  | -     | _    | —           |                 |             |      |      | DDR<6:0>  |      |      |      | 00         |

| 0B4      | USB<br>E6RXA     | 31:16<br>15:0 | _     | <u> </u>                               |       | r     | HUBPRIS   |       |      |             | MULTTRAN        |             |      |      | BADD<6:0> |      |      |      | 00         |

|          |                  | 31:16         |       |                                        | —     | —<br> | HUBPRT<6  | -     | _    | —           | —<br>MULTTRAN   |             |      |      | DDR<6:0>  |      |      |      | 00         |

| 0B8      | USB<br>E7TXA     | 15:0          |       |                                        | _     |       |           | .0>   |      | _           | MULTIRAN        |             |      |      | DDR<6:0>  |      |      |      | 00         |

|          |                  | 31:16         |       |                                        |       | RX    | HUBPRT<6  | ·0>   |      | _           | MULTTRAN        |             |      |      | BADD<6:0> |      |      |      | 00         |

| 0BC      | USB<br>E7RXA     | 15:0          |       |                                        | _     | _     | _         |       | _    | _           |                 |             |      |      | DDR<6:0>  |      |      |      | 00         |

|          | USB              | 31:16         |       |                                        |       |       |           |       |      |             |                 |             |      |      |           |      |      |      | 00         |

| 100      | E0CSR0           | 15:0          |       |                                        |       |       |           |       | Inde | exed by the | same bits in U  | SBIE0CSR0   |      |      |           |      |      |      | 00         |

| 3108     | USB              | 31:16         |       |                                        |       |       |           |       | Ind  | avad by the | oomo hito in Ll |             |      |      |           |      |      |      | 00         |

| 108      | E0CSR2           | 15:0          |       |                                        |       |       |           |       | Inde | exed by the | same bits in U  | SBIEUCSKZ   |      |      |           |      |      |      | 00         |

| 10C      | USB              | 31:16         |       |                                        |       |       |           |       | Inde | aved by the | same bits in U  | SBIEOCSR3   |      |      |           |      |      |      | 00         |

| 100      | E0CSR3           | 15:0          |       |                                        |       |       |           |       | Inde | sked by the | Same bits in O  | SDIE0001(3  |      |      |           |      |      |      | 00         |

| 3110     | USB              | 31:16         |       |                                        |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR0   |      |      |           |      |      |      | 00         |

| /0       | E1CSR0           | 15:0          |       |                                        |       |       |           |       |      | 5,00 5) 110 |                 | 00.2.100.10 |      |      |           |      |      |      | 00         |

| 3114     | USB              | 31:16         |       |                                        |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR1   |      |      |           |      |      |      | 00         |

|          | E1CSR1           | 15:0          |       |                                        |       |       |           |       |      |             |                 |             |      |      |           |      |      |      | 00         |

| 3118     | USB              | 31:16         |       |                                        |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR2   |      |      |           |      |      |      | 00         |

|          | E1CSR2           | 15:0          |       |                                        |       |       |           |       |      |             |                 |             |      |      |           |      |      |      | 00         |

| 11C      | USB<br>E1CSR3    | 31:16         |       |                                        |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR3   |      |      |           |      |      |      | 00         |

|          |                  | 15:0          |       |                                        |       |       |           |       |      |             |                 |             |      |      |           |      |      |      | 00         |

| 120      | USB<br>E2CSR0    | 31:16         |       |                                        |       |       |           |       | Inde | exed by the | same bits in U  | SBIE2CSR0   |      |      |           |      |      |      | 000        |

|          |                  | 15:0          |       |                                        |       |       |           |       |      |             |                 |             |      |      |           |      |      |      | 000        |

| 3124     | USB<br>E2CSR1    | 31:16         |       | Indexed by the same bits in USBIE2CSR1 |       |       |           |       |      |             |                 |             |      |      |           |      |      |      |            |

|          |                  | 15:0          |       | Reset; — = un                          |       |       |           |       |      |             |                 |             |      |      |           |      |      |      | 000        |

2: 3: 4:

Host mode.

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

| ILC0011      |                   |                   | SD CONTINU        |                   | <b>NEOIOTEN</b>   | 0                 |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | R/W-0             | R/W-0, HC         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | FORCEHST          | FIFOACC           | FORCEFS           | FORCEHS           | PACKET            | TESTK             | TESTJ            | NAK              |

| 22.16        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | —                 |                   | —                 | —                 |                   | ENDPOI            | NT<3:0>          |                  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 15:8         | —                 |                   | —                 | —                 | —                 | RI                | FRMUM<10:8       | 3>               |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | RFRMNU            | <b>/</b> <7:0>    |                   |                  |                  |

## REGISTER 11-4: USBCSR3: USB CONTROL STATUS REGISTER 3

| Legend:           | HC = Hardware Cleared |                          |                    |

|-------------------|-----------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | <b>FORCEHST:</b> Test Mode Force Host Select bit<br>1 = Forces USB module into <i>Host mode</i> , regardless of whether it is connected to any peripheral<br>0 = Normal operation                                                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | FIFOACC: Test Mode Endpoint 0 FIFO Transfer Force bit<br>1 = Transfers the packet in the Endpoint 0 TX FIFO to the Endpoint 0 RX FIFO<br>0 = No transfer                                                                                                                                                                             |

| bit 29    | <b>FORCEFS:</b> Test mode Force Full-Speed Mode Select bit<br>This bit is only active if FORCEHST = 1.<br>1 = Forces USB module into Full-Speed mode. Undefined behavior if FORCEHS = 1.<br>0 = If FORCEHS = 0, places USB module into Low-Speed mode.                                                                               |

| bit 28    | <ul> <li>FORCEHS: Test mode Force Hi-Speed Mode Select bit</li> <li>This bit is only active if FORCEHST = 1.</li> <li>1 = Forces USB module into Hi-Speed mode. Undefined behavior if FORCEFS = 1.</li> <li>0 = If FORCEFS = 0, places USB module into Low-Speed mode.</li> </ul>                                                    |

| bit 27    | <ul> <li>PACKET: Test_Packet Test Mode Select bit</li> <li>This bit is only active if module is in Hi-Speed mode.</li> <li>1 = The USB module repetitively transmits on the bus a 53-byte test packet. Test packet must be loaded into the Endpoint 0 FIFO before the test mode is entered.</li> <li>0 = Normal operation</li> </ul> |

| bit 26    | <b>TESTK:</b> Test_K Test Mode Select bit<br>1 = Enters Test_K test mode. The USB module transmits a continuous K on the bus.<br>0 = Normal operation                                                                                                                                                                                |

|           | This bit is only active if the USB module is in Hi-Speed mode.                                                                                                                                                                                                                                                                       |

| bit 25    | <b>TESTJ:</b> Test_J Test Mode Select bit<br>1 = Enters Test_J test mode. The USB module transmits a continuous J on the bus.<br>0 = Normal operation                                                                                                                                                                                |

|           | This bit is only active if the USB module is in Hi-Speed mode.                                                                                                                                                                                                                                                                       |

| bit 24    | <ul> <li>NAK: Test_SE0_NAK Test Mode Select bit</li> <li>1 = Enter Test_SE0_NAK test mode. The USB module remains in Hi-Speed mode but responds to any valid<br/>IN token with a NAK</li> <li>0 = Normal operation</li> </ul>                                                                                                        |

|           | This mode is only active if module is in Hi-Speed mode.                                                                                                                                                                                                                                                                              |

| bit 23-20 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                           |

## 12.2 Registers for Slew Rate Control

Some I/O pins can be configured for various types of slew rate control on its associated port. This is controlled by the Slew Rate Control bits in the SRCON1x and SRCON0x registers that are associated with each I/O port. The slew rate control is configured using the corresponding bit in each register, as shown in Table 12-1.

As an example, writing 0x0001, 0x0000 to SRCON1A and SRCON0A, respectively, will enable slew rate control on the RA0 pin and sets the slew rate to the slow edge rate.

|         | •=··    |                                                                         |

|---------|---------|-------------------------------------------------------------------------|

| SRCON1x | SRCON0x | Description                                                             |

| 1       | 1       | Slew rate control is enabled<br>and is set to the slowest<br>edge rate. |

| 1       | 0       | Slew rate control is enabled<br>and is set to the slow edge<br>rate.    |

| 0       | 1       | Slew rate control is enabled<br>and is set to the medium<br>edge rate.  |

| 0       | 0       | Slew rate control is disabled and is set to the fastest                 |

TABLE 12-1: SLEW RATE CONTROL BIT SETTINGS

**Note:** By default, all of the Port pins are set to the fastest edge rate.

edge rate.

# 12.3 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

# 12.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option. PPS configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 12.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

#### 12.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART, SPI, and CAN), general purpose timer clock inputs, timer-related peripherals (input capture and output compare), interrupt-on-change inputs, and reference clocks (input and output).

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

# TABLE 12-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                       |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 15B4                        | RPC13R                | 31:16     | _     |       | —     |       | _     |       |      | _    |      | —    | —    | —    | —    | —     | _      | -    | 0000       |

| 1364                        | RECISK                | 15:0      | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    |      | RPC13 | R<3:0> |      | 0000       |

| 15B8                        | RPC14R                | 31:16     | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1300                        | KFC14K                | 15:0      | _     |       | _     |       | —     |       |      | _    |      | -    | _    | _    |      | RPC14 | R<3:0> |      | 0000       |

| 15C0                        | RPD0R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1300                        | REDOR                 | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD0  | R<3:0> |      | 0000       |

| 15C4                        | RPD1R                 | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 1304                        | REDIK                 | 15:0      | —     |       | —     | _     | —     | _     |      | —    | _    | —    | —    | —    |      | RPD1  | R<3:0> |      | 0000       |

| 15C8                        | RPD2R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1300                        | KF D2K                | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | RPD2  | R<3:0> |      | 0000       |

| 15CC                        | RPD3R                 | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1300                        | KF D3K                | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD3  | R<3:0> |      | 0000       |

| 15D0                        | RPD4R                 | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    | —    |      | _     | —      | —    | 0000       |

| 1300                        | KF D4K                | 15:0      | _     | _     | _     | -     | —     | _     | _    | —    | -    | _    | _    | _    |      | RPD4  | R<3:0> |      | 0000       |

| 15D4                        | RPD5R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1304                        | REDSK                 | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | RPD5  | R<3:0> |      | 0000       |

| 15D8                        | RPD6R <sup>(2)</sup>  | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | _     | —      | —    | 0000       |

| 1300                        | KFD0K*/               | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD6  | R<3:0> |      | 0000       |

| 15DC                        | RPD7R <sup>(2)</sup>  | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | _     | —      | —    | 0000       |

| 1300                        | KFD/K·/               | 15:0      | _     | _     | _     | -     | —     | _     | _    | —    | -    | —    | _    | _    |      | RPD7  | R<3:0> |      | 0000       |

| 15E4                        | RPD9R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1324                        | KF D9K                | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | RPD9  | R<3:0> |      | 0000       |

| 15E8                        | RPD10R                | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | _     | —      | —    | 0000       |

| 1020                        | IN DIGIN              | 15:0      | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    |      | RPD10 | R<3:0> |      | 0000       |

| 15EC                        | RPD11R                | 31:16     | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1020                        | KI DIIK               | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD11 | R<3:0> |      | 0000       |

| 15F0                        | RPD12R <sup>(1)</sup> | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1010                        | KI DIZIK <sup>1</sup> | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD12 | R<3:0> |      | 0000       |

| 15F8                        | RPD14R <sup>(1)</sup> | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | —    |      |      | _     | —      | —    | 0000       |

| 101.0                       | IN DI4IN              | 15:0      | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    |      | RPD14 | R<3:0> |      | 0000       |

| 15FC                        | RPD15R <sup>(1)</sup> | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1010                        | N D ION /             | 15:0      | —     | _     |       |       | —     | _     | _    | —    | _    |      | _    |      |      | RPD15 | R<3:0> |      | 0000       |

| 160C                        | RPE3R                 | 31:16     | —     | _     | —     | _     | —     | —     | _    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1000                        | INF LOIN              | 15:0      | —     | -     | —     |       | —     | -     | -    | —    |      | —    | —    | —    |      | RPE3  | R<3:0> |      | 0000       |

| 1614                        | RPE5R                 | 31:16     | _     |       | —     |       | —     |       |      | _    | —    | —    | —    | _    | —    | —     | —      | —    | 0000       |

| 1014                        |                       | 15:0      | —     |       | _     | —     | —     | —     | —    | —    | —    | —    | —    | _    |      | RPE5  | R<3:0> |      | 0000       |

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is not available on 64-pin devices. Note 1:

This register is not available on 64-pin and 100-pin devices. 2:

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 22:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 7.0       | R-0, HC, HS       | R-0, HC, HS       | R-0, HC, HS       | U-0               | U-0               | U-0               | U-0              | R-0, HC, HS      |

| 7:0       | BAD1              | BAD2              | DMTEVENT          | _                 |                   | _                 | _                | WINOPN           |

#### REGISTER 15-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:           | HC = Hardware Cleared | HS = Hardware Set                  |            |

|-------------------|-----------------------|------------------------------------|------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as '0' |            |

| -n = Value at POR | '1' = Bit is set      | 0' = Bit is cleared $x = Bit is$   | is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP1<7:0> value was not detected                                                                                     |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer even was not detected                                                                                             |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

NOTES:

#### REGISTER 19-3: SPIxSTAT: SPI STATUS REGISTER

- bit 3 **SPITBE:** SPI Transmit Buffer Empty Status bit 1 = Transmit buffer, SPIxTXB is empty 0 = Transmit buffer, SPIxTXB is not empty Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

- bit 2 Unimplemented: Read as '0'

- bit 1 SPITBF: SPI Transmit Buffer Full Status bit

- 1 = Transmit is not yet started, SPITXB is full

- 0 = Transmit buffer is not full

#### Standard Buffer Mode:

Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR.

Enhanced Buffer Mode:

Set when CWPTR + 1 = SRPTR; cleared otherwise

- bit 0 SPIRBF: SPI Receive Buffer Full Status bit

- 1 = Receive buffer, SPIxRXB is full

- 0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

| REGIST  | TER 23-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)                                                                                     |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6 | CSF<1:0>: Chip Select Function bits <sup>(1)</sup>                                                                                              |

|         | 11 = Reserved                                                                                                                                   |

|         | 10 = PMCS1 and PMCS2 function as Chip Select                                                                                                    |

|         | 01 = PMCS2 functions as Chip Select and PMCS1 functions as address bit 14<br>00 = PMCS1 and PMCS2 function as address bit 14 and address bit 15 |

| 64 C    |                                                                                                                                                 |

| bit 5   | ALP: Address Latch Polarity bit <sup>(1)</sup>                                                                                                  |

|         | <ol> <li>Active-high (PMALL and PMALH)</li> <li>Active-low (PMALL and PMALH)</li> </ol>                                                         |

| bit 4   | <b>CS2P:</b> Chip Select 2 Polarity bit <sup>(1)</sup>                                                                                          |

|         | 1 = Active-high (PMCS2)                                                                                                                         |

|         | $0 = \text{Active-low}(\overline{\text{PMCS2}})$                                                                                                |

| bit 3   | CS1P: Chip Select 1 Polarity bit <sup>(1)</sup>                                                                                                 |

|         | 1 = Active-high (PMCS1)                                                                                                                         |

|         | $0 = \text{Active-low}(\overline{PMCS1})$                                                                                                       |

| bit 2   | Unimplemented: Read as '0'                                                                                                                      |

| bit 1   | WRSP: Write Strobe Polarity bit                                                                                                                 |

|         | For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):                                                                                       |

|         | 1 = Write strobe active-high (PMWR)                                                                                                             |

|         | 0 = Write strobe active-low (PMWR)                                                                                                              |

|         | For Master mode 1 (MODE<1:0> = 11):                                                                                                             |

|         | 1 = Enable strobe active-high (PMENB)<br>0 = Enable strobe active-low (PMENB)                                                                   |

| bit 0   |                                                                                                                                                 |

| DILU    | <b>RDSP:</b> Read Strobe Polarity bit<br>For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):                                              |

|         | 1 = Read Strobe active-high (PMRD)                                                                                                              |

|         | $0 = \text{Read Strobe active-ling}(\underline{(\text{MRD})})$                                                                                  |

|         | For Master mode 1 (MODE<1:0> = 11):                                                                                                             |

|         | 1 = Read/write strobe active-high (PMRD/PMWR)                                                                                                   |

|         | 0 = Read/write strobe active-low (PMRD/PMWR)                                                                                                    |

|         |                                                                                                                                                 |

Note 1: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | _                 | _                 | —                 | _                 | -                 | _                | —                |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   |                   |                   |                   | _                 |                   |                  | —                |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         |                   | _                 | _                 | _                 | _                 | _                 | _                | —                |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | HDRLEN<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 26-9: CEHDLEN: CRYPTO ENGINE HEADER LENGTH REGISTER

# Legend:

| Logona.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 HDRLEN<7:0>: DMA Header Length bits For every packet, skip this length of locations and start filling the data.

#### REGISTER 26-10: CETRLLEN: CRYPTO ENGINE TRAILER LENGTH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | _                 |                   |                   | —                 |                   |                  | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | TRLRLEN<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **TRLRLEN<7:0>:** DMA Trailer Length bits

For every packet, skip this length of locations at the end of the current packet and start putting the next packet.

ADCIMCON3: ADC INPUT MODE CONTROL REGISTER 3 (CONTINUED) **REGISTER 28-7:** bit 16 SIGN40: AN40 Signed Data Mode bit<sup>(2)</sup> 1 = AN40 is using Signed Data mode 0 = AN40 is using Unsigned Data mode DIFF39: AN39 Mode bit<sup>(2)</sup> bit 15 1 = AN39 is using Differential mode 0 = AN39 is using Single-ended mode bit 14 SIGN39: AN39 Signed Data Mode bit<sup>(2)</sup> 1 = AN39 is using Signed Data mode 0 = AN39 is using Unsigned Data mode bit 13 DIFF38: AN38 Mode bit<sup>(2)</sup> 1 = AN38 is using Differential mode 0 = AN38 is using Single-ended mode SIGN38: AN38 Signed Data Mode bit<sup>(2)</sup> bit 12 1 = AN38 is using Signed Data mode 0 = AN38 is using Unsigned Data mode DIFF37: AN37 Mode bit<sup>(2)</sup> bit 11 1 = AN37 is using Differential mode 0 = AN37 is using Single-ended mode bit 10 SIGN37: AN37 Signed Data Mode bit<sup>(2)</sup> 1 = AN37 is using Signed Data mode 0 = AN37 is using Unsigned Data mode DIFF36: AN36 Mode bit<sup>(2)</sup> bit 9 1 = AN36 is using Differential mode 0 = AN36 is using Single-ended mode SIGN36: AN36 Signed Data Mode bit<sup>(2)</sup> bit 8 1 = AN36 is using Signed Data mode 0 = AN36 is using Unsigned Data mode bit 7 DIFF35: AN35 Mode bit<sup>(2)</sup> 1 = AN35 is using Differential mode 0 = AN35 is using Single-ended mode SIGN35: AN35 Signed Data Mode bit<sup>(2)</sup> bit 6 1 = AN35 is using Signed Data mode 0 = AN35 is using Unsigned Data mode DIFF34: AN34 Mode bit<sup>(1)</sup> bit 5 1 = AN34 is using Differential mode 0 = AN34 is using Single-ended mode SIGN34: AN34 Signed Data Mode bit<sup>(1)</sup> bit 4 1 = AN34 is using Signed Data mode 0 = AN34 is using Unsigned Data mode DIFF33: AN33 Mode bit<sup>(1)</sup> bit 3 1 = AN33 is using Differential mode 0 = AN33 is using Single-ended mode SIGN33: AN33 Signed Data Mode bit<sup>(1)</sup> bit 2 1 = AN33 is using Signed Data mode 0 = AN33 is using Unsigned Data mode

**Note 1:** This bit is not available on 64-pin devices.

2: This bit is not available on 64-pin and 100-pin devices.

## 33.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes power-saving features for the PIC32MZ EF devices. These devices offer various methods and modes that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 33.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the speed of PBCLK7, or selecting a lower power clock source (i.e., LPRC or Sosc).

In addition, the Peripheral Bus Scaling mode is available for each peripheral bus where peripherals are clocked at reduced speed by selecting a higher divider for the associated PBCLKx, or by disabling the clock completely.

# 33.2 Power-Saving with CPU Halted

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

#### 33.2.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted and the associated clocks are disabled. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the peripheral bus clocks will start running and the device will enter into Idle mode.

#### 33.2.2 IDLE MODE

In Idle mode, the CPU is Halted; however, all clocks are still enabled. This allows peripherals to continue to operate. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

#### REGISTER 34-4: DEVCFG1/ADEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FNOSC<2:0>: Oscillator Selection bits

- 111 = FRC divided by FRCDIV<2:0> bits (FRCDIV)

- 110 = Reserved

- 101 = LPRC

- 100 **= S**OSC

- 011 = Reserved

- 010 = Posc (HS, EC)

- 001 = SPLL

- 000 = FRC divided by FRCDIV<2:0> bits (FRCDIV)

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|---------------------|-------------------|-----------------------|------------------|--|

| 04.04        | R                           | R                 | R                   | R                 | R                   | R                 | R                     | R                |  |

| 31:24        |                             | VER<3             | 8:0> <sup>(1)</sup> |                   |                     | DEVID<2           | 27:24> <sup>(1)</sup> |                  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                   | R                 | R                     | R                |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                     |                   |                       |                  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                   | R                 | R                     | R                |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                     |                   |                     |                   |                       |                  |  |

| 7.0          | R                           | R                 | R                   | R                 | R                   | R                 | R                     | R                |  |

| 7:0          |                             |                   |                     | DEVID<            | 7:0> <sup>(1)</sup> |                   |                       |                  |  |

#### REGISTER 34-11: DEVID: DEVICE AND REVISION ID REGISTER

#### Legend:

| Legend.                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID<sup>(1)</sup>

Note 1: Refer to "PIC32 Embedded Connectivity with Floating Point Unit (EF) Family Silicon Errata and Data Sheet Clarification" (DS80000663) for a list of Revision and Device ID values.

#### **REGISTER 34-12:** DEVSNx: DEVICE SERIAL NUMBER REGISTER 'x' ('x' = 0, 1)

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24     | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 31:24     |                   |                   |                   | SN<3              | 31:24>            |                   |                  |                  |  |

| 23:16     | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 23.10     | SN<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |

| 15:8      | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 15.6      | SN<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |

| 7.0       |                   |                   |                   | SN<               | :7:0>             |                   |                  |                  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 SN<31:0>: Device Unique Serial Number bits

# 36.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

# 36.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

|               |        | $\begin{array}{llllllllllllllllllllllllllllllllllll$                  |                    |                        |                       |       |                                                                                                                                                                                                      |

|---------------|--------|-----------------------------------------------------------------------|--------------------|------------------------|-----------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No. | Symbol | Characteristics                                                       | Min.               | Typical <sup>(1)</sup> | Max.                  | Units | Conditions                                                                                                                                                                                           |

| DI60a         | licl   | Input Low Injection<br>Current                                        | 0                  | _                      | <sub>-5</sub> (2,5)   | mA    | This parameter applies<br>to all pins, with the<br>exception of RB10.<br>Maximum IICH current<br>for this exception is<br>0 mA.                                                                      |

| DI60b         | lich   | Input High Injection<br>Current                                       | 0                  | _                      | +5 <sup>(3,4,5)</sup> | mA    | This parameter applies<br>to all pins, with the<br>exception of all 5V toler-<br>ant pins, OSCI, OSCO,<br>SOSCI, SOSCO, D+, D-<br>and RB10. Maximum<br>IICH current for these<br>exceptions is 0 mA. |

| DI60c         | ∑lict  | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(6)</sup> | —                      | +20(6)                | mA    | Absolute instantaneous<br>sum of all $\pm$ input<br>injection currents from<br>all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT                                                                |

#### TABLE 37-10: DC CHARACTERISTICS: I/O PIN INPUT INJECTION CURRENT SPECIFICATIONS

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: VIL source < (Vss - 0.3). Characterized but not tested.

**3:** VIH source > (VDD + 0.3) for non-5V tolerant pins only.

4: Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS - 0.3)).</li>

6: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 2, IICL = (((Vss - 0.3) - VIL source) / Rs). If Note 3, IICH = ((IICH source - (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss - 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

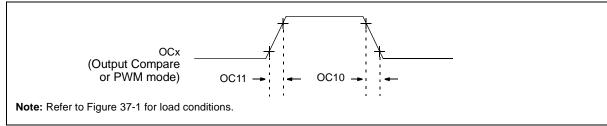

#### FIGURE 37-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 37-28: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                        |      |       |                    |

|--------------------|--------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                    | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| OC10               | TccF   | OCx Output Fall Time           | —                                                                                                                                                                                                                                                                                       | _                      | _    | ns    | See parameter DO32 |

| OC11               | TCCR   | OCx Output Rise Time           | —                                                                                                                                                                                                                                                                                       | —                      | _    | ns    | See parameter DO31 |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

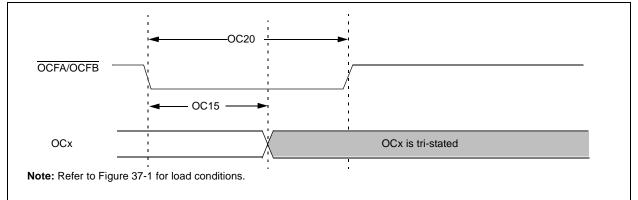

#### FIGURE 37-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 37-29: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                        |     |       |            |  |  |

|--------------------|--------|--------------------------------|-------------------------------------------------------|------------------------|-----|-------|------------|--|--|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup> | Min                                                   | Typical <sup>(2)</sup> | Max | Units | Conditions |  |  |

| OC15               | Tfd    | Fault Input to PWM I/O Change  | —                                                     | —                      | 50  | ns    |            |  |  |

| OC20               | TFLT   | Fault Input Pulse Width        | 50                                                    | —                      |     | ns    |            |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 39-3: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACTE                                                    | ERISTICS               |                        | Standard Operating Conditions: 2.1V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |  |  |

|----------------------------------------------------------------|------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Maximum <sup>(4)</sup> | Units                                                                                                                                           | Conditions |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |                        |                                                                                                                                                 |            |  |  |

| MDC35                                                          | 41                     | 60                     | mA                                                                                                                                              | 252 MHz    |  |  |

|                                                                |                        |                        |                                                                                                                                                 |            |  |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC+PLL with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBPMD = 1), VUSB3V3 is connected to Vss, PBCLKx divisor = 1:128 (' $x' \neq 7$ )

- CPU is in Idle mode (CPU core Halted)

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared (except USBPMD)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.