Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32 <sup>®</sup> M-Class                                                      |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efg064-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

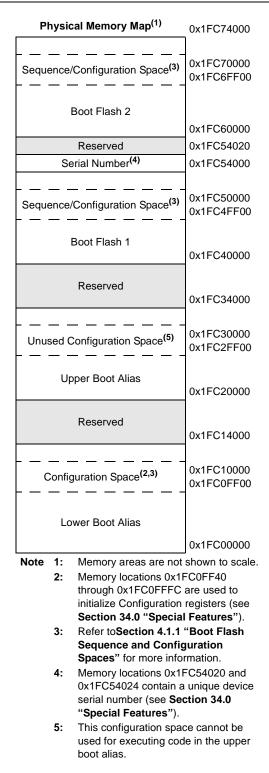

# FIGURE 4-5: BOOT AND ALIAS MEMORY MAP

#### TABLE 4-1: SFR MEMORY MAP

|                           | Virtual Ad | dress           |

|---------------------------|------------|-----------------|

| Peripheral                | Base       | Offset<br>Start |

| System Bus <sup>(1)</sup> | 0xBF8F0000 | 0x0000          |

| Prefetch                  |            | 0x0000          |

| EBI                       |            | 0x1000          |

| SQI1                      |            | 0x2000          |

| USB                       | 0xBF8E0000 | 0x3000          |

| Crypto                    |            | 0x5000          |

| RNG                       |            | 0x6000          |

| CAN1 and CAN2             |            | 0x0000          |

| Ethernet                  | 0xBF880000 | 0x2000          |

| USBCR                     |            | 0x4000          |

| PORTA-PORTK               | 0xBF860000 | 0x0000          |

| Timer1-Timer9             |            | 0x0000          |

| IC1-IC9                   |            | 0x2000          |

| OC1-OC9                   | 0xBF840000 | 0x4000          |

| ADC                       |            | 0xB000          |

| Comparator 1, 2           |            | 0xC000          |

| I2C1-I2C5                 |            | 0x0000          |

| SPI1-SPI6                 | 0,000000   | 0x1000          |

| UART1-UART6               | 0xBF820000 | 0x2000          |

| PMP                       |            | 0xE000          |

| Interrupt Controller      | 0xBF810000 | 0x0000          |

| DMA                       | 00000      | 0x1000          |

| Configuration             |            | 0x0000          |

| Flash Controller          |            | 0x0600          |

| Watchdog Timer            |            | 0x0800          |

| Deadman Timer             | 0vPE800000 | 0x0A00          |

| RTCC                      | 0xBF800000 | 0x0C00          |

| CVREF                     |            | 0x0E00          |

| Oscillator                |            | 0x1200          |

| PPS                       |            | 0x1400          |

Note 1: Refer to 4.2 "System Bus Arbitration" for important legal information.

# TABLE 4-13: SYSTEM BUS TARGET 5 REGISTER MAP

| sse                         |                  |           |       |       |       |          |          |       |       |      | Bits     |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|----------|-------|----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             |                  | 31:16     | MULTI | _     |       | _        |          | CODE  | <3:0> |      | _        |       | _        | _    | _      | _      | _       | _      | 0000          |

| 9420                        | SBT5ELOG1        | 15:0      |       |       |       | INI      | ΓID<7:0> |       |       |      | •        | REGIO | N<3:0>   | •    | —      | C      | MD<2:0> | •      | 0000          |

| 0424                        | SBT5ELOG2        | 31:16     | _     | —     | _     | —        | _        | _     | _     | _    | _        | _     | _        | —    | _      | _      | —       | _      | 0000          |

| 9424                        | SB15ELUG2        | 15:0      | _     | _     | _     | —        | _        | _     | _     | _    | _        | _     | _        | —    | _      | _      | GROU    | P<1:0> | 0000          |

| 0.400                       | SBT5ECON         | 31:16     |       | _     | _     | _        | _        | _     | _     | ERRP | -        | _     | _        | _    | _      | _      | —       | _      | 0000          |

| 9428                        | SBISECON         | 15:0      | _     | —     | _     | _        | —        |       | _     | —    | _        |       | —        | _    | —      | _      | —       | —      | 0000          |

| 9430                        | SBT5ECLRS        | 31:16     | -     | _     |       | —        | _        |       | _     | -    | _        |       | _        | _    | _      | _      | —       | -      | 0000          |

| 9430                        | SBISECLKS        | 15:0      | -     | _     |       | —        | _        |       | _     | -    | _        |       | _        | _    | _      | _      | —       | CLEAR  | 0000          |

| 9438                        | SBT5ECLRM        | 31:16     | _     | —     | _     | —        | —        | —     | —     | —    | _        | _     | —        | —    | —      | —      |         | —      | 0000          |

| 9430                        | SBISECERM        | 15:0      | _     | —     | _     | —        | —        | _     | —     | _    | _        | _     |          | —    | —      | _      | —       | CLEAR  | 0000          |

| 9440                        | SBT5REG0         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |          |      |        |        |         |        | xxxx          |

| 3440                        | OBTOREOU         | 15:0      |       | _     | BA    | ASE<5:0> | -        |       | PRI   | —    |          |       | SIZE<4:0 | >    | _      | —      |         | —      | xxxx          |

| 9450                        | SBT5RD0          | 31:16     | —     | —     | _     | _        | _        |       | —     | _    | —        | _     |          | —    | —      | _      | —       | _      | xxxx          |

| 0 100                       | OBTORES          | 15:0      | —     | —     | —     | —        | —        | —     | —     | —    | —        | —     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9458                        | SBT5WR0          | 31:16     | _     | —     | -     | —        | —        |       | —     | —    | —        |       | _        | —    | —      | _      | —       | —      | xxxx          |

| 0 100                       | obronnic         | 15:0      | _     | —     | —     | —        | —        |       |       | —    | —        | _     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9460                        | SBT5REG1         | 31:16     |       |       |       |          |          |       | 1     | BA   | SE<21:6> |       |          |      |        |        |         |        | xxxx          |

|                             |                  | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | —    |          |       | SIZE<4:0 | >    |        | —      |         | —      | XXXX          |

| 9470                        | SBT5RD1          | 31:16     | —     | —     |       | _        |          | _     | _     |      | _        | _     |          | _    | -      | _      |         | _      | XXXX          |

|                             |                  | 15:0      | —     | —     |       | _        |          |       | _     |      | _        |       |          | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | XXXX          |

| 9478                        | SBT5WR1          | 31:16     | —     | —     |       | _        |          |       | _     |      | _        |       |          | _    | _      | _      |         |        | XXXX          |

|                             |                  | 15:0      | —     | —     | —     | _        | —        |       |       | —    | _        | _     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9480                        | SBT5REG2         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |          |      |        |        |         |        | XXXX          |

|                             |                  | 15:0      |       |       | BA    | ASE<5:0> |          |       | PRI   | —    |          |       | SIZE<4:0 | >    |        | —      |         | —      | XXXX          |

| 9490                        | SBT5RD2          | 31:16     | _     | _     | —     | —        | —        |       | —     | —    | _        | —     | —        | —    | —      | —      | —       | —      | XXXX          |

|                             |                  | 15:0      | _     | _     | —     | —        | —        |       | —     | —    | _        | —     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9498                        | SBT5WR2          | 31:16     |       | _     | —     | —        | —        | _     |       | —    | _        | _     | —        | _    | —      | —      | —       | —      | XXXX          |

|                             |                  | 15:0      | —     | —     | —     | —        | —        | —     | —     | —    | —        | —     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

DS60001320D-page 82

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MZ EF devices contain an internal Flash program memory for executing user code, which includes the following features:

- Two Flash banks for live update support

- Dual boot support

- Write protection for program and boot Flash

- ECC support

There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 52. "Flash Program Memory with Support for Live Update"** (DS60001193) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which is available for download from the Microchip web site (www.microchip.com).

Note: In PIC32MZ EF devices, the Flash page size is 16 KB (4K IW) and the row size is 2 KB (512 IW).

# REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

- bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 CRCTYP: CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| REGISTER 11-9: | USBIENCSR1: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 1 |

|----------------|------------------------------------------------------------|

|                | (ENDPOINT 1-7)                                             |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R-0              | R/W-0            |

| 31:24        | AUTOCLR           | ISO               | DMAREQEN          | DISNYET           | T                 | _                 | —                | INCOMPRX         |

|              | AUTOCLK           | AUTORQ            | DIMAREQEN         | PIDERR            | DMAREQMD          | DATATWEN          | DATATGGL         | INCOVIPRA        |

|              | R/W-0, HC         | R/W-0, HS         | R/W-0             | R/W-0, HC         | R-0, HS           | R/W-0, HS         | R-0, HS, HC      | R/W-0, HS        |

| 23:16        | CLRDT             | SENTSTALL         | SENDSTALL         | FLUSH             | DATAERR           | OVERRUN           | FIFOFULL         | RXPKTRDY         |

|              | GLRDT             | RXSTALL           | REQPKT            | FLUSH             | DERRNAKT          | ERROR             |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         |                   |                   | MULT<4:0>         |                   |                   | R                 | XMAXP<10:8       | < <u>&lt;</u>    |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | RXMA              | XP<7:0>           |                   |                  |                  |

| Legend:           | HC = Hardware Cleared | HS = Hardware Set                  |                    |

|-------------------|-----------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31 AUTOCLR: RXPKTRDY Automatic Clear Control bit

- 1 = RXPKTRDY will be automatically cleared when a packet of RXMAXP bytes has been unloaded from the RX FIFO. When packets of less than the maximum packet size are unloaded, RXPKTRDY will have to be cleared manually. When using a DMA to unload the RX FIFO, data is read from the RX FIFO in 4-byte chunks regardless of the RXMAXP.

- 0 = No automatic clearing of RXPKTRDY

This bit should not be set for high-bandwidth Isochronous endpoints.

- bit 30 ISO: Isochronous Endpoint Control bit (Device mode)

- 1 = Enable the RX endpoint for Isochronous transfers

- 0 = Enable the RX endpoint for Bulk/Interrupt transfers

**AUTORQ:** Automatic Packet Request Control bit (*Host mode*)

- 1 = REQPKT will be automatically set when RXPKTRDY bit is cleared.

- 0 = No automatic packet request

This bit is automatically cleared when a short packet is received.

- bit 29 DMAREQEN: DMA Request Enable Control bit

- 1 = Enable DMA requests for the RX endpoint.

- 0 = Disable DMA requests for the RX endpoint.

- bit 28 **DISNYET:** Disable NYET Handshakes Control/PID Error Status bit (*Device mode*)

- 1 = In Bulk/Interrupt transactions, disables the sending of NYET handshakes. All successfully received RX packets are ACKed including at the point at which the FIFO becomes full.

- 0 = Normal operation.

In Bulk/Interrupt transactions, this bit only has any effect in Hi-Speed mode, in which mode it should be set for all Interrupt endpoints.

#### PIDERR: PID Error Status bit (Host mode)

1 = In ISO transactions, this indicates a PID error in the received packet.

0 = No error

- bit 27 DMAREQMD: DMA Request Mode Selection bit

- 1 = DMA Request Mode 1

- 0 = DMA Request Mode 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   | _                 |                   |                   | Rک                | (FIFOAD<12:       | 8>               |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        |                   |                   |                   | RXFIFO.           | AD<7:0>           |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         |                   | _                 | _                 |                   | TΣ                | (FIFOAD<12:       | 8>               |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | TXFIFO            | AD<7:0>           |                   |                  |                  |

#### REGISTER 11-14: USBFIFOA: USB FIFO ADDRESS REGISTER

# Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

bit 28-16 **RXFIFOAD<12:0>:** Receive Endpoint FIFO Address bits

Start address of the endpoint FIFO in units of 8 bytes as follows:

111111111111 = 0xFFF8

- •

- •

0000000000010 = 0x0010 000000000001 = 0x0008 000000000000 = 0x0000

bit 15-13 Unimplemented: Read as '0'

#### bit 12-0 TXFIFOAD<12:0>: Transmit Endpoint FIFO Address bits

Start address of the endpoint FIFO in units of 8 bytes as follows:

1111111111111 = 0xFFF8

•

•

•

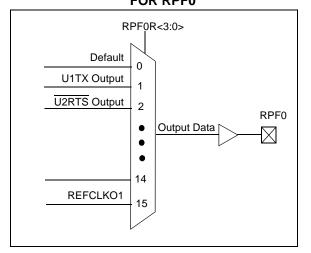

#### 12.4.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 12-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 12-3 and Figure 12-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 12-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPF0

#### 12.4.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32MZ EF devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

# 12.4.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators with Enhanced PLL"** in the *"PIC32 Family Reference Manual"* for details.

# 12.4.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOL0CK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | —                 |                   |                   | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | —                 | _                 |                   | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | —                 | DMAEIE            | PKTCOMPIE         | BDDONEIE         | CONTHRIE         |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CONEMPTYIE        | CONFULLIE         | RXTHRIE           | RXFULLIE          | RXEMPTYIE         | TXTHRIE           | TXFULLIE         | TXEMPTYIE        |

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

HS = Hardware Set

W = Writable bit

'1' = Bit is set

# REGISTER 20-8: SQI1INTEN: SQI INTERRUPT ENABLE REGISTER

| bit 10   | DMAEIE: DMA Bus Error Interrupt Enable bit <ol> <li>Interrupt is enabled</li> <li>Interrupt is disabled</li> <li>PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit</li> <li>Interrupt is enabled</li> <li>Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ol> |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10 I | <ul> <li>0 = Interrupt is disabled</li> <li>PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit</li> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                              |

| bit 10   | <ul> <li>PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit</li> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                                                                 |

| bit 9    | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                                                                                                                                                |

| bit 9    | <ul> <li>Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                                                                                                                                                                                      |

| bit 9 I  | BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit                                                                                                                                                                                                                                                                         |

| :        |                                                                                                                                                                                                                                                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                                   |

| l        | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

| bit 8    | CONTHRIE: Control Buffer Threshold Interrupt Enable bit                                                                                                                                                                                                                                                                           |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

| bit 7    | CONEMPTYIE: Control Buffer Empty Interrupt Enable bit                                                                                                                                                                                                                                                                             |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | CONFULLIE: Control Buffer Full Interrupt Enable bit                                                                                                                                                                                                                                                                               |

|          | This bit enables an interrupt when the receive FIFO buffer is full.                                                                                                                                                                                                                                                               |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | RXTHRIE: Receive Buffer Threshold Interrupt Enable bit                                                                                                                                                                                                                                                                            |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | RXFULLIE: Receive Buffer Full Interrupt Enable bit                                                                                                                                                                                                                                                                                |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                                   |

|          | RXEMPTYIE: Receive Buffer Empty Interrupt Enable bit                                                                                                                                                                                                                                                                              |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                   |

|          | TXTHRIE: Transmit Threshold Interrupt Enable bit                                                                                                                                                                                                                                                                                  |

|          | -                                                                                                                                                                                                                                                                                                                                 |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                   |

|          | TXFULLIE: Transmit Buffer Full Interrupt Enable bit                                                                                                                                                                                                                                                                               |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | TXEMPTYIE: Transmit Buffer Empty Interrupt Enable bit                                                                                                                                                                                                                                                                             |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

Legend:

R = Readable bit

-n = Value at POR

### REGISTER 22-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

PDSEL<1:0>: Parity and Data Selection bits

11 = 9-bit data, no parity

10 = 8-bit data, odd parity

01 = 8-bit data, even parity

00 = 8-bit data, no parity

STSEL: Stop Selection bit

1 = 2 Stop bits 0 = 1 Stop bit

bit 2-1

bit 0

bit 5 ABAUD: Auto-Baud Enable bit

1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion

0 = Baud rate measurement is disabled or completed

bit 4 RXINV: Receive Polarity Inversion bit

1 = UxRX Idle state is '0'

0 = UxRX Idle state is '1'

bit 3 BRGH: High Baud Rate Enable bit

1 = High-Speed mode – 4x baud clock enabled

0 = Standard Speed mode – 16x baud clock enabled

Note 1: These bits are present for legacy compatibility, and are superseded by PPS functionality on these devices.

For additional information, see Section 12.4 "Peripheral Pin Select (PPS)".

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24     | _                 |                   |                   |                   |                   |                   |                  | _                |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | _                 | _                 | —                 | _                 | LVL11             | LVL10             | LVL9             | LVL8             |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | LVL7              | LVL6              | LVL5              | LVL4              | LVL3              | LVL2              | LVL1             | LVL0             |

# REGISTER 28-26: ADCTRGSNS: ADC TRIGGER LEVEL/EDGE SENSITIVITY REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-12 Unimplemented: Read as '0'

- bit 11 LVL11:LVL0: Trigger Level and Edge Sensitivity bits

- 1 = Analog input is sensitive to the high level of its trigger (level sensitivity implies retriggering as long as the trigger signal remains high)

- 0 = Analog input is sensitive to the positive edge of its trigger (this is the value after a reset)

Note 1: This register specifies the trigger level for analog inputs 0 to 31.

2: The higher analog input ID belongs to Class 3, and therefore, is only scan triggered. All Class 3 analog inputs use the Scan Trigger, for which the level/edge is defined by the STRGLVL bit (ADCCON1<3>).

| REGISTER  | 29-10: CIFLTCON0: CAN FILTER CONTROL REGISTER 0 (CONTINUED)                                             |

|-----------|---------------------------------------------------------------------------------------------------------|

| bit 15    | FLTEN1: Filter 1 Enable bit                                                                             |

|           | 1 = Filter is enabled                                                                                   |

|           | 0 = Filter is disabled                                                                                  |

| bit 14-13 | MSEL1<1:0>: Filter 1 Mask Select bits                                                                   |

|           | 11 = Acceptance Mask 3 selected                                                                         |

|           | 10 = Acceptance Mask 2 selected                                                                         |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                      |

| bit 12-8  | FSEL1<4:0>: FIFO Selection bits                                                                         |

| 51(12.0   | 11111 = Message matching filter is stored in FIFO buffer 31                                             |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                             |

|           | •                                                                                                       |

|           | •                                                                                                       |

|           | •                                                                                                       |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                              |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                              |

| bit 7     | FLTEN0: Filter 0 Enable bit                                                                             |

|           | 1 = Filter is enabled                                                                                   |

| 1:0 5     | 0 = Filter is disabled                                                                                  |

| bit 6-5   | MSEL0<1:0>: Filter 0 Mask Select bits                                                                   |

|           | <ul><li>11 = Acceptance Mask 3 selected</li><li>10 = Acceptance Mask 2 selected</li></ul>               |

|           | 01 = Acceptance Mask 2 selected                                                                         |

|           | 00 = Acceptance Mask 0 selected                                                                         |

| bit 4-0   | FSEL0<4:0>: FIFO Selection bits                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                             |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                             |

|           | •                                                                                                       |

|           | •                                                                                                       |

|           | •                                                                                                       |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                              |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                              |

| Note: T   | he bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.   |

| 1010.     | The bits in this register out only be mounded in the corresponding filter enable (I LI LINII) bit is 0. |

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6   | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------------|---------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0                   | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | FLTEN15 MSEL15<1:0>     |                     |                   |                   |                   |                   |                  |                  |

| 00.40        | R/W-0                   | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN14                 | FLTEN14 MSEL14<1:0> |                   | FSEL14<4:0>       |                   |                   |                  |                  |

| 15.0         | R/W-0                   | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FLTEN13                 | FLTEN13 MSEL13<1:0> |                   |                   | F                 | SEL13<4:0>        |                  |                  |

| 7.0          | R/W-0                   | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | 7:0 FLTEN12 MSEL12<1:0> |                     |                   |                   | F                 | SEL12<4:0>        | 1                |                  |

# REGISTER 29-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | <b>FLTEN15:</b> Filter 15 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL15<1:0>: Filter 15 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | FSEL15<4:0>: FIFO Selection bits                                                                                                                                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                         |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                         |

|           | •                                                                                                                                                                                   |

|           | •                                                                                                                                                                                   |

|           |                                                                                                                                                                                     |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

| bit 23    | FLTEN14: Filter 14 Enable bit                                                                                                                                                       |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                              |

| bit 22-21 | MSEL14<1:0>: Filter 14 Mask Select bits                                                                                                                                             |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul>      |

| bit 20-16 | FSEL14<4:0>: FIFO Selection bits                                                                                                                                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                         |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                         |

|           | •                                                                                                                                                                                   |

|           | •                                                                                                                                                                                   |

|           | •                                                                                                                                                                                   |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

|           |                                                                                                                                                                                     |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### **REGISTER 30-24: EMAC1CFG2: ETHERNET CONTROLLER MAC CONFIGURATION 2 REGISTER** VLANPAD: VLAN Pad Enable bit<sup>(1,2)</sup> bit 6 1 = The MAC will pad all short frames to 64 bytes and append a valid CRC 0 = The MAC does not perform padding of short frames PADENABLE: Pad/CRC Enable bit<sup>(1,3)</sup> bit 5 1 = The MAC will pad all short frames 0 = The frames presented to the MAC have a valid length bit 4 CRCENABLE: CRC Enable1 bit 1 = The MAC will append a CRC to every frame whether padding was required or not. Must be set if the PADENABLE bit is set. 0 = The frames presented to the MAC have a valid CRC bit 3 DELAYCRC: Delayed CRC bit This bit determines the number of bytes, if any, of proprietary header information that exist on the front of the IEEE 802.3 frames. 1 = Four bytes of header (ignored by the CRC function) 0 = No proprietary header bit 2 HUGEFRM: Huge Frame enable bit 1 = Frames of any length are transmitted and received 0 = Huge frames are not allowed for receive or transmit bit 1 LENGTHCK: Frame Length checking bit 1 = Both transmit and receive frame lengths are compared to the Length/Type field. If the Length/Type field represents a length then the check is performed. Mismatches are reported on the transmit/receive statistics vector. 0 = Length/Type field check is not performed bit 0 FULLDPLX: Full-Duplex Operation bit 1 = The MAC operates in Full-Duplex mode

- 0 = The MAC operates in Half-Duplex mode

- **Note 1:** Table 30-6 provides a description of the pad function based on the configuration of this register.

- **2:** This bit is ignored if the PADENABLE bit is cleared.

- 3: This bit is used in conjunction with the AUTOPAD and VLANPAD bits.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware

# TABLE 30-6:PAD OPERATION

| Туре | AUTOPAD | VLANPAD | PADENABLE | Action                                                                                  |

|------|---------|---------|-----------|-----------------------------------------------------------------------------------------|

| Any  | х       | x       | 0         | No pad, check CRC                                                                       |

| Any  | 0       | 0       | 1         | Pad to 60 Bytes, append CRC                                                             |

| Any  | x       | 1       | 1         | Pad to 64 Bytes, append CRC                                                             |

| Any  | 1       | 0       | 1         | If untagged: Pad to 60 Bytes, append CRC<br>If VLAN tagged: Pad to 64 Bytes, append CRC |

# 34.2 Registers

#### Virtual Address (BFC0\_#) Bits Bit Range All Resets Register Name 16/0 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 IOL1WAY PMDL1WAY PGL1WAY FETHIO FMIIEN FUSBIDIO 31:16 \_ xxxx \_ FFC0 DEVCFG3 15:0 USERID<15:0> xxxx UPLLFSEL FPLLODIV<2:0> 31:16 \_ — \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx FFC4 DEVCFG2 15:0 FPLLIDIV<2:0> FPLLMULT<6:0> FPLLICLK FPLLRNG<2:0> \_ \_ xxxx 31:16 FDMTEN DMTCNT<4:0> FWDTWINSZ<1:0> FWDTEN WINDIS WDTSPGM WDTPS<4:0> xxxx FFC8 DEVCFG1 FCKSM<1:0> POSCMOD<1:0> 15:0 \_ OSCIOFNC IESO FSOSCEN DMTINTV<2:0> FNOSC<2:0> xxxx \_ \_ 31:16 \_ EJTAGBEN \_ \_ \_ \_ POSCBOOST POSCGAIN<1:0> SOSCBOOST SOSCGAIN<1:0> \_ \_ \_ \_ xxxx FFCC DEVCFG0 15:0 SMCLR DBGPER<2:0> \_ FSLEEP FECCCON<1:0> \_ BOOTISA TRCEN ICESEL<1:0> JTAGEN DEBUG<1:0> xxxx \_ \_ xxxx 31:16 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ FFD0 DEVCP3 15:0 \_ \_ \_ \_ \_ xxxx \_ \_ \_ \_\_\_\_ \_ \_ \_ \_ \_ \_ \_ 31:16 \_ \_ \_ \_ xxxx \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ FFD4 DEVCP2 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx 31:16 xxxx \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_\_\_\_ FFD8 DEVCP 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx \_ \_ CP 31:16 \_ \_ — \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx FFDC DEVCP0 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx 31:16 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx FFE0 DEVSIGN 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx \_ \_ \_ \_ \_ \_ xxxx 31:16 \_ \_ \_ \_ \_ — \_ \_ \_ \_\_\_\_ FFE4 DEVSIGN2 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 31:16 \_ \_ \_ \_ \_ xxxx FFE8 DEVSIGN1 15:0 \_ \_ \_ \_ \_ xxxx \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx 31:16 0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ FFEC DEVSIGNO 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ xxxx

# TABLE 34-1: DEVCFG: DEVICE CONFIGURATION WORD SUMMARY

Legend: x = unknown value on Reset; - = Reserved, read as '1'. Reset values are shown in hexadecimal

| TABLE 37-33: SPIx MODULE SLAVE MODE (CKE = 1) TIM | MING REQUIREMENTS (CONTINUED) |

|---------------------------------------------------|-------------------------------|

|---------------------------------------------------|-------------------------------|

| AC CHARACTERISTICS |                       |                                                                           | (unless o | d Operating<br>otherwise st<br>g temperatur | t <b>ated)</b><br>re -40°C | ≤ TA ≤ + | <b>1V to 3.6V</b><br>85°C for Industrial<br>125°C for Extended |

|--------------------|-----------------------|---------------------------------------------------------------------------|-----------|---------------------------------------------|----------------------------|----------|----------------------------------------------------------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.      | Typical <sup>(2)</sup>                      | Max.                       | Units    | Conditions                                                     |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 88        | _                                           |                            | ns       | _                                                              |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4)                        | 2.5       | _                                           | 12                         | ns       | -                                                              |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                                                     | 10        | _                                           |                            | ns       | —                                                              |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                  | —         | —                                           | 12.5                       | ns       | _                                                              |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 20 ns.

4: Assumes 30 pF load on all SPIx pins.

| AC CHA        | RACTER  | ISTICS           |                        | Standard Operating<br>(unless otherwise s<br>Operating temperatu | tated)<br>re -40° | C ≤ TA ≤ · | V to 3.6V<br>+85°C for Industrial<br>+125°C for Extended |  |

|---------------|---------|------------------|------------------------|------------------------------------------------------------------|-------------------|------------|----------------------------------------------------------|--|

| Param.<br>No. | Symbol  | Characteristics  |                        | Characteristics Min. <sup>(1)</sup>                              |                   | Units      | Conditions                                               |  |

| IM21          | TR:SCL  | SDAx and SCLx    | 100 kHz mode           | —                                                                | 1000              | ns         | CB is specified to be                                    |  |

|               |         | Rise Time        | 400 kHz mode           | 20 + 0.1 Св                                                      | 300               | ns         | from 10 to 400 pF                                        |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | —                                                                | 300               | ns         |                                                          |  |

| IM25          | TSU:DAT | Data Input       | 100 kHz mode           | 250                                                              | _                 | ns         | —                                                        |  |

|               |         | Setup Time       | 400 kHz mode           | 100                                                              | _                 | ns         |                                                          |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | 100                                                              |                   | ns         |                                                          |  |

| IM26          | THD:DAT | Data Input       | 100 kHz mode           | 0                                                                | _                 | μs         | —                                                        |  |

|               |         | Hold Time        | 400 kHz mode           | 0                                                                | 0.9               | μs         | ]                                                        |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | 0                                                                | 0.3               | μs         |                                                          |  |

| IM30          | TSU:STA | Start Condition  | 100 kHz mode           | TPBCLK2 * (BRG + 2)                                              | _                 | μs         | Only relevant for                                        |  |

|               |         | Setup Time       | 400 kHz mode           | TPBCLK2 * (BRG + 2)                                              | _                 | μs         | Repeated Start                                           |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | TPBCLK2 * (BRG + 2)                                              | _                 | μs         | condition                                                |  |

| IM31          | THD:STA | Start Condition  | 100 kHz mode           | TPBCLK2 * (BRG + 2)                                              | _                 | μs         | After this period, the                                   |  |

|               |         | Hold Time        | 400 kHz mode           | TPBCLK2 * (BRG + 2)                                              | _                 | μs         | first clock pulse is                                     |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | TPBCLK2 * (BRG + 2)                                              | _                 | μs         | generated                                                |  |

| IM33          | Tsu:sto | Stop Condition   | 100 kHz mode           | TPBCLK2 * (BRG + 2)                                              |                   | μs         | —                                                        |  |

|               |         | Setup Time       | 400 kHz mode           | TPBCLK2 * (BRG + 2)                                              | _                 | μs         |                                                          |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | TPBCLK2 * (BRG + 2)                                              |                   | μs         |                                                          |  |

| IM34          | THD:STO | Stop Condition   | 100 kHz mode           | TPBCLK2 * (BRG + 2)                                              |                   | ns         | —                                                        |  |

|               |         | Hold Time        | 400 kHz mode           | TPBCLK2 * (BRG + 2)                                              |                   | ns         |                                                          |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | TPBCLK2 * (BRG + 2)                                              | _                 | ns         |                                                          |  |

| IM40          | TAA:SCL | Output Valid     | 100 kHz mode           | —                                                                | 3500              | ns         | _                                                        |  |

|               |         | from Clock       | 400 kHz mode           | —                                                                | 1000              | ns         | —                                                        |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | —                                                                | 350               | ns         | —                                                        |  |

| IM45          | TBF:SDA | Bus Free Time    | 100 kHz mode           | 4.7                                                              | —                 | μs         | The amount of time                                       |  |

|               |         |                  | 400 kHz mode           | 1.3                                                              | —                 | μs         | the bus must be free                                     |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | 0.5                                                              |                   | μs         | before a new<br>transmission can start                   |  |

| IM50          | Св      | Bus Capacitive L | oading                 | —                                                                | _                 | pF         | See parameter DO58                                       |  |

| IM51          | TPGD    | Pulse Gobbler De | elay                   | 52                                                               | 312               | ns         | See Note 3                                               |  |

# TABLE 37-35: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

| AC CHARACTERISTICS |                                     | (unless | d Operatin<br>otherwise<br>g temperatu | <b>stated)</b><br>ire -40° | C ≤ TA ≤ +8 | <b>to 3.6V</b><br>85°C for Industrial<br>125°C for Extended |

|--------------------|-------------------------------------|---------|----------------------------------------|----------------------------|-------------|-------------------------------------------------------------|

| Param.<br>No.      | Characteristic                      | Min.    | Typical                                | Max.                       | Units       | Conditions                                                  |

| MIIM Tin           | ning Requirements                   |         |                                        |                            |             |                                                             |

| ET1                | MDC Duty Cycle                      | 40      | —                                      | 60                         | %           | —                                                           |

| ET2                | MDC Period                          | 400     | —                                      | _                          | ns          | —                                                           |

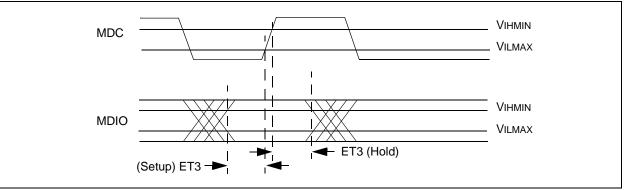

| ET3                | MDIO Output Setup and Hold          | 10      | —                                      | 10                         | ns          | See Figure 37-24                                            |

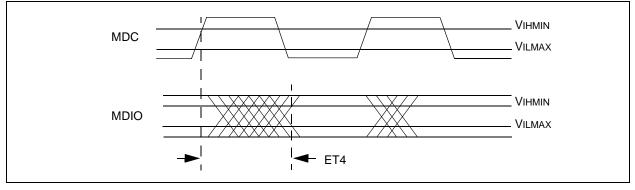

| ET4                | MDIO Input Setup and Hold           | 0       | —                                      | 300                        | ns          | See Figure 37-25                                            |

| MII Timi           | ng Requirements                     |         |                                        |                            |             |                                                             |

| ET5                | TX Clock Frequency                  |         | 25                                     | _                          | MHz         | —                                                           |

| ET6                | TX Clock Duty Cycle                 | 35      | —                                      | 65                         | %           | —                                                           |

| ET7                | ETXDx, ETEN, ETXERR Output Delay    | 0       | _                                      | 25                         | ns          | See Figure 37-26                                            |

| ET8                | RX Clock Frequency                  |         | 25                                     | _                          | MHz         | —                                                           |

| ET9                | RX Clock Duty Cycle                 | 35      | —                                      | 65                         | %           | —                                                           |

| ET10               | ERXDx, ERXDV, ERXERR Setup and Hold | 10      | _                                      | 30                         | ns          | See Figure 37-27                                            |

| <b>RMII</b> Tin    | ning Requirements                   |         |                                        |                            |             |                                                             |

| ET11               | Reference Clock Frequency           | —       | 50                                     | _                          | MHz         | —                                                           |

| ET12               | Reference Clock Duty Cycle          | 35      | —                                      | 65                         | %           | —                                                           |

| ET13               | ETXDx, ETEN, Setup and Hold         | 2       | —                                      | 4                          | ns          | —                                                           |

| ET14               | ERXDx, ERXDV, ERXERR Setup and Hold | 2       |                                        | 4                          | ns          | —                                                           |

# TABLE 37-46: ETHERNET MODULE SPECIFICATIONS

## FIGURE 37-24: MDIO SOURCED BY THE PIC32 DEVICE

# FIGURE 37-25: MDIO SOURCED BY THE PHY

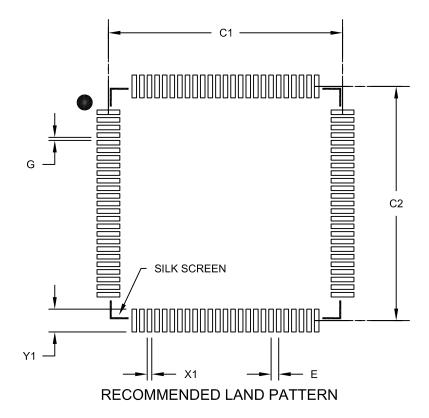

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Ν        | <b><i>MILLIMETER</i></b> | S        |      |

|---------------------------|----------|--------------------------|----------|------|

| Dimensior                 | n Limits | MIN                      | NOM      | MAX  |

| Contact Pitch             | E        |                          | 0.50 BSC |      |

| Contact Pad Spacing       | C1       |                          | 15.40    |      |

| Contact Pad Spacing       | C2       |                          | 15.40    |      |

| Contact Pad Width (X100)  | X1       |                          |          | 0.30 |

| Contact Pad Length (X100) | Y1       |                          |          | 1.50 |

| Distance Between Pads     | G        | 0.20                     |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

## A.4 Resets

The PIC32MZ EF family of devices has updated the resets modules to incorporate the new handling of NMI resets from the WDT, DMT, and the FSCM. In addition, some bits have been moved, as summarized in Table A-5.

#### TABLE A-5: RESET DIFFERENCES

| PIC32MX5XX/6XX/7XX Feature                                                                                                               | PIC32MZ EF Feature                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power                                                                                                                                    | Reset                                                                                                                                                                                                                                |

|                                                                                                                                          | The VREGS bit, which controls whether the internal regulator is<br>enabled in Sleep mode, has been moved from RCON in<br>PIC32MX5XX/6XX/7XX devices to a new PWRCON register in<br>PIC32MZ EF devices.                               |

| VREGS ( <b>RCON&lt;8&gt;</b> )                                                                                                           | VREGS ( <b>PWRCON&lt;0&gt;</b> )                                                                                                                                                                                                     |

| <ul> <li>1 = Regulator is enabled and is on during Sleep mode</li> <li>0 = Regulator is disabled and is off during Sleep mode</li> </ul> | <ul><li>1 = Voltage regulator will remain active during Sleep</li><li>0 = Voltage regulator will go to Stand-by mode during Sleep</li></ul>                                                                                          |