Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efg064-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                       |                                                                        | Pin Nu          | mber            |                          |                                          |                |                             |  |  |

|-----------------------|------------------------------------------------------------------------|-----------------|-----------------|--------------------------|------------------------------------------|----------------|-----------------------------|--|--|

| Pin Name              | 64-pin<br>QFN/<br>TQFP                                                 | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type                              | Buffer<br>Type | Description                 |  |  |

| Timer1 through Timer9 |                                                                        |                 |                 |                          |                                          |                |                             |  |  |

| T1CK                  | 48                                                                     | 73              | A49             | 106                      | Ι                                        | ST             | Timer1 External Clock Input |  |  |

| T2CK                  | PPS                                                                    | PPS             | PPS             | PPS                      | I                                        | ST             | Timer2 External Clock Input |  |  |

| T3CK                  | PPS                                                                    | PPS             | PPS             | PPS                      | I                                        | ST             | Timer3 External Clock Input |  |  |

| T4CK                  | PPS                                                                    | PPS             | PPS             | PPS                      | I                                        | ST             | Timer4 External Clock Input |  |  |

| T5CK                  | PPS                                                                    | PPS             | PPS             | PPS                      | I                                        | ST             | Timer5 External Clock Input |  |  |

| T6CK                  | PPS                                                                    | PPS             | PPS             | PPS                      | I                                        | ST             | Timer6 External Clock Input |  |  |

| T7CK                  | PPS                                                                    | PPS             | PPS             | PPS                      | I                                        | ST             | Timer7 External Clock Input |  |  |

| T8CK                  | PPS                                                                    | PPS             | PPS             | PPS                      | I                                        | ST             | Timer8 External Clock Input |  |  |

| T9CK                  | PPS                                                                    | PPS             | PPS             | PPS                      | I                                        | ST             | Timer9 External Clock Input |  |  |

| Real-                 |                                                                        |                 |                 | Real-                    | Time Clo                                 | ck and Cale    | endar                       |  |  |

| RTCC                  | 46                                                                     | 71              | A48             | 104                      | 0 — Real-Time Clock Alarm/Seconds Output |                |                             |  |  |

| Legend:               | CMOS = CMOS-compatible input or output Analog = Analog input P = Power |                 |                 |                          |                                          |                |                             |  |  |

#### **TABLE 1-7:** TIMER1 THROUGH TIMER9 AND RTCC PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels

TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select

I = Input

|          |                                                                        | Pin Nu          | mber            |                          |             |                                        |                                          |  |  |  |

|----------|------------------------------------------------------------------------|-----------------|-----------------|--------------------------|-------------|----------------------------------------|------------------------------------------|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP                                                 | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type                         | Description                              |  |  |  |

| AERXD0   | - 1                                                                    | 18              | _               | —                        | Ι           | ST                                     | Alternate Ethernet Receive Data 0        |  |  |  |

| AERXD1   | —                                                                      | 19              | _               | —                        | Ι           | ST                                     | Alternate Ethernet Receive Data 1        |  |  |  |

| AERXD2   | —                                                                      | 28              | _               | —                        | Ι           | ST                                     | Alternate Ethernet Receive Data 2        |  |  |  |

| AERXD3   | —                                                                      | 29              | —               | —                        | I           | ST                                     | Alternate Ethernet Receive Data 3        |  |  |  |

| AERXERR  | —                                                                      | 1               | —               | —                        | I           | ST                                     | Alternate Ethernet Receive Error Input   |  |  |  |

| AERXDV   | —                                                                      | 12              | —               | —                        | I           | ST                                     | Alternate Ethernet Receive Data Valid    |  |  |  |

| AERXCLK  | —                                                                      | 16              | —               | —                        | I           | ST                                     | Alternate Ethernet Receive Clock         |  |  |  |

| AETXD0   | —                                                                      | 47              | —               | —                        | 0           | —                                      | Alternate Ethernet Transmit Data 0       |  |  |  |

| AETXD1   | —                                                                      | 48              | —               | —                        | 0           | —                                      | Alternate Ethernet Transmit Data 1       |  |  |  |

| AETXD2   | —                                                                      | 44              | —               | —                        | 0           | —                                      | Alternate Ethernet Transmit Data 2       |  |  |  |

| AETXD3   | —                                                                      | 43              | —               | —                        | 0           | —                                      | Alternate Ethernet Transmit Data 3       |  |  |  |

| AETXERR  | —                                                                      | 35              | —               | —                        | 0           | —                                      | Alternate Ethernet Transmit Error        |  |  |  |

| AECOL    | —                                                                      | 42              | —               | —                        | I           | ST                                     | Alternate Ethernet Collision Detect      |  |  |  |

| AECRS    | —                                                                      | 41              | —               | —                        | I           | ST                                     | Alternate Ethernet Carrier Sense         |  |  |  |

| AETXCLK  | —                                                                      | 66              | —               | —                        | I           | ST                                     | Alternate Ethernet Transmit Clock        |  |  |  |

| AEMDC    | —                                                                      | 70              | —               | —                        | 0           | —                                      | Alternate Ethernet Management Data Clock |  |  |  |

| AEMDIO   | —                                                                      | 71              | _               | —                        | I/O         | —                                      | Alternate Ethernet Management Data       |  |  |  |

| AETXEN   | —                                                                      | 67              | —               | —                        | 0           | O — Alternate Ethernet Transmit Enable |                                          |  |  |  |

| Legend:  | CMOS = CMOS-compatible input or output Analog = Analog input P = Power |                 |                 |                          |             |                                        |                                          |  |  |  |

**TABLE 1-18: ALTERNATE ETHERNET MII PINOUT I/O DESCRIPTIONS**

CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output

I = Input

PPS = Peripheral Pin Select

#### **TABLE 1-19: ALTERNATE ETHERNET RMII PINOUT I/O DESCRIPTIONS**

|                        | Pin Nu                                                             | mber                                                                                                                                                                                                         | er                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP                                                    | 124-pin<br>VTLA                                                                                                                                                                                              | 144-pin<br>TQFP/<br>LQFP                                                                                                                                                                                                        | Pin<br>Type                                                                                                                                                                                                                                                                                                                                                                                   | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 43                     | 18                                                                 | -                                                                                                                                                                                                            | _                                                                                                                                                                                                                               | Ι                                                                                                                                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Receive Data 0                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 46                     | 19                                                                 |                                                                                                                                                                                                              | —                                                                                                                                                                                                                               | I                                                                                                                                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Receive Data 1                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 51                     | 1                                                                  |                                                                                                                                                                                                              | —                                                                                                                                                                                                                               | I                                                                                                                                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Receive Error Input                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 57                     | 47                                                                 |                                                                                                                                                                                                              | —                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                          | Alternate Ethernet Transmit Data 0                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 56                     | 48                                                                 |                                                                                                                                                                                                              | —                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                          | Alternate Ethernet Transmit Data 1                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 30                     | 70                                                                 |                                                                                                                                                                                                              | —                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                          | Alternate Ethernet Management Data Clock                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 49                     | 71                                                                 |                                                                                                                                                                                                              | —                                                                                                                                                                                                                               | I/O                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                          | Alternate Ethernet Management Data                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 50                     | 67                                                                 |                                                                                                                                                                                                              | —                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                          | Alternate Ethernet Transmit Enable                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 45                     | 16                                                                 | —                                                                                                                                                                                                            | —                                                                                                                                                                                                                               | Ι                                                                                                                                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Reference Clock                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 62                     | 12                                                                 | —                                                                                                                                                                                                            | —                                                                                                                                                                                                                               | I                                                                                                                                                                                                                                                                                                                                                                                             | ST                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Carrier Sense Data Valid                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                        | QFN/<br>TQFP<br>43<br>46<br>51<br>57<br>56<br>30<br>49<br>50<br>45 | 64-pin<br>QFN/<br>TQFP      100-pin<br>TQFP        43      18        46      19        51      1        57      47        56      48        30      70        49      71        50      67        45      16 | QFN/<br>TQFP      100-pin<br>TQFP      124-pin<br>VTLA        43      18         46      19         51      1         57      47         56      48         30      70         49      71         50      67         45      16 | 64-pin<br>QFN/<br>TQFP      100-pin<br>TQFP      124-pin<br>VTLA      144-pin<br>TQFP/<br>LQFP        43      18      -      -        46      19      -      -        51      1      -      -        57      47      -      -        56      48      -      -        30      70      -      -        49      71      -      -        50      67      -      -        45      16      -      - | 64-pin<br>QFN/<br>TQFP      100-pin<br>TQFP      124-pin<br>VTLA      144-pin<br>TQFP/<br>LQFP      Pin<br>Type        43      18       1        46      19       1        51      1       1        57      47       0        56      48       0        30      70       0        49      71       0        50      67       0        45      16       1 | 64-pin<br>QFN/<br>TQFP      100-pin<br>TQFP      124-pin<br>VTLA      144-pin<br>TQFP/<br>LQFP      Pin<br>TQFP/<br>LQFP      Buffer<br>Type        43      18       1      ST        46      19       1      ST        51      1        I      ST        57      47       0         56      48       0         30      70       0         49      71       N/O         50      67       0         45      16        I      ST |  |  |

CMOS = CMOS-compatible input or output Legend: ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = OutputPPS = Peripheral Pin Select

P = Power I = Input

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |                    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1        | Bit<br>24/16/8/0 |

|--------------|----------------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|------------------|

| 24.24        | r-1                              | U-0                | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0              |

| 31:24        | —                                | —                  | —                 | —                 | —                 | —                 | _                       | —                |

| 22.46        | U-0                              | R-0                | R-1               | R-0               | R-0               | R-0               | R-1                     | R/W-y            |

| 23:16        | —                                | IPLW               | <1:0>             |                   | MMAR<2:0>         | MCU               | ISAONEXC <sup>(1)</sup> |                  |

| 15.0         | R-y                              | R-y                | R-1               | R-1               | R-1               | R-1               | U-0                     | R-1              |

| 15:8         | ISA<1                            | :0> <sup>(1)</sup> | ULRI              | RXI               | DSP2P             | DSPP              | _                       | ITL              |

| 7.0          | U-0                              | R-1                | R-1               | R-0               | R-1               | U-0               | U-0                     | R-0              |

| 7:0          | _                                | VEIC               | VINT              | SP                | CDMM              | _                 | —                       | TL               |

|              | •                                | •                  |                   | •                 | -                 |                   |                         |                  |

# REGISTER 3-3: CONFIG3: CONFIGURATION REGISTER 3; CP0 REGISTER 16, SELECT 3

| Legend:           | r = Reserved bit | y = Value set from Co | alue set from Configuration bits on POR |  |  |  |

|-------------------|------------------|-----------------------|-----------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b   | it, read as '0'                         |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                      |  |  |  |

bit 31 **Reserved:** This bit is hardwired as '1' to indicate the presence of the Config4 register

- bit 30-23 Unimplemented: Read as '0'

- bit 22-21 **IPLW<1:0>:** Width of the Status IPL and Cause RIPL bits 01 = IPL and RIPL bits are 8-bits in width

- bit 20-18 **MMAR<2:0>:** microMIPS Architecture Revision Level bits 000 = Release 1

- bit 17 MCU: MIPS<sup>®</sup> MCU<sup>™</sup> ASE Implemented bit

- 1 = MCU ASE is implemented

- bit 16 **ISAONEXC:** ISA on Exception bit<sup>(1)</sup> 1 = microMIPS is used on entrance to an exception vector 0 = MIPS32 ISA is used on entrance to an exception vector

- bit 15-14 **ISA<1:0>:** Instruction Set Availability bits<sup>(1)</sup> 11 = Both MIPS32 and microMIPS are implemented; microMIPS is used when coming out of reset

- 10 = Both MIPS32 and microMIPS are implemented; MIPS32 ISA used when coming out of reset

- bit 13 ULRI: UserLocal Register Implemented bit

- 1 = UserLocal Coprocessor 0 register is implemented

- bit 12 RXI: RIE and XIE Implemented in PageGrain bit

- 1 = RIE and XIE bits are implemented

- bit 11 **DSP2P:** MIPS DSP ASE Revision 2 Presence bit 1 = DSP Revision 2 is present

- bit 10 **DSPP:** MIPS DSP ASE Presence bit

- 1 = DSP is present

- bit 9 Unimplemented: Read as '0'

- bit 8 ITL: Indicates that iFlowtrace<sup>®</sup> hardware is present

- $1 = \text{The iFlowtrace}^{\mathbb{R}}$  is implemented in the core

- bit 7 Unimplemented: Read as '0'

- bit 6 **VEIC:** External Vector Interrupt Controller bit

- 1 = Support for an external interrupt controller is implemented

- bit 5 **VINT:** Vector Interrupt bit

- 1 = Vector interrupts are implemented

- bit 4 SP: Small Page bit

- 0 = 4 KB page size

- bit 3 CDMM: Common Device Memory Map bit

- 1 = CDMM is implemented

- bit 2-1 Unimplemented: Read as '0'

- bit 0 **TL:** Trace Logic bit

- 0 = Trace logic is not implemented

Note 1: These bits are set based on the value of the BOOTISA Configuration bit (DEVCFG0<6>).

# TABLE 4-19: SYSTEM BUS TARGET 11 REGISTER MAP

| SSS                         |                  |           |                  |       |       |          |          |       |       |      | Bits     |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|------------------|-------|-------|----------|----------|-------|-------|------|----------|-------|----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15            | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| AC20                        | SBT11ELOG1       | 31:16     | MULTI            | —     | —     | —        |          | CODE  | <3:0> |      | _        | —     |          |      | —      | —      | —       |        | 0000          |

| AC20                        | SBITTELOGI       | 15:0      |                  |       |       | INI      | ΓID<7:0> |       |       |      |          | REGIO | N<3:0>   |      | —      | C      | MD<2:0> |        | 0000          |

| AC24 S                      | SBT11ELOG2       | 31:16     | _                | -     | _     | —        | -        | -     | _     | -    | _        | -     |          |      | —      | -      | -       |        | 0000          |

| AC24                        | 3BTTTELOG2       | 15:0      | _                | -     | _     | —        | -        | -     | _     | -    | _        | -     |          |      | —      | -      | GROU    | P<1:0> | 0000          |

| AC28                        | SBT11ECON        | 31:16     | _                | -     | _     | —        | -        | -     | _     | ERRP | _        | -     |          |      | —      | -      | -       |        | 0000          |

| AC20                        | SBITTECON        | 15:0      | _                | -     | _     | —        | -        | -     | _     | -    | _        | -     |          |      | —      | -      | -       |        | 0000          |

| AC30                        | SBT11ECLRS       | 31:16     | —                | —     | —     | —        | _        | —     | —     | _    | _        | —     | _        | _    | —      | _      | —       | -      | 0000          |

| AC30                        | SBITTECERS       | 15:0      | —                | _     | —     | —        | —        | —     | —     | —    | _        | —     | _        | _    | —      | _      | —       | CLEAR  | 0000          |

| AC 38                       | 3 SBT11ECLRM     | 31:16     | —                | _     | —     | —        | —        | —     | —     | —    | _        | —     | _        | _    | —      | _      | —       | _      | 0000          |

| AC30                        |                  | 15:0      | —                | -     | _     | —        | _        | _     | —     | _    | _        | —     | _        | _    | _      | —      | —       | CLEAR  | 0000          |

| AC40                        | SBT11REG0        | 31:16     |                  |       |       |          |          |       |       | BA   | SE<21:6> |       |          |      |        | -      |         |        | xxxx          |

| 7040                        | SBITIKEGO        | 15:0      |                  | _     | BA    | ASE<5:0> | -        | -     | PRI   | —    |          | -     | SIZE<4:0 | >    |        | —      | —       |        | xxxx          |

| AC50                        | SBT11RD0         | 31:16     | —                | —     | _     | _        | _        | _     | —     | _    | _        | _     | _        | _    | _      | _      | _       | _      | xxxx          |

| 7030                        | 30111120         | 15:0      | —                | —     | _     | _        | _        | _     | —     | _    | _        | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC58                        | SBT11WR0         | 31:16     | —                | —     | —     | —        | —        | —     | —     | —    | —        | —     | _        |      | —      | —      | —       |        | xxxx          |

| //000                       | OBIIII           | 15:0      | —                | —     | —     | —        | —        | —     | —     | —    | —        | —     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC60                        | SBT11REG1        | 31:16     | 31:16 BASE<21:6> |       |       |          |          |       | xxxx  |      |          |       |          |      |        |        |         |        |               |

| /.000                       | OBTINEOT         | 15:0      |                  |       | BA    | ASE<5:0> |          |       | PRI   |      |          |       | SIZE<4:0 | >    |        | _      | _       | _      | xxxx          |

| AC70                        | SBT11RD1         | 31:16     | —                | —     | —     | —        | —        | —     | —     | —    | —        | —     | _        | _    | —      | —      | —       | —      | xxxx          |

|                             | 55111151         | 15:0      | —                | —     | —     | —        | —        | —     | —     | —    | —        | —     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC78                        | SBT11WR1         | 31:16     | —                | —     | —     | —        | —        | —     | —     | —    | —        | —     | _        | _    | —      | —      | —       | —      | xxxx          |

|                             | 021110101        | 15:0      | _                | —     | _     | —        | _        | _     | _     | _    | _        | _     | -        | -    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note:** For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|----------------------|-----------------------|-------------------|-------------------|------------------|------------------|

|              | U-0               | U-0                 | U-0                  | U-0                   | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 |                     | —                    | —                     |                   |                   | —                | —                |

| 00.40        | U-0               | U-0                 | U-0                  | U-0                   | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 |                     | _                    | —                     | _                 |                   | _                | _                |

| 45.0         | R/W-0, HC         | R/W-0               | R-0, HS, HC          | R-0, HS, HC           | U-0               | U-0               | U-0              | U-0              |

| 15:8         | WR <sup>(1)</sup> | WREN <sup>(1)</sup> | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | _                 |                   | _                | _                |

| 7.0          | R/W-0             | R/W-x               | U-0                  | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | PFSWAP            | BFSWAP              | —                    |                       |                   | NVMOP             | <3:0>            |                  |

# REGISTER 5-1: NVMCON: FLASH PROGRAMMING CONTROL REGISTER

| Legend:           | HC = Hardware Set | HC = Hardware Cleared              |                    |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

# bit 31-16 Unimplemented: Read as '0'

bit 15 WR: Write Control bit<sup>(1)</sup>

This bit cannot be cleared and can be set only when WREN = 1 and the unlock sequence has been performed.

- 1 = Initiate a Flash operation

- 0 = Flash operation is complete or inactive

#### bit 14 WREN: Write Enable bit<sup>(1)</sup>

- 1 = Enable writes to the WR bit and disables writes to the NVMOP<3:0> bits

- 0 = Disable writes to WR bit and enables writes to the NVMOP<3:0> bits

# bit 13 WRERR: Write Error bit<sup>(1)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation.

- 1 = Program or erase sequence did not complete successfully

- 0 = Program or erase sequence completed normally

# bit 12 LVDERR: Low-Voltage Detect Error bit<sup>(1)</sup>

This bit can be cleared only by setting the NVMOP<3:0> bits = 0000 and initiating a Flash operation. 1 = Low-voltage detected (possible data corruption, if WRERR is set)

0 =Voltage level is acceptable for programming

# bit 11-8 Unimplemented: Read as '0'

# bit 7 **PFSWAP:** Program Flash Bank Swap Control bit

This bit is only writable when WREN = 0 and the unlock sequence has been performed.

- 1 = Program Flash Bank 2 is mapped to the lower mapped region and program Flash Bank 1 is mapped to the upper mapped region

- 0 = Program Flash Bank 1 is mapped to the lower mapped region and program Flash Bank 2 is mapped to the upper mapped region

- Note 1: These bits are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

- 2: This operation results in a "no operation" (NOP) when the Dynamic Flash ECC Configuration bits = 00 (FECCCON<1:0> (DVCFG0<9:8>)), which enables ECC at all times. For all other FECCCON<1:0> bit settings, this command will execute, but will not write the ECC bits for the word and can cause DED errors if dynamic Flash ECC is enabled (FECCCON<1:0> = 01). Refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) for information regarding ECC and Flash programming.

# TABLE 7-2: INTERRUPT IRQ, VECTOR, AND BIT LOCATION (CONTINUED)

|                                 |                    | IRQ | Mastan #     |          | Interru  | upt Bit Location | n            | Persistent |

|---------------------------------|--------------------|-----|--------------|----------|----------|------------------|--------------|------------|

| Interrupt Source <sup>(1)</sup> | XC32 Vector Name   | #   | Vector #     | Flag     | Enable   | Priority         | Sub-priority | Interrupt  |

| ADC Digital Comparator 5        | _ADC_DC5_VECTOR    | 50  | OFF050<17:1> | IFS1<18> | IEC1<18> | IPC12<20:18>     | IPC12<17:16> | Yes        |

| ADC Digital Comparator 6        | _ADC_DC6_VECTOR    | 51  | OFF051<17:1> | IFS1<19> | IEC1<19> | IPC12<28:26>     | IPC12<25:24> | Yes        |

| ADC Digital Filter 1            | _ADC_DF1_VECTOR    | 52  | OFF052<17:1> | IFS1<20> | IEC1<20> | IPC13<4:2>       | IPC13<1:0>   | Yes        |

| ADC Digital Filter 2            | _ADC_DF2_VECTOR    | 53  | OFF053<17:1> | IFS1<21> | IEC1<21> | IPC13<12:10>     | IPC13<9:8>   | Yes        |

| ADC Digital Filter 3            | _ADC_DF3_VECTOR    | 54  | OFF054<17:1> | IFS1<22> | IEC1<22> | IPC13<20:18>     | IPC13<17:16> | Yes        |

| ADC Digital Filter 4            | _ADC_DF4_VECTOR    | 55  | OFF055<17:1> | IFS1<23> | IEC1<23> | IPC13<28:26>     | IPC13<25:24> | Yes        |

| ADC Digital Filter 5            | _ADC_DF5_VECTOR    | 56  | OFF056<17:1> | IFS1<24> | IEC1<24> | IPC14<4:2>       | IPC14<1:0>   | Yes        |

| ADC Digital Filter 6            | _ADC_DF6_VECTOR    | 57  | OFF057<17:1> | IFS1<25> | IEC1<25> | IPC14<12:10>     | IPC14<9:8>   | Yes        |

| ADC Fault                       | _ADC_FAULT_VECTOR  | 58  | OFF058<17:1> | IFS1<26> | IEC1<26> | IPC14<20:18>     | IPC14<17:16> | No         |

| ADC Data 0                      | _ADC_DATA0_VECTOR  | 59  | OFF059<17:1> | IFS1<27> | IEC1<27> | IPC14<28:26>     | IPC14<25:24> | Yes        |

| ADC Data 1                      | _ADC_DATA1_VECTOR  | 60  | OFF060<17:1> | IFS1<28> | IEC1<28> | IPC15<4:2>       | IPC15<1:0>   | Yes        |

| ADC Data 2                      | _ADC_DATA2_VECTOR  | 61  | OFF061<17:1> | IFS1<29> | IEC1<29> | IPC15<12:10>     | IPC15<9:8>   | Yes        |

| ADC Data 3                      | _ADC_DATA3_VECTOR  | 62  | OFF062<17:1> | IFS1<30> | IEC1<30> | IPC15<20:18>     | IPC15<17:16> | Yes        |

| ADC Data 4                      | _ADC_DATA4_VECTOR  | 63  | OFF063<17:1> | IFS1<31> | IEC1<31> | IPC15<28:26>     | IPC15<25:24> | Yes        |

| ADC Data 5                      | _ADC_DATA5_VECTOR  | 64  | OFF064<17:1> | IFS2<0>  | IEC2<0>  | IPC16<4:2>       | IPC16<1:0>   | Yes        |

| ADC Data 6                      | _ADC_DATA6_VECTOR  | 65  | OFF065<17:1> | IFS2<1>  | IEC2<1>  | IPC16<12:10>     | IPC16<9:8>   | Yes        |

| ADC Data 7                      | _ADC_DATA7_VECTOR  | 66  | OFF066<17:1> | IFS2<2>  | IEC2<2>  | IPC16<20:18>     | IPC16<17:16> | Yes        |

| ADC Data 8                      | _ADC_DATA8_VECTOR  | 67  | OFF067<17:1> | IFS2<3>  | IEC2<3>  | IPC16<28:26>     | IPC16<25:24> | Yes        |

| ADC Data 9                      | _ADC_DATA9_VECTOR  | 68  | OFF068<17:1> | IFS2<4>  | IEC2<4>  | IPC17<4:2>       | IPC17<1:0>   | Yes        |

| ADC Data 10                     | _ADC_DATA10_VECTOR | 69  | OFF069<17:1> | IFS2<5>  | IEC2<5>  | IPC17<12:10>     | IPC17<9:8>   | Yes        |

| ADC Data 11                     | _ADC_DATA11_VECTOR | 70  | OFF070<17:1> | IFS2<6>  | IEC2<6>  | IPC17<20:18>     | IPC17<17:16> | Yes        |

| ADC Data 12                     | _ADC_DATA12_VECTOR | 71  | OFF071<17:1> | IFS2<7>  | IEC2<7>  | IPC17<28:26>     | IPC17<25:24> | Yes        |

| ADC Data 13                     | _ADC_DATA13_VECTOR | 72  | OFF072<17:1> | IFS2<8>  | IEC2<8>  | IPC18<4:2>       | IPC18<1:0>   | Yes        |

| ADC Data 14                     | _ADC_DATA14_VECTOR | 73  | OFF073<17:1> | IFS2<9>  | IEC2<9>  | IPC18<12:10>     | IPC18<9:8>   | Yes        |

| ADC Data 15                     | _ADC_DATA15_VECTOR | 74  | OFF074<17:1> | IFS2<10> | IEC2<10> | IPC18<20:18>     | IPC18<17:16> | Yes        |

| ADC Data 16                     | _ADC_DATA16_VECTOR | 75  | OFF075<17:1> | IFS2<11> | IEC2<11> | IPC18<28:26>     | IPC18<25:24> | Yes        |

| ADC Data 17                     | _ADC_DATA17_VECTOR | 76  | OFF076<17:1> | IFS2<12> | IEC2<12> | IPC19<4:2>       | IPC19<1:0>   | Yes        |

| ADC Data 18                     | _ADC_DATA18_VECTOR | 77  | OFF077<17:1> | IFS2<13> | IEC2<13> | IPC19<12:10>     | IPC19<9:8>   | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

3: This interrupt source is not available on 100-pin devices.

4: This interrupt source is not available on 124-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS9             | IFS8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1             | IFS0             |

#### REGISTER 7-5: IFSx: INTERRUPT FLAG STATUS REGISTER

# Legend:

| 5                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-2 for the exact bit definitions.

# REGISTER 7-6: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

# Legend:

| 5                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IEC31-IEC0: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-2 for the exact bit definitions.

# TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

| ss                          |                                 |                         |             |       | / ///////////////////////////////////// |       |        | -     |      | Bit    |        | ,      |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-------------------------|-------------|-------|-----------------------------------------|-------|--------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range               | 31/15       | 30/14 | 29/13                                   | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 15B0                        | DCH7ECON                        | 7ECON 31:16 CHAIRQ<7:0> |             |       |                                         |       |        |       |      | 00FF   |        |        |        |        |        |        |        |        |            |

| 1300                        | DOINECON                        | 15:0                    |             |       |                                         | CHSIR | Q<7:0> |       | -    | -      | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | _      |        |        | FF00       |

| 15C0                        | DCH7INT                         | 31:16                   | —           | —     | —                                       | —     | —      | —     | —    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 1000                        |                                 | 15:0                    | —           | —     | —                                       | —     | —      | —     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 15D0                        | DCH7SSA                         | 31:16                   |             |       |                                         |       |        |       |      | CHSSA- | <31:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0                    |             |       |                                         |       |        |       |      |        |        |        |        |        |        |        |        |        | 0000       |

| 15E0                        | DCH7DSA                         | 31:16<br>15:0           | CHDSA<31.0> |       |                                         |       |        |       |      | 0000   |        |        |        |        |        |        |        |        |            |

|                             |                                 | 31:16                   | _           | _     | _                                       | _     | _      | _     | _    | _      | _      | _      | _      | _      | _      | _      | _      |        | 0000       |

| 15F0                        | DCH7SSIZ                        | 15:0                    |             |       |                                         |       |        |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16                   |             |       |                                         |       |        | _     |      |        |        |        |        |        | _      |        | _      |        | 0000       |

| 1600                        | DCH7DSIZ                        | 15:0                    |             |       |                                         |       |        |       |      | CHDSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1010                        | DCH7SPTR                        | 31:16                   | —           | _     | —                                       | _     | —      | —     | —    | —      | —      | —      | —      | —      | _      | —      | —      | _      | 0000       |

| 1010                        | DCHISPIR                        | 15:0                    |             |       |                                         |       |        |       |      | CHSPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1620                        | DCH7DPTR                        | 31:16                   | _           | -     |                                         | _     |        |       | _    | _      |        | _      | _      |        |        |        |        | _      | 0000       |

| 1020                        | DOINDEIR                        | 15:0                    |             |       |                                         |       |        |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1630                        | DCH7CSIZ                        | 31:16                   | —           | _     |                                         | _     |        |       | _    | -      |        | _      | —      |        |        |        |        | _      | 0000       |

| 1030                        | DOINCOIL                        | 15:0                    |             |       |                                         |       |        |       |      | CHCSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1640                        | DCH7CPTR                        | 31:16                   | —           | —     | —                                       | _     | —      | —     | —    | _      | _      | _      | _      | _      | _      | —      | -      | _      | 0000       |

| 1010                        |                                 | 15:0                    |             |       |                                         |       |        |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1650                        | DCH7DAT                         | 31:16                   |             | —     | —                                       | —     | —      | —     | —    | —      | —      | —      | _      | —      | —      | —      | —      |        | 0000       |

|                             |                                 | 15:0                    |             |       |                                         |       |        |       |      | CHPDAT | <15:0> |        |        |        |        |        |        |        | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

# REGISTER 11-11: USBIENCSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 1-7)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 31:24        |                   | RXFIFC            | )SZ<3:0>          |                   | TXFIFOSZ<3:0>     |                   |                  |                  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 10.0         | RXINTERV<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | SPEEI             | D<1:0>            | PROTO             | COL<1:0>          |                   | TEP               | <3:0>            |                  |  |

# Leaend:

| Logena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

# bit 31-28 RXFIFOSZ<3:0>: Receive FIFO Size bits

|           | 1111 = Reserved<br>1110 = Reserved<br>1101 = 8192 bytes                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|

|           | 1101 = 4096 bytes                                                                                                                  |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | 0011 = 8 bytes<br>0010 = Reserved<br>0001 = Reserved<br>0000 = Reserved or endpoint has not been configured                        |

|           | This register only has this interpretation when dynamic sizing is not selected. It is not valid where dynamic FIFO sizing is used. |

| bit 27-24 | TXFIFOSZ<3:0>: Transmit FIFO Size bits<br>1111 = Reserved<br>1110 = Reserved<br>1101 = 8192 bytes<br>1100 = 4096 bytes             |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | •                                                                                                                                  |

|           | 0011 = 8 bytes<br>0010 = Reserved<br>0001 = Reserved<br>0000 = Reserved or endpoint has not been configured                        |

|           |                                                                                                                                    |

This register only has this interpretation when dynamic sizing is not selected. It is not valid where dynamic

FIFO sizing is used.

# bit 23-16 Unimplemented: Read as '0'

# 15.0 DEADMAN TIMER (DMT)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

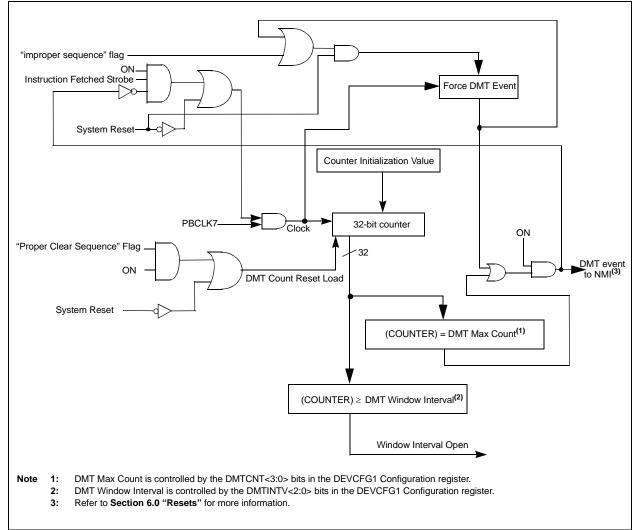

The primary function of the Deadman Timer (DMT) is to reset the processor in the event of a software malfunction. The DMT is a free-running instruction fetch timer, which is clocked whenever an instruction fetch occurs until a count match occurs. Instructions are not fetched when the processor is in Sleep mode. The DMT consists of a 32-bit counter with a time-out count match value as specified by the DMTCNT<3:0> bits in the DEVCFG1 Configuration register.

A Deadman Timer is typically used in mission critical and safety critical applications, where any single failure of the software functionality and sequencing must be detected.

Figure 15-1 shows a block diagram of the Deadman Timer module.

# FIGURE 15-1: DEADMAN TIMER BLOCK DIAGRAM

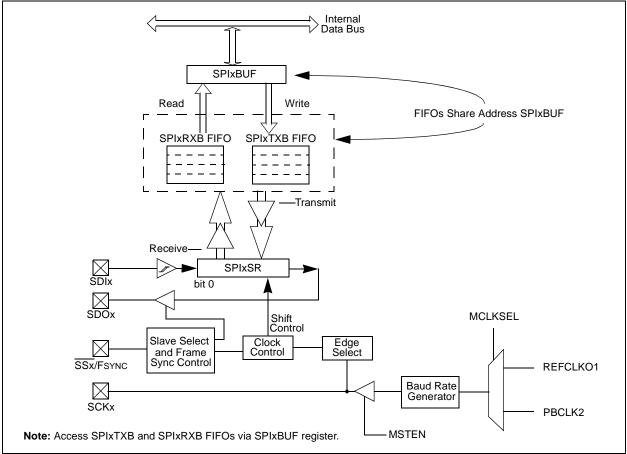

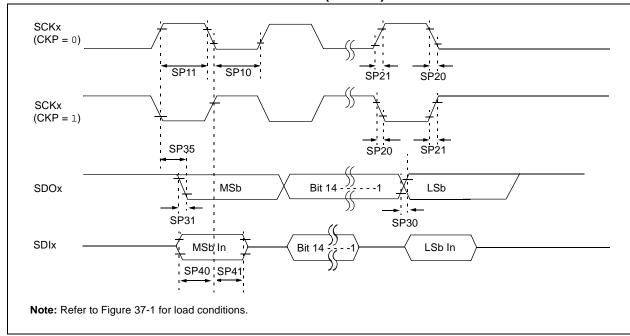

# 19.0 SERIAL PERIPHERAL INTERFACE (SPI) AND INTER-IC SOUND (I<sup>2</sup>S)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/ PIC32).

The SPI/I<sup>2</sup>S module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices, as well as digital audio devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, and so on.

The SPI/I<sup>2</sup>S module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The following are key features of the SPI module:

- Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

# FIGURE 19-1: SPI/I<sup>2</sup>S MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |  |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|--|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |  |

| 31.24        | —                    | —                 | -                 | —                 | —                        | —                 | _                | —                      |  |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |  |

| 23.10        | —                    | —                 | -                 | —                 | —                        | —                 | _                | —                      |  |