Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 46                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-QFN (9x9)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efg064t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                       |                                                                                                                                                                                      |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type        | Description                                                                                                                                                                          |  |

| VBUS     | 33                     | 51              | A35             | 73                       | I           | Analog                | USB bus power monitor                                                                                                                                                                |  |

| VUSB3V3  | 34                     | 52              | A36             | 74                       | Р           | _                     | USB internal transceiver supply. If the USB module is<br>not used, this pin must be connected to Vss. When<br>connected, the shared pin functions on USBID will not<br>be available. |  |

| D+       | 37                     | 55              | B30             | 77                       | I/O         | Analog                | USB D+                                                                                                                                                                               |  |

| D-       | 36                     | 54              | A37             | 76                       | I/O         | Analog                | USB D-                                                                                                                                                                               |  |

| USBID    | 38                     | 56              | A38             | 78                       | I           | ST                    | USB OTG ID detect                                                                                                                                                                    |  |

| Legend:  | CMOS = CI<br>ST = Schm | •               | •               | •                        |             | Analog =<br>O = Outpu | Analog input P = Power<br>ut I = Input                                                                                                                                               |  |

#### TABLE 1-14: **USB PINOUT I/O DESCRIPTIONS**

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output

PPS = Peripheral Pin Select

#### **TABLE 1-15**: **CAN1 AND CAN2 PINOUT I/O DESCRIPTIONS**

|          |                                                | Pin Nu          | mber            |                          |             |                |                        |  |

|----------|------------------------------------------------|-----------------|-----------------|--------------------------|-------------|----------------|------------------------|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP                         | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description            |  |

| C1TX     | PPS                                            | PPS             | PPS             | PPS                      | 0           | —              | CAN1 Bus Transmit Pin  |  |

| C1RX     | PPS                                            | PPS             | PPS             | PPS                      | I           | ST             | CAN1 Bus Receive Pin   |  |

| C2TX     | PPS                                            | PPS             | PPS             | PPS                      | 0           | _              | CAN2 Bus Transmit Pin  |  |

| C2RX     | PPS                                            | PPS             | PPS             | PPS                      | I           | ST             | CAN2 Bus Receive Pin   |  |

| Legend:  | CMOS = CI                                      | MOS-comp        | atible input    | or output                |             | Analog =       | Analog input P = Power |  |

|          | ST = Schm                                      | itt Trigger ir  | put with C      | MOS level                | S           | O = Outpu      | I = Input              |  |

|          | TTL = Transistor-transistor Logic input buffer |                 |                 |                          | er          | PPS = Pe       | ripheral Pin Select    |  |

# 2.4 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available from the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.5 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input voltage low (VIL) requirements.

# 2.6 Trace

The trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

# 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

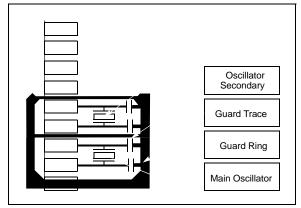

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

# TABLE 4-13: SYSTEM BUS TARGET 5 REGISTER MAP

| sse                         |                                                                                                                                                                                                                                                                                                                                      |           |               |       |       |          |       |       |       |        | Bits     |      |          |         |        |        |        |        |               |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|-------|-------|----------|-------|-------|-------|--------|----------|------|----------|---------|--------|--------|--------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name                                                                                                                                                                                                                                                                                                                     | Bit Range | 31/15         | 30/14 | 29/13 | 28/12    | 27/11 | 26/10 | 25/9  | 24/8   | 23/7     | 22/6 | 21/5     | 20/4    | 19/3   | 18/2   | 17/1   | 16/0   | All<br>Resets |

|                             |                                                                                                                                                                                                                                                                                                                                      | 31:16     | MULTI         | _     |       | _        |       | CODE  | <3:0> |        | _        |      | _        | _       | _      | _      | _      | _      | 0000          |

| 9420                        | SBI5ELOG1                                                                                                                                                                                                                                                                                                                            | 15:0      | 0 INITID<7:0> |       |       |          |       | •     | REGIO | N<3:0> | •        | —    | C        | MD<2:0> | •      | 0000   |        |        |               |

| 0424                        |                                                                                                                                                                                                                                                                                                                                      | 31:16     | _             | —     | _     | —        | _     | _     | _     | _      | _        | _    | _        | —       | _      | _      | —      | _      | 0000          |

| 9424                        | SBT5ELOG2       3         SBT5ECON       3         SBT5ECLRS       3         SBT5ECLRM       3         SBT5ECLRM       3         SBT5ECLRM       3         SBT5ECLRM       3         SBT5ECLRM       3         SBT5ECLRM       3         SBT5REG0       3         SBT5REG0       3         SBT5REG0       3         SBT5REG1       3 | 15:0      | _             | _     | _     | —        | _     | _     | _     | _      | _        | _    | _        | —       | _      | _      | GROU   | P<1:0> | 0000          |

| 0.400                       |                                                                                                                                                                                                                                                                                                                                      | 31:16     |               | _     | _     | _        | _     | _     | _     | ERRP   | -        | _    | _        | _       | _      | _      | —      | _      | 0000          |

| 9428                        | SBISECON                                                                                                                                                                                                                                                                                                                             | 15:0      | _             | —     | _     | _        | —     |       | _     | —      | _        |      | —        | _       | —      | _      | —      | —      | 0000          |

| 9430                        |                                                                                                                                                                                                                                                                                                                                      | 31:16     | -             | _     |       | —        | _     |       | _     | -      | _        |      | _        | _       | _      | _      | —      | -      | 0000          |

| 9430                        | SBISECLKS                                                                                                                                                                                                                                                                                                                            | 15:0      | -             | _     |       | —        | _     |       | _     | -      | _        |      | _        | _       | _      | _      | —      | CLEAR  | 0000          |

| 9438                        | SBT5ECL PM                                                                                                                                                                                                                                                                                                                           | 31:16     | _             | —     | _     | —        | —     | —     | —     | —      | _        | _    | —        | —       | —      | —      |        | —      | 0000          |

| 9430                        | SBISECERM                                                                                                                                                                                                                                                                                                                            | 15:0      | _             | —     | _     | _        | —     | _     | —     | _      | _        | _    |          | —       | —      | _      | —      | CLEAR  | 0000          |

| 9440                        | SBT5REGO                                                                                                                                                                                                                                                                                                                             | 31:16     |               |       |       |          |       |       |       | BA     | SE<21:6> |      |          |         |        |        |        |        | xxxx          |

| 3440                        | OBTOREOU                                                                                                                                                                                                                                                                                                                             | 15:0      |               | _     | BA    | ASE<5:0> | -     |       | PRI   | —      |          |      | SIZE<4:0 | >       | _      | —      |        | —      | xxxx          |

| 9450                        | SBT5RD0                                                                                                                                                                                                                                                                                                                              | 31:16     | —             | —     | _     | _        | _     |       | —     | _      | —        | _    |          | —       | —      | _      | —      | _      | xxxx          |

| 0 100                       | SBISKDU                                                                                                                                                                                                                                                                                                                              | 15:0      | —             | —     | —     | —        | —     | —     | —     | —      | —        | —    | —        | —       | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 9458                        | SBT5WR0                                                                                                                                                                                                                                                                                                                              | 31:16     | _             | —     | -     | —        | —     |       | —     | —      | —        |      | _        | —       | —      | _      | —      | —      | xxxx          |

| 0 100                       | obronnic                                                                                                                                                                                                                                                                                                                             | 15:0      | _             | —     | —     | —        | —     |       |       | —      | —        | _    | —        | —       | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 9460                        | SBT5REG1                                                                                                                                                                                                                                                                                                                             | 31:16     |               |       |       |          |       |       | 1     | BA     | SE<21:6> |      |          |         |        |        |        |        | xxxx          |

|                             |                                                                                                                                                                                                                                                                                                                                      | 15:0      |               |       | BA    | \SE<5:0> |       |       | PRI   | —      |          |      | SIZE<4:0 | >       |        | —      |        | —      | XXXX          |

| 9470                        | SBT5RD1                                                                                                                                                                                                                                                                                                                              | 31:16     | —             | _     |       | _        |       | _     | _     |        | _        | _    |          | _       | -      | _      |        | _      | XXXX          |

|                             |                                                                                                                                                                                                                                                                                                                                      | 15:0      | —             | —     |       | _        |       |       | _     |        | _        |      |          | _       | GROUP3 | GROUP2 | GROUP1 | GROUP0 | XXXX          |

| 9478                        | SBT5WR1                                                                                                                                                                                                                                                                                                                              | 31:16     | —             | —     |       | _        |       |       | _     |        | _        |      |          | _       | _      | _      |        |        | XXXX          |

|                             |                                                                                                                                                                                                                                                                                                                                      | 15:0      | —             | —     | —     | _        | —     |       |       | —      | _        | _    | —        | _       | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 9480                        | SBT5REG2                                                                                                                                                                                                                                                                                                                             | 31:16     |               |       |       |          |       |       |       | BA     | SE<21:6> |      |          |         |        |        |        |        | XXXX          |

|                             |                                                                                                                                                                                                                                                                                                                                      | 15:0      |               |       | BA    | ASE<5:0> |       |       | PRI   | —      |          |      | SIZE<4:0 | >       |        | —      |        | —      | XXXX          |

| 9490                        | SBT5RD2                                                                                                                                                                                                                                                                                                                              | 31:16     | _             | _     | —     | —        | —     |       | —     | —      | _        | —    | —        | —       | —      | —      | —      | —      | XXXX          |

|                             |                                                                                                                                                                                                                                                                                                                                      | 15:0      | _             | _     | —     | —        | —     |       | —     | —      | _        | —    | —        | —       | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 9498                        | SBT5WR2                                                                                                                                                                                                                                                                                                                              | 31:16     |               | _     | —     | —        | —     | _     |       | —      | _        | _    | —        | _       | —      | —      | —      | —      | XXXX          |

|                             |                                                                                                                                                                                                                                                                                                                                      | 15:0      | —             | —     | —     | —        | —     | —     | —     | —      | —        | —    | —        | _       | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

DS60001320D-page 82

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | -                 | -                 | —                 |                   | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | —                 |                   | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 |                   |                   | —                 |                   | _                | _                |

| 7.0          | U-0               | U-0               | R-0               | R-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          |                   | _                 | LPRCRDY           | SOSCRDY           |                   | POSCRDY           | DIVSPLLRDY       | FRCRDY           |

#### REGISTER 8-8: CLKSTAT: OSCILLATOR CLOCK STATUS REGISTER

### Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-6 Unimplemented: Read as '0'

- bit 5

LPRCRDY: Low-Power RC (LPRC) Oscillator Ready Status bit

1 = LPRC is stable and ready

0 = LPRC is disabled or not operating

bit 4

SOSCRDY: Secondary Oscillator (Sosc) Ready Status bit

1 = Sosc is stable and ready

- 0 = SOSC is disabled or not operating

- bit 3 Unimplemented: Read as '0'

- bit 2 **POSCRDY:** Primary Oscillator (Posc) Ready Status bit

- 1 = Posc is stable and ready

- 0 = Posc is disabled or not operating

- bit 1 DIVSPLLRDY: Divided System PLL Ready Status bit

- 1 = Divided System PLL is ready

- 0 = Divided System PLL is not ready

- bit 0 FRCRDY: Fast RC (FRC) Oscillator Ready Status bit

- 1 = FRC is stable and ready

- 0 = FRC is disabled for not operating

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | NRSTX            | NRST             |  |  |

| 00.40        | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-0             | R/W-1            | R/W-0            |  |  |

| 23:16        | LSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-1             | R/W-1            | R/W-1            |  |  |

| 15:8         | FSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R.W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | HSEOF<7:0>        |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 11-17: USBEOFRST: USB END-OF-FRAME/SOFT RESET CONTROL REGISTER

# Legend:

| 3                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-26 Unimplemented: Read as '0'

- bit 25 NRSTX: Reset of XCLK Domain bit

- 1 = Reset the XCLK domain, which is clock recovered from the received data by the PHY 0 = Normal operation

#### bit 24 NRST: Reset of CLK Domain bit

1 = Reset the CLK domain, which is clock recovered from the peripheral bus

0 = Normal operation

bit 23-16 LSEOF<7:0>: Low-Speed EOF bits These bits set the Low-Speed transaction in units of 1.067 μs (default setting is 121.6 μs) prior to the EOF to stop new transactions from beginning.

# bit 15-8 **FSEOF<7:0>:** Full-Speed EOF bits These bits set the Full-Speed transaction in units of 533.3 μs (default setting is 63.46 μs) prior to the EOF to stop new transactions from beginning.

#### bit 7-0 **HSEOF<7:0>:** Hi-Speed EOF bits These bits set the Hi-Speed transaction in units of 133.3 µs (default setting is 17.07µs) prior to the EOF to stop new transactions from beginning.

#### REGISTER 11-28: USBLPMR1: USB LINK POWER MANAGEMENT CONTROL REGISTER 1 (CONTINUED)

bit 16 LPMXMT: LPM Transition to the L1 State bit

# When in Device mode:

1 = USB module will transition to the L1 state upon the receipt of the next LPM transaction. LPMEN must be set to `0b11. Both LPMXMT and LPMEN must be set in the same cycle.

#### 0 = Maintain current state

When LPMXMT and LPMEN are set, the USB module can respond in the following ways:

- If no data is pending (all TX FIFOs are empty), the USB module will respond with an ACK. The bit will self clear and a software interrupt will be generated.

- If data is pending (data resides in at least one TX FIFO), the USB module will respond with a NYET. In this case, the bit will not self clear however a software interrupt will be generated.

#### When in Host mode:

- 1 = USB module will transmit an LPM transaction. This bit is self clearing, and will be immediately cleared upon receipt of any Token or three time-outs have occurred.

0 = Maintain current state

- bit 15-12 ENDPOINT<3:0>: LPM Token Packet Endpoint bits

- This is the endpoint in the token packet of the LPM transaction.

- bit 11-9 Unimplemented: Read as '0'

- bit 8 **RMTWAK:** Remote Wake-up Enable bit

This bit is applied on a temporary basis only and is only applied to the current suspend state.

- 1 = Remote wake-up is enabled

- 0 = Remote wake-up is disabled

- bit 7-4 HIRD<3:0>: Host Initiated Resume Duration bits

The minimum time the host will drive resume on the bus. The value in this register corresponds to an actual resume time of:

Resume Time = 50  $\mu$ s + HIRD \* 75  $\mu$ s. The resulting range is 50  $\mu$ s to 1200  $\mu$ s.

#### bit 3-0 LNKSTATE<3:0>: Link State bits

This value is provided by the host to the peripheral to indicate what state the peripheral must transition to after the receipt and acceptance of a LPM transaction. The only valid value for this register is '1' for Sleep State (L1). All other values are reserved.

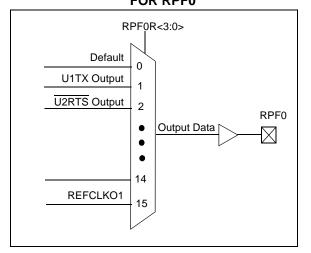

### 12.4.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 12-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 12-3 and Figure 12-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 12-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPF0

### 12.4.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32MZ EF devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

# 12.4.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators with Enhanced PLL"** in the *"PIC32 Family Reference Manual"* for details.

# 12.4.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOL0CK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

|              |                   | -                 | -                 |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | _                 | _                 | _                 | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                   | -                 |                   |                   | _                 |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | ?]R<3:0>         |                  |

#### **REGISTER 12-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|-------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 12-2 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

#### REGISTER 12-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | -                 | -                 |                   | _                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

# Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 12-3 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

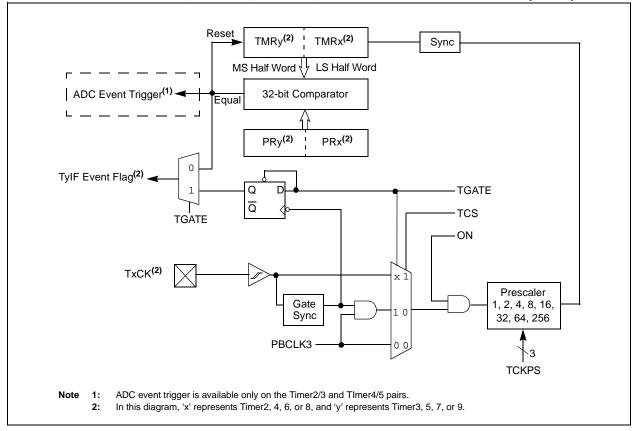

# FIGURE 14-2: TIMER2/3, TIMER4/5, TIMER6/7, AND TIMER8/9 BLOCK DIAGRAM (32-BIT)

# 15.1 Deadman Timer Control Registers

# TABLE 15-1: DEADMAN TIMER REGISTER MAP

| ess                         |                  | â         |               | _             | _     |       |        | _     | _    | _    | Bits         | _    | _        |      |        |      |      |        |            |

|-----------------------------|------------------|-----------|---------------|---------------|-------|-------|--------|-------|------|------|--------------|------|----------|------|--------|------|------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8 | 23/7         | 22/6 | 21/5     | 20/4 | 19/3   | 18/2 | 17/1 | 16/0   | All Resets |

| 0A00                        | DO DMTCON        | 31:16     | —             | —             | —     | —     | _      | —     | _    |      | —            | —    | —        | _    | —      | —    | —    | —      | 0000       |

| 0400                        |                  | 15:0      | ON            | _             | —     | _     |        | —     |      | _    | _            | _    | _        |      | —      | —    | _    | _      | x000       |

| 0410                        | DMTPRECLR        | 31:16     | _             | _             | —     | _     |        | —     | -    | _    | _            | _    | _        |      | —      | —    | _    | _      | 0000       |

| UATU                        |                  | 15:0      |               |               |       | STEP  | 1<7:0> |       |      |      | _            | _    | _        |      | —      | —    | _    | _      | 0000       |

| 0A20                        | DMTCLR           | 31:16     | —             | —             | —     | —     | _      | —     | _    | _    | —            | —    | —        | _    | —      | —    | —    | _      | 0000       |

| 0720                        | DIVITOEIX        | 15:0      | _             | _             | —     | —     | _      | —     | —    | _    |              |      |          | STEP | 2<7:0> |      |      |        | 0000       |

| 0A30                        | DMTSTAT          | 31:16     | —             | —             | —     | —     | _      | —     | —    | _    | —            | —    | —        | _    | —      | —    | —    | -      | 0000       |

| 07.00                       | DIMIGIAI         | 15:0      | —             | —             | —     | —     | _      | —     | —    | _    | BAD1         | BAD2 | DMTEVENT | _    | —      | —    | —    | WINOPN | 0000       |

| 0A40                        | DMTCNT           | 31:16     |               | COUNTER<31:0> |       |       |        |       |      |      |              |      |          |      |        |      |      |        |            |

| 0740                        | DIVITORI         | 15:0      |               |               |       |       |        |       |      | 000  |              | -0   |          |      |        |      |      |        | 0000       |

| 0A60                        | DMTPSCNT         | 31:16     | 6 PSCNT<31:0> |               |       |       |        |       |      | 0000 |              |      |          |      |        |      |      |        |            |

| 0700                        | Dimit Scivit     | 15:0      |               |               |       |       |        |       |      | 100  |              |      |          |      |        |      |      |        | 00xx       |

| 0A70                        | DMTPSINTV        | 31:16     |               |               |       |       |        |       |      | PSI  | NTV<31:0>    |      |          |      |        |      |      |        | 0000       |

|                             | DIVITESINT       | 15:0      |               |               |       |       |        |       |      | 1 31 | NT V \ 01.02 | -    |          |      |        |      |      |        | 000x       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4   | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------------|-------------------|--------------------|---------------------|---------------------|-------------------|------------------|------------------|

| 04.04        | U-0                     | U-0               | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | -                       | _                 | _                  | —                   | -                   |                   | —                | -                |

| 00.40        | R/W-0, HC               | U-0               | U-0                | U-0                 | U-0                 | U-0               | R/W-0            | U-0              |

| 23:16        | RDSTART                 | _                 | —                  | —                   | _                   | —                 | DUALBUF          | _                |

| 45.0         | R/W-0                   | U-0               | R/W-0              | R/W-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON                      | -                 | SIDL               | ADRML               | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0                   | R/W-0             | R/W-0              | R/W-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<1:0> <sup>(1)</sup> |                   | ALP <sup>(1)</sup> | CS2P <sup>(1)</sup> | CS1P <sup>(1)</sup> |                   | WRSP             | RDSP             |

#### REGISTER 23-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

bit 23 RDSTART: Start Read on PMP Bus bit This bit is cleared by hardware at the end of the read cycle. 1 = Start a read cycle on the PMP bus 0 = No effect

bit 22-18 Unimplemented: Read as '0'

bit 17 DUALBUF: Dual Read/Write Buffers enable bit

This bit is valid in Master mode only.

1 = PMP uses separate registers for reads and writes (PMRADDR, PMDATAIN, PMWADDR, PMDATAOUT)

0 = PMP uses legacy registers (PMADDR, PMDATA)

- bit 16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit

1 = PMP is enabled

- 0 = PMP is disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = Lower 8 bits of address are multiplexed on PMD<15:0> pins; upper 8 bits are not used

- 10 = All 16 bits of address are multiplexed on PMD<15:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port is enabled

- 0 = PMWR/PMENB port is disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port is enabled

- 0 = PMRD/PMWR port is disabled

**Note 1:** These bits have no effect when their corresponding pins are used as address lines.

|              |                   |                   | <u>т і т</u>      |                   |                   |                   | •                |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | CSADDR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CSADDR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | _                 | —                 | —                 | —                 | —                 | _                 | —                | —                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | _                 | —                 | —                 | —                 | —                 | _                 | —                | —                |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

# **REGISTER 24-1:** EBICSx: EXTERNAL BUS INTERFACE CHIP SELECT REGISTER ('x' = 0-3)

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 CSADDR<15:0>: Base Address for Device bits

Address in physical memory, which will select the external device.

bit 15-0 Unimplemented: Read as '0'

#### **RTCCON: REAL-TIME CLOCK AND CALENDAR CONTROL REGISTER** REGISTER 25-1:

| Bit<br>Range | Bit<br>31/23/15/7               | Bit<br>30/22/14/6           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0                |  |  |

|--------------|---------------------------------|-----------------------------|-------------------|-------------------|----------------------------|-------------------|------------------------|---------------------------------|--|--|

| 24.24        | U-0                             | U-0                         | U-0               | U-0               | U-0                        | U-0               | R/W-0                  | R/W-0                           |  |  |

| 31:24        | —                               | _                           | _                 | _                 | _                          | — CAL<            |                        | <9:8>                           |  |  |

| 00.40        | R/W-0                           | R/W-0                       | R/W-0             | R/W-0             | R/W-0                      | R/W-0             | R/W-0                  | R/W-0                           |  |  |

| 23:16        | CAL<7:0>                        |                             |                   |                   |                            |                   |                        |                                 |  |  |

|              | R/W-0                           | U-0                         | R/W-0             | U-0               | U-0                        | R/W-0             | R/W-0                  | R/W-0                           |  |  |

| 15:8         | ON <sup>(1)</sup>               | —                           | SIDL              | —                 |                            | RTCCLK            | (SEL<1:0>              | RTC<br>OUTSEL<1> <sup>(2)</sup> |  |  |

|              | R/W-0                           | R-0                         | U-0               | U-0               | R/W-0                      | R-0               | R-0                    | R/W-0                           |  |  |

| 7:0          | RTC<br>OUTSEL<0> <sup>(2)</sup> | RTC<br>CLKON <sup>(5)</sup> |                   |                   | RTC<br>WREN <sup>(3)</sup> | RTC<br>SYNC       | HALFSEC <sup>(4)</sup> | RTCOE                           |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: Real-Time Clock Drift Calibration bits, which contain a signed 10-bit integer value 0111111111 = Maximum positive adjustment, adds 511 real-time clock pulses every one minute 000000001 = Minimum positive adjustment, adds 1 real-time clock pulse every one minute 000000000 = No adjustment 1111111111 = Minimum negative adjustment, subtracts 1 real-time clock pulse every one minute 1000000000 = Maximum negative adjustment, subtracts 512 real-time clock pulses every one minute ON: RTCC On bit<sup>(1)</sup> bit 15 1 = RTCC module is enabled 0 = RTCC module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Stop in Idle Mode bit 1 = Disables RTCC operation when CPU enters Idle mode 0 = Continue normal operation when CPU enters Idle mode bit 12-11 Unimplemented: Read as '0' **Note 1:** The ON bit is only writable when RTCWREN = 1.

- **2:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 3: The RTCWREN bit can be set only when the write sequence is enabled.

- 4: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

- 5: This bit is undefined when RTCCLKSEL < 1:0 > = 00 (LPRC is the clock source).

#### Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                 | —                 | —                 | _                 | -                | —                |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   | MONT              | H10<3:0>          |                   | MONTH01<3:0>      |                   |                  |                  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   | DAY               | 10<1:0>           |                   | DAY01<3:0>        |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0          |                   |                   | _                 | _                 |                   | WDAY0             | 1<3:0>           |                  |  |

### REGISTER 25-6: ALRMDATE: ALARM DATE VALUE REGISTER

# Legend:

| Legenu.           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

٦

| Bit Range | Bit<br>31/23/15/7                   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04-04     | R-0, HS, HC                         | R-0, HS, HC       | R-0, HS, HC       | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24     | BGVRRDY REFFLT EOSRDY CVDCPL<2:0>   |                   |                   |                   |                   |                   | SAMC<9:8>        |                  |  |  |

| 00.40     | R/W-0                               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16     | SAMC<7:0>                           |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0      | R/W-0                               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | BGVRIEN REFFLTIEN EOSIEN ADCEIOVR — |                   |                   |                   |                   |                   | ADCEIS<2:0>      |                  |  |  |

| 7.0       | U-0                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | —                                   |                   |                   | AD                | CDIV<6:0>         |                   |                  |                  |  |  |

### REGISTER 28-2: ADCCON2: ADC CONTROL REGISTER 2

| Legend:           | HC = Hardware Set | HS = Hardware Cleared r = Reserved      |

|-------------------|-------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared x = Bit is unknown |

bit 31 BGVRRDY: Band Gap Voltage/ADC Reference Voltage Status bit 1 = Both band gap voltage and ADC reference voltages (VREF) are ready 0 = Either or both band gap voltage and ADC reference voltages (VREF) are not ready Data processing is valid only after BGVRRDY is set by hardware, so the application code must check that the BGVRRDY bit is set to ensure data validity. This bit set to '0' when ON (ADCCON1<15>) = 0. bit 30 **REFFLT:** Band Gap/VREF/AVDD BOR Fault Status bit 1 = Fault in band gap or the VREF voltage while the ON bit (ADCCON1<15>) was set. Most likely a band gap or VREF fault will be caused by a BOR of the analog VDD supply. 0 = Band gap and VREF voltage are working properly This bit is cleared when the ON bit (ADCCON1<15>) = 0 and the BGVRRDY bit = 1. bit 29 EOSRDY: End of Scan Interrupt Status bit 1 = All analog inputs are considered for scanning through the scan trigger (all analog inputs specified in the ADCCSS1 and ADCCSS2 registers) have completed scanning 0 = Scanning has not completed This bit is cleared when ADCCON2<31:24> are read in software. bit 28-26 CVDCPL<2:0>: Capacitor Voltage Divider (CVD) Setting bit 111 = 7 \* 2.5 pF = 17.5 pF 110 = 6 \* 2.5 pF = 15 pF 101 = 5 \* 2.5 pF = 12.5 pF 100 = 4 \* 2.5 pF = 10 pF 011 = 3 \* 2.5 pF = 7.5 pF 010 = 2 \* 2.5 pF = 5 pF 001 = 1 \* 2.5 pF = 2.5 pF 000 = 0 \* 2.5 pF = 0 pFbit 25-16 SAMC<9:0>: Sample Time for the Shared ADC (ADC7) bits 1111111111 = 1025 TAD7 000000001 = 3 TAD7 0000000000 = 2 TAD7 Where TAD7 = period of the ADC conversion clock for the Shared ADC (ADC7) controlled by the ADCDIV<6:0> bits. bit 15 BGVRIEN: Band Gap/VREF Voltage Ready Interrupt Enable bit 1 = Interrupt will be generated when the BGVRDDY bit is set 0 = No interrupt is generated when the BGVRRDY bit is set

| REGISTER | R 28-5: ADCIMCON1: ADC INPUT MODE CONTROL REGISTER 1 (CONTINUED) |

|----------|------------------------------------------------------------------|

| bit 20   | SIGN10: AN10 Signed Data Mode bit                                |

|          | 1 = AN10 is using Signed Data mode                               |

|          | 0 = AN10 is using Unsigned Data mode                             |

| bit 19   | DIFF9: AN9 Mode bit                                              |

| 2.1.10   | 1 = AN9 is using Differential mode                               |

|          | 0 = AN9 is using Single-ended mode                               |

| bit 18   | SIGN9: AN9 Signed Data Mode bit                                  |

| DIL TO   | 1 = AN9 is using Signed Data mode                                |

|          | 0 = AN9 is using Unsigned Data mode                              |

| bit 17   | DIFF8: AN 8 Mode bit                                             |

|          | 1 = AN8 is using Differential mode                               |

|          | 0 = AN8 is using Single-ended mode                               |

| bit 16   | SIGN8: AN8 Signed Data Mode bit                                  |

| DICTO    | •                                                                |

|          | 1 = AN8 is using Signed Data mode                                |

| 1.1.4.F  | 0 = AN8 is using Unsigned Data mode                              |

| bit 15   | DIFF7: AN7 Mode bit                                              |

|          | 1 = AN7 is using Differential mode                               |

| 1.1.4.4  | 0 = AN7 is using Single-ended mode                               |

| bit 14   | SIGN7: AN7 Signed Data Mode bit                                  |

|          | 1 = AN7 is using Signed Data mode                                |

| 1.1.40   | 0 = AN7 is using Unsigned Data mode                              |

| bit 13   | DIFF6: AN6 Mode bit                                              |

|          | 1 = AN6 is using Differential mode                               |

| 1.1.40   | 0 = AN6 is using Single-ended mode                               |

| bit 12   | SIGN6: AN6 Signed Data Mode bit                                  |

|          | 1 = AN6 is using Signed Data mode                                |

|          | 0 = AN6 is using Unsigned Data mode                              |

| bit 11   | DIFF5: AN5 Mode bit                                              |

|          | 1 = AN5 is using Differential mode                               |

| 1.1.40   | 0 = AN5 is using Single-ended mode                               |

| bit 10   | SIGN5: AN5 Signed Data Mode bit                                  |

|          | 1 = AN5 is using Signed Data mode                                |

|          | 0 = AN5 is using Unsigned Data mode                              |

| bit 9    | DIFF4: AN4 Mode bit                                              |

|          | 1 = AN4 is using Differential mode                               |

|          | 0 = AN4 is using Single-ended mode                               |

| bit 8    | SIGN4: AN4 Signed Data Mode bit                                  |

|          | 1 = AN4 is using Signed Data mode                                |

|          | 0 = AN4 is using Unsigned Data mode                              |

| bit 7    | DIFF3: AN3 Mode bit                                              |

|          | 1 = AN3 is using Differential mode                               |

|          | 0 = AN3 is using Single-ended mode                               |

| bit 6    | SIGN3: AN3 Signed Data Mode bit                                  |

|          | 1 = AN3 is using Signed Data mode                                |

|          | 0 = AN3 is using Unsigned Data mode                              |

| bit 5    | DIFF2: AN2 Mode bit                                              |

|          | 1 = AN2 is using Differential mode                               |

|          | 0 = AN2 is using Single-ended mode                               |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 |                   | -                 |                   |                   | —                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

|              | _                 | B2BIPKTGP<6:0>    |                   |                   |                   |                   |                  |                  |

### REGISTER 30-25: EMAC1IPGT: ETHERNET CONTROLLER MAC BACK-TO-BACK INTERPACKET GAP REGISTER

#### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-7 Unimplemented: Read as '0'

#### bit 6-0 B2BIPKTGP<6:0>: Back-to-Back Interpacket Gap bits

This is a programmable field representing the nibble time offset of the minimum possible period between the end of any transmitted packet, to the beginning of the next. In Full-Duplex mode, the register value should be the desired period in nibble times minus 3. In Half-Duplex mode, the register value should be the desired period in nibble times minus 6. In Full-Duplex the recommended setting is 0x15 (21d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps). In Half-Duplex mode, the recommended setting is 0x12 (18d), which also represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps).

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

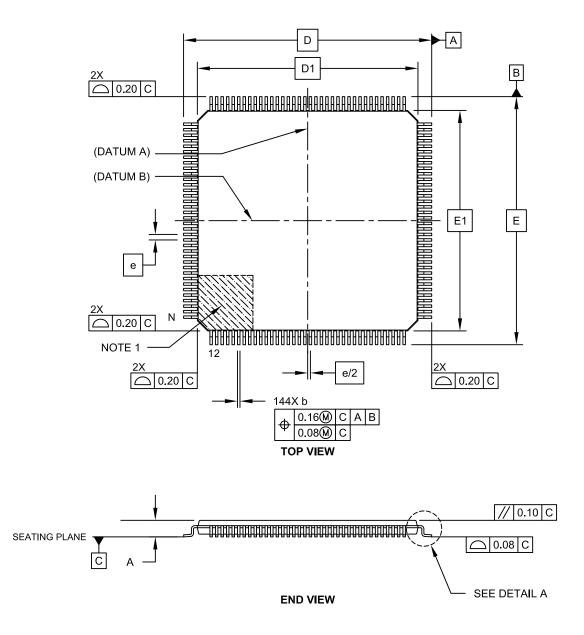

# 144-Lead Plastic Thin Quad Flatpack (PH)-16x16x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-155B Sheet 1 of 2