Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 46                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efg064t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note 1: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

# 2.1 Basic Connection Requirements

Getting started with the PIC32MZ EF family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- MCLR pin (see 2.3 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **2.4** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

Note: The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

# TABLE 4-13: SYSTEM BUS TARGET 5 REGISTER MAP

| sse                         |                  |           |       |       |       |          |          |       |       |      | Bits     |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|----------|-------|----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             |                  | 31:16     | MULTI | _     |       | _        |          | CODE  | <3:0> |      | _        |       | _        | _    | _      | _      | _       | _      | 0000          |

| 9420                        | SBT5ELOG1        | 15:0      |       |       |       | INI      | ΓID<7:0> |       |       |      | •        | REGIO | N<3:0>   | •    | —      | C      | MD<2:0> | •      | 0000          |

| 0424                        | SBT5ELOG2        | 31:16     | _     | —     | _     | —        | _        | _     | _     | _    | _        | _     | _        | —    | _      | _      | —       | _      | 0000          |

| 9424                        | SB15ELUG2        | 15:0      | _     | _     | _     | —        | _        | _     | _     | _    | _        | _     | _        | —    | _      | _      | GROU    | P<1:0> | 0000          |

| 0.400                       | SBT5ECON         | 31:16     |       | _     | _     | _        | _        | _     | _     | ERRP | -        | _     | _        | _    | _      | _      | —       | _      | 0000          |

| 9428                        | SBISECON         | 15:0      | _     | —     | _     | _        | —        |       | _     | —    | _        |       | —        | _    | —      | _      | —       | —      | 0000          |

| 9430                        | SBT5ECLRS        | 31:16     | _     | _     |       | —        | _        |       | _     | -    | _        |       | _        | _    | _      | _      | —       |        | 0000          |

| 9430                        | SBISECLKS        | 15:0      | _     | _     |       | —        | _        |       | _     | -    | _        |       | _        | _    | _      | _      | —       | CLEAR  | 0000          |

| 9438                        | SBT5ECLRM        | 31:16     | _     | —     | _     | —        | —        | —     | —     | —    | _        | _     | —        | —    | —      | —      |         | —      | 0000          |

| 9430                        | SBISECERM        | 15:0      | _     | —     | _     | _        | —        | _     | —     | _    | _        | _     |          | —    | —      | _      | —       | CLEAR  | 0000          |

| 9440                        | SBT5REG0         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |          |      |        |        |         |        | xxxx          |

| 3440                        | OBTOREOU         | 15:0      |       | _     | BA    | ASE<5:0> | -        |       | PRI   | —    |          |       | SIZE<4:0 | >    | _      | —      |         | —      | xxxx          |

| 9450                        | SBT5RD0          | 31:16     | —     | —     | _     | _        | _        |       | —     | _    | —        | _     |          | —    | —      | _      | —       | _      | xxxx          |

| 0 100                       | OBTORES          | 15:0      | —     | —     | —     | —        | —        | —     | —     | —    | —        | —     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9458                        | SBT5WR0          | 31:16     | _     | —     | -     | —        | —        |       | —     | —    | —        |       | —        | —    | —      | _      | —       | —      | xxxx          |

| 0 100                       | obronnic         | 15:0      | _     | —     | —     | —        | —        |       |       | —    | —        | _     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9460                        | SBT5REG1         | 31:16     |       |       |       |          |          |       | 1     | BA   | SE<21:6> |       |          |      |        |        |         |        | xxxx          |

|                             |                  | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | —    |          |       | SIZE<4:0 | >    |        | —      |         | —      | XXXX          |

| 9470                        | SBT5RD1          | 31:16     | —     | _     |       | _        |          | _     | _     |      | _        | _     |          | _    | -      | _      |         | _      | XXXX          |

|                             |                  | 15:0      | —     | —     |       | _        |          |       | _     |      | _        |       |          | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | XXXX          |

| 9478                        | SBT5WR1          | 31:16     | —     | —     |       | _        |          |       | _     |      | _        |       |          | _    | _      | _      |         |        | XXXX          |

|                             |                  | 15:0      | —     | —     | —     | _        | —        |       |       | —    | _        | _     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9480                        | SBT5REG2         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6> |       |          |      |        |        |         |        | XXXX          |

|                             |                  | 15:0      |       |       | BA    | ASE<5:0> |          |       | PRI   | —    |          |       | SIZE<4:0 | >    |        | —      |         | —      | XXXX          |

| 9490                        | SBT5RD2          | 31:16     | _     | _     | —     | —        | —        | —     | —     | —    | _        | —     | —        | —    | —      | —      | —       | —      | XXXX          |

|                             |                  | 15:0      | _     | _     | —     | —        | —        | —     | —     | —    | _        | —     | —        | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9498                        | SBT5WR2          | 31:16     |       | _     | —     | —        | —        | _     |       | —    | _        | _     | —        | _    | —      | —      | —       | —      | XXXX          |

|                             |                  | 15:0      | —     | —     | —     | —        | —        | —     | —     | —    | —        | —     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

DS60001320D-page 82

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| (1)                             | XODO Vester Nerre             | IRQ |              |          | Interru  | pt Bit Locatior | n            | Persistent |

|---------------------------------|-------------------------------|-----|--------------|----------|----------|-----------------|--------------|------------|

| Interrupt Source <sup>(1)</sup> | XC32 Vector Name              | #   | Vector #     | Flag     | Enable   | Priority        | Sub-priority | Interrupt  |

| Output Compare 4                | _OUTPUT_COMPARE_4_VECTOR      | 22  | OFF022<17:1> | IFS0<22> | IEC0<22> | IPC5<20:18>     | IPC5<17:16>  | No         |

| External Interrupt 4            | _EXTERNAL_4_VECTOR            | 23  | OFF023<17:1> | IFS0<23> | IEC0<23> | IPC5<28:26>     | IPC5<25:24>  | No         |

| Timer5                          | _TIMER_5_VECTOR               | 24  | OFF024<17:1> | IFS0<24> | IEC0<24> | IPC6<4:2>       | IPC6<1:0>    | No         |

| Input Capture 5 Error           | _INPUT_CAPTURE_5_ERROR_VECTOR | 25  | OFF025<17:1> | IFS0<25> | IEC0<25> | IPC6<12:10>     | IPC6<9:8>    | Yes        |

| Input Capture 5                 | _INPUT_CAPTURE_5_VECTOR       | 26  | OFF026<17:1> | IFS0<26> | IEC0<26> | IPC6<20:18>     | IPC6<17:16>  | Yes        |

| Output Compare 5                | _OUTPUT_COMPARE_5_VECTOR      | 27  | OFF027<17:1> | IFS0<27> | IEC0<27> | IPC6<28:26>     | IPC6<25:24>  | No         |

| Timer6                          | _TIMER_6_VECTOR               | 28  | OFF028<17:1> | IFS0<28> | IEC0<28> | IPC7<4:2>       | IPC7<1:0>    | No         |

| Input Capture 6 Error           | _INPUT_CAPTURE_6_ERROR_VECTOR | 29  | OFF029<17:1> | IFS0<29> | IEC0<29> | IPC7<12:10>     | IPC7<9:8>    | Yes        |

| Input Capture 6                 | _INPUT_CAPTURE_6_VECTOR       | 30  | OFF030<17:1> | IFS0<30> | IEC0<30> | IPC7<20:18>     | IPC7<17:16>  | Yes        |

| Output Compare 6                | _OUTPUT_COMPARE_6_VECTOR      | 31  | OFF031<17:1> | IFS0<31> | IEC0<31> | IPC7<28:26>     | IPC7<25:24>  | No         |

| Timer7                          | _TIMER_7_VECTOR               | 32  | OFF032<17:1> | IFS1<0>  | IEC1<0>  | IPC8<4:2>       | IPC8<1:0>    | No         |

| Input Capture 7 Error           | _INPUT_CAPTURE_7_ERROR_VECTOR | 33  | OFF033<17:1> | IFS1<1>  | IEC1<1>  | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| Input Capture 7                 | _INPUT_CAPTURE_7_VECTOR       | 34  | OFF034<17:1> | IFS1<2>  | IEC1<2>  | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| Output Compare 7                | _OUTPUT_COMPARE_7_VECTOR      | 35  | OFF035<17:1> | IFS1<3>  | IEC1<3>  | IPC8<28:26>     | IPC8<25:24>  | No         |

| Timer8                          | _TIMER_8_VECTOR               | 36  | OFF036<17:1> | IFS1<4>  | IEC1<4>  | IPC9<4:2>       | IPC9<1:0>    | No         |

| Input Capture 8 Error           | _INPUT_CAPTURE_8_ERROR_VECTOR | 37  | OFF037<17:1> | IFS1<5>  | IEC1<5>  | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| Input Capture 8                 | _INPUT_CAPTURE_8_VECTOR       | 38  | OFF038<17:1> | IFS1<6>  | IEC1<6>  | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| Output Compare 8                | _OUTPUT_COMPARE_8_VECTOR      | 39  | OFF039<17:1> | IFS1<7>  | IEC1<7>  | IPC9<28:26>     | IPC9<25:24>  | No         |

| Timer9                          | _TIMER_9_VECTOR               | 40  | OFF040<17:1> | IFS1<8>  | IEC1<8>  | IPC10<4:2>      | IPC10<1:0>   | No         |

| Input Capture 9 Error           | _INPUT_CAPTURE_9_ERROR_VECTOR | 41  | OFF041<17:1> | IFS1<9>  | IEC1<9>  | IPC10<12:10>    | IPC10<9:8>   | Yes        |

| Input Capture 9                 | _INPUT_CAPTURE_9_VECTOR       | 42  | OFF042<17:1> | IFS1<10> | IEC1<10> | IPC10<20:18>    | IPC10<17:16> | Yes        |

| Output Compare 9                | _OUTPUT_COMPARE_9_VECTOR      | 43  | OFF043<17:1> | IFS1<11> | IEC1<11> | IPC10<28:26>    | IPC10<25:24> | No         |

| ADC Global Interrupt            | _ADC_VECTOR                   | 44  | OFF044<17:1> | IFS1<12> | IEC1<12> | IPC11<4:2>      | IPC11<1:0>   | Yes        |

| ADC FIFO Data Ready Interrupt   | _ADC_FIFO_VECTOR              | 45  | OFF045<17:1> | IFS1<13> | IEC1<13> | IPC11<12:10>    | IPC11<9:8>   | Yes        |

| ADC Digital Comparator 1        | _ADC_DC1_VECTOR               | 46  | OFF046<17:1> | IFS1<14> | IEC1<14> | IPC11<20:18>    | IPC11<17:16> | Yes        |

| ADC Digital Comparator 2        | _ADC_DC2_VECTOR               | 47  | OFF047<17:1> | IFS1<15> | IEC1<15> | IPC11<28:26>    | IPC11<25:24> | Yes        |

| ADC Digital Comparator 3        | _ADC_DC3_VECTOR               | 48  | OFF048<17:1> | IFS1<16> | IEC1<16> | IPC12<4:2>      | IPC12<1:0>   | Yes        |

| ADC Digital Comparator 4        | _ADC_DC4_VECTOR               | 49  | OFF049<17:1> | IFS1<17> | IEC1<17> | IPC12<12:10>    | IPC12<9:8>   | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the list of available peripherals.

2: This interrupt source is not available on 64-pin devices.

3: This interrupt source is not available on 100-pin devices.

4: This interrupt source is not available on 124-pin devices.

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>f)                  | <b>N</b> -                      | Ð         |       |       |       |       |       |       |      | Bi         | s    |      |      |      |      |      |       |         | Ś          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|---------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0    | All Resets |

|                             | 055077(2)                       | 31:16     | _     | _     | _     | _     |       | —     | —    | _          | _    | _    | _    | _    | _    | _    | VOFF. | :17:16> | 0000       |

| 0674                        | OFF077 <sup>(2)</sup>           | 15:0      |       |       |       |       |       | •     | •    | VOFF<15:1> |      |      | •    |      |      | •    | •     | —       | 0000       |

| 0670                        | OFF078 <sup>(2)</sup>           | 31:16     | _     | _     | _     | _     | —     | —     | _    | _          | _    | _    | -    | _    | _    | _    | VOFF. | :17:16> | 0000       |

| 0070                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0670                        | OFF079 <sup>(2)</sup>           | 31:16     | _     | —     | —     | —     | _     | —     | _    | _          | _    | -    | —    | _    | —    | _    | VOFF. | :17:16> | 0000       |

| 0070                        | 011073.7                        | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      | -    |      |      | -    | -     | —       | 0000       |

| 0880                        | OFF080 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | _     | —     | —    | —          | _    | —    | —    | —    | —    |      | VOFF. | :17:16> | 0000       |

| 0000                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0684                        | OFF081 <sup>(2)</sup>           | 31:16     | —     | —     | _     | —     | —     | —     |      | —          | —    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

| 0004                        | 011001                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      | •    |      |      |      |       | —       | 0000       |

| 0688                        | OFF082 <sup>(2)</sup>           | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

| 0000                        | 011002                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0680                        | OFF083 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | _     | —     | _    | —          | _    | —    | —    | —    | —    |      | VOFF. | :17:16> | 0000       |

| 0000                        | 011005                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0690                        | OFF084 <sup>(2)</sup>           | 31:16     | —     | —     | _     | —     | —     | —     |      | —          | —    | —    | —    | —    | —    | _    | VOFF. | :17:16> | 0000       |

| 0000                        | 011004                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0694                        | OFF085 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    |            | _    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

| 0004                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      | -    |      |      |      |       |         | 0000       |

| 0698                        | OFF086 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    |            | _    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

|                             | 0.1000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0690                        | OFF087 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

|                             | 0.1.001                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      | -    |      |      |      |       |         | 0000       |

| 06A0                        | OFF088 <sup>(2)</sup>           | 31:16     | _     | —     | -     | —     | _     | —     | —    | —          | _    | —    | -    | —    | —    | —    | VOFF. | :17:16> | 0000       |

| 00,10                       | 0.1000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 06A4                        | OFF089 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | -    | —    | -    | —    | —    | —    | VOFF. | :17:16> | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 06A8                        | OFF090 <sup>(2)</sup>           | 31:16     | _     | —     | —     | —     | —     | —     | —    | _          | _    | —    | —    | —    | —    | _    | VOFF. | :17:16> | 0000       |

| 00/10                       | 0.7000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0640                        | OFF091 <sup>(2)</sup>           | 31:16     | _     | —     | -     | —     | —     | —     | —    | —          | _    | —    | —    | —    | —    | —    | VOFF. | :17:16> | 0000       |

|                             | 011001                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

DS60001320D-page 136

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

3: This bit or register is not available on devices without a CAN module.

4: This bit or register is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | —                 | _                 | -                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 |                   | —                 |                   |                  | —                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   | _                 | _                 |                   |                  | _                |

#### REGISTER 10-1: DMACON: DMA CONTROLLER CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** DMA On bit

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 Unimplemented: Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

- bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active and is transferring data

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

# REGISTER 10-9: DCHxINT: DMA CHANNEL x INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

# bit 31-24 Unimplemented: Read as '0'

| bit 23   | CHSDIE: Channel Source Done Interrupt Enable bit                                        |

|----------|-----------------------------------------------------------------------------------------|

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 22   | CHSHIE: Channel Source Half Empty Interrupt Enable bit                                  |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 21   | CHDDIE: Channel Destination Done Interrupt Enable bit                                   |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 20   | CHDHIE: Channel Destination Half Full Interrupt Enable bit                              |

|          | 1 = Interrupt is enabled                                                                |

| 1.11.40  | 0 = Interrupt is disabled                                                               |

| bit 19   | CHBCIE: Channel Block Transfer Complete Interrupt Enable bit                            |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>         |

| bit 18   |                                                                                         |

| DIL TO   | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled |

|          | 0 = Interrupt is disabled                                                               |

| bit 17   | CHTAIE: Channel Transfer Abort Interrupt Enable bit                                     |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 16   | CHERIE: Channel Address Error Interrupt Enable bit                                      |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 15-8 | Unimplemented: Read as '0'                                                              |

| bit 7    | CHSDIF: Channel Source Done Interrupt Flag bit                                          |

|          | 1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)                  |

|          | 0 = No interrupt is pending                                                             |

| bit 6    | CHSHIF: Channel Source Half Empty Interrupt Flag bit                                    |

|          | 1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)           |

|          | 0 = No interrupt is pending                                                             |

|          |                                                                                         |

# TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| ŝ        |                  |               |       |                                            |       |       |           |       |      |             | Bits            |                                         |  |      |           |    |  |      |            |

|----------|------------------|---------------|-------|--------------------------------------------|-------|-------|-----------|-------|------|-------------|-----------------|-----------------------------------------|--|------|-----------|----|--|------|------------|

| (BF8E_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                                      | 29/13 | 28/12 | 27/11     | 26/10 | 25/9 | 24/8        | 23/7            | 13/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 |  |      |           |    |  | 16/0 | All Recete |

|          | USB              | 31:16         | _     | RXHUBPRT<6:0> MULTTRAN RXHUBADD<6:0>       |       |       |           |       |      |             |                 |                                         |  |      |           | 00 |  |      |            |

| 09C      | E3RXA            | 15:0          |       | <u>− − − − − − − RXFADDR&lt;6:0&gt;</u> 00 |       |       |           |       |      |             |                 |                                         |  |      |           |    |  |      |            |

| 0A0      | US               | 31:16         | 1     |                                            |       | ТХ    | HUBPRT<6  | :0>   | -    | -           | MULTTRAN        |                                         |  | TXHU | BADD<6:0> |    |  |      | 0 0        |

|          | BE4TXA           | 15:0          | -     | _                                          |       |       |           |       |      |             |                 |                                         |  |      | 00        |    |  |      |            |

| 0A4      | USB              | 31:16         | _     |                                            |       | RX    | HUBPRT<6  | :0>   |      | 1           | MULTTRAN        |                                         |  |      | BADD<6:0> |    |  |      | 00         |

|          | E4RXA            | 15:0          | _     | -                                          | -     | —     | —         |       | -    | -           | —               |                                         |  |      | DDR<6:0>  |    |  |      | 00         |

| 0A8      | USB              | 31:16         | —     |                                            |       |       | HUBPRT<6  |       |      | -           | MULTTRAN        |                                         |  |      | BADD<6:0> |    |  |      | 00         |

|          | E5TXA            | 15:0          | _     | -                                          | —     | -     | —         | _     | -    | -           | —               |                                         |  |      | DDR<6:0>  |    |  |      | 00         |

| DAC      | USB<br>E5RXA     | 31:16         | _     |                                            |       | RX    | HUBPRT<6  | :0>   |      |             | MULTTRAN        |                                         |  |      | BADD<6:0> |    |  |      | 00         |

|          |                  | 15:0          |       |                                            | —     |       | -         |       | _    | -           | -               |                                         |  |      | DDR<6:0>  |    |  |      | 00         |

| 0В0      | USB<br>E6TXA     | 31:16         |       |                                            |       |       | HUBPRT<6: |       |      | 1           | MULTTRAN        |                                         |  |      | BADD<6:0> |    |  |      | 00         |

|          |                  | 15:0          | _     | _                                          | -     |       | HUBPRT<6  | -     | _    | —           |                 |                                         |  |      | DDR<6:0>  |    |  |      | 00         |

| 0B4      | USB<br>E6RXA     | 31:16<br>15:0 | _     | <u> </u>                                   |       | r     | HUBPRIS   |       |      |             | MULTTRAN        |                                         |  |      | BADD<6:0> |    |  |      | 00         |

|          |                  | 31:16         |       |                                            | —     | —<br> | HUBPRT<6  | -     | _    | —           | —<br>MULTTRAN   |                                         |  |      | DDR<6:0>  |    |  |      | 00         |

| 0B8      | USB<br>E7TXA     | 15:0          |       |                                            | _     |       |           | .0>   |      | _           | MULTIRAN        |                                         |  |      | DDR<6:0>  |    |  |      | 00         |

|          |                  | 31:16         |       |                                            |       | RX    | HUBPRT<6  | ·0>   |      | _           | MULTTRAN        |                                         |  |      | BADD<6:0> |    |  |      | 00         |

| 0BC      | USB<br>E7RXA     | 15:0          |       |                                            | _     | _     | _         |       | _    | _           |                 |                                         |  |      | DDR<6:0>  |    |  |      | 00         |

|          | USB              | 31:16         |       |                                            |       |       |           |       |      |             |                 |                                         |  |      |           |    |  |      | 00         |

| 100      | E0CSR0           | 15:0          |       |                                            |       |       |           |       | Inde | exed by the | same bits in U  | SBIE0CSR0                               |  |      |           |    |  |      | 00         |

| 3108     | USB              | 31:16         |       |                                            |       |       |           |       | Ind  | avad by the | oomo hito in Ll |                                         |  |      |           |    |  |      | 00         |

| 108      | E0CSR2           | 15:0          |       |                                            |       |       |           |       | Inde | exed by the | same bits in U  | SBIEUCSKZ                               |  |      |           |    |  |      | 00         |

| 10C      | USB              | 31:16         |       |                                            |       |       |           |       | Inde | aved by the | same bits in U  | SBIEOCSR3                               |  |      |           |    |  |      | 00         |

| 100      | E0CSR3           | 15:0          |       |                                            |       |       |           |       | Inde | sked by the | Same bits in O  | SDIE0001(3                              |  |      |           |    |  |      | 00         |

| 3110     | USB              | 31:16         |       |                                            |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR0                               |  |      |           |    |  |      | 00         |

| /0       | E1CSR0           | 15:0          |       |                                            |       |       |           |       |      | 5,00 5) 110 |                 | 00.2100110                              |  |      |           |    |  |      | 00         |

| 3114     | USB              | 31:16         |       |                                            |       |       |           |       | Inde | exed by the | same bits in U  | SBIE1CSR1                               |  |      |           |    |  |      | 00         |

|          | E1CSR1           | 15:0          |       |                                            |       |       |           |       |      |             |                 |                                         |  |      |           |    |  |      | 00         |

| 3118     | USB              | 31:16         |       | Indexed by the same bits in USBIE1CSR2     |       |       |           |       |      |             |                 |                                         |  |      |           |    |  |      |            |

|          | E1CSR2           | 15:0          |       | 000                                        |       |       |           |       |      |             |                 |                                         |  |      |           |    |  |      |            |

| 11C      | USB<br>E1CSR3    | 31:16         |       | Indexed by the same bits in USBIE1CSR3     |       |       |           |       |      |             |                 |                                         |  |      |           |    |  |      |            |

|          |                  | 15:0          |       |                                            |       |       |           |       |      |             |                 |                                         |  |      |           |    |  |      | 00         |

| 120      | USB<br>E2CSR0    | 31:16         |       |                                            |       |       |           |       | Inde | exed by the | same bits in U  | SBIE2CSR0                               |  |      |           |    |  |      | 000        |

|          |                  | 15:0          |       |                                            |       |       |           |       |      |             |                 |                                         |  |      |           |    |  |      | 000        |

| 3124     | USB<br>E2CSR1    | 31:16         |       |                                            |       |       |           |       | Inde | exed by the | same bits in U  | SBIE2CSR1                               |  |      |           |    |  |      | 000        |

|          |                  | 15:0          |       | Reset; — = un                              |       |       |           |       |      |             |                 |                                         |  |      |           |    |  |      | 000        |

2: 3: 4:

Host mode.

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

| REGISTER 11-6: | USBIE0CSR2: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 2 |

|----------------|------------------------------------------------------------|

|                | (ENDPOINT 0)                                               |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | _                 | _                 | _                 |                   | NAKLIM<4:0>       |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | SPEED<1:0>        |                   | _                 | —                 | —                 |                   | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |

| 7:0          | U-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

|              | _                 |                   |                   |                   | RXCNT<6:0>        |                   |                  |                  |  |

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 NAKLIM<4:0>: Endpoint 0 NAK Limit bits

The number of frames/microframes (Hi-Speed transfers) after which Endpoint 0 should time-out on receiving a stream of NAK responses.

- bit 23-22 SPEED<1:0>: Operating Speed Control bits

- 11 = Low-Speed

- 10 = Full-Speed

- 01 = Hi-Speed

- 00 = Reserved

- bit 21-7 Unimplemented: Read as '0'

- bit 6-0 **RXCNT<6:0>:** Receive Count bits

The number of received data bytes in the Endpoint 0 FIFO. The value returned changes as the contents of the FIFO change and is only valid while RXPKTRDY is set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 |                   |                   |                   |                   |                   | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0, HC         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | SWAPOEN           | SWRST             | SWAPEN            |                   |                   | BDPCHST           | BDPPLEN          | DMAEN            |

#### REGISTER 26-2: CECON: CRYPTO ENGINE CONTROL REGISTER

| Legend:           |                  | HC = Hardware Cleare  | HC = Hardware Cleared |  |  |

|-------------------|------------------|-----------------------|-----------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'        |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown    |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 SWAPOEN: Swap Output Data Enable bit

- 1 = Output data is byte swapped when written by dedicated DMA

- 0 = Output data is not byte swapped when written by dedicated DMA

- bit 6 SWRST: Software Reset bit

- 1 = Initiate a software reset of the Crypto Engine

- 0 = Normal operation

- bit 5 **SWAPEN:** Input Data Swap Enable bit

- 1 = Input data is byte swapped when read by dedicated DMA

- 0 = Input data is not byte swapped when read by dedicated DMA

- bit 4-3 Unimplemented: Read as '0'

#### bit 2 BDPCHST: Buffer Descriptor Processor (BDP) Fetch Enable bit

This bit should be enabled only after all DMA descriptor programming is completed.

- 1 = BDP descriptor fetch is enabled

- 0 = BDP descriptor fetch is disabled

#### bit 1 **BDPPLEN:** Buffer Descriptor Processor Poll Enable bit

This bit should be enabled only after all DMA descriptor programming is completed.

- 1 = Poll for descriptor until valid bit is set

- 0 = Do not poll

# bit 0 DMAEN: DMA Enable bit

- 1 = Crypto Engine DMA is enabled

- 0 = Crypto Engine DMA is disabled

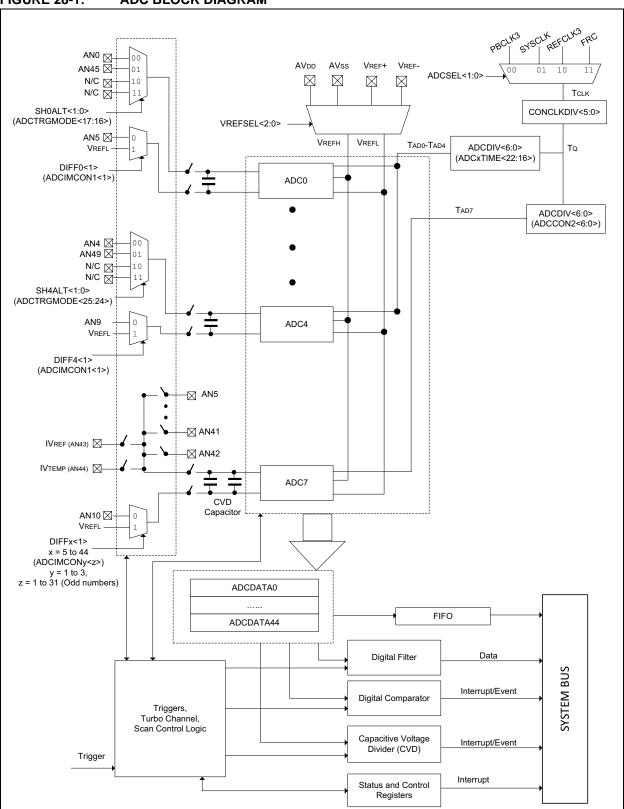

# FIGURE 28-1: ADC BLOCK DIAGRAM

# REGISTER 28-6: ADCIMCON2: ADC INPUT MODE CONTROL REGISTER 2 (CONTINUED)

| REGISTER | 20-0. ADCINICONZ. ADC INFUT IN                          |

|----------|---------------------------------------------------------|

| bit 21   | DIFF26: AN26 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN26 is using Differential mode                     |

|          | 0 = AN26 is using Single-ended mode                     |

| bit 20   | <b>SIGN26:</b> AN26 Signed Data Mode bit <sup>(1)</sup> |

|          | 1 = AN26 is using Signed Data mode                      |

|          | 0 = AN26 is using Unsigned Data mode                    |

| bit 19   | DIFF25: AN25 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN25 is using Differential mode                     |

|          | 0 = AN25 is using Single-ended mode                     |

| bit 18   | SIGN25: AN25 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN25 is using Signed Data mode                      |

|          | 0 = AN25 is using Unsigned Data mode                    |

| bit 17   | DIFF24: AN24 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN24 is using Differential mode                     |

|          | 0 = AN24 is using Single-ended mode                     |

| bit 16   | SIGN24: AN24 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN24 is using Signed Data mode                      |

|          | 0 = AN24 is using Unsigned Data mode                    |

| bit 15   | DIFF23: AN23 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN23 is using Differential mode                     |

|          | 0 = AN23 is using Single-ended mode                     |

| bit 14   | SIGN23: AN23 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN23 is using Signed Data mode                      |

|          | 0 = AN23 is using Unsigned Data mode                    |

| bit 13   | DIFF22: AN22 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN22 is using Differential mode                     |

|          | 0 = AN22 is using Single-ended mode                     |

| bit 12   | SIGN22: AN22 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN22 is using Signed Data mode                      |

|          | 0 = AN22 is using Unsigned Data mode                    |

| bit 11   | DIFF21: AN21 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN21 is using Differential mode                     |

|          | 0 = AN21 is using Single-ended mode                     |

| bit 10   | SIGN21: AN21 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN21 is using Signed Data mode                      |

|          | 0 = AN21 is using Unsigned Data mode                    |

| bit 9    | DIFF20: AN20 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN20 is using Differential mode                     |

|          | 0 = AN20 is using Single-ended mode                     |

| bit 8    | SIGN20: AN20 Signed Data Mode bit <sup>(1)</sup>        |

|          | 1 = AN20 is using Signed Data mode                      |

|          | 0 = AN20 is using Unsigned Data mode                    |

| bit 7    | DIFF19: AN19 Mode bit <sup>(1)</sup>                    |

|          | 1 = AN19 is using Differential mode                     |

|          | 0 = AN19 is using Single-ended mode                     |

|          |                                                         |

Note 1: This bit is not available on 64-pin devices.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|--|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |

| 31:24     |                   |                   |                   | PTV<              | 15:8>             |                   |                  |                     |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |

| 23:16     | PTV<7:0>          |                   |                   |                   |                   |                   |                  |                     |  |

| 15.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |  |

| 15:8      | ON                | —                 | SIDL              | _                 | —                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |  |

| 7:0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |  |

| 7:0       | AUTOFC            |                   | —                 | MANFC             | _                 | —                 | _                | BUFCDEC             |  |

#### REGISTER 30-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

|           | PAUSE Timer Value used for Flow Control.<br>This register should only be written when RXEN (ETHCON1<8>) is not set.                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | These bits are only used for Flow Control operations.                                                                                                                                                                                                                                                     |

| bit 15    | ON: Ethernet ON bit                                                                                                                                                                                                                                                                                       |

|           | <ul><li>1 = Ethernet module is enabled</li><li>0 = Ethernet module is disabled</li></ul>                                                                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                |

| bit 13    | SIDL: Ethernet Stop in Idle Mode bit                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Ethernet module transfers are paused during Idle mode</li> <li>0 = Ethernet module transfers continue during Idle mode</li> </ul>                                                                                                                                                            |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                |

| bit 9     | TXRTS: Transmit Request to Send bit                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Activate the TX logic and send the packet(s) defined in the TX EDT</li> <li>0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)</li> </ul>                                                                                                              |

|           | After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further. |

|           | This bit only affects TX operations.                                                                                                                                                                                                                                                                      |

| bit 8     | RXEN: Receive Enable bit <sup>(1)</sup>                                                                                                                                                                                                                                                                   |

|           | 1 Frankla DV largin manufactor and received and started in the DV hyther as controlled by the filter                                                                                                                                                                                                      |

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- $\ensuremath{\scriptscriptstyle 0}$  = Disable RX logic, no packets are received in the RX buffer

This bit only affects RX operations.

PTV<15:0>: PAUSE Timer Value bits

bit 31-16

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0         |

|--------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|--------------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 51.24        |                   | —                 | -                 | -                 | —                        | —                 | -                | —                        |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 23.10        | _                 | —                 | _                 | _                 | —                        | —                 | _                | —                        |

| 15.0         | U-0               | U-0               | U-0               | U-0               | R/W-0                    | U-0               | U-0              | R/W-0                    |

| 15:8         | _                 | —                 | _                 | _                 | RESETRMII <sup>(1)</sup> | —                 | _                | SPEEDRMII <sup>(1)</sup> |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                      |

| 7:0          |                   | _                 |                   | _                 | _                        | _                 | _                |                          |

#### REGISTER 30-29: EMAC1SUPP: ETHERNET CONTROLLER MAC PHY SUPPORT REGISTER

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31-12 Unimplemented: Read as '0'

- bit 11 **RESETRMII:** Reset RMII Logic bit<sup>(1)</sup>

- 1 = Reset the MAC RMII module

- 0 = Normal operation.

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPEEDRMII: RMII Speed bit<sup>(1)</sup>

- This bit configures the Reduced MII logic for the current operating speed.

- 1 = RMII is running at 100 Mbps

- 0 = RMII is running at 10 Mbps

- bit 7-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for the RMII module.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        |                   | _                 |                   | —                 | —                 |                   |                  | —                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |  |  |

| 15.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |

| 15:8         | STNADDR6<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |  |  |

| 7:0          |                   | STNADDR5<7:0>     |                   |                   |                   |                   |                  |                  |  |  |

### REGISTER 30-37: EMAC1SA0: ETHERNET CONTROLLER MAC STATION ADDRESS 0 REGISTER

| Legend:           |                  | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15-8 **STNADDR6<7:0>:** Station Address Octet 6 bits These bits hold the sixth transmitted octet of the station address.

- bit 7-0 **STNADDR5<7:0>:** Station Address Octet 5 bits These bits hold the fifth transmitted octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 |                   |                   | -                 | _                 | -                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 |                   |                   | _                 | _                 |                   |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 |                   |                   | _                 | _                 |                   |                  | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |

|              |                   |                   | _                 |                   |                   | _                 | C2OUT            | C1OUT            |

# REGISTER 31-2: CMSTAT: COMPARATOR STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-2 Unimplemented: Read as '0'

#### bit 1 C2OUT: Comparator Output bit

1 = Output of Comparator 2 is a '1'

0 = Output of Comparator 2 is a '0'

### bit 0 **C1OUT:** Comparator Output bit

1 = Output of Comparator 1 is a '1'

0 =Output of Comparator 1 is a '0'

# 36.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 36.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| AC CHARACTERISTICS |                  |                              |                        | Standard Operating Conditions: 2.1V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |              |       |                                        |  |

|--------------------|------------------|------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|----------------------------------------|--|

| Param.<br>No.      | Symbol<br>Tr:scl | Characteristics              |                        | Min. <sup>(1)</sup>                                                                                                                                                                                         | Max.         | Units | Conditions                             |  |

| IM21               |                  | SDAx and SCLx                | 100 kHz mode           | —                                                                                                                                                                                                           | 1000         | ns    | CB is specified to be                  |  |

|                    |                  | Rise Time                    | 400 kHz mode           | 20 + 0.1 Св                                                                                                                                                                                                 | 300          | ns    | from 10 to 400 pF                      |  |

|                    |                  |                              | 1 MHz mode<br>(Note 2) |                                                                                                                                                                                                             | 300          | ns    |                                        |  |

| IM25               | TSU:DAT          | Data Input                   | 100 kHz mode           | 250                                                                                                                                                                                                         | _            | ns    | —                                      |  |

|                    |                  | Setup Time                   | 400 kHz mode           | 100                                                                                                                                                                                                         |              | ns    |                                        |  |

|                    |                  |                              | 1 MHz mode<br>(Note 2) | 100                                                                                                                                                                                                         | _            | ns    |                                        |  |

| IM26               | THD:DAT          | Data Input                   | 100 kHz mode           | 0                                                                                                                                                                                                           | _            | μs    | —                                      |  |