Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

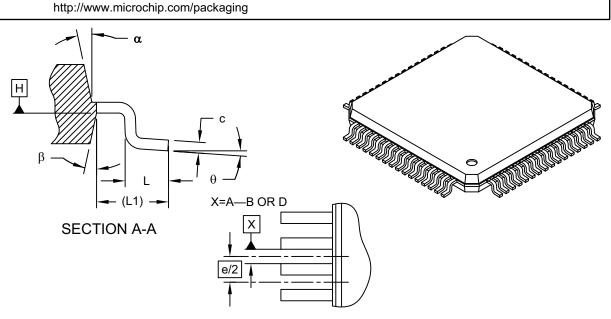

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efg100-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

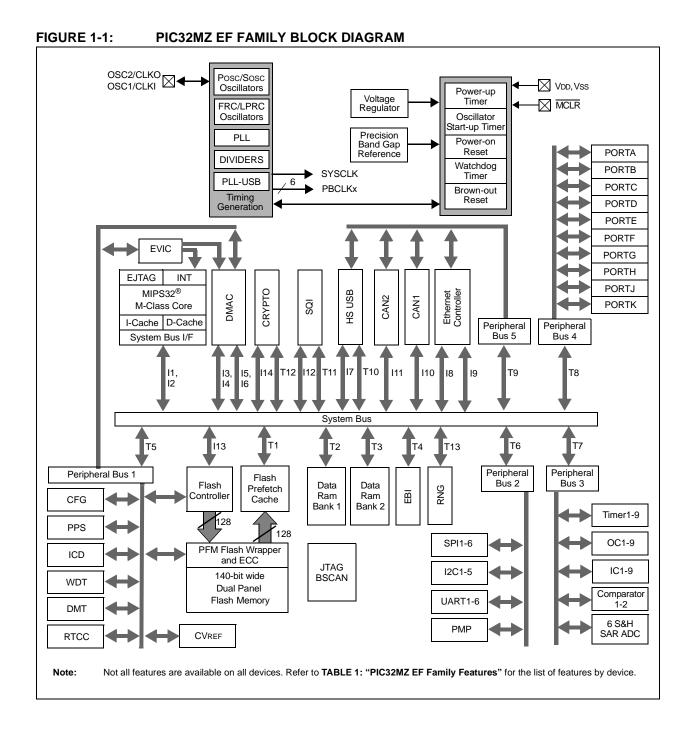

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). This data sheet contains device-specific information for PIC32MZ EF devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MZ EF family of devices.

Table 1-21 through Table 1-22 list the pinout I/O descriptions for the pins shown in the device pin tables (see Table 2 through Table 5).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|--------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |

| 31:24        | —                 | —                 | _                 | _                 | -                 | _                 | —                | _                  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |

| 15:8         | —                 | _                 | _                 | _                 | -                 | _                 | _                |                    |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0                |

|              |                   |                   |                   | _                 |                   |                   | GROU             | <sup>D</sup> <1:0> |

### **REGISTER 4-4:** SBTxELOG2: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 2 ('x' = 0-13)

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

### bit 31-3 Unimplemented: Read as '0'

- bit 1-0 GROUP<1:0>: Requested Permissions Group bits

- 11 = Group 3

- 10 = Group 2

- 01 = Group 1

- 00 = Group 0

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

#### REGISTER 4-5: SBTxECON: SYSTEM BUS TARGET 'x' ERROR CONTROL REGISTER ('x' = 0-13)

|              |                   | x = 0 = 13        |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        | —                 | —                 | _                 | _                 | -                 |                   | _                | ERRP             |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | -                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | —                 |                   |                   |                   |                   |                   |                  | —                |

| Legend:           |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-25 Unimplemented: Read as '0'

bit 24 ERRP: Error Control bit

1 = Report protection group violation errors

0 = Do not report protection group violation errors

bit 23-0 Unimplemented: Read as '0'

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | R/W-0, HS         | R/W-0, HS         | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | PFMDED            | PFMSEC            | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 7:0          | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |

|              |                   |                   |                   | PFMSEC            | CNT<7:0>          |                   |                  |                  |

# REGISTER 9-2: PRESTAT: PREFETCH MODULE STATUS REGISTER

| Legend:                           |                  | HS = Hardware Set    | HS = Hardware Set  |  |  |

|-----------------------------------|------------------|----------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bi | t, read as '0'     |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 31-28 Unimplemented: Read as '0'

- bit 27 **PFMDED:** Flash Double-bit Error Detected (DED) Status bit

This bit is set in hardware and can only be cleared (i.e., set to '0') in software.

1 = A DED error has occurred

- 0 = A DED error has not occurred

- bit 26 **PFMSEC:** Flash Single-bit Error Corrected (SEC) Status bit 1 = A SEC error occurred when PFMSECCNT<7:0> was equal to zero 0 = A SEC error has not occurred

- bit 25-8 Unimplemented: Read as '0'

- bit 7-0 **PFMSECCNT<7:0>:** Flash SEC Count bits 11111111 - 00000000 = SEC count

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 |                   |                   |                   | _                 |                   |                  | —                |  |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |

### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL x SOURCE SIZE REGISTER

# Legend:

| Legena.           |                                 |                      |                                    |  |  |

|-------------------|---------------------------------|----------------------|------------------------------------|--|--|

| R = Readable bit  | = Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

### **REGISTER 10-13: DCHxDSIZ: DMA CHANNEL x DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 |                   | —                 | —                 | _                 | —                 |                  | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |  |

| Legend:           |                  |                                        |                    |  |

|-------------------|------------------|----------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | bit U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                   | x = Bit is unknown |  |

bit 15-0 **CHDSIZ<15:0>:** Channel Destination Size bits

111111111111111 = 65,535 byte destination size  $\ensuremath{\cdot}$

## REGISTER 11-1: USBCSR0: USB CONTROL STATUS REGISTER 0 (CONTINUED)

- bit 10 **RESUME:** Resume from Suspend control bit

- 1 = Generate Resume signaling when the device is in Suspend mode

- 0 = Stop Resume signaling

In *Device mode*, the software should clear this bit after 10 ms (a maximum of 15 ms) to end Resume signaling. In *Host mode*, the software should clear this bit after 20 ms.

- bit 9 **SUSPMODE:** Suspend Mode status bit 1 = The USB module is in Suspend mode

- 0 = The USB module is in Normal operations

This bit is read-only in Device mode. In Host mode, it can be set by software, and is cleared by hardware.

- bit 8 SUSPEN: Suspend Mode Enable bit

- 1 = Suspend mode is enabled

- 0 = Suspend mode is not enabled

- bit 7 Unimplemented: Read as '0'

- bit 6-0 **FUNC<6:0>:** Device Function Address bits

These bits are only available in *Device mode*. This field is written with the address received through a SET\_ADDRESS command, which will then be used for decoding the function address in subsequent token packets.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | _                 |                   | —                 |                   |                   | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | _                 |                   | —                 | _                 |                   | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | —                 | DMAEIE            | PKTCOMPIE         | BDDONEIE         | CONTHRIE         |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CONEMPTYIE        | CONFULLIE         | RXTHRIE           | RXFULLIE          | RXEMPTYIE         | TXTHRIE           | TXFULLIE         | TXEMPTYIE        |

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

HS = Hardware Set

W = Writable bit

'1' = Bit is set

# REGISTER 20-8: SQI1INTEN: SQI INTERRUPT ENABLE REGISTER

| bit 10   | DMAEIE: DMA Bus Error Interrupt Enable bit <ol> <li>Interrupt is enabled</li> <li>Interrupt is disabled</li> <li>PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit</li> <li>Interrupt is enabled</li> <li>Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ol> |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10 I | <ul> <li>0 = Interrupt is disabled</li> <li>PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit</li> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                              |

| bit 10   | <ul> <li>PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit</li> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                                                                 |

| bit 9    | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                                                                                                                                                |

| bit 9    | <ul> <li>Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                                                                                                                                                                                      |

| bit 9 I  | BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit                                                                                                                                                                                                                                                                         |

| :        |                                                                                                                                                                                                                                                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                                   |

| l        | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

| bit 8    | CONTHRIE: Control Buffer Threshold Interrupt Enable bit                                                                                                                                                                                                                                                                           |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

| bit 7    | CONEMPTYIE: Control Buffer Empty Interrupt Enable bit                                                                                                                                                                                                                                                                             |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | CONFULLIE: Control Buffer Full Interrupt Enable bit                                                                                                                                                                                                                                                                               |

|          | This bit enables an interrupt when the receive FIFO buffer is full.                                                                                                                                                                                                                                                               |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | RXTHRIE: Receive Buffer Threshold Interrupt Enable bit                                                                                                                                                                                                                                                                            |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | RXFULLIE: Receive Buffer Full Interrupt Enable bit                                                                                                                                                                                                                                                                                |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                                   |

|          | RXEMPTYIE: Receive Buffer Empty Interrupt Enable bit                                                                                                                                                                                                                                                                              |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                   |

|          | TXTHRIE: Transmit Threshold Interrupt Enable bit                                                                                                                                                                                                                                                                                  |

|          | -                                                                                                                                                                                                                                                                                                                                 |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                   |

|          | TXFULLIE: Transmit Buffer Full Interrupt Enable bit                                                                                                                                                                                                                                                                               |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | TXEMPTYIE: Transmit Buffer Empty Interrupt Enable bit                                                                                                                                                                                                                                                                             |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

Legend:

R = Readable bit

-n = Value at POR

| REGISTER 24-3: | EBISMTX: EXTERNAL BUS INTERFACE STATIC MEMORY TIMING REGISTER |

|----------------|---------------------------------------------------------------|

|                | ('x' = 0-2)                                                   |

|              |                   | ,                  |                   | 1                       | 1                        |                   |                  |                  |  |

|--------------|-------------------|--------------------|-------------------|-------------------------|--------------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4       | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0               | U-0                | U-0               | U-0                     | U-0                      | R/W-1             | R/W-0            | R/W-0            |  |

|              | —                 | —                  | —                 | —                       | —                        | RDYMODE           | PAGESI           | ZE<1:0>          |  |

| 00.40        | R/W-0             | R/W-0              | R/W-0             | R/W-1                   | R/W-1                    | R/W-1             | R/W-0            | R/W-0            |  |

| 23:16        | PAGEMODE          |                    | TPRC<             | <3:0> <sup>(1)</sup>    | TBTA<2:0> <sup>(1)</sup> |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0              | R/W-1             | R/W-0                   | R/W-1                    | R/W-1             | R/W-0            | R/W-1            |  |

| 15:8         |                   | •                  | TWR<              | :1:0> <sup>(1)</sup>    |                          |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-1              | R/W-0             | R/W-0                   | R/W-1                    | R/W-0             | R/W-1            | R/W-1            |  |

| 7:0          | TAS<1             | :0> <sup>(1)</sup> |                   | TRC<5:0> <sup>(1)</sup> |                          |                   |                  |                  |  |

## Legend:

| 5                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

# bit 31-27 Unimplemented: Read as '0'

| bit 26    | RDYMODE: Data Ready Device Select bit                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------|

|           | The device associated with register set 'x' is a data-ready device, and will use the EBIRDYx pin.     |

|           | 1 = EBIRDYx input is used                                                                             |

|           | 0 = EBIRDYx input is not used                                                                         |

| bit 25-24 | PAGESIZE<1:0>: Page Size for Page Mode Device bits                                                    |

|           | 11 = 32-word page                                                                                     |

|           | 10 = 16-word page                                                                                     |

|           | 01 = 8-word page                                                                                      |

|           | 00 = 4-word page                                                                                      |

| bit 23    | PAGEMODE: Memory Device Page Mode Support bit                                                         |

|           | 1 = Device supports Page mode                                                                         |

|           | 0 = Device does not support Page mode                                                                 |

| bit 22-19 | TPRC<3:0>: Page Mode Read Cycle Time bits <sup>(1)</sup>                                              |

|           | Read cycle time is TPRC + 1 clock cycle.                                                              |

| bit 18-16 | TBTA<2:0>: Data Bus Turnaround Time bits <sup>(1)</sup>                                               |

|           | Clock cycles (0-7) for static memory between read-to-write, write-to-read, and read-to-read when Chip |

|           | Select changes.                                                                                       |

| bit 15-10 | TWP<5:0>: Write Pulse Width bits <sup>(1)</sup>                                                       |

|           | Write pulse width is TWP + 1 clock cycle.                                                             |

| bit 9-8   | TWR<1:0>: Write Address/Data Hold Time bits <sup>(1)</sup>                                            |

|           |                                                                                                       |

- Number of clock cycles to hold address or data on the bus.bit 7-6TAS<1:0>: Write Address Setup Time bits<sup>(1)</sup>

- TAS<1:0>: Write Address Setup Time bits<sup>(1)</sup>

Clock cycles for address setup time. A value of '0' is only valid in the case of SSRAM.

- bit 5-0 **TRC<5:0>:** Read Cycle Time bits<sup>(1)</sup> Read cycle time is TRC + 1 clock cycle.

- Note 1: Refer to the Section 47. "External Bus Interface (EBI)" in the "PIC32 Family Reference Manual" for the EBI timing diagrams and additional information.

## 26.3 Security Association Structure

Table 26-4 shows the Security Association Structure. The Crypto Engine uses the Security Association to determine the settings for processing a Buffer Descriptor Processor. The Security Association contains:

- · Which algorithm to use

- Whether to use engines in parallel (for both authentication and encryption/decryption)

- The size of the key

- Authentication key

- Encryption/decryption key

- Authentication Initialization Vector (IV)

- Encryption IV

| Name        |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| SA_CTRL     | 31:24 | _                 |                   | VERIFY            | _                 | NO_RX             | OR_EN             | ICVONLY          | IRFLAG           |  |  |

| _           | 23:16 | LNC               | LOADIV            | FB                | FLAGS             | _                 | _                 |                  | ALGO<6>          |  |  |

|             | 15:8  |                   |                   | ALGO<             | :5:0>             | 1                 |                   | ENCTYPE          | KEYSIZE<1:       |  |  |

|             | 7:0   | KEYSIZE<0>        | N                 | IULTITASK<2:0     | >                 |                   | CRYPTOA           | LGO<3:0>         | ILE I OILE (     |  |  |

| SA_AUTHKEY1 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |  |  |

| _           | 23:16 |                   |                   |                   | AUTHKEY<          |                   |                   |                  |                  |  |  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |  |  |

|             | 7:0   |                   |                   |                   | AUTHKEY           | <7:0>             |                   |                  |                  |  |  |

| SA_AUTHKEY2 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |  |  |

|             | 23:16 |                   |                   |                   | AUTHKEY<          | 23:16>            |                   |                  |                  |  |  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |  |  |

|             | 7:0   |                   |                   |                   | AUTHKEY           | <7:0>             |                   |                  |                  |  |  |

| SA_AUTHKEY3 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |  |  |

| _           | 23:16 |                   |                   |                   | AUTHKEY<          | 23:16>            |                   |                  |                  |  |  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |  |  |

|             | 7:0   | AUTHKEY<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| SA_AUTHKEY4 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |  |  |

| _           | 23:16 | AUTHKEY<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

|             | 15:8  | AUTHKEY<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

|             | 7:0   | AUTHKEY<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| SA_AUTHKEY5 | 31:24 | AUTHKEY<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

|             | 23:16 | AUTHKEY<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          |                   |                   |                  |                  |  |  |

|             | 7:0   | AUTHKEY<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| SA_AUTHKEY6 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |  |  |

|             | 23:16 | AUTHKEY<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

|             | 15:8  | AUTHKEY<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

|             | 7:0   | AUTHKEY<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| SA_AUTHKEY7 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |  |  |

|             | 23:16 | AUTHKEY<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |  |  |

|             | 7:0   | AUTHKEY<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| SA_AUTHKEY8 | 31:24 |                   |                   |                   | AUTHKEY<          | 31:24>            |                   |                  |                  |  |  |

|             | 23:16 | AUTHKEY<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

|             | 15:8  |                   |                   |                   | AUTHKEY<          | :15:8>            |                   |                  |                  |  |  |

|             | 7:0   |                   |                   |                   | AUTHKEY           | <7:0>             |                   |                  |                  |  |  |

| SA_ENCKEY1  | 31:24 |                   |                   |                   | ENCKEY<3          | 31:24>            |                   |                  |                  |  |  |

|             | 23:16 |                   |                   |                   | ENCKEY<2          | 23:16>            |                   |                  |                  |  |  |

|             | 15:8  |                   |                   |                   | ENCKEY<           | 15:8>             |                   |                  |                  |  |  |

|             | 7:0   |                   |                   |                   | ENCKEY<           | :7:0>             |                   |                  |                  |  |  |

| SA_ENCKEY2  | 31:24 |                   |                   |                   | ENCKEY<3          | 31:24>            |                   |                  |                  |  |  |

|             | 23:16 |                   |                   |                   | ENCKEY<2          | 23:16>            |                   |                  |                  |  |  |

# TABLE 26-4: CRYPTO ENGINE SECURITY ASSOCIATION STRUCTURE

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FLTEN19           | MSEL19<1:0>       |                   | FSEL19<4:0>       |                   |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN18           | MSEL18<1:0>       |                   | FSEL18<4:0>       |                   |                   |                  |                  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FLTEN17           | MSEL17<1:0>       |                   | FSEL17<4:0>       |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN16           | MSEL16<1:0>       |                   | FSEL16<4:0>       |                   |                   |                  |                  |

## REGISTER 29-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | FLTEN19: Filter 19 Enable bit                                                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                                                                    |

|           | 0 = Filter is disabled                                                                                                   |

| bit 30-29 | MSEL19<1:0>: Filter 19 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                       |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 28-24 | FSEL19<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN18: Filter 18 Enable bit                                                                                            |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                          |

| bit 22-21 | MSEL18<1:0>: Filter 18 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected                                                                                          |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                       |

| bit 20-16 | <b>FSEL18&lt;4:0&gt;:</b> FIFO Selection bits                                                                            |

| 511 20 10 | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                               |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                               |

|           |                                                                                                                          |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FLTEN23           | MSEL23<1:0>       |                   | FSEL23<4:0>       |                   |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN22           | MSEL22<1:0>       |                   | FSEL22<4:0>       |                   |                   |                  |                  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FLTEN21           | MSEL21<1:0>       |                   | FSEL21<4:0>       |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN20           | MSEL20<1:0>       |                   | FSEL20<4:0>       |                   |                   |                  |                  |

## REGISTER 29-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | FLTEN23: Filter 23 Enable bit                                                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                          |

| bit 30-29 | MSEL23<1:0>: Filter 23 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                       |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 28-24 | FSEL23<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           |                                                                                                                          |

|           |                                                                                                                          |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN22: Filter 22 Enable bit                                                                                            |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                   |

| bit 22-21 | MSEL22<1:0>: Filter 22 Mask Select bits                                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                                          |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                       |

|           | 00 = Acceptance Mask 0 selected                                                                                          |

| bit 20-16 | FSEL22<4:0>: FIFO Selection bits                                                                                         |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                              |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                              |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | •                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                   |

| Note.     | The bits in this register can only be modified if the corresponding little enable (I EI EI III) bit is 0.                |

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | —                 | _                 | —                 | —                 | —                 | —                | —                |

| 00.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | _                 | —                 | —                 | —                 | —                | —                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0      | —                 | —                 | _                 | —                 | —                 | R                 | XBUFSZ<6:        | 4>               |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 7:0       | RXBUFSZ<3:0>      |                   |                   | —                 | _                 | —                 | —                |                  |

# REGISTER 30-2: ETHCON2: ETHERNET CONTROLLER CONTROL REGISTER 2

# Legend:

| Logona.           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

## bit 31-11 Unimplemented: Read as '0'

| bit 10-4 | RXBUFSZ<6:0>: RX Data Buffer Size for All RX Descriptors (in 16-byte increments) bits<br>1111111 = RX data Buffer size for descriptors is 2032 bytes                                                      |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | •                                                                                                                                                                                                         |

|          | •                                                                                                                                                                                                         |

|          | 1100000 = RX data Buffer size for descriptors is 1536 bytes                                                                                                                                               |

|          | •                                                                                                                                                                                                         |

|          | •                                                                                                                                                                                                         |

|          | •                                                                                                                                                                                                         |

|          | 0000011 = RX data Buffer size for descriptors is 48 bytes<br>0000010 = RX data Buffer size for descriptors is 32 bytes<br>0000001 = RX data Buffer size for descriptors is 16 bytes<br>0000000 = Reserved |

| bit 3-0  | Unimplemented: Read as '0'                                                                                                                                                                                |

| Note 1:  | This register is only used for RX operations.                                                                                                                                                             |

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

#### **REGISTER 30-24: EMAC1CFG2: ETHERNET CONTROLLER MAC CONFIGURATION 2 REGISTER** VLANPAD: VLAN Pad Enable bit<sup>(1,2)</sup> bit 6 1 = The MAC will pad all short frames to 64 bytes and append a valid CRC 0 = The MAC does not perform padding of short frames PADENABLE: Pad/CRC Enable bit<sup>(1,3)</sup> bit 5 1 = The MAC will pad all short frames 0 = The frames presented to the MAC have a valid length bit 4 CRCENABLE: CRC Enable1 bit 1 = The MAC will append a CRC to every frame whether padding was required or not. Must be set if the PADENABLE bit is set. 0 = The frames presented to the MAC have a valid CRC bit 3 DELAYCRC: Delayed CRC bit This bit determines the number of bytes, if any, of proprietary header information that exist on the front of the IEEE 802.3 frames. 1 = Four bytes of header (ignored by the CRC function) 0 = No proprietary header bit 2 HUGEFRM: Huge Frame enable bit 1 = Frames of any length are transmitted and received 0 = Huge frames are not allowed for receive or transmit bit 1 LENGTHCK: Frame Length checking bit 1 = Both transmit and receive frame lengths are compared to the Length/Type field. If the Length/Type field represents a length then the check is performed. Mismatches are reported on the transmit/receive statistics vector. 0 = Length/Type field check is not performed bit 0 FULLDPLX: Full-Duplex Operation bit 1 = The MAC operates in Full-Duplex mode

- 0 = The MAC operates in Half-Duplex mode

- **Note 1:** Table 30-6 provides a description of the pad function based on the configuration of this register.

- **2:** This bit is ignored if the PADENABLE bit is cleared.

- 3: This bit is used in conjunction with the AUTOPAD and VLANPAD bits.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware

# TABLE 30-6:PAD OPERATION

| Туре | AUTOPAD | VLANPAD | PADENABLE | Action                                                                                  |

|------|---------|---------|-----------|-----------------------------------------------------------------------------------------|

| Any  | x       | x       | 0         | No pad, check CRC                                                                       |

| Any  | 0       | 0       | 1         | Pad to 60 Bytes, append CRC                                                             |

| Any  | x       | 1       | 1         | Pad to 64 Bytes, append CRC                                                             |

| Any  | 1       | 0       | 1         | If untagged: Pad to 60 Bytes, append CRC<br>If VLAN tagged: Pad to 64 Bytes, append CRC |

| RE | REGISTER 30-31: EMAC1MCFG: ETHERNET CONTROLLER MAC MII MANAGEMENT |     |     |             |     |     |             |     |  |

|----|-------------------------------------------------------------------|-----|-----|-------------|-----|-----|-------------|-----|--|

|    | CONFIGURATION REGISTER                                            |     |     |             |     |     |             |     |  |

|    | Dit                                                               | 5.4 | D'/ | <b>D</b> .' | D'/ | D'1 | <b>D</b> '' | D.1 |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 51.24        |                   | —                 | _                 | _                 | _                     | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | _                 | _                 | _                     | _                 | —                | —                |

| 15:8         | R/W-0             | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 15.0         | RESETMGMT         | —                 | _                 | _                 | _                     | _                 | —                | —                |

| 7:0          | U-0               | U-0               | R/W-1             | R/W-0             | R/W-0                 | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | _                 |                   | CLKSEL            | _<3:0> <sup>(1)</sup> |                   | NOPRE            | SCANINC          |

### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **RESETMGMT:** Test Reset MII Management bit 1 = Reset the MII Management module 0 = Normal Operation

- bit 14-6 Unimplemented: Read as '0'

#### bit 1 NOPRE: Suppress Preamble bit

- 1 = The MII Management will perform read/write cycles without the 32-bit preamble field. Some PHYs support suppressed preamble

- 0 = Normal read/write cycles are performed

#### bit 0 SCANINC: Scan Increment bit

- 1 = The MII Management module will perform read cycles across a range of PHYs. The read cycles will start from address 1 through the value set in EMAC1MADR<PHYADDR>

- 0 = Continuous reads of the same PHY

- **Note 1:** Table 30-7 provides a description of the clock divider encoding.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

### TABLE 30-7: MIIM CLOCK SELECTION

| MIIM Clock Select     | EMAC1MCFG<5:2>        |

|-----------------------|-----------------------|

| TPBCLK5 divided by 4  | 000x                  |

| TPBCLK5 divided by 6  | 0010                  |

| TPBCLK5 divided by 8  | 0011                  |

| TPBCLK5 divided by 10 | 0100                  |

| TPBCLK5 divided by 14 | 0101                  |

| TPBCLK5 divided by 20 | 0110                  |

| TPBCLK5 divided by 28 | 0111                  |

| TPBCLK5 divided by 40 | 1000                  |

| TPBCLK5 divided by 48 | 1001                  |

| TPBCLK5 divided by 50 | 1010                  |

| Undefined             | Any other combination |

bit 5-2 **CLKSEL<3:0>:** MII Management Clock Select 1 bits<sup>(1)</sup> These bits are used by the clock divide logic in creating the MII Management Clock (MDC), which the IEEE 802.3 Specification defines to be no faster than 2.5 MHz. Some PHYs support clock rates up to 12.5 MHz.

# 33.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes power-saving features for the PIC32MZ EF devices. These devices offer various methods and modes that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 33.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the speed of PBCLK7, or selecting a lower power clock source (i.e., LPRC or Sosc).

In addition, the Peripheral Bus Scaling mode is available for each peripheral bus where peripherals are clocked at reduced speed by selecting a higher divider for the associated PBCLKx, or by disabling the clock completely.

# 33.2 Power-Saving with CPU Halted

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

## 33.2.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted and the associated clocks are disabled. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the peripheral bus clocks will start running and the device will enter into Idle mode.

## 33.2.2 IDLE MODE

In Idle mode, the CPU is Halted; however, all clocks are still enabled. This allows peripherals to continue to operate. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0       |

|--------------|-------------------|-------------------|-----------------------|------------------------|-----------------------|-------------------|-----------------------|------------------------|

| 04-04        | U-0               | U-0               | U-0                   | U-0                    | U-0                   | U-0               | R/W-0                 | R/W-0                  |

| 31:24        | —                 | —                 | —                     | —                      | —                     | —                 | DMAPRI <sup>(1)</sup> | CPUPRI <sup>(1)</sup>  |

| 00.40        | U-0               | U-0               | U-0                   | U-0                    | U-0                   | U-0               | R/W-0                 | R/W-0                  |

| 23:16        | —                 | —                 | —                     | —                      | —                     | —                 | ICACLK <sup>(1)</sup> | OCACLK <sup>(1)</sup>  |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | R/W-0                 | U-0               | U-0                   | R/W-0                  |

| 15:8         | —                 | —                 | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> | PGLOCK <sup>(1)</sup> | _                 | _                     | USBSSEN <sup>(1)</sup> |

| 7:0          | R/W-0             | U-0               | R/W-1                 | R/W-1                  | R/W-1                 | R/W-0             | U-0                   | R/W-1                  |