Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

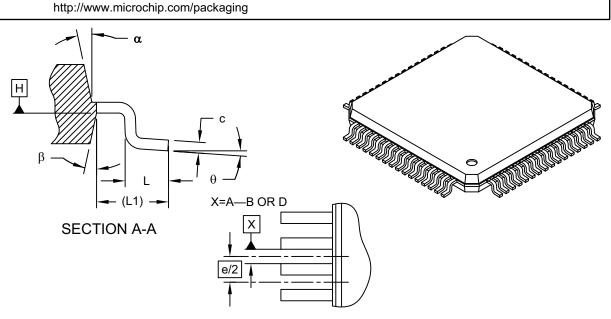

| Mounting Type              | Surface Mount                                                                     |

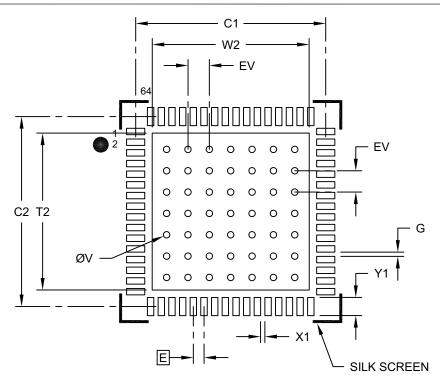

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efg100t-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.7 M-Class Core Configuration

Register 3-1 through Register 3-4 show the default configuration of the M-Class core, which is included on the PIC32MZ EF family of devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-1               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 31:24        |                   | —                 | —                 | _                 | —                 |                   | —                | ISP              |

| 22:46        | R-0               | R-0               | R-1               | R-0               | U-0               | R-1               | R-0              | R-0              |

| 23:16        | DSP               | UDI               | SB                | MDU               | —                 | MM<1:0> E         |                  | BM               |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-1               | R-0              | R-0              |

| 15:8         | BE                | AT<               | 1:0>              |                   | AR<2:0>           |                   | MT<              | 2:1>             |

| 7.0          | R-1               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | MT<0>             |                   | _                 | _                 | _                 |                   | K0<2:0>          |                  |

# REGISTER 3-1: CONFIG: CONFIGURATION REGISTER; CP0 REGISTER 16, SELECT 0

| Legend:           | r = Reserved bit |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31 Reserved: This bit is hardwired to '1' to indicate the presence of the Config1 register.<br>bit 30-25 Unimplemented: Read as '0'<br>bit 24 ISP: Instruction Scratch Pad RAM bit<br>0 = Instruction Scratch Pad RAM is not implemented<br>bit 23 DSP: Data Scratch Pad RAM is not implemented<br>bit 24 UDI: User-defined bit<br>0 = CorExtend User-Defined Instructions are not implemented<br>bit 21 SB: SimpleBE bit<br>1 = Only Simple Byte Enables are allowed on the internal bus interface<br>bit 20 MDU: Multiply/Divide Unit bit<br>0 = Fast, high-performance MDU<br>bit 19 Unimplemented: Read as '0'<br>bit 18-17 MM-1:00: Warge Mode bits<br>10 = Merging is allowed<br>bit 15 BE: Endian Mode bit<br>0 = Burst order is sequential<br>bit 14-3 AT<1:0>: Architecture Type bits<br>00 = MIPS32<br>bit 12-10 AR<2:0>: Architecture Revision Level bits<br>001 = MIPS32 Release 2<br>bit 9: VIT-2:0>: MMUU Type bits<br>001 = M-Class MPU Microprocessor core uses a TLB-based MMU<br>bit 2- Ko2:0>: Kseg0 Coherency Algorithm bits<br>011 = Cacheable, non-coherent, write-back, write allocate<br>002 = Cacheable, non-coherent, write-back, write allocate<br>003 = Cacheable, non-coherent, write-through, no write allocate<br>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111<br>mapped to 010.                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 24       ISP: Instruction Scratch Pad RAM bit         0 = Instruction Scratch Pad RAM is not implemented         bit 23       DSP: Data Scratch Pad RAM is not implemented         bit 22       UDI: User-defined bit         0 = CorExtend User-Defined Instructions are not implemented         bit 21       SB: SimpleBE bit         1 = Only Simple Byte Enables are allowed on the internal bus interface         bit 20       MDU: Multiply/Divide Unit bit         0 = Fast, high-performance MDU         bit 19       Unimplemented: Read as '0'         bit 18-17       MM<1:0>: Merge Mode bits         10 = Merging is allowed         bit 16       BM: Burst Mode bit         0 = Burst order is sequential         bit 15       BE: Endian Mode bit         0 = Little-endian         bit 14-13       AT<:0>: Architecture Type bits         001 = MIPS32         bit 9-7       MT<2:0>: MMU Type bits         001 = M-Class MPU Microprocessor core uses a TLB-based MMU         bit 6-3       Unimplemented: Read as '0'         bit 2-0       Ko<2:0>: Kseg0 Coherency Algorithm bits         01 = Cacheable, non-coherent, write-back, write allocate         010 = Uncached       011 = Cacheable, non-coherent, write-through, write allocate         010 = Cacheable, non-coherent, write                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 31    | Reserved: This bit is hardwired to '1' to indicate the presence of the Config1 register.                                                                              |

| 0 = Instruction Scratch Pad RAM is not implemented         bit 23       DSP: Data Scratch Pad RAM bit         0 = Data Scratch Pad RAM is not implemented         bit 22       UDI: User-defined bit         0 = CorExtend User-Defined Instructions are not implemented         bit 21       SB: SimpleBE bit         1 = Only Simple Byte Enables are allowed on the internal bus interface         bit 20       MDU: Multiply/Divide Unit bit         0 = Fast, high-performance MDU         bit 19       Unimplemented: Read as '0'         bit 18-17       MM<1:0>: Merging is allowed         bit 16       BW: Burst Mode bit         0 = Burst order is sequential         bit 16       BE: Endian Mode bit         0 = Little-endian         bit 14-13       AT<1:0>: Architecture Type bits         001 = MIPS32         bit 14-13       AT<2:0>: Architecture Revision Level bits         001 = MIPS32 Release 2         bit 97       MT<2:0>: Kseg0 Coherency Algorithm bits         011 = Cacheable, non-coherent, write-thorugh, write allocate         012 = Cacheable, non-coherent, write-through, no write allocate         013 = Cacheable, non-coherent, write allocate         014 = Cacheable, non-coherent, write-through, no write allocate         015 = Cacheable, non-coherent, write-through, no write allocate </td <td>bit 30-25</td> <td>Unimplemented: Read as '0'</td>                                                                                                                                                                                                                                                                                                                                                                                     | bit 30-25 | Unimplemented: Read as '0'                                                                                                                                            |

| <ul> <li>0 = Data Scratch Pad RAM is not implemented</li> <li>bit 22</li> <li>UDI: User-defined bit         <ul> <li>0 = CorExtend User-Defined Instructions are not implemented</li> <li>bit 21</li> <li>SB: SimpleBE bit</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 24    |                                                                                                                                                                       |

| <ul> <li>0 = CorExtend User-Defined Instructions are not implemented</li> <li>bit 21</li> <li>SB: SimpleBE bit         <ul> <li>1 = Only Simple Byte Enables are allowed on the internal bus interface</li> </ul> </li> <li>bit 20</li> <li>MDU: Multiply/Divide Unit bit         <ul> <li>0 = Fast, high-performance MDU</li> <li>bit 19</li> <li>Unimplemented: Read as '0'</li> <li>bit 18-17</li> <li>MM&lt;1:0&gt;: Merging is allowed</li> </ul> </li> <li>bit 18-17</li> <li>MM&lt;1:0&gt;: Merge Mode bits         <ul> <li>10 = Merging is allowed</li> </ul> </li> <li>bit 16</li> <li>BM: Burst Mode bit             <ul> <li>0 = Burst order is sequential</li> <li>0 = Little-endian</li> <li>bit 14-13</li> <li>AT&lt;1:0&gt;: Architecture Type bits             <ul> <li>00 = MIPS32</li> <li>bit 12-10</li> <li>AR&lt;2:0&gt;: Architecture Revision Level bits             <ul> <li>001 = MIPS32 Release 2</li> <li>bit 9-7</li> <li>MT&lt;2:0&gt;: MMU Type bits             <ul> <li>001 = M-Class MPU Microprocessor core uses a TLB-based MMU</li> <li>bit 2-0</li> <li>KO&lt;2:0&gt;: Kseg0 Coherency Algorithm bits             <ul> <li>011 = Cacheable, non-coherent, write-back, write allocate</li> <li>010 = Uncached</li> <li>001 = Cacheable, non-coherent, write-through, no write allocate</li> <li>010 = Cachea</li></ul></li></ul></li></ul></li></ul></li></ul></li></ul> | bit 23    |                                                                                                                                                                       |

| 1 = Only Simple Byte Enables are allowed on the internal bus interface         bit 20       MDU: Multiply/Divide Unit bit         0 = Fast, high-performance MDU         bit 19       Unimplemented: Read as '0'         bit 18-17       MM<1:0>: Merge Mode bits         10 = Merging is allowed         bit 18       BM: Burst Mode bit         0 = Burst order is sequential         bit 15       BE: Endian Mode bit         0 = Little-endian         bit 14-13       AT<1:0>: Architecture Type bits         00 = MIPS32         bit 12-10       AR<2:0>: Architecture Revision Level bits         001 = MIPS32 Release 2         bit 9-7       MT<2:0>: MMU Type bits         001 = MIPS32 Release 2         bit 2-0       K0<2:0>: Kseg0 Coherency Algorithm bits         011 = Cacheable, non-coherent, write-back, write allocate         0102 = Uncached         011 = Cacheable, non-coherent, write-through, write allocate         0102 = Cacheable, non-coherent, write-through, write allocate         0103 = Cacheable, non-coherent, write-through, no write allocate         0104 = Cacheable, non-coherent, write-through, no write allocate         0105 = Cacheable, non-coherent, write-through, no write allocate         0105 = Cacheable, non-coherent, write-through, no write allocate         0106 = Ca                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 22    |                                                                                                                                                                       |

| <ul> <li>0 = Fast, high-performance MDU</li> <li>bit 19 Unimplemented: Read as '0'</li> <li>bit 18-17 MM&lt;1:0&gt;: Merge Mode bits 10 = Merging is allowed</li> <li>bit 16 BM: Burst Mode bit 0 = Burst order is sequential</li> <li>bit 15 BE: Endian Mode bit 0 = Little-endian</li> <li>bit 14-13 AT&lt;1:0&gt;: Architecture Type bits 00 = MIPS32</li> <li>bit 12-10 AR&lt;2:0&gt;: Architecture Revision Level bits 001 = MIPS32 Release 2</li> <li>bit 9-7 MT&lt;2:0&gt;: MMU Type bits 001 = M-Class MPU Microprocessor core uses a TLB-based MMU</li> <li>bit 6-3 Unimplemented: Read as '0'</li> <li>bit 2-0 KO&lt;2:0&gt;: Kseg0 Coherency Algorithm bits 011 = Cacheable, non-coherent, write-through, write allocate 010 = Uncached 001 = Cacheable, non-coherent, write-through, no write allocate All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 21    |                                                                                                                                                                       |

| bit 18-17       MM-1:0>: Merge Mode bits         10 = Merging is allowed         bit 16       BM: Burst Mode bit         0 = Burst order is sequential         bit 15       BE: Endian Mode bit         0 = Little-endian         bit 14-13       AT<1:0>: Architecture Type bits         00 = MIPS32         bit 12-10       AR<2:0>: Architecture Revision Level bits         001 = MIPS32 Release 2         bit 9-7       MT<2:0>: MMU Type bits         001 = MIPS32 Release 2         bit 6-3       Unimplemented: Read as '0'         bit 6-3       Unimplemented: Read as '0'         bit 2-0       K0<2:0>: Kseg0 Coherency Algorithm bits         011 = Cacheable, non-coherent, write-back, write allocate         010 = Uncached         001 = Cacheable, non-coherent, write-through, write allocate         001 = Cacheable, non-coherent, write-through, no write allocate         000 = Cacheable, non-coherent, write-through, no write allocate         001 = Cacheable, non-coherent, write-through, no write allocate         001 = Cacheable, non-coherent, write-through, no write allocate         000 = Cacheable, non-coherent, write-through, no write allocate         001 = Cacheable, non-coherent, write-through, no write allocate         000 = Cacheable, non-coherent, write-through, no write allocate <t< td=""><td>bit 20</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                           | bit 20    |                                                                                                                                                                       |

| 10 = Merging is allowed         bit 16       BM: Burst Mode bit         0 = Burst order is sequential         bit 15       BE: Endian Mode bit         0 = Little-endian         bit 14-13       AT<1:0>: Architecture Type bits         00 = MIPS32         bit 12-10       AR<2:0>: Architecture Revision Level bits         001 = MIPS32 Release 2         bit 9-7       MT<2:0>: MMU Type bits         001 = M-Class MPU Microprocessor core uses a TLB-based MMU         bit 2-0       K0<2:0>: Kseg0 Coherency Algorithm bits         011 = Cacheable, non-coherent, write-back, write allocate         010 = Uncached         001 = Cacheable, non-coherent, write-through, no write allocate         000                                                                                                                                                                                                                                                                                                                                                                                                   | bit 19    | Unimplemented: Read as '0'                                                                                                                                            |

| <ul> <li>0 = Burst order is sequential</li> <li>bit 15 BE: Endian Mode bit</li> <li>0 = Little-endian</li> <li>bit 14-13 AT&lt;1:0&gt;: Architecture Type bits</li> <li>00 = MIPS32</li> <li>bit 12-10 AR&lt;2:0&gt;: Architecture Revision Level bits</li> <li>001 = MIPS32 Release 2</li> <li>bit 9-7 MT&lt;2:0&gt;: MMU Type bits</li> <li>001 = M-Class MPU Microprocessor core uses a TLB-based MMU</li> <li>bit 6-3 Unimplemented: Read as '0'</li> <li>bit 2-0 K0&lt;2:0&gt;: Kseg0 Coherency Algorithm bits</li> <li>011 = Cacheable, non-coherent, write-back, write allocate</li> <li>001 = Cacheable, non-coherent, write-through, write allocate</li> <li>000 = Cacheable, non-coherent, write-through, no write allocate</li> <li>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 18-17 | 0                                                                                                                                                                     |

| <ul> <li>0 = Little-endian</li> <li>bit 14-13 AT&lt;1:0&gt;: Architecture Type bits<br/>00 = MIPS32</li> <li>bit 12-10 AR&lt;2:0&gt;: Architecture Revision Level bits<br/>001 = MIPS32 Release 2</li> <li>bit 9-7 MT&lt;2:0&gt;: MMU Type bits<br/>001 = M-Class MPU Microprocessor core uses a TLB-based MMU</li> <li>bit 6-3 Unimplemented: Read as '0'</li> <li>bit 2-0 K0&lt;2:0&gt;: Kseg0 Coherency Algorithm bits<br/>011 = Cacheable, non-coherent, write-back, write allocate<br/>010 = Uncached<br/>001 = Cacheable, non-coherent, write-through, write allocate<br/>000 = Cacheable, non-coherent, write-through, no write allocate<br/>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 16    |                                                                                                                                                                       |

| <ul> <li>00 = MIPS32</li> <li>bit 12-10 AR&lt;2:0&gt;: Architecture Revision Level bits<br/>001 = MIPS32 Release 2</li> <li>bit 9-7 MT&lt;2:0&gt;: MMU Type bits<br/>001 = M-Class MPU Microprocessor core uses a TLB-based MMU</li> <li>bit 6-3 Unimplemented: Read as '0'</li> <li>bit 2-0 K0&lt;2:0&gt;: Kseg0 Coherency Algorithm bits<br/>011 = Cacheable, non-coherent, write-back, write allocate<br/>010 = Uncached<br/>001 = Cacheable, non-coherent, write-through, write allocate<br/>000 = Cacheable, non-coherent, write-through, no write allocate<br/>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 15    |                                                                                                                                                                       |

| <ul> <li>001 = MIPS32 Release 2</li> <li>bit 9-7 MT&lt;2:0&gt;: MMU Type bits<br/>001 = M-Class MPU Microprocessor core uses a TLB-based MMU</li> <li>bit 6-3 Unimplemented: Read as '0'</li> <li>bit 2-0 K0&lt;2:0&gt;: Kseg0 Coherency Algorithm bits<br/>011 = Cacheable, non-coherent, write-back, write allocate<br/>010 = Uncached<br/>001 = Cacheable, non-coherent, write-through, write allocate<br/>000 = Cacheable, non-coherent, write-through, no write allocate<br/>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 14-13 |                                                                                                                                                                       |

| <ul> <li>001 = M-Class MPU Microprocessor core uses a TLB-based MMU</li> <li>bit 6-3 Unimplemented: Read as '0'</li> <li>bit 2-0 K0&lt;2:0&gt;: Kseg0 Coherency Algorithm bits</li> <li>011 = Cacheable, non-coherent, write-back, write allocate</li> <li>010 = Uncached</li> <li>001 = Cacheable, non-coherent, write-through, write allocate</li> <li>000 = Cacheable, non-coherent, write-through, no write allocate</li> <li>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 12-10 |                                                                                                                                                                       |

| bit 2-0 <b>K0&lt;2:0&gt;:</b> Kseg0 Coherency Algorithm bits<br>011 = Cacheable, non-coherent, write-back, write allocate<br>010 = Uncached<br>001 = Cacheable, non-coherent, write-through, write allocate<br>000 = Cacheable, non-coherent, write-through, no write allocate<br>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 9-7   |                                                                                                                                                                       |

| <ul> <li>011 = Cacheable, non-coherent, write-back, write allocate</li> <li>010 = Uncached</li> <li>001 = Cacheable, non-coherent, write-through, write allocate</li> <li>000 = Cacheable, non-coherent, write-through, no write allocate</li> <li>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 6-3   | Unimplemented: Read as '0'                                                                                                                                            |

| 000 = Cacheable, non-coherent, write-through, no write allocate<br>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 2-0   | 011 = Cacheable, non-coherent, write-back, write allocate                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | 000 = Cacheable, non-coherent, write-through, no write allocate<br>All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                                                                                                                                                       |

is

| REGISTER 3-9: | FENR: FLOATING POINT EXCEPTIONS AND MODES ENABLE REGISTER; |

|---------------|------------------------------------------------------------|

|               | CP1 REGISTER 28                                            |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |   |  |   |   |   |  |  |   |   |   |   |   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|---|--|---|---|---|--|--|---|---|---|---|---|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |   |  |   |   |   |  |  |   |   |   |   |   |

| 31:24        | —                 | —                 |                   |                   |                   |                   | _                | _                |   |  |   |   |   |  |  |   |   |   |   |   |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |   |  |   |   |   |  |  |   |   |   |   |   |

| 23:16        | —                 | —                 | -                 | —                 | -                 | _                 | _                | _                |   |  |   |   |   |  |  |   |   |   |   |   |

|              | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |   |  |   |   |   |  |  |   |   |   |   |   |

| 15:8         |                   |                   |                   |                   | ENABLES<4:1>      |                   |                  |                  |   |  |   |   |   |  |  |   |   |   |   |   |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                | _ |  | _ | _ | _ |  |  | _ | V | Z | 0 | U |

|              | R/W-x             | U-0               | U-0               | U-0               | U-0               | R-x               | R/W-x            | R/W-x            |   |  |   |   |   |  |  |   |   |   |   |   |

| 7:0          | ENABLES<0>        |                   |                   |                   |                   | FS                | RM<1:0>          |                  |   |  |   |   |   |  |  |   |   |   |   |   |

|              | I                 |                   | _                 | _                 | _                 | гð                |                  |                  |   |  |   |   |   |  |  |   |   |   |   |   |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-12 Unimplemented: Read as '0'

bit 11-7 ENABLES<4:0>: FPU Exception Enable bits

These bits control whether or not a trap is taken when an IEEE exception condition occurs for any of the five conditions. The trap occurs when both an enable bit and its corresponding cause bit are set either during an FPU arithmetic operation or by moving a value to the FCSR or one of its alternative representations.

- bit 11 V: Invalid Operation bit

- bit 10 Z: Divide-by-Zero bit

- bit 9 O: Overflow bit

- bit 8 **U:** Underflow bit

- bit 7 I: Inexact bit

- bit 6-3 Unimplemented: Read as '0'

- bit 2 FS: Flush to Zero control bit

1 = Denormal input operands are flushed to zero. Tiny results are flushed to either zero or the applied format's smallest normalized number (MinNorm) depending on the rounding mode settings.

0 = Denormal input operands result in an Unimplemented Operation exception.

- bit 1-0 RM<1:0>: Rounding Mode control bits

- 11 = Round towards Minus Infinity  $(-\infty)$

- 10 = Round towards Plus Infinity (+  $\infty$ )

- 01 = Round toward Zero (0)

- 00 = Round to Nearest

#### REGISTER 4-9: SBTxRDy: SYSTEM BUS TARGET 'x' REGION 'y' READ PERMISSIONS REGISTER ('x' = 0-13; 'y' = 0-8)

|              |                   |                   |                   | / /               |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 |                   | —                 | _                 |                   | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-1             | R/W-1            | R/W-1            |

| 7:0          |                   |                   |                   |                   | GROUP3            | GROUP2            | GROUP1           | GROUP0           |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

- bit 31-4 Unimplemented: Read as '0'

- bit 3 Group3: Group3 Read Permissions bits

- 1 = Privilege Group 3 has read permission

- 0 = Privilege Group 3 does not have read permission

- bit 2 Group2: Group2 Read Permissions bits

- 1 = Privilege Group 2 has read permission

- 0 = Privilege Group 2 does not have read permission

#### bit 1 Group1: Group1 Read Permissions bits

- 1 = Privilege Group 1 has read permission

- 0 = Privilege Group 1 does not have read permission

- bit 0 **Group0:** Group0 Read Permissions bits

- 1 = Privilege Group 0 has read permission

- 0 = Privilege Group 0 does not have read permission

#### Note 1: Refer to Table 4-6 for the list of available targets and their descriptions.

2: For some target regions, certain bits in this register are read-only with preset values. See Table 4-6 for more information.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MZ EF devices contain an internal Flash program memory for executing user code, which includes the following features:

- Two Flash banks for live update support

- Dual boot support

- Write protection for program and boot Flash

- ECC support

There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 52. "Flash Program Memory with Support for Live Update"** (DS60001193) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which is available for download from the Microchip web site (www.microchip.com).

Note: In PIC32MZ EF devices, the Flash page size is 16 KB (4K IW) and the row size is 2 KB (512 IW).

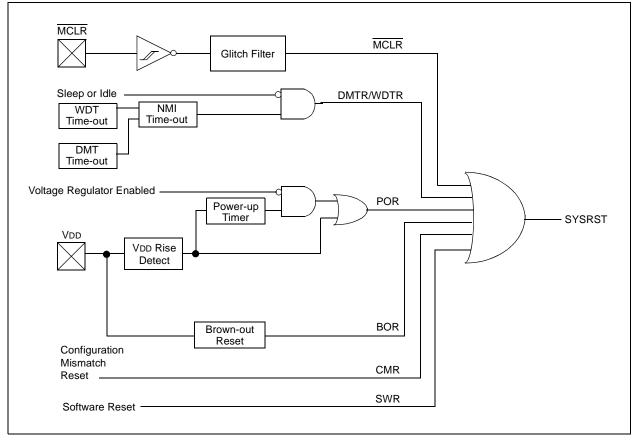

# 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7**. "**Resets**" (DS60001118) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The device Reset sources are as follows:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

- Deadman Timer Reset (DMTR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

# FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

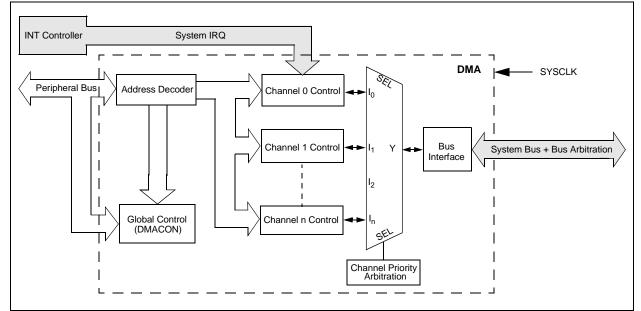

# 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Direct Memory Access (DMA) Controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the device such as SPI, UART, PMP, etc., or memory itself.

The following are key features of the DMA Controller:

- Eight identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

### FIGURE 10-1: DMA BLOCK DIAGRAM

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Up to 2-byte Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent error address accessed by a DMA channel

- Most recent DMA channel to transfer data

- CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

# REGISTER 10-9: DCHxINT: DMA CHANNEL x INTERRUPT CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

### bit 31-24 Unimplemented: Read as '0'

| bit 23   | CHSDIE: Channel Source Done Interrupt Enable bit                                        |

|----------|-----------------------------------------------------------------------------------------|

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 22   | CHSHIE: Channel Source Half Empty Interrupt Enable bit                                  |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 21   | CHDDIE: Channel Destination Done Interrupt Enable bit                                   |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 20   | CHDHIE: Channel Destination Half Full Interrupt Enable bit                              |

|          | 1 = Interrupt is enabled                                                                |

| 1.11.40  | 0 = Interrupt is disabled                                                               |

| bit 19   | CHBCIE: Channel Block Transfer Complete Interrupt Enable bit                            |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>         |

| bit 18   |                                                                                         |

| DIL TO   | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled |

|          | 0 = Interrupt is disabled                                                               |

| bit 17   | CHTAIE: Channel Transfer Abort Interrupt Enable bit                                     |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 16   | CHERIE: Channel Address Error Interrupt Enable bit                                      |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 15-8 | Unimplemented: Read as '0'                                                              |

| bit 7    | CHSDIF: Channel Source Done Interrupt Flag bit                                          |

|          | 1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)                  |

|          | 0 = No interrupt is pending                                                             |

| bit 6    | CHSHIF: Channel Source Half Empty Interrupt Flag bit                                    |

|          | 1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)           |

|          | 0 = No interrupt is pending                                                             |

|          |                                                                                         |

### REGISTER 11-3: USBCSR2: USB CONTROL STATUS REGISTER 2 (CONTINUED)

- bit 19 SOFIF: Start of Frame Interrupt bit 1 = A new frame has started 0 = No start of frame detected bit 18 **RESETIF:** Reset/Babble Interrupt bit 1 = In Host mode, indicates babble is detected. In Device mode, indicates reset signaling is detected on the bus. 0 = No reset/babble detected bit 17 **RESUMEIF:** Resume Interrupt bit 1 = Resume signaling is detected on the bus while USB module is in Suspend mode 0 = No Resume signaling detected bit 16 SUSPIF: Suspend Interrupt bit 1 = Suspend signaling is detected on the bus (Device mode) 0 = No suspend signaling detected bit 15-8 Unimplemented: Read as '0' bit 7-1 EP7RXIE:EP1RXIE: Endpoint 'n' Receive Interrupt Enable bit 1 = Receive interrupt is enabled for this endpoint 0 = Receive interrupt is not enabled

- bit 0 Unimplemented: Read as '0'

| REGISTER 11-6: | USBIE0CSR2: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 2 |

|----------------|------------------------------------------------------------|

|                | (ENDPOINT 0)                                               |

|              |                   |                   | /                 |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | _                 | _                 | _                 |                   | NAKLIM<4:0>       |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | SPEED<1:0>        |                   | _                 | —                 | —                 |                   | —                | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | _                 | _                 | _                 | —                 | —                 | _                 | _                | —                |  |  |  |

| 7.0          | U-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | _                 |                   |                   |                   | RXCNT<6:0>        |                   |                  |                  |  |  |  |

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 NAKLIM<4:0>: Endpoint 0 NAK Limit bits

The number of frames/microframes (Hi-Speed transfers) after which Endpoint 0 should time-out on receiving a stream of NAK responses.

- bit 23-22 SPEED<1:0>: Operating Speed Control bits

- 11 = Low-Speed

- 10 = Full-Speed

- 01 = Hi-Speed

- 00 = Reserved

- bit 21-7 Unimplemented: Read as '0'

- bit 6-0 **RXCNT<6:0>:** Receive Count bits

The number of received data bytes in the Endpoint 0 FIFO. The value returned changes as the contents of the FIFO change and is only valid while RXPKTRDY is set.

# 27.1 RNG Control Registers

# TABLE 27-2: RANDOM NUMBER GENERATOR (RNG) REGISTER MAP

| ess                         |                  | 6         |                 | Bits  |       |       |          |       |        |        |       |      |      |        |         |      |      |      |            |

|-----------------------------|------------------|-----------|-----------------|-------|-------|-------|----------|-------|--------|--------|-------|------|------|--------|---------|------|------|------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15           | 30/14 | 29/13 | 28/12 | 27/11    | 26/10 | 25/9   | 24/8   | 23/7  | 22/6 | 21/5 | 20/4   | 19/3    | 18/2 | 17/1 | 16/0 | All Resets |

| 6000                        | RNGVER           | 31:16     |                 |       |       |       |          |       |        | ID<15  | :0>   |      |      |        |         |      |      |      | xxxx       |

| 0000                        | KNOVER           | 15:0      |                 |       |       | VERS  | ION<7:0> |       |        |        |       |      |      | REVISI | ON<7:0> |      | -    |      | xxxx       |

| 6004                        | RNGCON           | 31:16     | —               | —     | —     | —     | —        | _     | _      |        | —     | —    | —    | —      | —       | —    | —    | —    | 0000       |

| 0004                        | Rivecon          | 15:0      | —               | —     | —     | LOAD  | TRNGMODE | CONT  | PRNGEN | TRNGEN |       |      |      | PLE    | N<7:0>  |      |      |      | 0064       |

| 6008                        | RNGPOLY1         | 31:16     |                 |       |       |       |          |       |        | POLY<3 | 1.0~  |      |      |        |         |      |      |      | FFFF       |

| 0000                        | KNOI OEI I       | 15:0      |                 |       |       |       |          |       |        | TOLICO | 11.02 |      |      |        |         |      |      |      | 0000       |

| 600C                        | RNGPOLY2         | 31:16     |                 |       |       |       |          |       |        | POLY<3 | 1.0>  |      |      |        |         |      |      |      | FFFF       |

| 0000                        |                  | 15:0      |                 |       |       |       |          |       |        | TOLICO | 11.02 |      |      |        |         |      |      |      | 0000       |

| 6010                        | RNGNUMGEN1       | 31:16     |                 |       |       |       |          |       |        | RNG<3  | 1.0>  |      |      |        |         |      |      |      | FFFF       |

| 0010                        | RIGHUNGEN        | 15:0      |                 |       |       |       |          |       |        | NNO<0  | 1.02  |      |      |        |         |      |      |      | FFFF       |

| 6014                        | RNGNUMGEN2       | 31:16     |                 |       |       |       |          |       |        | RNG<3  | 1.0>  |      |      |        |         |      |      |      | FFFF       |

| 0014                        | RINGINOWIGEINZ   | 15:0      |                 |       |       |       |          |       |        | KNG<3  | 1.0>  |      |      |        |         |      |      |      | FFFF       |

| 6018                        | RNGSEED1         | 31:16     |                 |       |       |       |          |       |        | SEED<3 | 21.0  |      |      |        |         |      |      |      | 0000       |

| 0010                        | RINGSEEDT        | 15:0      |                 |       |       |       |          |       |        | SEED<3 | 51.0> |      |      |        |         |      |      |      | 0000       |

| 601C                        | RNGSEED2         | 31:16     | 6<br>SEED<31:0> |       |       |       |          |       |        |        |       | 0000 |      |        |         |      |      |      |            |

| 0010                        | NINGSEED2        | 15:0      |                 |       |       |       |          |       |        | SEED<3 | 01.0> |      |      |        |         |      |      |      | 0000       |

| 6020                        | RNGCNT           | 31:16     | —               | —     | —     | —     | —        | —     | —      | —      | —     | —    |      | —      | —       | —    | —    | —    | 0000       |

| 6020                        | RINGCINI         | 15:0      | _               |       |       |       |          |       |        |        |       | 0000 |      |        |         |      |      |      |            |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Bit Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|-----------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 04.04     | R/W-0                 |

| 31:24     | DIFF31 <sup>(1)</sup> | SIGN31 <sup>(1)</sup> | DIFF30 <sup>(1)</sup> | SIGN30 <sup>(1)</sup> | DIFF29 <sup>(1)</sup> | SIGN29 <sup>(1)</sup> | DIFF28 <sup>(1)</sup> | SIGN28 <sup>(1)</sup> |

| 00.40     | R/W-0                 |

| 23:16     | DIFF27 <sup>(1)</sup> | SIGN27 <sup>(1)</sup> | DIFF26 <sup>(1)</sup> | SIGN26 <sup>(1)</sup> | DIFF25 <sup>(1)</sup> | SIGN25 <sup>(1)</sup> | DIFF24 <sup>(1)</sup> | SIGN24 <sup>(1)</sup> |

| 45-0      | R/W-0                 |

| 15:8      | DIFF23 <sup>(1)</sup> | SIGN23 <sup>(1)</sup> | DIFF22 <sup>(1)</sup> | SIGN22 <sup>(1)</sup> | DIFF21 <sup>(1)</sup> | SIGN21 <sup>(1)</sup> | DIFF20 <sup>(1)</sup> | SIGN20 <sup>(1)</sup> |

| 7.0       | R/W-0                 |

| 7:0       | DIFF19 <sup>(1)</sup> | SIGN19 <sup>(1)</sup> | DIFF18                | SIGN18                | DIFF17                | SIGN17                | DIFF16                | SIGN16                |

# REGISTER 28-6: ADCIMCON2: ADC INPUT MODE CONTROL REGISTER 2

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

| bit 31                     | DIFF31: AN31 Mode bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | 1 = AN31 is using Differential mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                            | 0 = AN31 is using Single-ended mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 30                     | SIGN31: AN31 Signed Data Mode bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                            | 1 = AN31 is using Signed Data mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                            | 0 = AN31 is using Unsigned Data mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 29                     | DIFF30: AN30 Mode bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                            | 1 = AN30 is using Differential mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                            | 0 = AN30 is using Single-ended mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 28                     | <b>SIGN30:</b> AN30 Signed Data Mode bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                            | 1 = AN30 is using Signed Data mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |