Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 97                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                  |

| Supplier Device Package    | 124-VTLA (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efg124t-i-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-22: JTAG, TRACE, AND PROGRAMMING/DEBUGGING PINOUT I/O DESCRIPTIONS

|          |                        | Pin Nu          | mber            |                          |             |                |                                                                            |  |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|----------------------------------------------------------------------------|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                                                |  |  |

|          |                        |                 |                 |                          | J٦          | ΓAG            |                                                                            |  |  |

| TCK      | 27                     | 38              | B21             | 56                       | I           | ST             | JTAG Test Clock Input Pin                                                  |  |  |

| TDI      | 28                     | 39              | A26             | 57                       | I           | ST             | JTAG Test Data Input Pin                                                   |  |  |

| TDO      | 24                     | 40              | B22             | 58                       | 0           | _              | JTAG Test Data Output Pin                                                  |  |  |

| TMS      | 23                     | 17              | A11             | 22                       | I           | ST             | JTAG Test Mode Select Pin                                                  |  |  |

|          |                        |                 |                 |                          | Tr          | ace            |                                                                            |  |  |

| TRCLK    | 57                     | 89              | A61             | 129                      | 0           | _              | Trace Clock                                                                |  |  |

| TRD0     | 58                     | 97              | B55             | 141                      | 0           | _              | Trace Data bits 0-3                                                        |  |  |

| TRD1     | 61                     | 96              | A65             | 140                      | 0           | _              |                                                                            |  |  |

| TRD2     | 62                     | 95              | B54             | 139                      | 0           | _              |                                                                            |  |  |

| TRD3     | 63                     | 90              | B51             | 130                      | 0           | _              |                                                                            |  |  |

|          |                        |                 |                 | Pro                      | grammir     | ng/Debuggi     | ing                                                                        |  |  |

| PGED1    | 16                     | 25              | A18             | 36                       | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1             |  |  |

| PGEC1    | 15                     | 24              | A17             | 35                       | I           | ST             | Clock input pin for Programming/Debugging Communication Channel 1          |  |  |

| PGED2    | 18                     | 27              | A19             | 38                       | I/O         | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 2          |  |  |

| PGEC2    | 17                     | 26              | B14             | 37                       | I           | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 2       |  |  |

| MCLR     | 9                      | 15              | A10             | 20                       | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device. |  |  |

egend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input

O = Output

P = Power I = Input

PPS = Peripheral Pin Select

|   | c | , |

|---|---|---|

|   | Q | Ō |

|   | č | " |

|   | ۲ | 3 |

|   | - | 3 |

| ĺ | Ň | š |

|   | c | 2 |

|   | è | 5 |

| , | ٥ | Š |

|   | a | 5 |

|   | ç | o |

| 1 | u | v |

TABLE 4-14: SYSTEM BUS TARGET 6 REGISTER MAP

| ess                         |                  |           |                           |       |       |          |          |       |          |      | Bits     |      |          |      |        |        |        |        |               |

|-----------------------------|------------------|-----------|---------------------------|-------|-------|----------|----------|-------|----------|------|----------|------|----------|------|--------|--------|--------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15                     | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9     | 24/8 | 23/7     | 22/6 | 21/5     | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All<br>Resets |

| 9820                        | SBT6ELOG1        | 31:16     | MULTI                     | _     | _     | _        |          | CODE  | <3:0>    |      | _        | _    | _        | _    | _      | _      | _      | _      | 0000          |

| 3020                        | OBTOLLOGT        | 15:0      | INITID<7:0> REGION<3:0> — |       |       |          | _        | С     | MD<2:0>  |      | 0000     |      |          |      |        |        |        |        |               |

| 9824                        | SBT6ELOG2        | 31:16     | _                         |       |       |          | _        | _     | _        | _    | _        | _    | _        | _    | _      | _      | _      | 0000   |               |

| 3024                        | OBTOLLOGZ        | 15:0      | _                         | _     | _     | _        | _        | _     | _        | _    | _        | _    | _        | _    | _      | _      | GROU   | P<1:0> | 0000          |

| 9828                        | SBT6ECON         | 31:16     | _                         | _     | _     | _        |          | _     | _        | ERRP | _        | _    | _        | _    | _      | _      | _      | _      | 0000          |

| 3020                        | SBIOLOGIA        | 15:0      | _                         | _     | _     | _        |          | _     | _        |      | _        | _    | _        | _    | _      | _      | _      | _      | 0000          |

| 9830                        | SBT6ECLRS        | 31:16     | _                         | _     | _     | _        | _        | _     | _        | _    | _        | _    | _        | _    | _      | _      | _      | _      | 0000          |

| 3000                        | OBTOLOLINO       | 15:0      | _                         | _     | _     | _        | _        | _     | _        | _    | _        | _    | _        | _    | _      | _      | _      | CLEAR  | 0000          |

| 9838                        | SBT6ECLRM        | 31:16     | _                         | _     | _     | _        | _        | _     | _        | _    | _        | _    | _        | _    | _      | _      | _      | _      | 0000          |

| 0000                        | OBTOLOLINI       | 15:0      | _                         | _     | _     | _        | _        | _     | _        | _    | _        | _    | _        | _    | _      | _      | _      | CLEAR  | 0000          |

| 9840                        | SBT6REG0         | 31:16     |                           |       |       |          |          |       | 1        | BA   | SE<21:6> |      |          |      |        |        |        |        | xxxx          |

| 00.0                        |                  | 15:0      |                           | •     | BA    | \SE<5:0> |          |       | PRI      | _    |          |      | SIZE<4:0 | >    |        | _      | _      | _      | xxxx          |

| 9850                        | SBT6RD0          | 31:16     | _                         | _     | _     | _        | _        | _     |          | _    |          |      |          |      | _      | _      | _      | _      | xxxx          |

|                             |                  | 15:0      | _                         | _     | _     | _        | _        | _     |          | _    |          |      |          |      | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 9858                        | SBT6WR0          | 31:16     | _                         | _     | _     | _        | _        | _     |          | _    |          |      |          |      | _      | _      | _      | _      | xxxx          |

|                             |                  | 15:0      | _                         | _     | _     | _        | _        | _     | _        | _    | _        | _    | _        | _    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 9860                        | SBT6REG1         | 31:16     |                           |       |       |          |          |       |          | BA   | SE<21:6> |      |          |      |        | I      |        | 1      | xxxx          |

|                             |                  | 15:0      |                           |       | BA    | \SE<5:0> |          | I     | PRI      | _    |          |      |          |      | _      | _      | xxxx   |        |               |

| 9870                        | SBT6RD1          | 31:16     | _                         | _     | _     |          |          |       |          |      |          |      |          |      | _      | _      | _      | _      | xxxx          |

|                             | - ***-           | 15:0      | _                         | _     | _     | _        | _        | _     | _        | _    | _        | _    | _        | _    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 9878                        | SBT6WR1          | 31:16     | _                         | _     | _     | _        | _        | _     | _        | _    | _        | _    | _        | _    | _      | _      | _      | _      | xxxx          |

|                             |                  | 15:0      | _                         | _     | _     | _        | <u> </u> | _     | <u> </u> |      | _        | _    |          |      | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

# REGISTER 4-3: SBTxELOG1: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 1 ('x' = 0-13) (CONTINUED)

bit 7-4 REGION<3:0>: Requested Region Number bits

1111 - 0000 = Target's region that reported a permission group violation

bit 3 Unimplemented: Read as '0'

bit 2-0 CMD<2:0>: Transaction Command of the Requester bits

111 = Reserved

110 = Reserved

101 = Write (a non-posted write)

100 = Reserved

011 = Read (a locked read caused by a Read-Modify-Write transaction)

010 = Read 001 = Write 000 = Idle

**Note:** Refer to Table 4-6 for the list of available targets and their descriptions.

| ⊚<br>2    |

|-----------|

| 2         |

| 2015-2016 |

| 201       |

| 6         |

| Microchip |

| Technolog |

| 응         |

| TABLE 7-3: INTERRUPT REGISTER | MAP (CONTINUED) |

|-------------------------------|-----------------|

|-------------------------------|-----------------|

| ress<br>()                  |                                 | ω         |       |       |       |       |       | •     |      | Bi         | ts   |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 05FC                        | OFF047                          | 15:0      |       |       | •     | •     |       | •     |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0000                        | OFF048                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0600                        | OFF046                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0604                        | OFF049                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | -    | _    | _    | -    | _    | _    | VOFF< | 17:16> | 0000       |

| 0004                        | OFF049                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | ı      | 0000       |

| 0600                        | OFF050                          | 31:16     | _     | _     | _     | _     | 1     | _     | 1    | _          | _    | -    | 1    | I    | _    | 1    | VOFF< | 17:16> | 0000       |

| 0008                        | OFF030                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | I      | 0000       |

| 0600                        | OFF051                          | 31:16     | -     | _     | _     | _     |       | _     | ı    | _          | -    | -    | -    | ı    | _    | -    | VOFF< | 17:16> | 0000       |

| 0000                        | OFFUST                          | 15:0      |       |       | _     | _     |       | _     |      | VOFF<15:1> |      |      |      |      |      |      |       | -      | 0000       |

| 0610                        | OFF052                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | -    | _    | _    | -    | _    | _    | VOFF< | 17:16> | 0000       |

| 0010                        | OFF032                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | ı      | 0000       |

| 0644                        | OFF053                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | -    | _    | _    | VOFF< | 17:16> | 0000       |

| 0614                        | OFF053                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 0619                        | OFF054                          | 31:16     | -     | _     | _     | _     |       | _     | ı    | _          | -    | -    | -    | ı    | _    | -    | VOFF< | 17:16> | 0000       |

| 0010                        | OFF034                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0610                        | OFF055                          | 31:16     | _     | _     | _     | _     | -     | _     | -    | _          | _    | _    | -    |      | _    | -    | VOFF< | 17:16> | 0000       |

| 0610                        | OFFUSS                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | ı      | 0000       |

| 0620                        | OFF056                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | -    | _    | _    | VOFF< | 17:16> | 0000       |

| 0020                        | OFF030                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 0624                        | OFF057                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0024                        | OFF037                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | ı      | 0000       |

| 0620                        | OFF058                          | 31:16     | _     | _     | _     | _     | -     | _     | -    | _          | _    | _    | -    |      | _    | -    | VOFF< | 17:16> | 0000       |

| 0626                        | OFF036                          | 15:0      |       | •     | •     | •     |       | -     |      | VOFF<15:1> |      |      |      |      | •    |      |       | ı      | 0000       |

| 0620                        | OFF059                          | 31:16     | _     | _     | _     | _     | 1     | _     | 1    | _          | _    | -    | 1    | I    | _    | 1    | VOFF< | 17:16> | 0000       |

| 0020                        | 01.1009                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 0620                        | OFF060                          | 31:16     | _     | _     |       | _     |       | _     | _    | =          | _    | _    |      | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0030                        | OI FUUU                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0624                        | OFF061                          | 31:16     | _     | _     |       | _     | _     | _     | _    |            | _    | _    |      |      | _    | _    | VOFF< | 17:16> | 0000       |

| 0034                        | 01.1001                         | 15:0      |       |       |       | ·     |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | ı      | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

Point Unit (EF) Family

- 3: This bit or register is not available on devices without a CAN module.

- This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

- 6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

- 7: This bit or register is not available on devices without a Crypto module.

- This bit or register is not available on 124-pin devices.

# REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7)

|              |                   | · -               |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | AUTOSET           | ISO               | MODE              | DMADEGEN          | FRCDATTG          | DMAREOMD          | _                | _                |  |  |  |  |

|              | AUTOSET           | _                 | MODE              | DIVIAREQEIN       | FREDATIG          | DIVIAREQIVID      | DATAWEN          | DATATGGL         |  |  |  |  |

|              | R/W-0, HS         | R/W-0, HC         | R/W-0, HS         | R/W-0             | R/W-0             | R/W-0, HS         | R/W-0            | R/W-0, HC        |  |  |  |  |

| 23:16        | INCOMPTX          | CLRDT             | SENTSTALL         | SENDSTALL         | FLUSH             | UNDERRUN          | FIFONE           | TXPKTRDY         |  |  |  |  |

|              | NAKTMOUT          | CLKDI             | RXSTALL           | SETUPPKT          | FLUSH             | ERROR             | FIFOINE          | INFRIRDI         |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   | MULT<4:0>         |                   |                   | T.                | XMAXP<10:8:      | >                |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | TXMAXP<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31 AUTOSET: Auto Set Control bit

- 1 = TXPKTRDY will be automatically set when data of the maximum packet size (value in TXMAXP) is loaded into the TX FIFO. If a packet of less than the maximum packet size is loaded, then TXPKTRDY will have to be set manually.

- 0 = TXPKTRDY must be set manually for all packet sizes

- bit 30 ISO: Isochronous TX Endpoint Enable bit (Device mode)

- 1 = Enables the endpoint for Isochronous transfers

- 0 = Disables the endpoint for Isochronous transfers and enables it for Bulk or Interrupt transfers.

This bit only has an effect in Device mode. In Host mode, it always returns zero.

- bit 29 MODE: Endpoint Direction Control bit

- 1 = Endpoint is TX

- 0 = Endpoint is RX

This bit only has any effect where the same endpoint FIFO is used for both TX and RX transactions.

- bit 28 DMAREQEN: Endpoint DMA Request Enable bit

- 1 = DMA requests are enabled for this endpoint

- 0 = DMA requests are disabled for this endpoint

- bit 27 FRCDATTG: Force Endpoint Data Toggle Control bit

- 1 = Forces the endpoint data toggle to switch and the data packet to be cleared from the FIFO, regardless of whether an ACK was received.

- 0 = No forced behavior

- bit 26 DMAREQMD: Endpoint DMA Request Mode Control bit

- 1 = DMA Request Mode 1

- 0 = DMA Request Mode 0

This bit must not be cleared either before or in the same cycle as the above DMAREQEN bit is cleared.

- bit 25 **DATAWEN:** Data Toggle Write Enable bit (Host mode)

- 1 = Enable the current state of the TX Endpoint data toggle (DATATGGL) to be written

- 0 = Disables writing the DATATGGL bit

- bit 24 DATATGGL: Data Toggle Control bit (Host mode)

When read, this bit indicates the current state of the TX Endpoint data toggle. If DATAWEN = 1, this bit may be written with the required setting of the data toggle. If DATAWEN = 0, any value written to this bit is ignored.

# REGISTER 11-9: USBIENCSR1: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 1 (ENDPOINT 1-7) (CONTINUED)

- bit 26 **DATATWEN:** Data Toggle Write Enable Control bit (*Host mode*)

- 1 = DATATGGL can be written

- 0 = DATATGGL is not writable

- bit 25 **DATATGGL:** Data Toggle bit (Host mode)

When read, this bit indicates the current state of the endpoint data toggle.

If DATATWEN = 1, this bit may be written with the required setting of the data toggle.

If DATATWEN = 0, any value written to this bit is ignored.

- bit 24 INCOMPRX: Incomplete Packet Status bit

- 1 = The packet in the RX FIFO during a high-bandwidth Isochronous/Interrupt transfer is incomplete because parts of the data were not received

- 0 = Written by then software to clear this bit

In anything other than Isochronous transfer, this bit will always return 0.

- bit 23 CLRDT: Clear Data Toggle Control bit

- 1 = Reset the endpoint data toggle to 0

- 0 = Leave endpoint data toggle alone

- bit 22 SENTSTALL: STALL Handshake Status bit (Device mode)

- 1 = STALL handshake is transmitted

- 0 = Written by the software to clear this bit

#### **RXSTALL:** STALL Handshake Receive Status bit (*Host mode*)

- 1 = A STALL handshake has been received. An interrupt is generated.

- 0 = Written by the software to clear this bit

- bit 21 **SENDSTALL:** STALL Handshake Control bit (*Device mode*)

- 1 = Issue a STALL handshake

- 0 = Terminate stall condition

#### REQPKT: IN Transaction Request Control bit (Host mode)

- 1 = Request an IN transaction.

- 0 = No request

This bit is cleared when RXPKTRDY is set.

- bit 20 FLUSH: Flush FIFO Control bit

- 1 = Flush the next packet to be read from the endpoint RX FIFO. The FIFO pointer is reset and the RXPKTRDY bit is cleared. This should only be used when RXPKTRDY is set. If the FIFO is double-buffered, FLUSH may need to be set twice to completely clear the FIFO.

- 0 = Normal FIFO operation

This bit is automatically cleared.

- bit 19 **DATAERR:** Data Packet Error Status bit (*Device mode*)

- 1 = The data packet has a CRC or bit-stuff error.

- 0 = No data error

This bit is cleared when RXPKTRDY is cleared. This bit is only valid when the endpoint is operating in ISO mode. In Bulk mode, it always returns zero.

#### **DERRNAKT:** Data Error/NAK Time-out Status bit (*Host mode*)

- 1 = The data packet has a CRC or bit-stuff error. In Bulk mode, the RX endpoint is halted following the receipt of NAK responses for longer than the time set as the NAK limit.

- 0 = No data or NAK time-out error

TABLE 12-18: PORTH REGISTER MAP FOR 144-PIN DEVICES ONLY

| ess                         | _                               | ø             |               |               |               |               |                |               |              | Bits         |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|---------------|---------------|---------------|---------------|---------------|----------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14         | 29/13         | 28/12         | 27/11          | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0700                        | ANSELH                          | 31:16         | _             | _             | _             | _             | _              | _             |              | _            | _            | _            | _            | ı            | _            | _            | ı            |              | 0000          |

| 0,00                        |                                 | 15:0          | _             | _             |               | _             | _              | _             | _            | _            | _            | ANSH6        | ANSH5        | ANSH4        | _            | _            | ANSH1        | ANSH0        | 0073          |

| 0710                        | TRISH                           | 31:16         | _             | _             | _             | _             | _              | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

|                             |                                 | 15:0          | TRISH15       | TRISH14       | TRISH13       | TRISH12       | TRISH11        | TRISH10       | TRISH9       | TRISH8       | TRISH7       | TRISH6       | TRISH5       | TRISH4       | TRISH3       | TRISH2       | TRISH1       | TRISH0       | FFFF          |

| 0720                        | PORTH                           | 31:16         |               | _             |               | _             | _              | _             | _            | _            | _            | _            | _            | _            |              | _            | _            |              | 0000          |

|                             |                                 | 15:0          | RH15          | RH14          | RH13          | RH12          | RH11           | RH10          | RH9          | RH8          | RH7          | RH6          | RH5          | RH4          | RH3          | RH2          | RH1          | RH0          | XXXX          |

| 0730                        | LATH                            | 31:16         | —<br>LATU45   | —<br>LATU4.4  |               | —<br>LATU40   | —<br>LATI144   | —<br>         | —<br>LATUO   | —<br>LATUO   | —<br>        | —<br>LATUO   | —<br>-       | —<br>. ATI14 | —<br>LATUO   |              | —<br>LATI14  | —<br>LATUS   | 0000          |

|                             |                                 | 15:0<br>31:16 | LATH15        | LATH14        | LATH13        | LATH12        | LATH11         | LATH10        | LATH9        | LATH8        | LATH7        | LATH6        | LATH5        | LATH4        | LATH3        | LATH2        | LATH1        | LATH0        | XXXX          |

| 0740                        | ODCH                            | 15:0          | ODCH15        | ODCH14        | ODCH13        | ODCH12        | ODCH11         | ODCH10        | ODCH9        | ODCH8        | ODCH7        | ODCH6        | ODCH5        | ODCH4        | ODCH3        | ODCH2        | ODCH1        | ODCH0        | 0000          |

|                             |                                 | 31:16         | <u> </u>      | - ODC/114     | —             | —             | —              | —             | — —          | —            | — —          | —            | - ODC113     | -            | —            | - ODC112     | _            | —            | 0000          |

| 0750                        | CNPUH                           | 15:0          | CNPUH15       | CNPUH14       | CNPUH13       | CNPUH12       | CNPUH11        | CNPUH10       | CNPUH9       | CNPUH8       | CNPUH7       | CNPUH6       | CNPUH5       | CNPUH4       | CNPUH3       | CNPUH2       | CNPUH1       |              | 0000          |

|                             |                                 | 31:16         | _             | _             | _             | _             | _              | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0760                        | CNPDH                           | 15:0          | CNPDH15       | CNPDH14       | CNPDH13       | CNPDH12       | CNPDH11        | CNPDH10       | CNPDH9       | CNPDH8       | CNPDH7       | CNPDH6       | CNPDH5       | CNPDH4       | CNPDH3       | CNPDH2       | CNPDH1       | CNPDH0       | 0000          |

|                             |                                 | 31:16         | _             | _             | _             | _             | _              | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0770                        | CNCONH                          | 15:0          | ON            | _             | _             | _             | EDGE<br>DETECT | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0700                        | ONENIII                         | 31:16         | _             | _             | _             | _             | _              | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0780                        | CNENH                           | 15:0          | CNENH15       | CNENH14       | CNENH13       | CNENH12       | CNENH11        | CNENH10       | CNENH9       | CNENH8       | CNENH7       | CNENH6       | CNENH5       | CNENH4       | CNENH3       | CNENH2       | CNENH1       | CNENH0       | 0000          |

|                             |                                 | 31:16         | _             | _             | _             | _             | _              | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0790                        | CNSTATH                         | 15:0          | CN<br>STATH15 | CN<br>STATH14 | CN<br>STATH13 | CN<br>STATH12 | CN<br>STATH11  | CN<br>STATH10 | CN<br>STATH9 | CN<br>STATH8 | CN<br>STATH7 | CN<br>STATH6 | CN<br>STATH5 | CN<br>STATH4 | CN<br>STATH3 | CN<br>STATH2 | CN<br>STATH1 | CN<br>STATH0 | 0000          |

| 07A0                        | CNNEH                           | 31:16         | _             | _             | _             | _             |                | _             | _            | _            | _            | _            |              | _            |              | _            |              | _            | 0000          |

| UTAU                        | CIVINLIT                        | 15:0          | CNNEH15       | CNNEH14       | CNNEH13       | CNNEH12       | CNNEH11        | CNNEH10       | CNNEH9       | CNNEH8       | CNNEH7       | CNNEH6       | CNNEH5       | CNNEH4       | CNNEH3       | CNNEH2       | CNNEH1       | CNNEH0       | 0000          |

| 07B0                        | CNFH                            | 31:16         | _             | _             | _             | _             | _              | _             | _            | _            | _            | _            | _            | _            | _            | _            |              | _            | 0000          |

| 0700                        | 014111                          | 15:0          | CNFH15        | CNFH14        | CNFH13        | CNFH12        | CNFH11         | CNFH10        | CNFH9        | CNFH8        | CNFH7        | CNFH6        | CNFH5        | CNFH4        | CNFH3        | CNFH2        | CNFH1        | CNFH0        | 0000          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

The timer source for each Input Capture module depends on the setting of the ICACLK bit in the CFGCON register. The available configurations are shown in Table 17-1.

TABLE 17-1: TIMER SOURCE CONFIGURATIONS

| Input Capture<br>Module | Timerx     | Timery |  |  |  |  |  |  |  |  |  |

|-------------------------|------------|--------|--|--|--|--|--|--|--|--|--|

| ICACLK (CFGCC           | N<17>) = 0 |        |  |  |  |  |  |  |  |  |  |

| IC1                     | Timer2     | Timer3 |  |  |  |  |  |  |  |  |  |

| •                       | •          | •      |  |  |  |  |  |  |  |  |  |

| •                       | •          | •      |  |  |  |  |  |  |  |  |  |

| •                       | •          | •      |  |  |  |  |  |  |  |  |  |

| IC9                     | Timer2     | Timer3 |  |  |  |  |  |  |  |  |  |

| ICACLK (CFGCC           | N<17>) = 1 |        |  |  |  |  |  |  |  |  |  |

| IC1                     | Timer4     | Timer5 |  |  |  |  |  |  |  |  |  |

| IC2                     | Timer4     | Timer5 |  |  |  |  |  |  |  |  |  |

| IC3                     | Timer4     | Timer5 |  |  |  |  |  |  |  |  |  |

| IC4                     | Timer2     | Timer3 |  |  |  |  |  |  |  |  |  |

| IC5                     | Timer2     | Timer3 |  |  |  |  |  |  |  |  |  |

| IC6                     | Timer2     | Timer3 |  |  |  |  |  |  |  |  |  |

| IC7                     | Timer6     | Timer7 |  |  |  |  |  |  |  |  |  |

| IC8                     | Timer6     | Timer7 |  |  |  |  |  |  |  |  |  |

| IC9                     | Timer6     | Timer7 |  |  |  |  |  |  |  |  |  |

#### **REGISTER 19-3: SPIXSTAT: SPI STATUS REGISTER**

| Bit<br>Range    | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04           | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24 — — RXBUF |                   |                   |                   |                   |                   |                   | 0>               |                  |  |  |

| 00.40           | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16           | _                 | _                 | _                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 45.0            | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |  |

| 15:8            | _                 | _                 | _                 | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |  |  |

| 7.0             | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |

| 7:0             | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | _                 | SPITBF           | SPIRBF           |  |  |

Legend:C = Clearable bitHS = Set in hardwareR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

bit 23-21 Unimplemented: Read as '0'

bit 20-16 TXBUFELM<4:0>: Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

bit 15-13 Unimplemented: Read as '0'

bit 12 FRMERR: SPI Frame Error status bit

1 = Frame error is detected

0 = No Frame error is detected

This bit is only valid when FRMEN = 1.

bit 11 SPIBUSY: SPI Activity Status bit

1 = SPI peripheral is currently busy with some transactions

0 = SPI peripheral is currently idle

bit 10-9 **Unimplemented:** Read as '0'

bit 8 SPITUR: Transmit Under Run bit

1 = Transmit buffer has encountered an underrun condition

0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling/re-enabling the module.

bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

1 = When SPI module shift register is empty

0 = When SPI module shift register is not empty

bit 6 SPIROV: Receive Overflow Flag bit

1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

0 = No overflow has occurred

This bit is set in hardware; can only be cleared (= 0) in software.

bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1)

1 = RX FIFO is empty (CRPTR = SWPTR)

0 = RX FIFO is not empty (CRPTR ≠ SWPTR)

bit 4 **Unimplemented:** Read as '0'

REGISTER 23-6: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | -                 | -                 | _                 | -                 | 1                 | -                 | _                | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | -                 | _                 | _                | _                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | PTEN<             | :15:14>           | PTEN<13:8>        |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | PTEN<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-15 Unimplemented: Read as '0'

bit 15-14 PTEN<15:14>: PMCS1 Strobe Enable bits

1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS1 and PMCS2(1)

0 = PMA15 and PMA14 function as port I/O

bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits

1 = PMA<13:2> function as PMP address lines

0 = PMA<13:2> function as port I/O

bit 1-0 PTEN<1:0>: PMALH/PMALL Strobe Enable bits

1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL(2)

0 = PMA1 and PMA0 pads function as port I/O

**Note 1:** The use of these pins as PMA15 and PMA14 or CS1 and CS2 is selected by the CSF<1:0> bits in the PMCON register.

2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

#### REGISTER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(2)</sup>

11111111 = Alarm will trigger 256 times

:

•

00000000 = Alarm will trigger one time

The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- Note 1: Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

**Note:** This register is reset only on a Power-on Reset (POR).

#### REGISTER 25-3: RTCTIME: REAL-TIME CLOCK TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-x                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                         | HR10              |                   | HR01<3:0>         |                   |                   |                  |                  |  |  |

| 22.40        | R/W-x                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                         | MIN10             | <3:0>             |                   | MIN01<3:0>        |                   |                  |                  |  |  |

| 45.0         | R/W-x R/W-x R/W-x R/W-x |                   |                   |                   | R/W-x R/W-x R/W-x |                   |                  |                  |  |  |

| 15:8         |                         | SEC10             | <3:0>             |                   | SEC01<3:0>        |                   |                  |                  |  |  |

| 7.0          | U-0                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | _                       | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10 digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1 digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

REGISTER 26-1: CEVER: CRYPTO ENGINE REVISION, VERSION, AND ID REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        |                   | REVISION<7:0>     |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | VERSION<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         | ID<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | ID<7              | :0>               |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-24 **REVISION<7:0>:** Crypto Engine Revision bits bit 23-16 **VERSION<7:0>:** Crypto Engine Version bits bit 15-0 **ID<15:0>:** Crypto Engine Identification bits

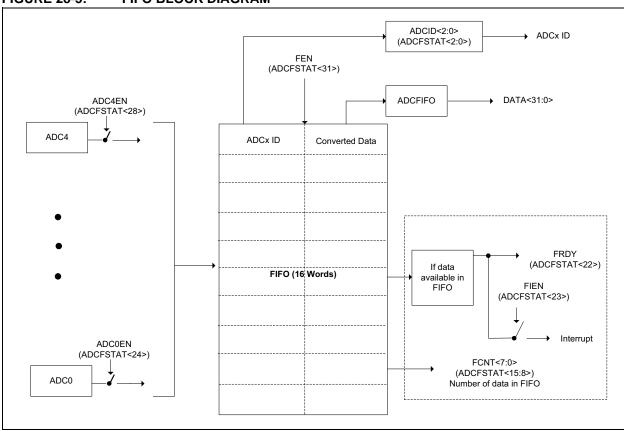

FIGURE 28-3: FIFO BLOCK DIAGRAM

# REGISTER 28-14: ADCCMPENx: ADC DIGITAL COMPARATOR 'x' ENABLE REGISTER ('x' = 1 THROUGH 6)

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 24.24        | R/W-0                 |

| 31:24        | CMPE31 <sup>(1)</sup> | CMPE30 <sup>(1)</sup> | CMPE29 <sup>(1)</sup> | CMPE28 <sup>(1)</sup> | CMPE27 <sup>(1)</sup> | CMPE26 <sup>(1)</sup> | CMPE25 <sup>(1)</sup> | CMPE24 <sup>(1)</sup> |

| 22.40        | R/W-0                 |

| 23:16        | CMPE23 <sup>(1)</sup> | CMPE22 <sup>(1)</sup> | CMPE21 <sup>(1)</sup> | CMPE20 <sup>(1)</sup> | CMPE19 <sup>(1)</sup> | CMPE18                | CMPE17                | CMPE16                |

| 15.0         | R/W-0                 |

| 15:8         | CMPE15                | CMPE14                | CMPE13                | CMPE12                | CMPE11                | CMPE10                | CMPE9                 | CMPE8                 |

| 7.0          | R/W-0                 |

| 7:0          | CMPE7                 | CMPE6                 | CMPE5                 | CMPE4                 | CMPE3                 | CMPE2                 | CMPE1                 | CMPE0                 |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 CMPE31:CMPE0: ADC Digital Comparator 'x' Enable bits(2,3)

These bits enable conversion results corresponding to the Analog Input to be processed by the Digital Comparator. CMPE0 enables AN0, CMPE1 enables AN1, and so on.

- Note 1: This bit is not available on 64-pin devices.

- 2: CMPEx = ANx, where 'x' = 0-31 (Digital Comparator inputs are limited to AN0 through AN31).

- 3: Changing the bits in this register while the Digital Comparator is enabled (ENDCMP = 1) can result in unpredictable behavior.

#### REGISTER 29-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0 R/W-0       |                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | FLTEN19           | MSEL1             | 9<1:0>            | FSEL19<4:0>       |                   |                   |                  |                  |  |

| 22,46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN18           | MSEL18<1:0>       |                   | FSEL18<4:0>       |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0 R/W-0       |                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN17           | MSEL1             | MSEL17<1:0>       |                   |                   | SEL17<4:0>        | >                |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN16           | MSEL1             | 6<1:0>            | FSEL16<4:0>       |                   |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FLTEN19: Filter 19 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 30-29 MSEL19<1:0>: Filter 19 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 28-24 FSEL19<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

•

•

•

00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0

bit 23 FLTEN18: Filter 18 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 22-21 MSEL18<1:0>: Filter 18 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 20-16 FSEL18<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

•

•

•

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

TABLE 33-2: PERIPHERAL MODULE DISABLE REGISTER SUMMARY

| ess                         |                                 |           |       | Bits  |        |        |         |         |         |         |        |         | "     |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|--------|--------|---------|---------|---------|---------|--------|---------|-------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13  | 28/12  | 27/11   | 26/10   | 25/9    | 24/8    | 23/7   | 22/6    | 21/5  | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 0040                        | PMD1                            | 31:16     | _     | ı     | _      | _      | I       | _       | _       | _       |        | _       |       | _      | _      | _      | _      | _      | 0000       |

| 0040                        | TIMET                           | 15:0      | _     | _     | _      | CVRMD  | _       | _       | _       | _       | _      | _       | _     | _      | _      | _      | _      | ADCMD  | 0000       |

| 0050                        | PMD2                            | 31:16     | _     |       | _      | _      |         | _       | _       | _       | _      | _       | _     | _      | _      | _      | _      | _      | 0000       |

| 0030                        | FIVIDZ                          | 15:0      |       |       | _      | _      |         | _       | _       | _       | _      | _       | -     | _      | _      | _      | CMP2MD | CMP1MD | 0000       |

| 0060                        | PMD3                            | 31:16     |       | 1     |        | -      | _       | _       | _       | OC9MD   | OC8MD  | OC7MD   | OC6MD | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000       |

| 0000                        | FIVIDS                          | 15:0      |       | 1     |        | -      | _       | _       | _       | IC9MD   | IC8MD  | IC7MD   | IC6MD | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD  | 0000       |

| 0070                        | PMD4                            | 31:16     | _     | _     | _      | _      | _       | _       | _       | _       | _      | _       | _     | _      | _      | _      | _      | _      | 0000       |

| 0070                        | FIVID4                          | 15:0      | _     |       | _      | _      |         | _       | _       | T9MD    | T8MD   | T7MD    | T6MD  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | 0000       |

| 0080                        | PMD5                            | 31:16     |       | 1     | CAN2MD | CAN1MD | _       | _       | _       | USBMD   | _      | _       | _     | I2C5MD | I2C4MD | I2C3MD | I2C2MD | I2C1MD | 0000       |

| 0000                        | PIVIDS                          | 15:0      | 1     | _     | SPI6MD | SPI5MD | SPI4MD  | SPI3MD  | SPI2MD  | SPI1MD  | _      | _       | U6MD  | U5MD   | U4MD   | U3MD   | U2MD   | U1MD   | 0000       |

| 0000                        | PMD6                            | 31:16     | 1     | -     | _      | ETHMD  | _       | _       | _       | _       | SQI1MD | _       | _     | _      | _      | _      | EBIMD  | PMPMD  | 0000       |

| 0090                        | PIVIDO                          | 15:0      | _     | _     | _      | _      | REFO4MD | REFO3MD | REFO2MD | REFO1MD | _      | _       | _     | _      | _      | _      | _      | RTCCMD | 0000       |

| 0040                        | PMD7                            | 31:16     | _     |       | _      | _      | I       | _       | _       | _       | _      | CRYPTMD | _     | RNGMD  | _      | _      | _      | _      | 0000       |

| 00A0                        | PIVID/                          | 15:0      | _     | _     | _      | _      | _       | _       | _       | _       | _      | _       | _     | DMAMD  | _      | _      | _      | _      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

TABLE 37-40: ADC SAMPLE TIMES WITH CVD ENABLED

| AC CHARACTERISTICS <sup>(2)</sup> |        |                                                                                                    | (unles                                 | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |       |                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----------------------------------|--------|----------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param.<br>No.                     | Symbol | Characteristics                                                                                    | Min.                                   | Typ. <sup>(1)</sup>                                                                                                                                                                                                                                 | Max. | Units | Conditions                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| AD60a                             | TSAMP  | Sample Time for<br>ADC7 (Class 2 and<br>Class 3 Inputs) with<br>the CVDEN bit<br>(ADCCON1<11>) = 1 | 8<br>9<br>11<br>12<br>14<br>16<br>17   | _                                                                                                                                                                                                                                                   | _    | TAD   | Source Impedance ≤ 200Ω<br>CVDCPL<2:0> (ADCCON2<28:26>) = 001<br>CVDCPL<2:0> (ADCCON2<28:26>) = 010<br>CVDCPL<2:0> (ADCCON2<28:26>) = 011<br>CVDCPL<2:0> (ADCCON2<28:26>) = 100<br>CVDCPL<2:0> (ADCCON2<28:26>) = 101<br>CVDCPL<2:0> (ADCCON2<28:26>) = 101<br>CVDCPL<2:0> (ADCCON2<28:26>) = 110<br>CVDCPL<2:0> (ADCCON2<28:26>) = 111                 |  |  |  |

|                                   |        |                                                                                                    | 10<br>12<br>14<br>16<br>18<br>19<br>21 | _                                                                                                                                                                                                                                                   | _    | TAD   | Source Impedance ≤ 500Ω<br>CVDCPL<2:0> (ADCCON2<28:26>) = 001<br>CVDCPL<2:0> (ADCCON2<28:26>) = 010<br>CVDCPL<2:0> (ADCCON2<28:26>) = 011<br>CVDCPL<2:0> (ADCCON2<28:26>) = 100<br>CVDCPL<2:0> (ADCCON2<28:26>) = 101<br>CVDCPL<2:0> (ADCCON2<28:26>) = 101<br>CVDCPL<2:0> (ADCCON2<28:26>) = 110<br>CVDCPL<2:0> (ADCCON2<28:26>) = 111                 |  |  |  |

|                                   |        |                                                                                                    | 13<br>16<br>18<br>21<br>23<br>26<br>28 | _                                                                                                                                                                                                                                                   | _    | TAD   | Source Impedance $\leq$ 1 KΩ CVDCPL<2:0> (ADCCON2<28:26>) = 001 CVDCPL<2:0> (ADCCON2<28:26>) = 010 CVDCPL<2:0> (ADCCON2<28:26>) = 011 CVDCPL<2:0> (ADCCON2<28:26>) = 100 CVDCPL<2:0> (ADCCON2<28:26>) = 100 CVDCPL<2:0> (ADCCON2<28:26>) = 101 CVDCPL<2:0> (ADCCON2<28:26>) = 101 CVDCPL<2:0> (ADCCON2<28:26>) = 110 CVDCPL<2:0> (ADCCON2<28:26>) = 111 |  |  |  |

|                                   |        |                                                                                                    | 41<br>48<br>56<br>63<br>70<br>78<br>85 | _                                                                                                                                                                                                                                                   | _    | TAD   | Source Impedance $\leq$ 5 KΩ CVDCPL<2:0> (ADCCON2<28:26>) = 001 CVDCPL<2:0> (ADCCON2<28:26>) = 010 CVDCPL<2:0> (ADCCON2<28:26>) = 011 CVDCPL<2:0> (ADCCON2<28:26>) = 100 CVDCPL<2:0> (ADCCON2<28:26>) = 100 CVDCPL<2:0> (ADCCON2<28:26>) = 101 CVDCPL<2:0> (ADCCON2<28:26>) = 101 CVDCPL<2:0> (ADCCON2<28:26>) = 110 CVDCPL<2:0> (ADCCON2<28:26>) = 111 |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**<sup>2:</sup>** The ADC module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is guaranteed, but not characterized.

# APPENDIX A: MIGRATING FROM PIC32MX5XX/6XX/7XX TO PIC32MZ EF

This appendix provides an overview of considerations for migrating from PIC32MX5XX/6XX/7XX devices to the PIC32MZ EF family of devices. The code developed for PIC32MX5XX/6XX/7XX devices can be ported to PIC32MZ EF devices after making the appropriate changes outlined in the following sections.

The PIC32MZ EF devices are based on a new architecture, and feature many improvements and new capabilities over PIC32MX5XX/6XX/7XX devices.

#### A.1 Oscillator and PLL Configuration

Because the maximum speed of the PIC32MZ EF family is greater, the configuration of the oscillator is different from prior PIC32MX5XX/6XX/7XX devices.

Table A-1 summarizes the differences (indicated by **Bold** type) between the family devices for the oscillator.

TABLE A-1: OSCILLATOR CONFIGURATION DIFFERENCES

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                                                      | PIC32MZ EF Feature                                                                                                                                                                        |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Primary Oscillator Configuration                                                                                                                                                                                |                                                                                                                                                                                           |  |  |  |  |  |  |  |

| On PIC32MX devices, XT mode had to be selected if the input frequency was in the 3 MHz to 10 MHz range (4-10 for PLL), and HS mode had to be selected if the input frequency was in the 10 MHz to 20 MHz range. | On PIC32MZ EF devices, HS mode has a wider input frequency range (4 MHz to 12 MHz). The bit setting of '01' is Reserved.                                                                  |  |  |  |  |  |  |  |

| POSCMOD<1:0> (DEVCFG1<9:8>)  11 = Primary Oscillator disabled  10 = HS Oscillator mode selected  01 = XT Oscillator mode selected  00 = External Clock mode selected                                            | POSCMOD<1:0> (DEVCFG1<9:8>)  11 = Primary Oscillator disabled  10 = HS Oscillator mode selected  01 = Reserved  00 = External Clock mode selected                                         |  |  |  |  |  |  |  |

| On PIC32MX devices, crystal mode could be selected with the HS or XT POSC setting, but an external oscillator could be fed into the OSC1/CLKI pin and the part would operate normally.                          | On PIC32MZ devices, this option is not available. External oscillator signals should only be fed into the OSC1/CLKI pin with the POSC set to EC mode.                                     |  |  |  |  |  |  |  |

| Oscillator Selection                                                                                                                                                                                            |                                                                                                                                                                                           |  |  |  |  |  |  |  |

| On PIC32MX devices, clock selection choices are as follows:  FNOSC<2:0> (DEVCFG1<2:0>)  NOSC<2:0> (OSCCON<10:8>)  111 = FRCDIV  110 = FRCDIV16  101 = LPRC  100 = SOSC  011 = POSC with PLL module              | On PIC32MZ EF devices, clock selection choices are as follows:  FNOSC<2:0> (DEVCFG1<2:0>)  NOSC<2:0> (OSCCON<10:8>)  111 = FRCDIV  110 = Reserved  101 = LPRC  100 = SOSC  011 = Reserved |  |  |  |  |  |  |  |

| 010 = POSC (XT, HS, EC)<br>001 = FRCDIV+PLL<br>000 = FRC<br>COSC<2:0> (OSCCON<14:12>)<br>111 = FRC divided by FRCDIV                                                                                            | 010 = POSC (HS or EC)<br>001 = System PLL (SPLL)<br>000 = FRCDIV<br>COSC<2:0> (OSCCON<14:12>)<br>111 = FRC divided by FRCDIV                                                              |  |  |  |  |  |  |  |

| 110 = FRC divided by 16<br>101 = LPRC<br>100 = SOSC<br>011 = POSC + PLL module<br>010 = POSC                                                                                                                    | 110 = BFRC<br>101 = LPRC<br>100 = SOSC<br>011 = Reserved<br>010 = POSC                                                                                                                    |  |  |  |  |  |  |  |

| 001 = FRCPLL<br>000 = FRC                                                                                                                                                                                       | 001 = System PLL<br>000 = FRC divided by FRCDIV                                                                                                                                           |  |  |  |  |  |  |  |

TABLE A-1: OSCILLATOR CONFIGURATION DIFFERENCES (CONTINUED)

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                  | PIC32MZ EF Feature                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Secondary Os                                                                                                                                                                | cillator Enable                                                                                                                                                                                                           |

|                                                                                                                                                                             | The location of the SOSCEN bit in the Flash Configuration Words has moved.                                                                                                                                                |