Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

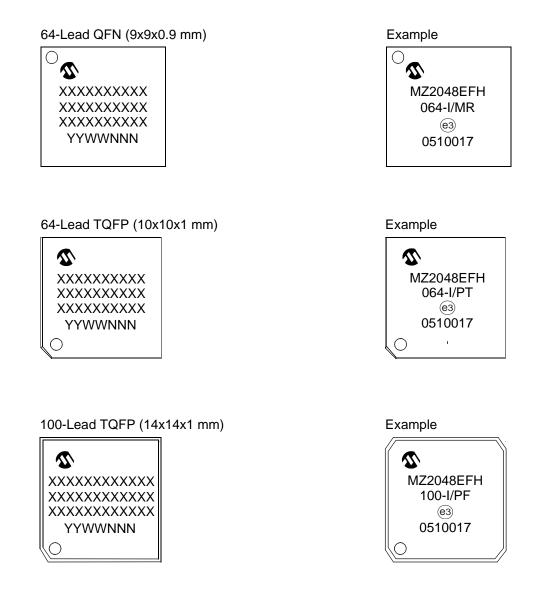

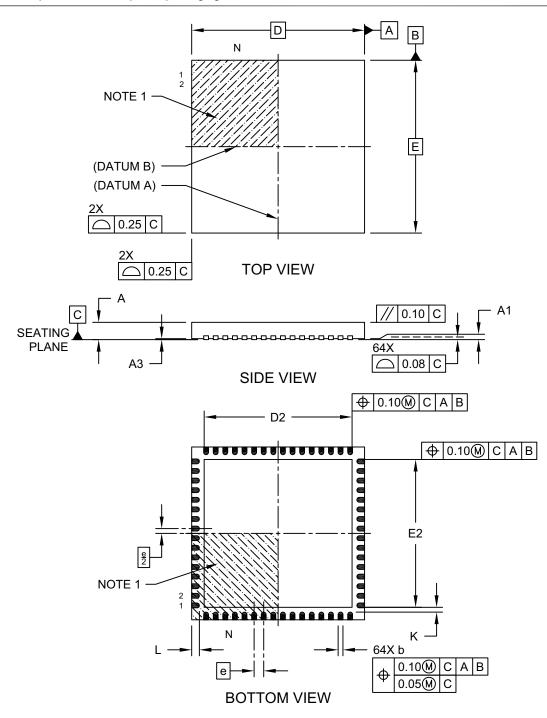

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efh064-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                                        |     |             |                                   |

|----------|------------------------|-----------------|-----------------|----------------------------------------|-----|-------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | <sup>-piii</sup>   TOFP/   Type   Type |     | Description |                                   |

|          | •                      | •               |                 | •                                      | PO  | RTD         | ·                                 |

| RD0      | 46                     | 71              | A48             | 104                                    | I/O | ST          | PORTD is a bidirectional I/O port |

| RD1      | 49                     | 76              | A52             | 109                                    | I/O | ST          |                                   |

| RD2      | 50                     | 77              | B42             | 110                                    | I/O | ST          |                                   |

| RD3      | 51                     | 78              | A53             | 111                                    | I/O | ST          |                                   |

| RD4      | 52                     | 81              | A56             | 118                                    | I/O | ST          |                                   |

| RD5      | 53                     | 82              | B46             | 119                                    | I/O | ST          |                                   |

| RD6      | —                      | _               | A57             | 120                                    | I/O | ST          |                                   |

| RD7      | —                      | _               | B47             | 121                                    | I/O | ST          |                                   |

| RD9      | 43                     | 68              | B38             | 97                                     | I/O | ST          |                                   |

| RD10     | 44                     | 69              | A46             | 98                                     | I/O | ST          |                                   |

| RD11     | 45                     | 70              | B39             | 99                                     | I/O | ST          |                                   |

| RD12     | —                      | 79              | B43             | 112                                    | I/O | ST          |                                   |

| RD13     | —                      | 80              | A54             | 113                                    | I/O | ST          |                                   |

| RD14     | —                      | 47              | B27             | 69                                     | I/O | ST          |                                   |

| RD15     | —                      | 48              | A32             | 70                                     | I/O | ST          |                                   |

|          |                        |                 |                 |                                        | PO  | RTE         |                                   |

| RE0      | 58                     | 91              | B52             | 135                                    | I/O | ST          | PORTE is a bidirectional I/O port |

| RE1      | 61                     | 94              | A64             | 138                                    | I/O | ST          |                                   |

| RE2      | 62                     | 98              | A66             | 142                                    | I/O | ST          |                                   |

| RE3      | 63                     | 99              | B56             | 143                                    | I/O | ST          |                                   |

| RE4      | 64                     | 100             | A67             | 144                                    | I/O | ST          |                                   |

| RE5      | 1                      | 3               | A3              | 3                                      | I/O | ST          |                                   |

| RE6      | 2                      | 4               | B2              | 4                                      | I/O | ST          |                                   |

| RE7      | 3                      | 5               | A4              | 5                                      | I/O | ST          |                                   |

| RE8      | —                      | 18              | B10             | 23                                     | I/O | ST          |                                   |

| RE9      |                        | 19              | A12             | 24                                     | I/O | ST          |                                   |

|          |                        |                 |                 |                                        | PC  | RTF         |                                   |

| RF0      | 56                     | 85              | A59             | 124                                    | I/O | ST          | PORTF is a bidirectional I/O port |

| RF1      | 57                     | 86              | B49             | 125                                    | I/O | ST          |                                   |

| RF2      |                        | 57              | B31             | 79                                     | I/O | ST          |                                   |

| RF3      | 38                     | 56              | A38             | 78                                     | I/O | ST          |                                   |

| RF4      | 41                     | 64              | B36             | 90                                     | I/O | ST          |                                   |

| RF5      | 42                     | 65              | A44             | 91                                     | I/O | ST          |                                   |

| RF8      | _                      | 58              | A39             | 80                                     | I/O | ST          | ]                                 |

| RF12     | —                      | 40              | B22             | 58                                     | I/O | ST          |                                   |

| RF13     | —                      | 39              | A26             | 57                                     | I/O | ST          |                                   |

| Legend:  | CMOS = C               | MOS-comp        | atible input    | t or output                            |     | Analog =    | Analog input P = Power            |

#### **TABLE 1-6:** PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS (CONTINUED)

CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output PPS = Peripheral Pin Select P = Power I = Input

|          |                                       | Pin Nu          | mber            |                          |             |                |                                                                            |

|----------|---------------------------------------|-----------------|-----------------|--------------------------|-------------|----------------|----------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP                | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                                                |

|          |                                       |                 |                 |                          | J           | ΓAG            |                                                                            |

| ТСК      | 27                                    | 38              | B21             | 56                       | I           | ST             | JTAG Test Clock Input Pin                                                  |

| TDI      | 28                                    | 39              | A26             | 57                       | I           | ST             | JTAG Test Data Input Pin                                                   |

| TDO      | 24                                    | 40              | B22             | 58                       | 0           | —              | JTAG Test Data Output Pin                                                  |

| TMS      | 23                                    | 17              | A11             | 22                       | I           | ST             | JTAG Test Mode Select Pin                                                  |

|          | •                                     | •               | •               |                          | Tr          | ace            | •                                                                          |

| TRCLK    | 57                                    | 89              | A61             | 129                      | 0           | _              | Trace Clock                                                                |

| TRD0     | 58                                    | 97              | B55             | 141                      | 0           | —              | Trace Data bits 0-3                                                        |

| TRD1     | 61                                    | 96              | A65             | 140                      | 0           | —              |                                                                            |

| TRD2     | 62                                    | 95              | B54             | 139                      | 0           | —              |                                                                            |

| TRD3     | 63                                    | 90              | B51             | 130                      | 0           | —              |                                                                            |

|          |                                       |                 |                 | Pro                      | grammiı     | ng/Debugg      | ing                                                                        |

| PGED1    | 16                                    | 25              | A18             | 36                       | I/O         | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 1          |

| PGEC1    | 15                                    | 24              | A17             | 35                       | Ι           | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 1       |

| PGED2    | 18                                    | 27              | A19             | 38                       | I/O         | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 2          |

| PGEC2    | 17                                    | 26              | B14             | 37                       | Ι           | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 2       |

| MCLR     | 9                                     | 15              | A10             | 20                       | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device. |

| Legend:  | CMOS = CI<br>ST = Schm<br>TTL = Trans | itt Trigger ir  | put with C      | MOS level                |             | O = Outp       | Analog input P = Power<br>ut I = Input<br>eripheral Pin Select             |

#### **TABLE 1-22:** JTAG, TRACE, AND PROGRAMMING/DEBUGGING PINOUT I/O DESCRIPTIONS

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   |                   |                   |                   | FS                |                   |                  |                  |

| 00:40        | R/W-x             | R/W-x             | R/W-x             | R-0               | R-1               | R-1               | R/W-x            | R/W-x            |

| 23:16        | FCC<0>            | FO                | FN                | MAC2008           | ABS2008           | NAN2008           | CAUSE<5:4>       |                  |

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | CAUSE             | .2.0.             |                   |                   | ENABLE            | S<4:1>           |                  |

|              |                   | CAUSE             | <3.0>             |                   | V                 | Z                 | 0                | U                |

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          | ENABLES<0>        |                   |                   | FLAGS<4:0>        |                   |                   | DM               | -1.0             |

|              | I                 | V                 | Z                 | 0                 | U                 |                   | RM<1:0>          |                  |

#### REGISTER 3-10: FCSR: FLOATING POINT CONTROL AND STATUS REGISTER; CP1 REGISTER 31

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-25 FCC<7:1>: Floating Point Condition Code bits

These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

#### bit 24 **FS:** Flush to Zero control bit

1 = Denormal input operands are flushed to zero. Tiny results are flushed to either zero or the applied format's smallest normalized number (MinNorm) depending on the rounding mode settings.

0 = Denormal input operands result in an Unimplemented Operation exception.

#### bit 23 FCC<0>: Floating Point Condition Code bits

These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

- bit 22 **FO:** Flush Override Control bit

- 1 = The intermediate result is kept in an internal format, which can be perceived as having the usual mantissa precision but with unlimited exponent precision and without forcing to a specific value or taking an exception.

- 0 = Handling of Tiny Result values depends on setting of the FS bit.

#### bit 21 FN: Flush to Nearest Control bit

- 1 = Final result is rounded to either zero or 2E\_min (MinNorm), whichever is closest when in Round to Nearest (RN) rounding mode. For other rounding modes, a final result is given as if FS was set to 1.

0 = Handling of Tiny Result values depends on setting of the FS bit.

- bit 20 MAC2008: Fused Multiply Add mode control bit

- 0 = Unfused multiply-add. Intermediary multiplication results are rounded to the destination format.

- bit 19 ABS2008: Absolute value format control bit

- 1 = ABS.fmt and NEG.fmt instructions compliant with IEEE Standard 754-2008. The ABS and NEG functions accept QNAN inputs without trapping.

- bit 18 NAN2008: NaN Encoding control bit

- 1 = Quiet and signaling NaN encodings recommended by the IEEE Standard 754-2008. A quiet NaN is encoded with the first bit of the fraction being 1 and a signaling NaN is encoded with the first bit of the fraction being 0.

#### bit 17-12 CAUSE<5:0>: FPU Exception Cause bits

These bits indicated the exception conditions that arise during execution of an FPU arithmetic instruction.

bit 17 E: Unimplemented Operation bit

| Big<br>S         Z         Bit<br>S         CHO         CHO </th <th>-</th> <th>_E 4-3: B</th> <th></th> <th>FLAST</th> <th colspan="10">-LASH 2 SEQUENCE AND CONFIGURATION WORDS SUMMARY</th> | -                         | _E 4-3: B        |           | FLAST | -LASH 2 SEQUENCE AND CONFIGURATION WORDS SUMMARY |       |       |       |       |      |           |             |             |           |      |      |      |      |      |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------|-----------|-------|--------------------------------------------------|-------|-------|-------|-------|------|-----------|-------------|-------------|-----------|------|------|------|------|------|------------|

| FF40       ABF2DEVCFG3       31:0       xx         FF44       ABF2DEVCFG3       31:0       xx         FF44       ABF2DEVCF60       31:0       xx         FF44       ABF2DEVCF60       31:0       xx         FF50       ABF2DEVCP2       31:0       xx         FF54       ABF2DEVCP2       31:0       xx         FF54       ABF2DEVCP1       31:0       xx         FF56       ABF2DEVSIGN3       31:0       xx         FF66       ABF2DEVSIGN3       31:0       xx         FF66       ABF2DEVSIGN3       31:0       xx         FF66       ABF2DEVSIGN3       31:0       xx         FF66       ABF2DEVSIGN3       31:0       xx         FF60       BF2DEVCFG3       31:0       xx         FF60       BF2DEVCP3       31:0       xx         FF60       BF2DEVCP1                                                                                                                                                                                                                                                                                                                        | SS                        |                  |           |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      |            |

| FF44         ABF2DEVCFG2         31:0           FF46         ABF2DEVCFG3         31:0           FF50         ABF2DEVCFG3         31:0           FF54         ABF2DEVCF3         31:0           FF54         ABF2DEVCF1         31:0           FF56         ABF2DEVCF03         31:0           FF56         ABF2DEVCP1         31:0           FF56         ABF2DEVSIGN3         31:0           FF60         ABF2DEVSIGN3         31:0           FF60         ABF2DEVSIGN3         31:0           FF60         ABF2DEVSIGN3         31:0           FF60         ABF2DEVCF62         31:0           FF60         BF2DEVCF63         31:0           FF60         BF2DEVCF61         31:0           FF60         BF2DEVCF1         31:0           FF60         BF2DEVCP1         31:0           FF60         BF2DEVCP1         31:0           FF60                                                                                                                                                                                                                                                       | Virtual Addre<br>(BFC6_#) | Register<br>Name | Bit Range | 31/15 | 30/14                                            | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8      | 23/7        | 22/6        | 21/5      | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| FF48         ABF2DEVCFG1         31:0           FF44         ABF2DEVCFG3         31:0           FF54         ABF2DEVCP2         31:0           FF54         ABF2DEVCP2         31:0           FF56         ABF2DEVCP3         31:0           FF64         ABF2DEVCP63         31:0           FF64         ABF2DEVSIGN3         31:0           FF60         BF2DEVCFG3         31:0           FF60         BF2DEVCFG3         31:0           FF60         BF2DEVCFG3         31:0           FF60         BF2DEVCFG3         31:0           FF60         BF2DEVCF63         31:0           FF60 </td <td>FF40</td> <td>ABF2DEVCFG3</td> <td>31:0</td> <td></td> <td>xxxx</td>              | FF40                      | ABF2DEVCFG3      | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| F4C         AB72DEVCPG0         31:0           F750         AB72DEVCP2         31:0           F754         AB72DEVCP2         31:0           F758         AB72DEVCP2         31:0           F760         AB72DEVCP2         31:0           F760         AB72DEVSIGN3         31:0           F760         BF2DEVCPG3         31:0           F760         BF2DEVCP3         31:0           F760         BF2DEVCP3         31:0           F760         BF2DEVCP3         31:0           F760                                                                                                                                                                                                                                                        | FF44                      | ABF2DEVCFG2      | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FF60         ABF2DEVCP3         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0                                                                                                      | FF48                      | ABF2DEVCFG1      | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FF54         ABF2DEVCP2         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0         31:0                                                                                                      | FF4C                      | ABF2DEVCFG0      | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FF58         ABF2DEVCP1         31:0           FF56         ABF2DEVSIGN3         31:0           FF60         ABF2DEVSIGN2         31:0           FF60         ABF2DEVSIGN3         31:0           FF60         ABF2DEVSIGN3         31:0           FF60         ABF2DEVSIGN3         31:0           FF60         ABF2DEVSIGN3         31:0           FF60         BF2DEVCFG3         31:0           FF60         BF2DEVCFG3         31:0           FF60         BF2DEVCFG3         31:0           FF60         BF2DEVCP2         31:0           FF00         BF2DEVCP1         31:0           FF00         BF2DEVCP2         31:0           FF60         BF2DEVSIGN3         31:0           FF60                                                                                                                                                                                                                                                       | FF50                      | ABF2DEVCP3       | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | XXXX       |

| FF62       ABF2DEVCP1       31:0       31:0         FF60       ABF2DEVSIGN3       31:0       31:0         FF64       ABF2DEVSIGN3       31:0       31:0         FF64       ABF2DEVSIGN3       31:0       31:0         FF66       ABF2DEVSIGN3       31:0       31:0         FF67       BF2DEVCFG3       31:0       31:0         FF67       BF2DEVCFG3       31:0       31:0         FF66       BF2DEVCFG3       31:0       31:0         FF67       BF2DEVCFG3       31:0       31:0         FF66       BF2DEVCFG3       31:0       31:0         FF67       BF2DEVCFG3       31:0       31:0         FF67       BF2DEVCFG3       31:0       31:0         FF60       BF2DEVCF3       31:0       31:0         FF60       BF2DEVCF3       31:0       31:0         FF60       BF2DEVCF3       31:0       31:0         FF60       BF2DEVCF3       31:0       31:0         FF60       BF2DEVSIGN3       31:0       31:0         FF60       BF2DEVSIGN3       31:0       31:0         FF60       BF2DEVSIGN3       31:0       31:0         FF60                                                                                                                                                                                                                                                                                                        | -                         | -                | 31:0      |       |                                                  |       |       |       |       | Not  | . Soo Tah | lo 31-2 for | the hit des | criptions |      |      |      |      |      | xxxx       |

| FF60         ABF2DEVSIGN3         31:0         31:0           FF64         ABF2DEVSIGN2         31:0         31:0           FF62         ABF2DEVSIGN0         31:0         31:0           FF60         BF2DEVCFG3         31:0         31:0           FF62         BF2DEVCFG0         31:0         31:0           FF62         BF2DEVCFG0         31:0         31:0           FF62         BF2DEVCFG0         31:0         31:0           FF60         BF2DEVCF03         31:0         31:0           FF60         BF2DEVCP1         31:0         31:0           FF60         BF2DEVCP2         31:0         31:0           FF60         BF2DEVCP1         31:0         31:0           FF60         BF2DEVCP0         31:0         31:0           FF60         BF2DEVSIGN2         31:0         31:0           FF60         BF2DEVSIGN1         31:0         31:0                                                                                                                                                                                                                          | FF58                      | ABF2DEVCP1       | 31:0      |       |                                                  |       |       |       |       | Note | . Oee lab | 10 34-2 10  |             | suptions. |      |      |      |      |      | xxxx       |

| FF64       ABF2DEVSIGN2       31:0       31:0         FF68       ABF2DEVSIGN1       31:0       31:0         FF60       ABF2DEVSIGN0       31:0       31:0         FF60       BF2DEVCFG2       31:0       31:0         FF64       BF2DEVCFG0       31:0       31:0         FF60       BF2DEVCFG0       31:0       31:0         FF60       BF2DEVCF03       31:0       31:0         FF60       BF2DEVCP1       31:0       31:0         FF60       BF2DEVCP3       31:0       31:0         FF60       BF2DEVCP1       31:0       31:0         FF60       BF2DEVCP1       31:0       31:0         FF60       BF2DEVCP1       31:0       31:0         FF60       BF2DEVSIGN3       31:0       31:0         FF60                                                                                                                                                                                                                                                                                                       |                           |                  |           |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FF68         ABF2DEVSIGN1         31:0         xxx           FF60         ABF2DEVSIGN0         31:0         xxx           FFC0         BF2DEVCFG3         31:0         xxx           FFC4         BF2DEVCFG1         31:0         xxx           FFC6         BF2DEVCFG0         31:0         xxx           FFC6         BF2DEVCFG2         31:0         xxx           FFC6         BF2DEVCF20         31:0         xxx           FFD0         BF2DEVCF22         31:0         xxx           FFD0         BF2DEVCP2         31:0         xxx           FFD0         BF2DEVCP2         31:0         xxx           FFE6         BF2DEVCP2         31:0         xxx           FFE6         BF2DEVCP3         31:0         xxx           FFE6         BF2DEVSIGN3         31:0         xxx           FFE6         BF2DEVSIGN1         31:0         xxx           FFE6         BF2DEVSIGN3         31:0         xxx           FFE6         BF2DEVSIGN3         31:0         xxx           FFE6         BF2DEVSIGN3         31:0         xxx           FFE6         BF2DEVSIGN3         31:0         xxx           F                                                                                                                                                                                                                                  |                           |                  |           |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FF6C         ABF2DEVSIGN0         31:0         xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |                  | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFC0         BF2DEVCFG3         31:0         xx           FFC4         BF2DEVCFG1         31:0         xx           FFC8         BF2DEVCFG1         31:0         xx           FFC0         BF2DEVCFG3         31:0         xx           FFD0         BF2DEVCP2         31:0         xx           FFD4         BF2DEVCP2         31:0         xx           FFD6         BF2DEVCP2         31:0         xx           FFD6         BF2DEVCP2         31:0         xx           FFD6         BF2DEVCP2         31:0         xx           FFD6         BF2DEVCP0         31:0         xx           FFE0         BF2DEVSIGN3         31:0         xx           FFE6         BF2DEVSIGN2         31:0         xx           FFE6         BF2DEVSIGN3         31:0         xx           FFE6         BF2DEVSIGN3         31:0         xx           FFE7         BF2DEVSIGN3         31:0         xx           FFE7         BF2DEVSIGN3         31:0         xx           FFF6         BF2DEVSIGN3         31:0         xx           FFF6         BF2DEVSIGN3         31:0         xx           FFF6         B                                                                                                                                                                                                                                           |                           |                  |           |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFC4         BF2DEVCFG2         31:0           FFC8         BF2DEVCFG0         31:0           FFC0         BF2DEVCP3         31:0           FFD0         BF2DEVCP2         31:0           FFD0         BF2DEVCP2         31:0           FFD0         BF2DEVCP2         31:0           FFD0         BF2DEVCP2         31:0           FFD0         BF2DEVCP1         31:0           FFD0         BF2DEVCP1         31:0           FFE0         BF2DEVCP1         31:0           FFE0         BF2DEVSIGN3         31:0           FFE4         BF2DEVSIGN1         31:0           FFE6         BF2DEVSIGN0         31:0           FFE6         BF2DEVSIGN1         31:0           FFE6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN1         31:0           FFE7         BF2DEVSIGN0         31:0           FFE6         BF2DEVSIGN0         31:0           FFE7         BF2SEQ3         31:16           FFE7         BF2SEQ2         31:16                                                                                                                                                                                                                                                                                                                                                                                  | FF6C                      | ABF2DEVSIGN0     | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFC8         BF2DEVCFG1         31:0           FFC0         BF2DEVCP3         31:0           FFD4         BF2DEVCP2         31:0           FFD4         BF2DEVCP1         31:0           FFD6         BF2DEVCP2         31:0           FFD7         BF2DEVCP3         31:0           FFD8         BF2DEVCP1         31:0           FFD6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN3         31:0           FFE7         BF2DEVSIGN0         31:0           FFF0         BF2SEQ3         31:16           FFF4         BF2SEQ2         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FFC0                      | BF2DEVCFG3       | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFCC         BF2DEVCFG0         31:0           FFD0         BF2DEVCP2         31:0           FFD4         BF2DEVCP2         31:0           FFD5         BF2DEVCP1         31:0           FFD6         BF2DEVSIGN3         31:0           FFD7         BF2DEVSIGN2         31:0           FFE6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN0         31:0           FFE7         BF2DEVSIGN0         31:0           FFF6         BF2DEVSIGN0         31:0           FFF4         BF2SEQ2         31:16                                                                                                                                                                                                                                                                                                                                                                    |                           |                  | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFD0         BF2DEVCP3         31:0           FFD4         BF2DEVCP2         31:0           FFD8         BF2DEVCP1         31:0           FFD0         BF2DEVCP0         31:0           FFE0         BF2DEVCP0         31:0           FFE4         BF2DEVSIGN3         31:0           FFE8         BF2DEVSIGN2         31:0           FFE6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN3         31:0           FFE7         BF2DEVSIGN0         31:0           FFF6         BF2DEVSIGN0         31:16           FFF6         BF2SEQ3         31:16           TSEQ<15:0>         x2           TSEQ<15:0>         x2           FFF4         BF2SEQ2         31:16                                                                                                                                                                                                                                                                                                                                                                                                         |                           |                  | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFD4         BF2DEVCP2         31:0           FFD8         BF2DEVCP1         31:0           FFD0         BF2DEVCP0         31:0           FFE0         BF2DEVSIGN3         31:0           FFE4         BF2DEVSIGN2         31:0           FFE6         BF2DEVSIGN3         31:0           FFE6         BF2DEVSIGN3         31:0           FFE7         BF2DEVSIGN1         31:0           FFE6         BF2DEVSIGN0         31:0           FFE7         BF2DEVSIGN0         31:0           FFF0         BF2DEVSIGN0         31:0           FFF0         BF2DEVSIGN0         31:0           FFF6         BF2DEVSIGN0         31:0           FFF6         BF2DEVSIGN0         31:0           FFF6         BF2DEVSIGN0         31:0           FFF6         BF2DEVSIGN0         31:16           FFF6         BF2SEQ3         31:16           FFF4         BF2SEQ2         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |                  | 31:0      |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFD8         BF2DEVCP1         31:0           FFD0         BF2DEVCP0         31:0           FFE0         BF2DEVSIGN3         31:0           FFE4         BF2DEVSIGN1         31:0           FFE6         BF2DEVSIGN1         31:0           FFE6         BF2DEVSIGN0         31:0           FFE7         BF2DEVSIGN0         31:0           FFF0         BF2DEVSIGN0         31:0           FFF6         BF2DEVSIGN0         31:0           FFF6         BF2DEVSIGN0         31:0           FFF6         BF2DEVSIGN0         31:0           FFF6         BF2SEQ3         31:16           TSEQ<15:0>         xx           FFF4         BF2SEQ2         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |                  |           |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFD8       BF2DEVCP1       31:0         FFD0       BF2DEVCP0       31:0         FFE0       BF2DEVSIGN3       31:0         FFE4       BF2DEVSIGN2       31:0         FFE6       BF2DEVSIGN1       31:0         FFE6       BF2DEVSIGN2       31:0         FFE6       BF2DEVSIGN1       31:0         FFE6       BF2DEVSIGN0       31:0         FFE6       BF2DEVSIGN0       31:0         FFF6       BF2DEVSIGN0       31:16         CSEQ<15:0>         TSEQ<15:0>       x2         TSEQ<15:0>         TSEQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |                  |           |       |                                                  |       |       |       |       | Note | • See Tab | le 34-1 for | the hit des | criptions |      |      |      |      |      | xxxx       |

| FFE0       BF2DEVSIGN3       31:0         FFE4       BF2DEVSIGN2       31:0         FFE8       BF2DEVSIGN1       31:0         FFE0       BF2DEVSIGN0       31:0         FFF0       BF2SEQ3       31:16         FFF4       BF2SEQ2       31:16       CSEQ<15:0>         FFF4       BF2SEQ2       31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                  |           |       |                                                  |       |       |       |       |      |           |             |             | suptiono. |      |      |      |      |      | XXXX       |

| FFE4         BF2DEVSIGN2         31:0           FFE8         BF2DEVSIGN1         31:0           FFE0         BF2DEVSIGN0         31:0           FFF0         BF2SEQ3         31:16           FFF4         BF2SEQ2         31:16         CSEQ<15:0>           FFF4         BF2SEQ2         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                  |           |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFE8         BF2DEVSIGN1         31:0         xx           FFEC         BF2DEVSIGN0         31:0         xx           FFF0         BF2SEQ3         31:16         CSEQ<15:0>         xx           FFF4         BF2SEQ2         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |                  |           |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFEC         BF2DEVSIGN0         31:0         xx           FFF0         BF2SEQ3         31:16         CSEQ<15:0>         xx           FFF4         BF2SEQ2         31:16         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         >         >                                                                                                                                                                                                                                   |                           |                  |           |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      | xxxx       |

| FFF0     BF2SEQ3     31:16     CSEQ<15:0>     xx       FFF4     BF2SEQ2     31:16      xx       FFF4     BF2SEQ2     31:16      xx       FFF4     BF2SEQ2     31:16       xx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |                  |           |       | XXXX                                             |       |       |       |       |      |           |             |             |           |      |      |      |      |      |            |

| FFF0     BF2SEQ3     TSEQ<15:0>     xx       FFF4     BF2SEQ2     31:16     -     -     -     -     -     -     -     -     xx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FFEC                      | BF2DEVSIGN0      |           |       | XXXX                                             |       |       |       |       |      |           |             |             |           |      |      |      |      |      |            |

| Image: https://www.image: https://wwwwwwww.image: https://www.image: https://www.image: https://www.image: https://www.image: https://www.image: https://wwwwwwwwwwwwwwwwwwwwwwwwwwwwwwwwwww                                                                                                                                          | FFFO                      | BE2SE03          |           |       |                                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      |            |

| FFF4 BF2SEQ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           | 5, 202 00        | 15:0      |       | TSEQ<15:0> xxxx                                  |       |       |       |       |      |           |             |             |           |      |      |      |      |      |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EEE4                      | BE2SEO2          | 31:16     | _     | -                                                | -     | —     | —     | —     | —    | -         | _           | -           | _         | -    | —    | _    | —    | _    | xxxx       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1114                      |                  | 15:0      | —     | —                                                | —     | —     | —     | —     | —    | _         | —           | —           | —         | —    | —    | —    | _    | —    | xxxx       |

\_

|

—

\_

\_

Ι

\_

\_

\_

—

\_

\_

\_

\_

\_

|

\_

\_

\_

Ι

—

\_

#### TABLE 4-3: BOOT FLASH 2 SEQUENCE AND CONFIGURATION WORDS SUMMARY

Legend:

—

Ι

—

\_

31:16

15:0

31:16

15:0

FFF8 BF2SEQ1

FFFC BF2SEQ0

\_

\_

—

\_

\_

\_

\_

\_

\_

Ι

—

\_

\_

\_

\_

\_

—

|

\_

\_

xxxx

xxxx

xxxx

xxxx

\_

|

—

\_

\_

\_

—

\_

\_

|

\_

\_

\_

Ι

\_

\_

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | —                 |                   | IP3<2:0>          |                   | IS3<             | :1:0>            |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | —                 | _                 |                   | IP2<2:0>          |                   | IS2<             | :1:0>            |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | _                 | —                 | _                 |                   | IP1<2:0>          |                   | IS1<             | :1:0>            |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | —                 | _                 |                   | IP0<2:0>          | IS0<              | :1:0>            |                  |

## REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

# bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: Interrupt Priority bits                                  |

|-----------|--------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 25-24 | IS3<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1                                    |

|           | 00 = Interrupt subpriority is 0                                    |

| bit 23-21 |                                                                    |

| bit 20-18 | IP2<2:0>: Interrupt Priority bits                                  |

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 17-16 | IS2<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1<br>00 = Interrupt subpriority is 0 |

| hit 15-13 | Unimplemented: Read as '0'                                         |

| 5115-15   | ommplemented. Read as 0                                            |

| Note:     | This register represents a generic defi                            |

|           |                                                                    |

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-2 for the exact bit definitions.

# TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

| ss                          |                                 |               |                                             |       | / ///////////////////////////////////// |       |        | -     |      | Bit    |        | ,      |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|---------------------------------------------|-------|-----------------------------------------|-------|--------|-------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                                       | 30/14 | 29/13                                   | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 15B0                        | DCH7ECON                        | 31:16         | <u>− − − − − − − CHAIRQ&lt;7:0&gt;</u> 00FI |       |                                         |       |        |       |      |        |        |        |        | 00FF   |        |        |        |        |            |

| 1300                        | DOINECON                        | 15:0          |                                             |       |                                         | CHSIR | Q<7:0> |       | -    | -      | CFORCE | CABORT | PATEN  | SIRQEN | AIRQEN | _      |        |        | FF00       |

| 15C0                        | DCH7INT                         | 31:16         | —                                           | —     | —                                       | —     | —      | —     | —    | —      | CHSDIE | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 1000                        |                                 | 15:0          | —                                           | —     | —                                       | —     | —      | —     | —    | —      | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 15D0                        | DCH7SSA                         | 31:16         |                                             |       |                                         |       |        |       |      | CHSSA- | <31:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0          |                                             |       |                                         |       |        |       |      |        |        |        |        |        |        |        |        |        | 0000       |

| 15E0                        | DCH7DSA                         | 31:16<br>15:0 | CHDSA<31:0>                                 |       |                                         |       |        |       |      |        |        |        |        |        |        |        |        |        |            |

|                             |                                 | 31:16         | _                                           | _     | _                                       | _     | _      | _     | _    | _      | _      | _      | _      | _      | _      | _      | _      |        | 0000       |

| 15F0                        | DCH7SSIZ                        | 15:0          |                                             |       |                                         |       |        |       |      | CHSSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         |                                             |       |                                         |       |        | _     |      |        |        |        |        |        | _      |        | _      |        | 0000       |

| 1600                        | DCH7DSIZ                        | 15:0          |                                             |       |                                         |       |        |       |      | CHDSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1010                        | DCH7SPTR                        | 31:16         | —                                           | _     | —                                       | _     | —      | —     | —    | —      | —      | —      | —      | —      | _      | —      | —      | _      | 0000       |

| 1010                        | DCHISPIR                        | 15:0          |                                             |       |                                         |       |        |       |      | CHSPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1620                        | DCH7DPTR                        | 31:16         | _                                           | -     |                                         | _     |        |       | _    | _      |        | _      | _      |        |        |        |        | _      | 0000       |

| 1020                        | DOINDEIR                        | 15:0          |                                             |       |                                         |       |        |       |      | CHDPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1630                        | DCH7CSIZ                        | 31:16         | —                                           | _     |                                         | _     |        |       | _    | -      |        | _      | —      |        |        |        |        | _      | 0000       |

| 1030                        | DOINCOIL                        | 15:0          |                                             |       |                                         |       |        |       |      | CHCSIZ | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1640                        | DCH7CPTR                        | 31:16         | —                                           | —     | —                                       | _     | —      | —     | —    | _      | _      | _      | _      | _      | _      | —      | -      | _      | 0000       |

| 1010                        |                                 | 15:0          |                                             |       |                                         |       |        |       |      | CHCPTR | <15:0> |        |        |        |        |        |        |        | 0000       |

| 1650                        | DCH7DAT                         | 31:16         |                                             | —     | —                                       | —     | —      | —     | —    | —      | —      | —      | _      | —      | —      | —      | —      |        | 0000       |

|                             |                                 | 15:0          | 0 CHPDAT<15:0> 0000                         |       |                                         |       |        |       |      |        |        |        |        |        |        |        |        |        |            |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | —                 | _                 | -                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 |                   | —                 |                   |                  | —                |