Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

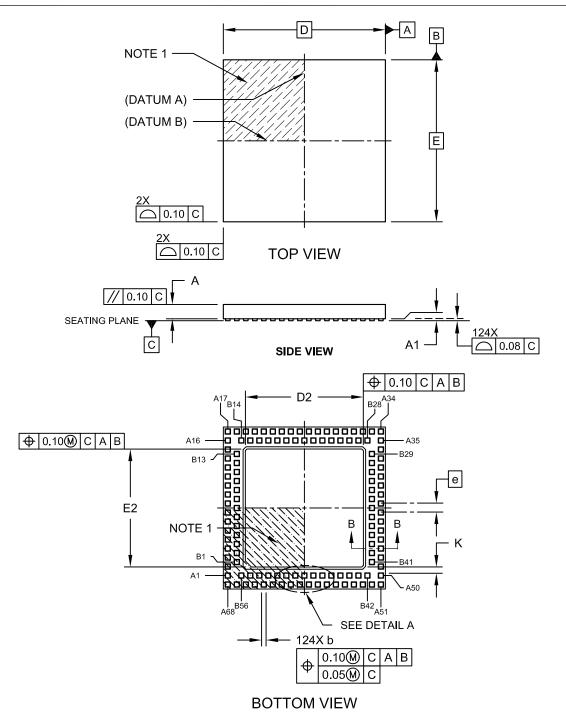

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efh064-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                                     |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                         |

| EBIA0    | _                      | 44              | B24             | 30                       | 0           | —              | External Bus Interface Address Bus  |

| EBIA1    | _                      | 43              | A28             | 51                       | 0           | _              | 7                                   |

| EBIA2    |                        | 16              | B9              | 21                       | 0           |                | 1                                   |

| EBIA3    |                        | 12              | B7              | 52                       | 0           |                | 1                                   |

| EBIA4    |                        | 11              | A8              | 68                       | 0           |                | 1                                   |

| EBIA5    |                        | 2               | B1              | 2                        | 0           |                | 1                                   |

| EBIA6    |                        | 6               | B3              | 6                        | 0           |                | 1                                   |

| EBIA7    |                        | 33              | A23             | 48                       | 0           |                | 1                                   |

| EBIA8    |                        | 65              | A44             | 91                       | 0           |                | 1                                   |

| EBIA9    |                        | 64              | B36             | 90                       | 0           |                | 1                                   |

| EBIA10   | _                      | 32              | B18             | 47                       | 0           | _              | 1                                   |

| EBIA11   | _                      | 41              | A27             | 29                       | 0           | —              | 1                                   |

| EBIA12   | _                      | 7               | A6              | 11                       | 0           | _              | 1                                   |

| EBIA13   | _                      | 34              | B19             | 28                       | 0           | —              | 1                                   |

| EBIA14   | _                      | 61              | A42             | 87                       | 0           | —              | 1                                   |

| EBIA15   | _                      | 68              | B38             | 97                       | 0           | —              | 1                                   |

| EBIA16   | _                      | 17              | A11             | 19                       | 0           | —              | 1                                   |

| EBIA17   | _                      | 40              | B22             | 53                       | 0           |                | 1                                   |

| EBIA18   | -                      | 39              | A26             | 92                       | 0           | _              |                                     |

| EBIA19   | -                      | 38              | B21             | 93                       | 0           | _              |                                     |

| EBIA20   | -                      | _               | _               | 94                       | 0           | _              |                                     |

| EBIA21   | _                      | _               | _               | 126                      | 0           | _              | 1                                   |

| EBIA22   | _                      | _               | _               | 117                      | 0           | _              | -                                   |

| EBIA23   | _                      | _               | _               | 103                      | 0           | _              | 1                                   |

| EBID0    | _                      | 91              | B52             | 135                      | I/O         | ST             | External Bus Interface Data I/O Bus |

| EBID1    | _                      | 94              | A64             | 138                      | I/O         | ST             |                                     |

| EBID2    | _                      | 98              | A66             | 142                      | I/O         | ST             | -                                   |

| EBID3    | _                      | 99              | B56             | 143                      | I/O         | ST             | -                                   |

| EBID4    | _                      | 100             | A67             | 144                      | I/O         | ST             | 1                                   |

| EBID5    | _                      | 3               | A3              | 3                        | I/O         | ST             | -                                   |

| EBID6    | _                      | 4               | B2              | 4                        | I/O         | ST             | 1                                   |

| EBID7    | _                      | 5               | A4              | 5                        | I/O         | ST             | 1                                   |

| EBID8    | _                      | 88              | B50             | 128                      | I/O         | ST             | 1                                   |

| EBID9    | _                      | 87              | A60             | 127                      | I/O         | ST             | 1                                   |

| EBID10   | _                      | 86              | B49             | 125                      | I/O         | ST             | 1                                   |

| EBID11   | _                      | 85              | A59             | 124                      | I/O         | ST             | 1                                   |

| EBID12   | _                      | 79              | B43             | 112                      | I/O         | ST             | 1                                   |

| EBID13   | _                      | 80              | A54             | 113                      | I/O         | ST             | 4                                   |

| EBID14   |                        | 77              | B42             | 110                      | I/O         | ST             | 4                                   |

| EBID15   |                        | 78              | A53             | 110                      | I/O         | ST             | 4                                   |

| EBIBS0   |                        |                 |                 | 9                        | 0           |                | External Bus Interface Byte Select  |

| EBIBS1   |                        | <u> </u>        | <u> </u>        | 10                       | 0           |                |                                     |

| EBICS0   |                        | 59              | A41             | 131                      | 0           |                | External Bus Interface Chip Select  |

| EBICS1   |                        |                 |                 | 131                      | 0           |                |                                     |

| EBICS2   |                        |                 |                 | 132                      | 0           |                | 4                                   |

| EBICS2   |                        |                 |                 | 133                      | 0           |                | 4                                   |

#### TABLE 1-13: **EBI PINOUT I/O DESCRIPTIONS**

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

PPS = Peripheral Pin Select

#### REGISTER 11-9: USBIENCSR1: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 1 (ENDPOINT 1-7) (CONTINUED)

#### bit 18 **OVERRUN:** Data Overrun Status bit (*Device mode*)

- 1 = An OUT packet cannot be loaded into the RX FIFO.

- 0 = Written by software to clear this bit

This bit is only valid when the endpoint is operating in ISO mode. In Bulk mode, it always returns zero.

ERROR: No Data Packet Received Status bit (Host mode)

- 1 = Three attempts have been made to receive a packet and no data packet has been received. An interrupt is generated.

- 0 = Written by the software to clear this bit.

This bit is only valid when the RX endpoint is operating in Bulk or Interrupt mode. In ISO mode, it always returns zero.

- bit 17 FIFOFULL: FIFO Full Status bit

- 1 = No more packets can be loaded into the RX FIFO

- 0 = The RX FIFO has at least one free space

- bit 16 RXPKTRDY: Data Packet Reception Status bit

- 1 = A data packet has been received. An interrupt is generated.

- 0 = Written by software to clear this bit when the packet has been unloaded from the RX FIFO.

- bit 15-11 MULT<4:0>: Multiplier Control bits

For Isochronous/Interrupt endpoints or of packet splitting on Bulk endpoints, multiplies TXMAXP by MULT+1 for the payload size.

For Bulk endpoints, MULT can be up to 32 and defines the number of "USB" packets of the specified payload into which a single data packet placed in the FIFO should be split, prior to transfer. The data packet is required to be an exact multiple of the payload specified by TXMAXP.

For Isochronous/Interrupts endpoints operating in Hi-Speed mode, MULT may be either 2 or 3 and specifies the maximum number of such transactions that can take place in a single microframe.

#### bit 10-0 RXMAXP<10:0>: Maximum RX Payload Per Transaction Control bits

This field sets the maximum payload (in bytes) transmitted in a single transaction. The value is subject to the constraints placed by the USB Specification on packet sizes for Bulk, Interrupt and Isochronous transfers in Full-Speed and Hi-Speed operations.

RXMAXP must be set to an even number of bytes for proper interrupt generation in DMA Mode 1.

## TABLE 12-11: PORTE REGISTER MAP FOR 100-PIN, 124-PIN, AND 144-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |                |       |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0400                        | ANSELE                          | 31:16     |       | _     |       |       | —              |       | _            | _            |              | _            | —            |              | _            | _            |              | _            | 0000          |

| 0400                        | ANOLLL                          | 15:0      | —     | _     | —     |       | —              | _     | ANSE9        | ANSE8        | ANSE7        | ANSE6        | ANSE5        | ANSE4        | _            | _            | —            |              | 03F0          |

| 0410                        | TRISE                           | 31:16     | —     | —     | —     | —     | —              | _     | —            | —            | —            | —            | —            | -            | —            | —            | —            | —            | 0000          |

| 0110                        | HUGE                            | 15:0      | —     | -     | —     | —     | —              | -     | TRISE9       | TRISE8       | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | 03FF          |

| 0420                        | PORTE                           | 31:16     | —     | —     | —     | —     | —              |       | —            | —            | —            | —            | —            |              | —            | —            | —            | —            | 0000          |

| 0.20                        |                                 | 15:0      | —     | —     | —     | —     | —              |       | RE9          | RE8          | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 0430                        | LATE                            | 31:16     | —     | —     | —     | —     | —              |       | —            | —            | —            | —            | —            |              | —            | _            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | _     | —     | —     | —              | _     | LATE9        | LATE8        | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | XXXX          |

| 0440                        | ODCE                            | 31:16     | _     | _     | —     | —     | —              | —     | —            | —            |              | —            | —            |              | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | _     | —     | —     | _              | —     | ODCE9        | ODCE8        | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 0450                        | CNPUE                           | 31:16     | —     | _     | —     | —     | _              | —     | —            | —            | _            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | —     | _     | _              | _     | CNPUE9       | CNPUE8       | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPUE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 0460                        | CNPDE                           | 31:16     | _     | _     | —     | _     | _              | _     | —            | _            | _            | —            | —            | _            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _              |       | CNPDE9       | CNPDE8       | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

| 0470                        |                                 | 31:16     | _     | _     | _     | _     | -              | _     |              | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0470                        | CNCONE                          | 15:0      | ON    | _     | _     | _     | EDGE<br>DETECT | _     | —            | —            | —            | _            | —            | _            | _            | _            | _            | _            | 0000          |

| 0480                        | CNENE                           | 31:16     | —     | -     | —     | —     | —              | -     | —            | —            | —            | _            | —            |              | —            | _            | —            | _            | 0000          |

| 0.00                        | 0.12.12                         | 15:0      | _     | _     | —     | —     | _              | _     | CNENE9       | CNENE8       | CNENE7       | CNENE6       | CNENE5       | CNENE4       | CNENE3       | CNENE2       | CNENE1       | CNENE0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | —     | —              |       | —            | —            | —            | —            | —            |              | —            | _            | —            | —            | 0000          |

| 0490                        | CNSTATE                         | 15:0      | _     | -     | —     | —     | —              | _     | CN<br>STATE9 | CN<br>STATE8 | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

| 04A0                        | CNNEE                           | 31:16     | _     |       | -     | _     | -              |       | _            |              | -            | ١            | -            |              |              |              | _            |              | 0000          |

| 04A0                        | CININEL                         | 15:0      | _     |       |       |       | -              |       | CNNEE9       | CNNEE8       | CNNEE7       | CNNEE6       | CNNEE5       | CNNEE4       | CNNEE3       | CNNEE2       | CNNEE1       | CNNEE0       | 0000          |

| 04B0                        | CNFE                            | 31:16     | _     | -     | —     | _     | _              | _     | —            | _            | _            | -            | —            | -            | _            | -            | _            | -            | 0000          |

| 0400                        |                                 | 15:0      | _     |       | —     | —     | _              |       | CNFE9        | CNFE8        | CNFE7        | CNFE6        | CNFE5        | CNFE4        | CNFE3        | CNFE2        | CNFE1        | CNFE0        | 0000          |

| 04C0                        | SRCON0E                         | 31:16     | —     | _     | —     | —     | —              | _     | —            | —            | —            | _            | —            | —            | _            | _            | —            |              | 0000          |

| 0400                        | SILCONUL                        | 15:0      | _     |       | —     | —     | —              | _     | —            | —            | -            |              | —            | —            | SR0E3        | SR0E2        | SR0E1        | SR0E0        | 0000          |

| 04D0                        | SRCON1E                         | 31:16     | —     | _     | —     | —     | —              | _     | —            | —            | —            | _            | —            | —            | —            | _            | —            | —            | 0000          |

| 0400                        | SILCONTE                        | 15:0      | _     | -     | —     | _     | _              | _     | -            | —            | _            | -            | _            | —            | SR1E3        | SR1E2        | SR1E1        | SR1E0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

| SSS                         |                  |           |       |       |       |       |       |       |      | B    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 4444                        | IC4R             | 31:16     | —     | —     | -     | —     | -     | —     | —    | —    | —    | -    | —    | —    | —    | —     | -      | —    | 0000       |

| 1444                        | IC4R             | 15:0      |       | _     | —     | _     |       | _     | _    | _    | _    | —    | —    | —    |      | IC4R  | <3:0>  |      | 0000       |

| 1448                        | IC5R             | 31:16     |       | —     | —     | —     |       | —     | —    |      | —    | _    | _    | _    | _    | _     | _      |      | 0000       |

| 1440                        | 10.51            | 15:0      |       | —     | —     | —     |       | —     | —    | —    | _    | _    | —    | —    |      | IC5R  | <3:0>  |      | 0000       |

| 144C                        | IC6R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1440                        | ICOIX            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | IC6R  | <3:0>  |      | 0000       |

| 1450                        | IC7R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1430                        | 10/10            | 15:0      | _     | _     | —     | —     | _     | —     | —    | _    | _    | —    | _    | —    |      | IC7R  | <3:0>  |      | 0000       |

| 1454                        | IC8R             | 31:16     | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1-0-1                       | 10011            | 15:0      | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | IC8R  | <3:0>  |      | 0000       |

| 1458                        | IC9R             | 31:16     | -     | —     | —     | —     | _     | —     | —    | _    | _    | —    | _    | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | -     | —     |       | —     | _     | _     | —    | —    | _    |      |      | _    |      | IC9R  | <3:0>  |      | 0000       |

| 1460                        | OCFAR            | 31:16     | _     | —     |       | —     | _     | —     | —    | _    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     |       | —     |       | —     | —    |      | _    | —    | —    | —    |      | OCFA  | R<3:0> |      | 0000       |

| 1468                        | U1RXR            | 31:16     | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |      | —     | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |      | U1RXI | R<3:0> |      | 0000       |

| 146C                        | U1CTSR           | 31:16     | _     |       |       | —     | _     | —     | —    | —    | _    |      |      | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | —     | —     | _     | —     | _     | —     | —    | —    | —    | —    | —    | —    |      | U1CTS |        |      | 0000       |

| 1470                        | U2RXR            | 31:16     | _     | —     |       | _     | _     | —     | —    | —    | —    | —    | _    | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | -     | —     | —     | —     | —    | _    | _    | —    | —    | —    |      | U2RXI |        |      | 0000       |

| 1474                        | U2CTSR           | 31:16     | _     | _     |       |       | _     | _     | _    |      | _    |      |      | _    | _    | —     | _      | —    | 0000       |

|                             |                  | 15:0      | _     | _     | -     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2CTS |        |      | 0000       |

| 1478                        | <b>U3RXR</b>     | 31:16     | _     |       | -     | _     | _     |       | _    | _    | _    | —    |      | _    | —    |       | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     | _     | _     |       | _     | _    | _    | _    | _    |      | _    |      | U3RXI |        |      | 0000       |

| 147C                        | <b>U3CTSR</b>    | 31:16     | _     | _     |       | _     | _     | _     | _    | _    | _    |      |      | _    | —    |       | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     |       | _     |       | _     | _    | _    | _    | _    | _    | _    |      | U3CTS | R<3:0> |      | 0000       |

| 1480                        | U4RXR            | 31:16     |       | —     | _     | _     | _     | —     | _    |      | _    | _    | _    | _    | _    |       |        | _    | 0000       |

|                             |                  | 15:0      |       | —     | _     | _     | _     | —     | —    |      | _    | _    | _    | _    |      | U4RXI |        |      | 0000       |

| 1484                        | U4CTSR           | 31:16     |       | —     | _     | _     | _     | —     | —    |      | _    | _    | _    | _    |      | -     | —      | _    | 0000       |

|                             |                  | 15:0      |       | —     | —     | —     | -     | —     | —    | —    | —    |      | _    | —    |      | U4CTS | R<3:0> |      | 0000       |

## TABLE 12-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

## 15.1 Deadman Timer Control Registers

## TABLE 15-1: DEADMAN TIMER REGISTER MAP

| ess                             |                  | â         |       | _     | _     |       |        | _     | _    | _    | Bits         | _    | _        |      |      |      |      |        |            |

|---------------------------------|------------------|-----------|-------|-------|-------|-------|--------|-------|------|------|--------------|------|----------|------|------|------|------|--------|------------|

| Virtual Address<br>(BF80_#)     | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8 | 23/7         | 22/6 | 21/5     | 20/4 | 19/3 | 18/2 | 17/1 | 16/0   | All Resets |

| 0A00                            | DMTCON           | 31:16     | —     | —     | —     | —     | _      | —     | _    |      | —            | —    | —        | _    | —    | —    | —    | —      | 0000       |

| 0400                            | DMICON           | 15:0      | ON    | _     | —     | _     |        | —     |      | _    | _            | _    | _        |      | —    | —    | _    | _      | x000       |

| 0410                            | DMTPRECLR        | 31:16     | _     | _     | —     | _     |        | —     | -    | _    | _            | _    | _        |      | —    | —    | _    | _      | 0000       |

| UATU                            |                  | 15:0      |       |       |       | STEP  | 1<7:0> |       |      |      | _            | _    | _        |      | —    | —    | _    | _      | 0000       |

| 0A20                            | DMTCLR           | 31:16     | —     | —     | —     | —     | _      | —     | _    | _    | —            | —    | —        | _    | —    | —    | —    | _      | 0000       |

| 0720                            |                  | 15:0      | —     | _     | —     | —     | _      | —     | —    | _    | STEP2<7:0>   |      |          |      |      |      | 0000 |        |            |

| 0A30                            | DMTSTAT          | 31:16     | —     | —     | —     | —     | _      | —     | —    | _    | —            | —    | —        | _    | —    | —    | —    | -      | 0000       |

| 07.00                           | DIMIGIAI         | 15:0      | —     | —     | —     | —     | _      | —     | —    | _    | BAD1         | BAD2 | DMTEVENT | _    | —    | —    | —    | WINOPN | 0000       |

| 0A40                            | DMTCNT           | 31:16     |       |       |       |       |        |       |      | COLL | NTER<31:0    | 0~   |          |      |      |      |      |        | 0000       |

| 0740                            | DIVITORI         | 15:0      |       |       |       |       |        |       |      | 000  |              | -0   |          |      |      |      |      |        | 0000       |

| 0A60 DMTPSCNT 31:16 PSCNT<31:0> |                  |           |       |       |       |       |        |       | 0000 |      |              |      |          |      |      |      |      |        |            |

| 0,00                            | Dimit Scivit     | 15:0      |       |       |       |       |        |       |      | 100  |              |      |          |      |      |      |      |        | 00xx       |

| 0A70                            | DMTPSINTV        | 31:16     |       |       |       |       |        |       |      | PSI  | NTV<31:0>    |      |          |      |      |      |      |        | 0000       |

|                                 |                  | 15:0      |       |       |       |       |        |       |      | 1 31 | NT V \ 01.02 | -    |          |      |      |      |      |        | 000x       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

The timer source for each Input Capture module depends on the setting of the ICACLK bit in the CFGCON register. The available configurations are shown in Table 17-1.

| TABLE 17-1: | TIMER SOURCE   |

|-------------|----------------|

|             | CONFIGURATIONS |

| Input Capture<br>Module | Timerx                  | Timery |

|-------------------------|-------------------------|--------|

| ICACLK (CFGCC           | <b>N&lt;17&gt;) =</b> 0 |        |

| IC1                     | Timer2                  | Timer3 |

| •                       | •                       | •      |

| •                       | ٠                       | •      |

| •                       | •                       | •      |

| IC9                     | Timer2                  | Timer3 |

| ICACLK (CFGCC           | N<17>) = 1              |        |

| IC1                     | Timer4                  | Timer5 |

| IC2                     | Timer4                  | Timer5 |

| IC3                     | Timer4                  | Timer5 |

| IC4                     | Timer2                  | Timer3 |

| IC5                     | Timer2                  | Timer3 |

| IC6                     | Timer2                  | Timer3 |

| IC7                     | Timer6                  | Timer7 |

| IC8                     | Timer6                  | Timer7 |

| IC9                     | Timer6                  | Timer7 |

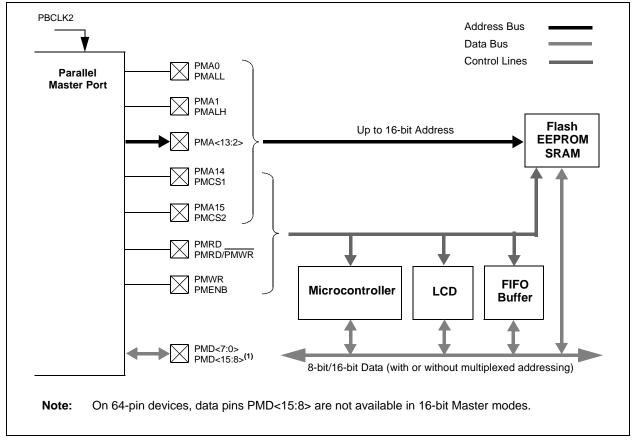

## 23.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features<br>of the PIC32MZ EF family of devices. It is<br>not intended to be a comprehensive refer-<br>ence source. To complement the informa-<br>tion in this data sheet, refer to <b>Section 13</b> . |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | "Parallel Master Port (PMP)"                                                                                                                                                                                                           |

|       | (DS60001128) in the "PIC32 Family Ref-                                                                                                                                                                                                 |

|       | erence Manual", which is available from                                                                                                                                                                                                |

|       | the Microchip web site (www.micro-<br>chip.com/PIC32).                                                                                                                                                                                 |

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. The following are key features of the PMP module:

- 8-bit,16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options:

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- Parallel Slave Port support:

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait states

- Operate during Sleep and Idle modes

- Separate configurable read/write registers or dual buffers for Master mode

- Fast bit manipulation using CLR, SET, and INV registers

Note: On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   |                   | _                 | _                 |                  | —                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              |                   |                   | OB3E              | OB2E              | OB1E             | OB0E             |

#### REGISTER 23-7: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HS = Hardware Set | SC = Software Cleared | Ł                  |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi  | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **IBF:** Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer is occurred (must be cleared in software)

- 0 = No overflow is occurred

#### bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer x Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

#### bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

#### bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

- 0 = No underflow is occurred

- bit 5-4 Unimplemented: Read as '0'

#### bit 3-0 **OBxE:** Output Buffer x Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

| Bit<br>Range                 | Bit<br>31/23/15/7       | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |

|------------------------------|-------------------------|----------------------|--------------------|-------------------|-------------------|-------------------|----------------------|------------------|

| 31:24                        | U-0                     | U-0                  | U-0                | U-0               | U-0               | U-0               | U-0                  | U-0              |

| 31.24                        | —                       |                      | —                  | -                 | —                 |                   | —                    |                  |

| 23:16                        | U-0                     | U-0                  | U-0                | U-0               | U-0               | U-0               | U-0                  | U-0              |

|                              | —                       | —                    | —                  | —                 | —                 | —                 | —                    | _                |

| 45.0                         | R/W-0                   | R/W-0                | R/W-0              | R-0               | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 15:8                         | ALRMEN <sup>(1,2)</sup> | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC          |                   | AMASK             | <3:0> <sup>(2)</sup> |                  |

| 7.0                          | R/W-0                   | R/W-0                | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 7:0 ARPT<7:0> <sup>(2)</sup> |                         |                      |                    |                   |                   |                   |                      |                  |

#### REGISTER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER

#### Legend:

| Logona.           |                  |                                                |                    |  |  |

|-------------------|------------------|------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | /ritable bit U = Unimplemented bit, read as 'C |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                           | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

## bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is more than 32 real-time clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved

- 1011 = Reserved

- 11xx = Reserved

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

#### **Note:** This register is reset only on a Power-on Reset (POR).

© 2015-2016 Microchip Technology Inc.

#### REGISTER 28-20: ADCCMPCON1: ADC DIGITAL COMPARATOR 1 CONTROL REGISTER

- bit 3 IEHIHI: High/High Digital Comparator 0 Event bit

- 1 = Generate a Digital Comparator 0 Event when DCMPHI<15:0> ≤ DATA<31:0>

- 0 = Do not generate an event

- bit 2 IEHILO: High/Low Digital Comparator 0 Event bit

- 1 = Generate a Digital Comparator 0 Event when DATA<31:0> < DCMPHI<15:0>

- 0 = Do not generate an event

- bit 1 IELOHI: Low/High Digital Comparator 0 Event bit

- 1 = Generate a Digital Comparator 0 Event when DCMPLO<15:0>  $\leq$  DATA<31:0>

- 0 = Do not generate an event

- bit 0 IELOLO: Low/Low Digital Comparator 0 Event bit

- 1 = Generate a Digital Comparator 0 Event when DATA<31:0> < DCMPLO<15:0>

- 0 = Do not generate an event

#### 30.1 **Ethernet Control Registers**

## TABLE 30-5: ETHERNET CONTROLLER REGISTER SUMMARY

| ess                         |                                 |               |                  |              |              |       |       |       |                | В                   | its          |               |               |        |              |               |               |               |            |

|-----------------------------|---------------------------------|---------------|------------------|--------------|--------------|-------|-------|-------|----------------|---------------------|--------------|---------------|---------------|--------|--------------|---------------|---------------|---------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15            | 30/14        | 29/13        | 28/12 | 27/11 | 26/10 | 25/9           | 24/8                | 23/7         | 22/6          | 21/5          | 20/4   | 19/3         | 18/2          | 17/1          | 16/0          | All Resets |

| 2000                        | ETHCON1                         | 31:16         |                  |              |              |       |       |       |                |                     |              | 0000          |               |        |              |               |               |               |            |

| 2000                        | LINCONT                         | 15:0          | ON               | —            | SIDL         | _     | _     | _     | TXRTS          | RXEN                | AUTOFC       | _             | _             | MANFC  | —            | —             | —             | BUFCDEC       | 0000       |

| 2010                        | ETHCON2                         | 31:16         | _                |              | _            |       | _     | —     | _              | _                   | —            | —             | —             | —      | _            |               |               |               | 0000       |

|                             |                                 | 15:0          | _                | _            |              | _     | _     |       |                |                     | XBUFSZ<6:0   | >             |               |        |              | -             | _             | _             | 0000       |

| 2020                        | ETHTXST                         | 31:16<br>15:0 |                  |              |              |       |       |       | TYOTAD         | TXSTADE<br>DR<15:2> | )R<31:16>    |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 31:16         |                  |              |              |       |       |       | TXSTADI        |                     | DR<31:16>    |               |               |        |              |               | _             | —             | 0000       |

| 2030                        | ETHRXST                         | 15:0          |                  |              |              |       |       |       | RXSTAD         | DR<15:2>            | 01(<01.10>   |               |               |        |              |               | _             | _             | 0000       |

|                             |                                 | 31:16         |                  |              |              |       |       |       | 10101712       |                     |              |               |               |        |              |               |               |               | 0000       |

| 2040                        | ETHHT0                          | 15:0          |                  |              |              |       |       |       |                | HT<                 | 31:0>        |               |               |        |              |               |               |               | 0000       |

| 2050                        |                                 | 31:16         | 0.0              |              |              |       |       |       |                |                     |              | 0000          |               |        |              |               |               |               |            |

| 2050                        | ETHHT1                          | 15:0          |                  |              |              |       |       |       |                |                     |              | 0000          |               |        |              |               |               |               |            |

| 2060                        | ETHPMM0                         | 31:16         | PMM<31:0>        |              |              |       |       |       |                |                     |              | 0000          |               |        |              |               |               |               |            |

| 2000                        |                                 | 15:0          | FIVIIVI<31:U> 00 |              |              |       |       |       |                |                     |              | 0000          |               |        |              |               |               |               |            |

| 2070                        | ETHPMM1                         | 31:16         | PMM<63:32>       |              |              |       |       |       |                |                     |              | 0000          |               |        |              |               |               |               |            |

|                             |                                 | 15:0          |                  |              |              |       |       |       |                |                     |              |               |               | 1      |              | 1             | 1             | 1             | 0000       |

| 2080                        | ETHPMCS                         | 31:16<br>15:0 | _                | _            |              | _     | —     | _     |                | PMCS                | —<br><15:0>  | —             | —             | —      | —            | —             | _             | —             | 0000       |

|                             |                                 | 31:16         | _                | _            | _            | _     | _     | _     | _              | - FINICO            |              | _             | _             | _      | _            | _             | _             | _             | 0000       |

| 2090                        | ETHPMO                          | 15:0          |                  |              |              |       |       |       |                | PMO.                |              |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 31:16         | _                | _            | _            | _     | _     | _     | _              | _                   |              | _             | _             | _      |              | _             | _             | _             | 0000       |

| 20A0                        | ETHRXFC                         | 15:0          | HTEN             | MPEN         | _            | NOTPM |       | PMMO  | DE<3:0>        |                     | CRC<br>ERREN | CRC<br>OKEN   | RUNT<br>ERREN | RUNTEN | UCEN         | NOT<br>MEEN   | MCEN          | BCEN          | 0000       |

| 2080                        | ETHRXWM                         | 31:16         | _                | _            | _            | _     | _     | _     | _              |                     |              |               |               | RXFW   | M<7:0>       |               |               |               | 0000       |

| 2080                        |                                 | 15:0          | _                | -            | —            | _     | -     | -     | —              | —                   |              |               |               | RXEW   | M<7:0>       |               |               |               | 0000       |

|                             |                                 | 31:16         | —                | —            | —            | _     | _     | _     | —              | —                   | —            | —             | —             | _      | —            | —             | —             | —             | 0000       |

| 20C0                        | ETHIEN                          | 15:0          | —                | TX<br>BUSEIE | RX<br>BUSEIE | —     | —     | —     | EW<br>MARKIE   | FW<br>MARKIE        | RX<br>DONEIE | PK<br>TPENDIE | RX<br>ACTIE   | _      | TX<br>DONEIE | TX<br>ABORTIE | RX<br>BUFNAIE | RX<br>OVFLWIE | 0000       |

| 20D0                        | ETHIRQ                          | 31:16         | —                | —            | —            | _     | _     | _     | —              | —                   | —            | —             | —             | _      | —            | —             | -             | —             | 0000       |

|                             |                                 | 15:0          | _                | TXBUSE       | RXBUSE       |       | _     | _     | EWMARK         | FWMARK              | RXDONE       | PKTPEND       | RXACT         | —      | TXDONE       | TXABORT       | RXBUFNA       | RXOVFLW       | 0000       |

| 20E0                        | ETHSTAT                         | 31:16         | —                | _            | _            | _     | _     | _     | _              | _                   |              |               |               | BUFCI  | NT<7:0>      |               |               |               | 0000       |

| <u> </u>                    |                                 | 15:0          | _                | —            | _            | _     | —     | —     |                | _                   | BUSY         | TXBUSY        | RXBUSY        | -      | -            | _             | _             |               | 0000       |

| 2100                        | ETH<br>RXOVFLOW                 | 31:16         | _                | -            | —            | _     | -     | —     | _              |                     | —<br>—       | —             | —             | -      | _            | -             | -             | _             | 0000       |

|                             | NAUVELOW                        | 15:0          | ualua an Da      |              |              |       |       |       | overle einerel | RXOVFLW             | CNT<15:0>    |               |               |        |              |               |               |               | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information. Note 1:

Reset values default to the factory programmed value. 2:

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24     |                   |                   |                   |                   | -                 | —                 |                  | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | _                 | _                 | _                 | _                 | —                 | —                 | _                | _                |

| 15:8      | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15.6      | _                 | TXBUSE            | RXBUSE            | _                 | —                 | —                 | EWMARK           | FWMARK           |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       | RXDONE            | PKTPEND           | RXACT             |                   | TXDONE            | TXABORT           | RXBUFNA          | RXOVFLW          |

#### **REGISTER 30-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

| bit 31-15 <b>Unimplemented:</b> Read as '0' |  |

|---------------------------------------------|--|

| Dil 31-15 Unimplemented: Read as 0          |  |

- bit 14 **TXBUSE:** Transmit BVCI Bus Error Interrupt bit<sup>(2)</sup>

- 1 = BVCI Bus Error has occurred 0 = BVCI Bus Error has not occurred

This bit is set when the TX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.

- bit 13 **RXBUSE:** Receive BVCI Bus Error Interrupt bit<sup>(2)</sup>

- 1 = BVCI Bus Error has occurred

- 0 = BVCI Bus Error has not occurred

This bit is set when the RX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.

#### bit 12-10 Unimplemented: Read as '0'

- bit 9 EWMARK: Empty Watermark Interrupt bit<sup>(2)</sup>

- 1 = Empty Watermark pointer reached

0 = No interrupt pending

This bit is set when the RX Descriptor Buffer Count is less than or equal to the value in the RXEWM bit (ETHRXWM<0:7>) value. It is cleared by BUFCNT bit (ETHSTAT<16:23>) being incremented by hardware. Writing a '0' or a '1' has no effect.

#### bit 8 FWMARK: Full Watermark Interrupt bit<sup>(2)</sup>

## 1 = Full Watermark pointer reached

0 = No interrupt pending

This bit is set when the RX Descriptor Buffer Count is greater than or equal to the value in the RXFWM bit (ETHRXWM<16:23>) field. It is cleared by writing the BUFCDEC (ETHCON1<0>) bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect.

- Note 1: This bit is only used for TX operations.

- 2: This bit is are only used for RX operations.

**Note:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|

| 31:24        | U-0                      | U-0                     |

| 31.24        | —                 | —                 | —                 | —                 | _                 |                   | —                        | —                       |

| 23:16        | U-0                      | U-0                     |

| 23.10        | —                 | —                 | —                 | —                 | _                 |                   | —                        | _                       |

| 15:8         | U-0                      | U-0                     |

| 15.0         | —                 | —                 | —                 | —                 | _                 |                   | —                        | _                       |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   |

| 7.0          |                   |                   | _                 | _                 | _                 | TESTBP            | TESTPAUSE <sup>(1)</sup> | SHRTQNTA <sup>(1)</sup> |

### REGISTER 30-30: EMAC1TEST: ETHERNET CONTROLLER MAC TEST REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-3 Unimplemented: Read as '0'

- bit 2 TESTBP: Test Backpressure bit

- 1 = The MAC will assert backpressure on the link. Backpressure causes preamble to be transmitted, raising carrier sense. A transmit packet from the system will be sent during backpressure.

0 = Normal operation

#### bit 1 **TESTPAUSE:** Test PAUSE bit<sup>(1)</sup>

1 = The MAC Control sub-layer will inhibit transmissions, just as if a PAUSE Receive Control frame with a non-zero pause time parameter was received

0 = Normal operation

#### bit 0 SHRTQNTA: Shortcut PAUSE Quanta bit<sup>(1)</sup>

1 = The MAC reduces the effective PAUSE Quanta from 64 byte-times to 1 byte-time

0 = Normal operation

**Note 1:** This bit is only used for testing purposes.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

|              |                   | LOISTEN           |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   | —                 | —                 | —                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   | —                 | —                 | —                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                   | —                 |                   | —                 | —                 | —                 | —                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 7.0          | _                 | —                 | _                 | —                 | —                 | —                 | SCAN             | READ             |

# REGISTER 30-32: EMAC1MCMD: ETHERNET CONTROLLER MAC MII MANAGEMENT COMMAND REGISTER

#### Legend:

| - 3               |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-2 Unimplemented: Read as '0'

- bit 1 SCAN: MII Management Scan Mode bit

- 1 = The MII Management module will perform read cycles continuously (for example, useful for monitoring the Link Fail)

- 0 = Normal Operation

#### bit 0 READ: MII Management Read Command bit

- 1 = The MII Management module will perform a single read cycle. The read data is returned in the EMAC1MRDD register

- 0 = The MII Management module will perform a write cycle. The write data is taken from the EMAC1MWTD register

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

|              |                   | LOIGIEN           |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 | —                 | —                 | -                 |                  | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | —                 | —                 | —                 | -                 |                  | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 | —                 | —                 | —                 | -                 |                  | -                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | —                 | —                 | —                 | LINKFAIL          | NOTVALID          | SCAN             | MIIMBUSY         |

# REGISTER 30-36: EMAC1MIND: ETHERNET CONTROLLER MAC MII MANAGEMENT INDICATORS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | it U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|---------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |

#### bit 31-4 Unimplemented: Read as '0'

bit 3 LINKFAIL: Link Fail bit

When '1' is returned - indicates link fail has occurred. This bit reflects the value last read from the PHY status register.

bit 2 NOTVALID: MII Management Read Data Not Valid bit When '1' is returned - indicates an MII management read cycle has not completed and the Read Data is not yet valid.

## bit 1 SCAN: MII Management Scanning bit When '1' is returned - indicates a scan operation (continuous MII Management Read cycles) is in progress.

#### bit 0 MIIMBUSY: MII Management Busy bit

When '1' is returned - indicates MII Management module is currently performing an MII Management Read or Write cycle.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Peripheral               | PMDx bit Name | Register Name and Bit Location |

|--------------------------|---------------|--------------------------------|

| UART3                    | U3MD          | PMD5<2>                        |

| UART4                    | U4MD          | PMD5<3>                        |

| UART5                    | U5MD          | PMD5<4>                        |

| UART6                    | U6MD          | PMD5<5>                        |

| SPI1                     | SPI1MD        | PMD5<8>                        |

| SPI2                     | SPI2MD        | PMD5<9>                        |

| SPI3                     | SPI3MD        | PMD5<10>                       |

| SPI4                     | SPI4MD        | PMD5<11>                       |

| SPI5                     | SPI5MD        | PMD5<12>                       |

| SPI6                     | SPI6MD        | PMD5<13>                       |

| I2C1                     | I2C1MD        | PMD5<16>                       |

| I2C2                     | I2C2MD        | PMD5<17>                       |

| 12C3                     | I2C3MD        | PMD5<18>                       |

| I2C4                     | I2C4MD        | PMD5<19>                       |

| 12C5                     | I2C5MD        | PMD5<20>                       |

| USB <sup>(2)</sup>       | USBMD         | PMD5<24>                       |

| CAN1                     | CAN1MD        | PMD5<28>                       |

| CAN2                     | CAN2MD        | PMD5<29>                       |

| RTCC                     | RTCCMD        | PMD6<0>                        |

| Reference Clock Output 1 | REFO1MD       | PMD6<8>                        |

| Reference Clock Output 2 | REFO2MD       | PMD6<9>                        |

| Reference Clock Output 3 | REFO3MD       | PMD6<10>                       |

| Reference Clock Output 4 | REFO4MD       | PMD6<11>                       |

| PMP                      | PMPMD         | PMD6<16>                       |

| EBI                      | EBIMD         | PMD6<17>                       |

| SQI1                     | SQI1MD        | PMD6<23>                       |

| Ethernet                 | ETHMD         | PMD6<28>                       |

| DMA                      | DMAMD         | PMD7<4>                        |

| Random Number Generator  | RNGMD         | PMD7<20>                       |

| Crypto                   | CRYPTMD       | PMD7<22>                       |

## TABLE 33-1: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS<sup>(1)</sup> (CONTINUED)

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the lists of available peripherals.

2: Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

### TABLE 37-20: INTERNAL FRC ACCURACY

| AC CHARACTERISTICS |                        | (unless          | d Operat<br>otherwis<br>g temper | se stated | )<br>-40°C | <b>2.1V to 3.6V</b><br>C $\leq$ TA $\leq$ +85°C for Industrial<br>C $\leq$ TA $\leq$ +125°C for Extended |

|--------------------|------------------------|------------------|----------------------------------|-----------|------------|----------------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Characteristics        |                  | Тур.                             | Max.      | Units      | Conditions                                                                                               |

| Internal           | FRC Accuracy @ 8.00 MH | z <sup>(1)</sup> |                                  |           |            |                                                                                                          |

| F20                | FRC                    | -5               | _                                | +5        | %          | $0^{\circ}C \le TA \le +85^{\circ}C$                                                                     |

|                    |                        | -8               | _                                | +8        | %          | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                                   |

|                    |                        | -10              | _                                | +10       | %          | $-40^{\circ}C \le TA \le +125^{\circ}C$                                                                  |

**Note 1:** Frequency calibrated at +25°C and 3.3V. The TUN bits (OSCTUN<5:0>) can be used to compensate for temperature drift.

#### TABLE 37-21: INTERNAL LPRC ACCURACY

| AC CHARACTERISTICS                        |                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |       |                                         |  |

|-------------------------------------------|-----------------|------------------------------------------------------|------|------|-------|-----------------------------------------|--|

| Param.<br>No.                             | Characteristics | Min.                                                 | Тур. | Max. | Units | Conditions                              |  |

| Internal LPRC @ 32.768 kHz <sup>(1)</sup> |                 |                                                      |      |      |       |                                         |  |

| F21                                       | LPRC            | -8                                                   | _    | +8   | %     | $0^{\circ}C \le TA \le +85^{\circ}C$    |  |

|                                           |                 | -25                                                  |      | +25  | %     | $-40^{\circ}C \le TA \le +125^{\circ}C$ |  |