Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | MIPS32® M-Class                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 250MHz                                                                               |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                         |

| Number of I/O              | 46                                                                                   |

| Program Memory Size        | 2MB (2M x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 512K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x12b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 80°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-TQFP                                                                              |

| Supplier Device Package    | 64-TQFP (10x10)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efh064t-250i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: ADC PINOUT I/O DESCRIPTIONS

|          | Pin Number             |                 |                 |                          |             |                |                       |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description           |

| AN0      | 16                     | 25              | A18             | 36                       | I           | Analog         | Analog Input Channels |

| AN1      | 15                     | 24              | A17             | 35                       | I           | Analog         |                       |

| AN2      | 14                     | 23              | A16             | 34                       | I           | Analog         |                       |

| AN3      | 13                     | 22              | A14             | 31                       | I           | Analog         |                       |

| AN4      | 12                     | 21              | A13             | 26                       | I           | Analog         |                       |

| AN5      | 23                     | 34              | B19             | 49                       | I           | Analog         |                       |

| AN6      | 24                     | 35              | A24             | 50                       | I           | Analog         |                       |

| AN7      | 27                     | 41              | A27             | 59                       | I           | Analog         |                       |

| AN8      | 28                     | 42              | B23             | 60                       | I           | Analog         |                       |

| AN9      | 29                     | 43              | A28             | 61                       | I           | Analog         |                       |

| AN10     | 30                     | 44              | B24             | 62                       | I           | Analog         |                       |

| AN11     | 10                     | 16              | В9              | 21                       | I           | Analog         |                       |

| AN12     | 6                      | 12              | В7              | 16                       | I           | Analog         |                       |

| AN13     | 5                      | 11              | A8              | 15                       | I           | Analog         |                       |

| AN14     | 4                      | 10              | B6              | 14                       | I           | Analog         |                       |

| AN15     | 3                      | 5               | A4              | 5                        | I           | Analog         |                       |

| AN16     | 2                      | 4               | B2              | 4                        | I           | Analog         |                       |

| AN17     | 1                      | 3               | A3              | 3                        | I           | Analog         |                       |

| AN18     | 64                     | 100             | A67             | 144                      | I           | Analog         |                       |

| AN19     | _                      | 9               | A7              | 13                       | I           | Analog         |                       |

| AN20     | _                      | 8               | B5              | 12                       | I           | Analog         |                       |

| AN21     | _                      | 7               | A6              | 11                       | I           | Analog         |                       |

| AN22     | _                      | 6               | В3              | 6                        | I           | Analog         |                       |

| AN23     | _                      | 1               | A2              | 1                        | I           | Analog         |                       |

| AN24     | _                      | 17              | A11             | 22                       | I           | Analog         |                       |

| AN25     | _                      | 18              | B10             | 23                       | I           | Analog         |                       |

| AN26     | _                      | 19              | A12             | 24                       | I           | Analog         |                       |

| AN27     | _                      | 28              | B15             | 39                       | I           | Analog         |                       |

| AN28     | _                      | 29              | A20             | 40                       | I           | Analog         |                       |

| AN29     | _                      | 38              | B21             | 56                       | I           | Analog         |                       |

| AN30     | _                      | 39              | A26             | 57                       | I           | Analog         | 1                     |

| AN31     | _                      | 40              | B22             | 58                       | I           | Analog         | ]                     |

| AN32     | _                      | 47              | B27             | 69                       | I           | Analog         | 1                     |

| AN33     | _                      | 48              | A32             | 70                       | I           | Analog         | 1                     |

| AN34     | _                      | 2               | B1              | 2                        | I           | Analog         | 1                     |

| AN35     | _                      | _               | A5              | 7                        | I           | Analog         | 1                     |

|          |                        |                 |                 |                          | •           | •              |                       |

**Legend:** CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input O = Output

PPS = Peripheral Pin Select

P = Power I = Input

#### 3.1.4 FLOATING POINT UNIT (FPU)

The Floating Point Unit (FPU), Coprocessor (CP1), implements the MIPS Instruction Set Architecture for floating point computation. The implementation supports the ANSI/IEEE Standard 754 (IEEE for Binary Floating Point Arithmetic) for 32-bit and 64-bit floating point data formats. The FPU can be programmed to have thirty-two 32-bit or 64-bit floating point registers used for floating point operations.

The performance is optimized for 32-bit formats. Most instructions have one FPU cycle throughput and four FPU cycle latency. The FPU implements the multiply-add (MADD) and multiply-sub (MSUB) instructions with intermediate rounding after the multiply function. The result is guaranteed to be the same as executing a MUL and an ADD instruction separately, but the instruction latency, instruction fetch, dispatch bandwidth, and the total number of register accesses are improved.

IEEE denormalized input operands and results are supported by hardware for some instructions. IEEE denormalized results are not supported by hardware in general, but a fast flush-to-zero mode is provided to optimize performance. The fast flush-to-zero mode is enabled through the FCCR register, and use of this mode is recommended for best performance when denormalized results are generated.

The FPU has a separate pipeline for floating point instruction execution. This pipeline operates in parallel with the integer core pipeline and does not stall when the integer pipeline stalls. This allows long-running FPU operations, such as divide or square root, to be partially masked by system stalls and/or other integer unit instructions. Arithmetic instructions are always dispatched and completed in order, but loads and stores can complete out of order. The exception model is "precise" at all times.

Table 3-4 contains the floating point instruction latencies and repeat rates for the processor core. In this table, 'Latency' refers to the number of FPU cycles necessary for the first instruction to produce the result needed by the second instruction. The "Repeat Rate" refers to the maximum rate at which an instruction can be executed per FPU cycle.

TABLE 3-4: FPU INSTRUCTION

LATENCIES AND REPEAT

RATES

| Op code                                                                                             | Latency<br>(FPU<br>Cycles) | Repeat<br>Rate<br>(FPU<br>Cycles) |

|-----------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------|

| ABS.[S,D], NEG.[S,D], ADD.[S,D], SUB.[S,D], C.cond.[S,D], MUL.S                                     | 4                          | 1                                 |

| MADD.S, MSUB.S,<br>NMADD.S, NMSUB.S,<br>CABS.cond.[S,D]                                             | 4                          | 1                                 |

| CVT.D.S, CVT.PS.PW,<br>CVT.[S,D].[W,L]                                                              | 4                          | 1                                 |

| CVT.S.D, CVT.[W,L].[S,D], CEIL.[W,L].[S,D], FLOOR.[W,L].[S,D], ROUND.[W,L].[S,D], TRUNC.[W,L].[S,D] | 4                          | 1                                 |

| MOV.[S,D], MOVF.[S,D],<br>MOVN.[S,D],<br>MOVT.[S,D], MOVZ.[S,D]                                     | 4                          | 1                                 |

| MUL.D                                                                                               | 5                          | 2                                 |

| MADD.D, MSUB.D,<br>NMADD.D, NMSUB.D                                                                 | 5                          | 2                                 |

| RECIP.S                                                                                             | 13                         | 10                                |

| RECIP.D                                                                                             | 26                         | 21                                |

| RSQRT.S                                                                                             | 17                         | 14                                |

| RSQRT.D                                                                                             | 36                         | 31                                |

| DIV.S, SQRT.S                                                                                       | 17                         | 14                                |

| DIV.D, SQRT.D                                                                                       | 32                         | 29                                |

| MTC1, DMTC1, LWC1,<br>LDC1, LDXC1, LUXC1,<br>LWXC1                                                  | 4                          | 1                                 |

| MFC1, DMFC1, SWC1,<br>SDC1, SDXC1, SUXC1,<br>SWXC1                                                  | 1                          | 1                                 |

**Legend:** S = Single (32-bit) D = Double (64-bit)

W = Word (32-bit) L = Long word (64-bit)

TABLE 4-15: SYSTEM BUS TARGET 7 REGISTER MAP

| ess                         |                  | _         |       |       |       |          |          |       |       |      | Bits      |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|-----------|-------|----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7      | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| 9C20                        | SBT7ELOG1        | 31:16     | MULTI | _     | _     | _        |          | CODE  | <3:0> |      | _         | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 9020                        | 361722061        | 15:0      |       |       |       | INIT     | ΓID<7:0> |       |       |      |           | REGIO | N<3:0>   |      | _      | С      | MD<2:0> |        | 0000          |

| 9C24                        | SBT7ELOG2        | 31:16     | _     | _     | _     | _        | _        | _     | _     | _    |           | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 9024                        | 3B17LLOG2        | 15:0      | _     | _     | _     | _        | _        | _     | -     | _    | _         | _     | _        | _    | _      | _      | GROU    | P<1:0> | 0000          |

| 9C28                        | SBT7ECON         | 31:16     | _     | _     | _     | _        | _        | _     | -     | ERRP | _         | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 9020                        | 3B17ECON         | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    |           | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 9C30                        | SBT7ECLRS        | 31:16     | _     | _     | _     | _        | _        | _     | _     | _    |           | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 3030                        | OBTTECENO        | 15:0      | _     | _     | _     | _        | _        | _     |       | _    |           | _     | _        | _    | _      | _      | _       | CLEAR  | 0000          |

| 9C38                        | SBT7ECLRM        | 31:16     | _     | _     | _     | _        | _        | _     |       | _    |           | _     | _        | _    | _      | _      | _       | _      | 0000          |

| 3030                        | OD17 LOLKW       | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    |           | _     | _        | _    | _      | _      | _       | CLEAR  | 0000          |

| 9C40                        | SBT7REG0         | 31:16     |       |       |       |          |          |       |       | BAS  | SE<21:6>  |       |          |      |        |        |         |        | xxxx          |

| 3040                        | OBITICEOU        | 15:0      |       |       | BA    | ASE<5:0> |          |       | PRI   | _    | SIZE<4:0> |       |          |      |        | _      | _       | _      | xxxx          |

| 9C50                        | SBT7RD0          | 31:16     | _     | _     | _     | _        | _        | _     |       | _    | _         | _     | _        | _    | _      | _      | _       | _      | xxxx          |

| 3030                        | SBITTED          | 15:0      | _     | _     | _     | _        | _        | _     |       | _    | _         | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9C58                        | SBT7WR0          | 31:16     | _     | _     | _     | _        | _        | _     |       | _    | _         | _     | _        | _    | _      | _      | _       | _      | xxxx          |

| 3030                        | OB17 WINO        | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    | _         | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9C60                        | SBT7REG1         | 31:16     |       |       |       |          |          |       |       | BAS  | SE<21:6>  |       |          |      |        |        |         |        | xxxx          |

| 3000                        | OBTACOT          | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | _    |           |       | SIZE<4:0 | >    |        | _      | _       | _      | xxxx          |

| 9C70                        | SBT7RD1          | 31:16     | _     | _     | _     | _        | _        | _     | _     | _    | _         | _     | _        | _    | _      | _      | _       | _      | xxxx          |

| 3070                        | 3517101          | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    | _         | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9C78                        | SBT7WR1          | 31:16     | _     | _     | _     | _        | _        | _     | _     | _    | _         | _     | _        | _    | _      | _      | _       | _      | xxxx          |

| 3070                        | OB17WK1          | 15:0      | _     | _     | _     | _        | _        | _     | _     | _    | _         | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

#### REGISTER 5-8: NVMBWP: FLASH BOOT (PAGE) WRITE-PROTECT REGISTER

- bit 4 **UBWP4:** Upper Boot Alias Page 4 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC30000 through 0x1FC33FFF enabled

- 0 = Write protection for physical address 0x01FC30000 through 0x1FC33FFF disabled

- bit 3 **UBWP3:** Upper Boot Alias Page 3 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC2C000 through 0x1FC2FFFF enabled

- 0 = Write protection for physical address 0x01FC2C000 through 0x1FC2FFFF disabled

- bit 2 **UBWP2:** Upper Boot Alias Page 2 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC28000 through 0x1FC2BFFF enabled

- 0 = Write protection for physical address 0x01FC28000 through 0x1FC2BFFF disabled

- bit 1 **UBWP1:** Upper Boot Alias Page 1 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC24000 through 0x1FC27FFF enabled

- 0 = Write protection for physical address 0x01FC24000 through 0x1FC27FFF disabled

- bit 0 **UBWP0:** Upper Boot Alias Page 0 Write-protect bit<sup>(1)</sup>

- 1 = Write protection for physical address 0x01FC20000 through 0x1FC23FFF enabled

- 0 = Write protection for physical address 0x01FC20000 through 0x1FC23FFF disabled

- **Note 1:** These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (LBWPULOCK or UBWPULOCK) is set.

Note: The bits in this register are only writable when the NVMKEY unlock sequence is followed.

TABLE 12-3: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR              | RPnR bits                  | RPnR Value to Peripheral<br>Selection         |  |  |

|----------------------|-----------------------|----------------------------|-----------------------------------------------|--|--|

| RPD1                 | RPD1R                 | RPD1R<3:0>                 | 0000 = <u>No Con</u> nect                     |  |  |

| RPG9                 | RPG9R                 | RPG9R<3:0>                 | 0001 = U1RTS                                  |  |  |

| RPB14                | RPB14R                | RPB14R<3:0>                | 0010 = <u>U2TX</u><br>0011 = <u>U5RTS</u>     |  |  |

| RPD0                 | RPD0R                 | RPD0R<3:0>                 | 0100 = U6TX                                   |  |  |

| RPB6                 | RPB6R                 | RPB6R<3:0>                 | 0101 = Reserved                               |  |  |

| RPD5                 | RPD5R                 | RPD5R<3:0>                 | 0110 = SS2<br>0111 = Reserved                 |  |  |

| RPB2                 | RPB2R                 | RPB2R<3:0>                 | 1000 = SDO4                                   |  |  |

| RPF3                 | RPF3R                 | RPF3R<3:0>                 | 1001 = Reserved                               |  |  |

| RPF13 <sup>(1)</sup> | RPF13R <sup>(1)</sup> | RPF13R<3:0> <sup>(1)</sup> | 1010 = SDO6 <sup>(1)</sup><br>1011 = OC2      |  |  |

| RPC2 <sup>(1)</sup>  | RPC2R <sup>(1)</sup>  | RPC2R<3:0> <sup>(1)</sup>  | 1100 = OC1                                    |  |  |

| RPE8 <sup>(1)</sup>  | RPE8R <sup>(1)</sup>  | RPE8R<3:0> <sup>(1)</sup>  | 1101 = OC9                                    |  |  |

| RPF2 <sup>(1)</sup>  | RPF2R <sup>(1)</sup>  | RPF2R<3:0> <sup>(1)</sup>  | 1110 = Reserved<br>1111 = C2TX <sup>(3)</sup> |  |  |

Note 1: This selection is not available on 64-pin devices.

<sup>2:</sup> This selection is not available on 64-pin or 100-pin devices.

<sup>3:</sup> This selection is not available on devices without a CAN module.

#### REGISTER 15-5: DMTCNT: DEADMAN TIMER COUNT REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 31:24     |                   | COUNTER<31:24>    |                   |                   |                   |                   |                  |                  |  |

| 22:40     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23:16     |                   |                   |                   | COUNTER           | ?<23:16>          |                   |                  |                  |  |

| 45.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8      |                   | COUNTER<15:8>     |                   |                   |                   |                   |                  |                  |  |

| 7.0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0       |                   |                   |                   | COUNTE            | R<7:0>            |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 **COUNTER<31:0>:** Read current contents of DMT counter

#### REGISTER 15-6: DMTPSCNT: POST STATUS CONFIGURE DMT COUNT STATUS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 31.24     |                   |                   |                   | PSCNT<            | 31:24>            |                   |                  |                  |  |

| 23:16     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23.10     |                   |                   |                   | PSCNT<            | 23:16>            |                   |                  |                  |  |

| 15.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8      |                   | PSCNT<15:8>       |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R-0               | R-0               | R-0               | R-y               | R-y               | R-y               | R-y              | R-y              |  |

| 7.0       | PSCNT<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |

Legend:y = Value set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-8 **PSCNT<31:0>:** DMT Instruction Count Value Configuration Status bits

This is always the value of the DMTCNT<4:0> bits in the DEVCFG1 Configuration register.

REGISTER 20-14: SQI1BDCON: SQI BUFFER DESCRIPTOR CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | -                 | _                 | -                 | 1                 |                   |                  | -                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | -                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | -                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 | -                 | START             | POLLEN           | DMAEN            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-3 Unimplemented: Read as '0'

bit 2 START: Buffer Descriptor Processor Start bit

1 = Start the buffer descriptor processor0 = Disable the buffer descriptor processor

bit 1 POLLEN: Buffer Descriptor Poll Enable bit

1 = BDP poll is enabled

0 = BDP poll is not enabled

bit 0 **DMAEN:** DMA Enable bit

1 = DMA is enabled

0 = DMA is disabled

#### REGISTER 20-15: SQI1BDCURADD: SQI BUFFER DESCRIPTOR CURRENT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        |                   | BDCURRADDR<31:24> |                   |                   |                   |                   |                  |                  |  |  |

| 22.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        |                   |                   |                   | BDCURRADI         | OR<23:16>         |                   |                  |                  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         |                   |                   |                   | BDCURRAD          | DR<15:8>          |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | BDCURRADDR<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 BDCURRADDR<31:0>: Current Buffer Descriptor Address bits

These bits contain the address of the current descriptor being processed by the Buffer Descriptor Processor.

#### REGISTER 20-22: SQI1INTSIGEN: SQI INTERRUPT SIGNAL ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|              | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | _                 | DMAEISE           | PKT<br>DONEISE    | BD<br>DONEISE    | CON<br>THRISE    |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CON<br>EMPTYISE   | CON<br>FULLISE    | RX<br>THRISE      | RX<br>FULLISE     | RX<br>EMPTYISE    | TX<br>THRISE      | TX<br>FULLISE    | TX<br>EMPTYISE   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-12 Unimplemented: Read as '0'

bit 11 DMAEISE: DMA Bus Error Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 10 **PKTDONEISE:** Receive Error Interrupt Signal Enable bit

1 = Interrupt signal is enabled0 = Interrupt signal is disabled

bit 9 BDDONEISE: Transmit Error Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 8 CONTHRISE: Control Buffer Threshold Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 7 CONEMPTYISE: Control Buffer Empty Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 6 CONFULLISE: Control Buffer Full Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 5 RXTHRISE: Receive Buffer Threshold Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 4 RXFULLISE: Receive Buffer Full Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 3 RXEMPTYISE: Receive Buffer Empty Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 2 TXTHRISE: Transmit Buffer Threshold Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 1 TXFULLISE: Transmit Buffer Full Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

bit 0 TXEMPTYISE: Transmit Buffer Empty Interrupt Signal Enable bit

1 = Interrupt signal is enabled

0 = Interrupt signal is disabled

| PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family |

|--------------------------------------------------------------------|

| NOTES:                                                             |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

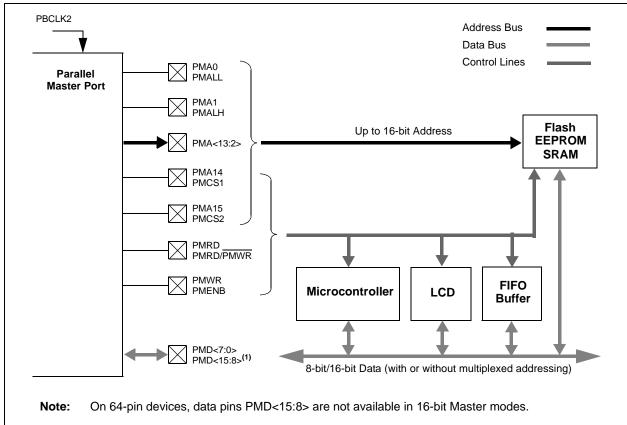

# 23.0 PARALLEL MASTER PORT (PMP)

Note:

This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable.

The following are key features of the PMP module:

- 8-bit.16-bit interface

- Up to 16 programmable address lines

- · Up to two Chip Select lines

- · Programmable strobe options:

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- · Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- · Programmable polarity on control signals

- Parallel Slave Port support:

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable Wait states

- Operate during Sleep and Idle modes

- Separate configurable read/write registers or dual buffers for Master mode

- Fast bit manipulation using CLR, SET, and INV registers

Note:

On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

#### FIGURE 23-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

#### REGISTER 26-2: CECON: CRYPTO ENGINE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | _                 | _                 | _                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |

| 7.0          | R/W-0             | R/W-0, HC         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | SWAPOEN           | SWRST             | SWAPEN            | _                 | _                 | BDPCHST           | BDPPLEN          | DMAEN            |

**Legend:** HC = Hardware Cleared

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 SWAPOEN: Swap Output Data Enable bit

1 = Output data is byte swapped when written by dedicated DMA

0 = Output data is not byte swapped when written by dedicated DMA

bit 6 SWRST: Software Reset bit

1 = Initiate a software reset of the Crypto Engine

0 = Normal operation

bit 5 **SWAPEN:** Input Data Swap Enable bit

1 = Input data is byte swapped when read by dedicated DMA

0 = Input data is not byte swapped when read by dedicated DMA

bit 4-3 Unimplemented: Read as '0'

bit 2 BDPCHST: Buffer Descriptor Processor (BDP) Fetch Enable bit

This bit should be enabled only after all DMA descriptor programming is completed.

1 = BDP descriptor fetch is enabled

0 = BDP descriptor fetch is disabled

bit 1 BDPPLEN: Buffer Descriptor Processor Poll Enable bit

This bit should be enabled only after all DMA descriptor programming is completed.

1 = Poll for descriptor until valid bit is set

0 = Do not poll

bit 0 DMAEN: DMA Enable bit

1 = Crypto Engine DMA is enabled

0 = Crypto Engine DMA is disabled

#### REGISTER 26-5: CESTAT: CRYPTO ENGINE STATUS REGISTER (CONTINUED)

bit 16 ACTIVE: Buffer Descriptor Processor Status bit

1 = BDP is active 0 = BDP is idle

bit 15-0 BDCTRL<15:0>: Descriptor Control Word Status bits

These bits contain the Control Word for the current Buffer Descriptor.

#### REGISTER 29-9: CIRXMN: CAN ACCEPTANCE FILTER MASK 'n' REGISTER ('n' = 0-3)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | SID<10:3>         |                   |                   |                   |                   |                   |                  |                  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |  |

|              |                   | SID<2:0>          |                   | _                 | MIDE              | _                 | EID<             | 17:16>           |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | EID<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-21 SID<10:0>: Standard Identifier bits

1 = Include bit, SIDx, in filter comparison

0 = Bit SIDx is 'don't care' in filter operation

bit 20 Unimplemented: Read as '0'

bit 19 MIDE: Identifier Receive Mode bit

1 = Match only message types (standard/extended address) that correspond to the EXID bit in filter

0 = Match either standard or extended address message if filters match (that is, if (Filter SID) = (Message SID) or if (FILTER SID/EID) = (Message SID/EID))

bit 18 Unimplemented: Read as '0'

bit 17-0 **EID<17:0>:** Extended Identifier bits

1 = Include bit, EIDx, in filter comparison

0 = Bit EIDx is 'don't care' in filter operation

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

| PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family |

|--------------------------------------------------------------------|

| NOTES:                                                             |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

|                                                                    |

REGISTER 34-9: CFGEBIC: EXTERNAL BUS INTERFACE CONTROL PIN CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | U-0              |

|              | EBI<br>RDYINV3    | EBI<br>RDYINV2    | EBI<br>RDYIN1     | _                 | EBI<br>RDYEN3     | EBI<br>RDYEN2     | EBI<br>RDYEN1    | 1                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

|              | _                 | _                 | _                 | _                 | _                 | _                 | EBIRDYLVL        | EBIRPEN          |

| 15:8         | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

|              | _                 | _                 | EBIWEEN           | EBIOEEN           | _                 | _                 | EBIBSEN1         | EBIBSEN0         |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

|              | EBICSEN3          | EBICSEN2          | EBICSEN1          | EBICSEN0          | _                 | _                 | EBIDEN1          | EBIDEN0          |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 EBIRDYINV3: EBIRDY3 Inversion Control bit

1 = Invert EBIRDY3 pin before use

0 = Do not invert EBIRDY3 pin before use

bit 30 EBIRDYINV2: EBIRDY2 Inversion Control bit

1 = Invert EBIRDY2 pin before use

0 = Do not invert EBIRDY2 pin before use

bit 29 EBIRDYINV1: EBIRDY1 Inversion Control bit

1 = Invert EBIRDY1 pin before use

0 = Do not invert EBIRDY1 pin before use

bit 28 Unimplemented: Read as '0'

bit 27 EBIRDYEN3: EBIRDY3 Pin Enable bit

1 = EBIRDY3 pin is enabled for use by the EBI module

0 = EBIRDY3 pin is available for general use

bit 26 EBIRDYEN2: EBIRDY2 Pin Enable bit

1 = EBIRDY2 pin is enabled for use by the EBI module

0 = EBIRDY2 pin is available for general use

bit 25 EBIRDYEN1: EBIRDY1 Pin Enable bit

1 = EBIRDY1 pin is enabled for use by the EBI module

0 = EBIRDY1 pin is available for general use

bit 24-18 Unimplemented: Read as '0'

bit 17 EBIRDYLVL: EBIRDYx Pin Sensitivity Control bit

1 = Use level detect for EBIRDYx pins

0 = Use edge detect for EBIRDYx pins

bit 16 EBIRPEN: EBIRP Pin Sensitivity Control bit

$1 = \overline{\mathsf{EBIRP}}$  pin is enabled for use by the EBI module

0 = EBIRP pin is available for general use

bit 15-14 Unimplemented: Read as '0'

bit 13 **EBIWEEN:** EBIWE Pin Enable bit

$1 = \overline{\mathsf{EBIWE}}$  pin is enabled for use by the EBI module

0 = EBIWE pin is available for general use

**Note:** When EBIMD = 1, the bits in this register are ignored and the pins are available for general use.

TABLE 37-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS |                        |                        | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |       |                                                 |  |  |

|--------------------|------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------|--|--|

| Param.<br>No.      | Typical <sup>(2)</sup> | Maximum <sup>(5)</sup> | Units Conditions                                                                                                                                                       |       |                                                 |  |  |

| Power-Dov          | wn Current (IPI        | o) (Note 1)            |                                                                                                                                                                        |       |                                                 |  |  |

| DC40k              | 0.7                    | 7                      | mA                                                                                                                                                                     | -40°C |                                                 |  |  |

| DC40I              | 1.5                    | 7                      | mA                                                                                                                                                                     | +25°C | Base Power-Down Current                         |  |  |

| DC40n              | 7                      | 20                     | mA                                                                                                                                                                     | +85°C |                                                 |  |  |

| Module Di          | fferential Curre       | ent                    |                                                                                                                                                                        |       |                                                 |  |  |

| DC41e              | 15                     | 50                     | μΑ                                                                                                                                                                     | 3.6V  | Watchdog Timer Current: ΔIWDT (Note 3)          |  |  |

| DC42e              | 25                     | 50                     | μΑ                                                                                                                                                                     | 3.6V  | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |

| DC43d              | 3                      | 3.8                    | mA                                                                                                                                                                     | 3.6V  | ADC: ΔIADC (Notes 3, 4)                         |  |  |

| DC44               | 15                     | 50                     | μΑ                                                                                                                                                                     | 3.6V  | Deadman Timer Current: ΔIDMT (Note 3)           |  |  |

**Note 1:** The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBMD = 1), VUSB3V3 is connected to VSS

- CPU is in Sleep mode

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), and the associated PMD bit is set. All clocks are disabled ON bit (PBxDIV<15>) = 0 (x ≠ 1,7)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD

- · RTCC and JTAG are disabled

- Voltage regulator is in Stand-by mode (VREGS = 0)

- 2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- **4:** Voltage regulator is operational (VREGS = 1).

- 5: Data in the "Maximum" column is at 3.3V, +85°C at specified operating frequency, unless otherwise stated. Parameters are for design guidance only and are not tested.

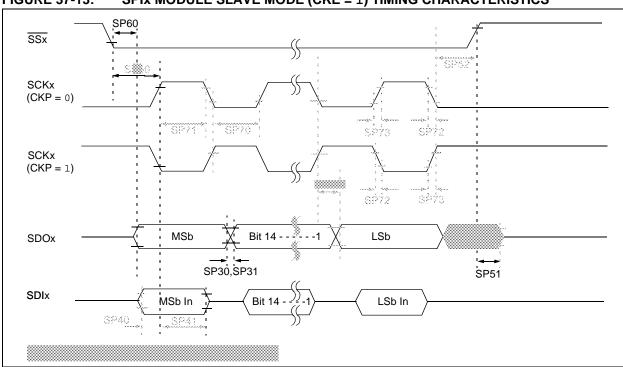

FIGURE 37-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

TABLE 37-33: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            |        | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature -40°C $\leq$ TA $\leq$ +85°C for Industrial -40°C $\leq$ TA $\leq$ +125°C for Extended |      |       |                    |  |  |

|--------------------|-----------------------|--------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>             | Min.   | Typical <sup>(2)</sup>                                                                                                                                                             | Max. | Units | Conditions         |  |  |

| SP70               | TscL                  | SCKx Input Low Time (Note 3)               | Tsck/2 | _                                                                                                                                                                                  |      | ns    | _                  |  |  |

| SP71               | TscH                  | SCKx Input High Time (Note 3)              | Tsck/2 | _                                                                                                                                                                                  | _    | ns    | _                  |  |  |

| SP72               | TscF                  | SCKx Input Fall Time                       | _      | _                                                                                                                                                                                  | 10   | ns    | _                  |  |  |

| SP73               | TscR                  | SCKx Input Rise Time                       | _      | _                                                                                                                                                                                  | 10   | ns    | _                  |  |  |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)        | _      | _                                                                                                                                                                                  | _    | ns    | See parameter DO32 |  |  |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)        | _      | _                                                                                                                                                                                  | _    | ns    | See parameter DO31 |  |  |

| SP35               | TscH2DoV,             | SDOx Data Output Valid after               | _      | _                                                                                                                                                                                  | 10   | ns    | VDD > 2.7V         |  |  |

|                    | TscL2DoV              | SCKx Edge                                  | _      | _                                                                                                                                                                                  | 15   | ns    | VDD < 2.7V         |  |  |

| SP40               | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge | 0      | _                                                                                                                                                                                  | _    | ns    | _                  |  |  |

| SP41               | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 7      | _                                                                                                                                                                                  | 1    | ns    | _                  |  |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 20 ns.

- 4: Assumes 30 pF load on all SPIx pins.

#### 39.0 252 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MZ EF electrical characteristics for devices running at 252 MHz. Additional information will be provided in future revisions of this document as it becomes available.

The specifications for 252 MHz are identical to those shown in **37.0** "Electrical Characteristics" including absolute maximum ratings, with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 252 MHz operation. For example, parameter DC27a in **37.0** "Electrical Characteristics", is the up to 200 MHz operation equivalent for MDC27a.

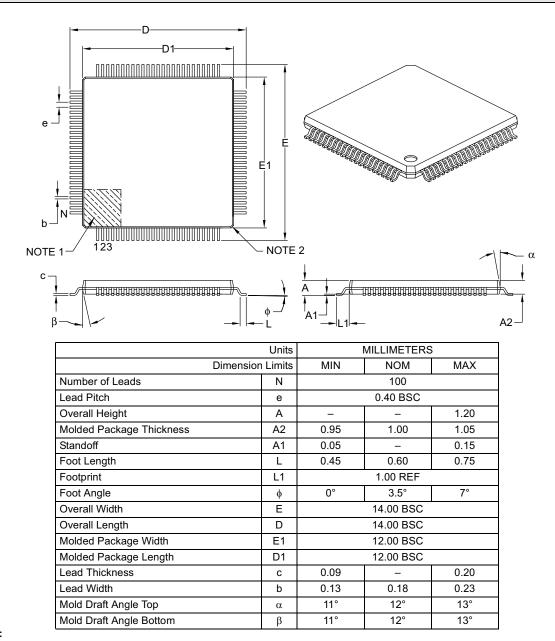

#### 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

TABLE C-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                              | Update Description                                                                                                                                                       |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27.0 "Random Number Generator (RNG)"                      | The TRNGMODE bit was added to the RNGCON register (see Register 27-2).                                                                                                   |

| 28.0 "12-bit High-Speed                                   | The S&H Block Diagram was updated (see Figure 28-2).                                                                                                                     |

| Successive Approximation Register (SAR) Analog-to-Digital | The registers, ADCTRG4 through ADCTRG8, were removed.                                                                                                                    |

| Converter (ADC)"                                          | The bit value definitions for the ADCSEL<1:0> and CONCLKDIV<5:0> bits in the ADCCON3 register were updated (see Register 28-3).                                          |

|                                                           | The bit names in the ADC Status registers (Register 28-12 and Register 28-13) were updated to match the names in the SFR summary table.                                  |

|                                                           | The ADCTRGSNS register was updated (see Register 28-26).                                                                                                                 |

|                                                           | The POR values were changed in the ADC System Configuration registers (see Register 28-34 and Register 28-35).                                                           |

| 34.0 "Special Features"                                   | The FDBGWP bit was removed from the DEVCFG0/ADEVCFG0 registers (see Register 34-3).                                                                                      |

| 37.0 "Electrical Characteristics"                         | V-Temp (-40°C $\leq$ TA $\leq$ +105°C) information was removed from all tables.                                                                                          |

|                                                           | The operating conditions voltage range was updated in the Absolute Maximum Ratings and in all tables to: 2.1V to 3.6V.                                                   |

|                                                           | Notes on Maximum value operating conditions were added to the Operating, Idle, and Power-Down Current tables (see Table 37-6, Table 37-7, and Table 37-8, respectively). |

|                                                           | The conditions for System Timing Requirement parameters OS55a and OS55b were updated (see Table 37-18).                                                                  |

|                                                           | The Internal FRC Accuracy specifications were updated (see Table 37-20).                                                                                                 |

|                                                           | The Internal LPRC Accuracy specifications were updated (see Table 37-21).                                                                                                |

|                                                           | The ADC Module Specifications were updated (see Table 37-38).                                                                                                            |

|                                                           | The Analog-to-Digital Conversion Timing Requirements were updated (see Table 37-39).                                                                                     |

| Appendix B: "Migrating from PIC32MZ EC to PIC32MZ EF"     | This appendix was added, which provides an overview of considerations for migrating from PIC32MZ EC devices to the PIC32MZ EF family of devices.                         |

| Product Identification System                             | V-Temp (-40°C $\leq$ TA $\leq$ +105°C) information was removed.                                                                                                          |