Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 46                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | ·                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efh064t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTE | ER 5-8:   | NVMBWP: FLASH BOOT (PAGE) WRITE-PROTECT REGISTER                                                                                               |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | UBWP4:    | Upper Boot Alias Page 4 Write-protect bit <sup>(1)</sup>                                                                                       |

|         |           | protection for physical address 0x01FC30000 through 0x1FC33FFF enabled protection for physical address 0x01FC30000 through 0x1FC33FFF disabled |

| bit 3   | UBWP3:    | Upper Boot Alias Page 3 Write-protect bit <sup>(1)</sup>                                                                                       |

|         | 0 = Write | protection for physical address 0x01FC2C000 through 0x1FC2FFFF enabled protection for physical address 0x01FC2C000 through 0x1FC2FFFF disabled |

| bit 2   | UBWP2:    | Upper Boot Alias Page 2 Write-protect bit <sup>(1)</sup>                                                                                       |

|         |           | protection for physical address 0x01FC28000 through 0x1FC2BFFF enabled protection for physical address 0x01FC28000 through 0x1FC2BFFF disabled |

| bit 1   | UBWP1:    | Upper Boot Alias Page 1 Write-protect bit <sup>(1)</sup>                                                                                       |

|         | 0 = Write | protection for physical address 0x01FC24000 through 0x1FC27FFF enabled protection for physical address 0x01FC24000 through 0x1FC27FFF disabled |

| bit 0   | UBWP0:    | Upper Boot Alias Page 0 Write-protect bit <sup>(1)</sup>                                                                                       |

|         |           | protection for physical address 0x01FC20000 through 0x1FC23FFF enabled protection for physical address 0x01FC20000 through 0x1FC23FFF disabled |

|         |           |                                                                                                                                                |

**Note 1:** These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (LBWPULOCK or UBWPULOCK) is set.

Note: The bits in this register are only writable when the NVMKEY unlock sequence is followed.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2          | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                        | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | _                 | —                 | _                 | _                 | —                 | —                          | —                | _                |  |  |  |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                      | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 |                   | SYSDIV<3:0> <sup>(1)</sup> |                  |                  |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                      | R/W-1            | R/W-0            |  |  |  |  |  |  |

| 15:8         | —                 | —                 | _                 | _                 | —                 | :                          | SLWDIV<2:0>      | •                |  |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-1                      | R/W-0            | R-0, HS, HC      |  |  |  |  |  |  |

| 7:0          |                   | _                 |                   |                   | _                 | UPEN                       | DNEN             | BUSY             |  |  |  |  |  |  |

#### REGISTER 8-7: SLEWCON: OSCILLATOR SLEW CONTROL REGISTER

| Legend:           | HC = Hardware Cleared | HS = Hardware Set         |                    |  |  |  |

|-------------------|-----------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, re | ad as '0'          |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

bit 31-20 Unimplemented: Read as '0'

```

bit 19-16 SYSDIV<3:0>: System Clock Divide Control bits<sup>(1)</sup>

```

- bit 15-11 Unimplemented: Read as '0'

- bit 10-8 **SLWDIV<2:0>:** Slew Divisor Steps Control bits

These bits control the maximum division steps used when slewing during a frequency change.

- 111 = Steps are divide by 128, 64, 32, 16, 8, 4, 2, and then no divisor

- 110 = Steps are divide by 64, 32, 16, 8, 4, 2, and then no divisor

- 101 = Steps are divide by 32, 16, 8, 4, 2, and then no divisor

- 100 = Steps are divide by 16, 8, 4, 2, and then no divisor

- 011 = Steps are divide by 8, 4, 2, and then no divisor

- 010 = Steps are divide by 4, 2, and then no divisor

- 001 = Steps are divide by 2, and then no divisor

- 000 = No divisor is used during slewing

Note: The steps apply in reverse order (i.e., 2, 4, 8, etc.) during a downward frequency change.

- bit 7-3 **Unimplemented:** Read as '0'

- bit 2 UPEN: Upward Slew Enable bit

- 1 = Slewing enabled for switching to a higher frequency

- 0 = Slewing disabled for switching to a higher frequency

- bit 1 **DNEN:** Downward Slew Enable bit

- 1 = Slewing enabled for switching to a lower frequency

- 0 = Slewing disabled for switching to a lower frequency

- bit 0 BUSY: Clock Switching Slewing Active Status bit

- 1 = Clock frequency is being actively slewed to the new frequency

- 0 = Clock switch has reached its final value

**Note 1:** The SYSDIV<3:0> bit settings are ignored if both UPEN and DNEN = 0, and SYSCLK will be divided by 1.

## TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| ss                          |                  |               |                     |                                                                |       |       |       |       |          |        | Bits        |          |         |      |       |         |        |       |            |

|-----------------------------|------------------|---------------|---------------------|----------------------------------------------------------------|-------|-------|-------|-------|----------|--------|-------------|----------|---------|------|-------|---------|--------|-------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15               | 30/14                                                          | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8   | 23/7        | 22/6     | 21/5    | 20/4 | 19/3  | 18/2    | 17/1   | 16/0  | All Resets |

| 3248                        | USB              | 31:16         |                     |                                                                |       |       |       |       |          | DMA    | ADDR<31:16  | >        |         |      |       |         |        |       | 0000       |

| 3248                        | DMA5A            | 15:0          |                     |                                                                |       |       |       |       |          | DM     | ADDR<15:0   | •        |         |      |       |         |        |       | 0000       |

| 324C                        | USB              | 31:16         |                     |                                                                |       |       |       |       |          | DMA    | COUNT<31:10 | i>       |         |      |       |         |        |       | 0000       |

| 0240                        | DMA5N            | 15:0          |                     |                                                                |       | -     | •     |       |          | DMA    | COUNT<15:0  | >        |         |      |       |         |        |       | 0000       |

| 3254                        | USB              | 31:16         | _                   | _                                                              | —     | —     |       | _     | —        | -      | _           | —        | —       | -    | -     | -       | _      | -     | 0000       |

|                             | DMA6C            | 15:0          | —                   | —                                                              | —     |       | -     | DMABR | STM<1:0> | DMAERR |             |          | EP<3:0> |      | DMAIE | DMAMODE | DMADIR | DMAEN |            |

| 3258                        | USB<br>DMA6A     | 31:16         |                     |                                                                |       |       |       |       |          |        | ADDR<31:16  |          |         |      |       |         |        |       | 0000       |

|                             |                  | 15:0          |                     |                                                                |       |       |       |       |          |        | ADDR<15:0   |          |         |      |       |         |        |       | 0000       |

| 325C                        | USB<br>DMA6N     | 31:16         |                     | DMACOUNT<31:16> 0000 DMACOUNT<15:0> 0000                       |       |       |       |       |          |        |             |          |         |      |       |         |        |       |            |

| $\vdash$                    |                  | 15:0          |                     |                                                                |       |       | r     |       |          |        |             |          |         |      |       |         |        |       |            |

| 3264                        | USB<br>DMA7C     | 31:16<br>15:0 | _                   |                                                                |       |       |       |       |          |        |             |          |         |      |       |         |        |       |            |

|                             |                  | 31:16         | _                   | DMABRSTM<1:0> DMAER DMAEP<3:0> DMAIE DMAMODE DMADIR DMAEN 0000 |       |       |       |       |          |        |             |          |         |      |       |         |        |       |            |

| 3268                        | USB<br>DMA7A     | 15:0          |                     | DMAADDR<31:16> 0000 DMAADDR<15:0> 0000                         |       |       |       |       |          |        |             |          |         |      |       |         |        |       |            |

|                             | USB              | 31:16         |                     | DMAADDK<5.0> 0000<br>DMACOUNT<31:16> 0000                      |       |       |       |       |          |        |             |          |         |      |       |         |        |       |            |

| 326C                        | DMA7N            | 15:0          | DMACOUNT<15:0> 0000 |                                                                |       |       |       |       |          |        |             |          |         |      |       |         |        |       |            |

|                             | USB              | 31:16         | _                   | _                                                              |       | _     | _     | _     | _        | _      | _           | _        | _       | _    | _     | _       | _      | _     | 0000       |

| 3274                        | DMA8C            | 15:0          | _                   | _                                                              | _     | _     | _     | DMABR | STM<1:0> | DMAERR |             | DMA      | EP<3:0> |      | DMAIE | DMAMODE | DMADIR | DMAEN | 0000       |

| 0070                        | USB              | 31:16         |                     |                                                                |       |       |       | 1     |          | DMA    | ADDR<31:16  | >        |         |      | 1     |         | 1      | J     | 0000       |

| 3278                        | DMA8A            | 15:0          |                     |                                                                |       |       |       |       |          | DM     | ADDR<15:0   | •        |         |      |       |         |        |       | 0000       |

| 327C                        | USB              | 31:16         |                     |                                                                |       |       |       |       |          | DMA    | COUNT<31:10 | i>       |         |      |       |         |        |       | 0000       |

| 3270                        | DMA8N            | 15:0          |                     |                                                                |       |       |       |       |          | DMA    | COUNT<15:0  | >        |         |      |       |         |        |       | 0000       |

| 3304                        | USB              | 31:16         | —                   |                                                                | —     | _     | —     | _     | —        | —      | _           | —        | _       | -    | —     | _       | _      | —     | 0000       |

| 5504                        | E1RPC            | 15:0          |                     |                                                                |       | -     |       | -     |          | RQP    | KTCNT<15:0  | >        |         | -    |       |         |        |       | 0000       |

| 3308                        | USB              | 31:16         | —                   | —                                                              | —     | —     | -     | —     | —        | —      | —           | —        | -       | -    | —     | -       | —      | —     | 0000       |

|                             | E2RPC            | 15:0          |                     |                                                                |       |       |       |       |          | RQP    | KTCNT<15:0  | >        | 1       |      |       |         |        |       | 0000       |

| 330C                        | USB              | 31:16         | _                   | _                                                              | —     |       | _     |       | —        | —      |             |          | _       | _    | _     | _       | _      | —     | 0000       |

|                             | E3RPC            | 15:0          |                     |                                                                |       |       | 1     |       |          |        | KTCNT<15:0  |          |         |      |       |         |        |       | 0000       |

| 3310                        | USB<br>E4RPC     | 31:16         | _                   | _                                                              | —     |       | -     | —     | —        | —      | —           | _        | _       | -    | _     | _       | _      |       | 0000       |

| $\vdash$                    |                  | 15:0          |                     |                                                                |       |       |       |       |          |        | KTCNT<15:0  |          |         |      |       |         |        |       | 0000       |

| 3314                        | USB<br>E5RPC     | 31:16<br>15:0 | —                   | _                                                              | —     | _     | —     | _     | —        |        |             | _        | —       | —    | _     | —       | —      | —     | 0000       |

| $\vdash$                    |                  |               |                     |                                                                |       |       |       |       |          |        | KTCNT<15:0  |          |         |      |       |         |        |       | 0000       |

| 3318                        | USB<br>E6RPC     | 31:16<br>15:0 |                     |                                                                |       |       |       |       |          |        |             |          |         |      |       |         |        |       |            |

| $\vdash$                    |                  | 31:16         | _                   | _                                                              | _     |       |       | _     |          |        |             | <u> </u> |         | _    | _     | _       |        | _     | 0000       |

| 331C                        | USB<br>E7RPC     | 15:0          | _                   | _                                                              |       |       | _     |       |          | ROP    |             |          | _       | _    |       | _       |        |       |            |

| 1                           |                  | 10.0          |                     | RQPKTCNT<15:0> 0000                                            |       |       |       |       |          |        |             |          |         |      |       |         |        |       |            |

Legend: Note x = unknownDevice mode.

Host mode.

1: 2: 3: 4: Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

#### REGISTER 11-1: USBCSR0: USB CONTROL STATUS REGISTER 0 (CONTINUED)

- bit 10 **RESUME:** Resume from Suspend control bit

- 1 = Generate Resume signaling when the device is in Suspend mode

- 0 = Stop Resume signaling

In *Device mode*, the software should clear this bit after 10 ms (a maximum of 15 ms) to end Resume signaling. In *Host mode*, the software should clear this bit after 20 ms.

- bit 9 **SUSPMODE:** Suspend Mode status bit 1 = The USB module is in Suspend mode

- 0 = The USB module is in Normal operations

This bit is read-only in Device mode. In Host mode, it can be set by software, and is cleared by hardware.

- bit 8 SUSPEN: Suspend Mode Enable bit

- 1 = Suspend mode is enabled

- 0 = Suspend mode is not enabled

- bit 7 Unimplemented: Read as '0'

- bit 6-0 **FUNC<6:0>:** Device Function Address bits

These bits are only available in *Device mode*. This field is written with the address received through a SET\_ADDRESS command, which will then be used for decoding the function address in subsequent token packets.

| REGISTER 11-9: | USBIENCSR1: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 1 |

|----------------|------------------------------------------------------------|

|                | (ENDPOINT 1-7)                                             |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R-0              | R/W-0            |  |  |  |

| 31:24        | AUTOCLR           | ISO               | DMAREQEN          | DISNYET           | DMAREQMD          | _                 | —                | INCOMPRX         |  |  |  |

|              | AUTOCLK           | AUTORQ            | DIMAREQEN         | PIDERR            | DIMAREQIVID       | DATATWEN          | DATATGGL         |                  |  |  |  |

|              | R/W-0, HC         | R/W-0, HS         | R/W-0             | R/W-0, HC         | R-0, HS           | R/W-0, HS         | R-0, HS, HC      | R/W-0, HS        |  |  |  |

| 23:16        | CLRDT             | SENTSTALL         | SENDSTALL         | FLUSH             | DATAERR           | OVERRUN           | FIFOFULL         | RXPKTRDY         |  |  |  |

|              | GLRDT             | RXSTALL           | REQPKT            | FLUSH             | DERRNAKT          | ERROR             | FIFOFULL         | KAFKIKUT         |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.6         |                   |                   | MULT<4:0>         |                   |                   | R                 | XMAXP<10:8       | < <u>&lt;</u>    |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          | RXMAXP<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           | HC = Hardware Cleared | HS = Hardware Set                  |                    |

|-------------------|-----------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31 AUTOCLR: RXPKTRDY Automatic Clear Control bit

- 1 = RXPKTRDY will be automatically cleared when a packet of RXMAXP bytes has been unloaded from the RX FIFO. When packets of less than the maximum packet size are unloaded, RXPKTRDY will have to be cleared manually. When using a DMA to unload the RX FIFO, data is read from the RX FIFO in 4-byte chunks regardless of the RXMAXP.

- 0 = No automatic clearing of RXPKTRDY

This bit should not be set for high-bandwidth Isochronous endpoints.

- bit 30 ISO: Isochronous Endpoint Control bit (Device mode)

- 1 = Enable the RX endpoint for Isochronous transfers

- 0 = Enable the RX endpoint for Bulk/Interrupt transfers

**AUTORQ:** Automatic Packet Request Control bit (*Host mode*)

- 1 = REQPKT will be automatically set when RXPKTRDY bit is cleared.

- 0 = No automatic packet request

This bit is automatically cleared when a short packet is received.

- bit 29 DMAREQEN: DMA Request Enable Control bit

- 1 = Enable DMA requests for the RX endpoint.

- 0 = Disable DMA requests for the RX endpoint.

- bit 28 **DISNYET:** Disable NYET Handshakes Control/PID Error Status bit (*Device mode*)

- 1 = In Bulk/Interrupt transactions, disables the sending of NYET handshakes. All successfully received RX packets are ACKed including at the point at which the FIFO becomes full.

- 0 = Normal operation.

In Bulk/Interrupt transactions, this bit only has any effect in Hi-Speed mode, in which mode it should be set for all Interrupt endpoints.

#### PIDERR: PID Error Status bit (Host mode)

1 = In ISO transactions, this indicates a PID error in the received packet.

0 = No error

- bit 27 DMAREQMD: DMA Request Mode Selection bit

- 1 = DMA Request Mode 1

- 0 = DMA Request Mode 0

#### I/O Ports Control Registers 12.5

| <b>TABLE 12-4:</b> | PORTA | REGISTI |

|--------------------|-------|---------|

| IADLL 12-4.        |       |         |

## FER MAP FOR 100-PIN, 124-PIN, AND 144-PIN DEVICES ONLY

| ess)                        |                                 | ۵         |               |               |       |       |            |               |              | Bits | ;            |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|-------|-------|------------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11      | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0000                        | ANSELA                          | 31:16     | —             | —             | _     | _     |            | -             | —            |      | —            | _            | —            | —            | —            |              | —            | —            | 0000          |

| 0000                        | ANGLLA                          | 15:0      | —             | —             | _     | _     | _          | ANSA10        | ANSA9        | _    | —            | —            | ANSA5        | —            | —            | _            | ANSA1        | ANSA0        | 0623          |

| 0010                        | TRISA                           | 31:16     | —             | —             | —     | _     |            | _             | —            | _    | _            | _            | _            | —            | —            | _            | _            | _            | 0000          |

| 0010                        | 11(10/1                         | 15:0      | TRISA15       | TRISA14       | —     | —     | —          | TRISA10       | TRISA9       | —    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | C6FF          |

| 0020                        | PORTA                           | 31:16     | —             | —             | —     | _     |            | _             | —            | _    | _            | _            | _            | —            | —            | _            | _            | _            | 0000          |

| 0020                        | 1 OKIA                          | 15:0      | RA15          | RA14          | —     | —     | —          | RA10          | RA9          | —    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 0030                        | LATA                            | 31:16     | —             | —             | —     | —     | —          | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0000                        | 2,000                           | 15:0      | LATA15        | LATA14        | —     | —     | _          | LATA10        | LATA9        | —    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 0040                        | ODCA                            | 31:16     | —             | —             | _     | _     | —          | _             | —            | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0010                        | 020/1                           | 15:0      | ODCA15        | ODCA14        | _     | _     | _          | ODCA10        | ODCA9        | _    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | 0000          |

| 0050                        | CNPUA                           | 31:16     | —             | —             | _     | _     | —          | _             | —            | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             | 0.1. 0.1.                       | 15:0      | CNPUA15       | CNPUA14       | _     | _     | —          | CNPUA10       | CNPUA9       | _    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | 0000          |

| 0060                        | CNPDA                           | 31:16     | —             | —             | —     | _     | —          | _             | —            | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             | 0                               |           | CNPDA15       | CNPDA14       | —     | _     | —          | CNPDA10       | CNPDA9       | _    | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       | 0000          |

| 0070                        | CNCONA                          | 31:16     | —             | —             | —     | _     | -          | _             | —            | _    | —            |              | —            | —            | —            |              | —            | —            | 0000          |

|                             |                                 | 15:0      | ON            | —             | —     | _     | EDGEDETECT | _             | —            | _    | —            |              | —            | —            | —            |              | —            | —            | 0000          |

| 0080                        | CNENA                           | 31:16     | —             | —             |       |       |            | —             | —            |      | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | CNENA15       | CNENA14       | —     | _     | _          | CNENA10       | CNENA9       |      | CNENA7       | CNENA6       | CNENA5       | CNENA4       | CNENA3       | CNENA2       | CNENA1       | CNENA0       | 0000          |

|                             |                                 | 31:16     | —             | —             | —     | _     | _          | —             | —            | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0090                        | CNSTATA                         | 15:0      | CN<br>STATA15 | CN<br>STATA14 | _     | _     | —          | CN<br>STATA10 | CN<br>STATA9 | —    | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | 0000          |

| 00A0                        | CNNEA                           | 31:16     | —             | —             | _     | -     | _          | _             | —            | _    | —            | _            | —            | _            | _            | _            | —            | —            | 0000          |

| UUAU                        | CINILA                          | 15:0      | CNNEA15       | CNNEA14       | _     | -     | _          | CNNEA10       | CNNEA9       | _    | CNNEA7       | CNNEA6       | CNNEA5       | CNNEA4       | CNNEA3       | CNNEA2       | CNNEA1       | CNNEA0       | 0000          |

| 00B0                        | CNFA                            | 31:16     | —             | —             | _     | -     | _          | _             | —            | _    | _            | _            | _            | _            | _            | _            | —            | —            | 0000          |

| 0000                        | CINIA                           | 15:0      | CNFA15        | CNFA14        | _     | -     | _          | CNFA10        | CNFA9        | _    | CNFA7        | CNFA76       | CNFA5        | CNFA4        | CNFA3        | CNFA2        | CNFA71       | CNFA0        | 0000          |

| 0000                        | SRCON0A                         | 31:16     | —             | —             | _     | _     | -          | _             | —            | _    | —            | _            | —            | _            | —            |              | —            | —            | 0000          |

| 0000                        | SICONUA                         | 15:0      | —             | —             | _     | _     | -          | _             | —            | _    | SR0A7        | SR0A6        | —            | _            | —            |              | —            | —            | 0000          |

| 0000                        | SRCON1A                         | 31:16     | —             | —             | _     |       | -          | _             | —            | _    | —            |              | —            | —            | —            |              | —            | —            | 0000          |

| 0000                        | SICONTA                         | 15:0      | —             | _             | _     | —     |            | _             | —            | _    | SR1A7        | SR0A6        | _            | _            | _            |              | _            | _            | 0000          |

x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

## TABLE 12-13: PORTF REGISTER MAP FOR 100-PIN, 124-PIN, AND 144-PIN DEVICES ONLY

| ess                         |                                 |               |       |       |               |               |                |       |      | Bit          | ts   |      |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|---------------|-------|-------|---------------|---------------|----------------|-------|------|--------------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13         | 28/12         | 27/11          | 26/10 | 25/9 | 24/8         | 23/7 | 22/6 | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0500                        | ANSELF                          | 31:16         | —     |       | —             | —             | —              |       |      |              | _    | _    | —            | _            | _            |              | —            | _            | 0000          |

|                             | _                               | 15:0          | —     | —     | ANSF13        | ANSF12        | —              | —     | —    | —            | —    | —    | _            | —            | —            | —            | —            | _            | 3000          |

| 0510                        | TRISF                           | 31:16         | _     | _     | _             |               | _              | _     | _    |              | _    | _    | _            |              |              | _            |              | _            | 0000          |

|                             |                                 | 15:0          | _     | _     | TRISF13       | TRISF12       | _              | _     | —    | TRISF8       | _    | —    | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | 313F          |

| 0520                        | PORTF                           | 31:16         | _     | _     | _             | _             | _              | _     | —    | _            | _    | —    | _            |              | _            | _            | _            | _            | 0000          |

|                             |                                 | 15:0          | _     | _     | RF13          | RF12          | _              | _     | _    | RF8          | _    | _    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | XXXX          |

| 0530                        | LATF                            | 31:16         | -     | _     |               | —             | _              | _     | _    |              | _    | _    |              |              |              |              | —            |              | 0000          |

|                             |                                 | 15:0          | _     | _     | LATF13        | LATF12        | _              | _     | _    | LATF8        | _    | _    | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | XXXX          |

| 0540                        | ODCF                            | 31:16         | _     |       | -             | -             | _              |       |      | -            |      |      | -            | -            | -            | -            | -            | -            | 0000          |

|                             |                                 | 15:0          | _     |       | ODCF13        | ODCF12        | _              |       |      | ODCF8        |      |      | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | 0000          |

| 0550                        | CNPUF                           | 31:16         | _     | _     |               |               | _              | _     | _    |              | _    |      |              |              |              |              |              |              | 0000          |

|                             |                                 | 15:0          |       | _     | CNPUF13       | CNPUF12       | _              |       | _    | CNPUF8       |      |      | CNPUF5       | CNPUF4       | CNPUF3       | CNPUF2       | CNPUF1       | CNPUF0       | 0000          |

| 0560                        | CNPDF                           | 31:16<br>15:0 | _     | _     | —<br>CNPDF13  | —<br>CNPDF12  | _              |       | _    | CNPDF8       |      |      | CNPDF5       | —<br>CNPDF4  | —<br>CNPDF3  | —<br>CNPDF2  | —<br>CNPDF1  |              | 0000          |

|                             |                                 | 31:16         | _     |       |               | CNPDF12       | _              |       |      | CNPDF8       |      |      | CNPDF5       |              | CNPDF3       |              | CNPDF1       |              | 0000          |

| 0570                        |                                 | 15:0          | ON    | _     |               | _             | EDGE<br>DETECT | _     | _    | _            |      | _    | _            |              |              |              | _            |              | 0000          |

|                             |                                 | 31:16         | _     | _     | _             | _             | _              | _     | _    | _            |      | _    | _            | _            | _            | _            |              | _            | 0000          |

| 0580                        | CNENF                           | 15:0          | _     | _     | CNENF13       | CNENF12       | _              | _     | _    | CNENF8       |      | _    | CNENF5       | CNENF4       | CNENF3       | CNENF2       | CNENF1       | CNENF0       | 0000          |

|                             |                                 | 31:16         | _     | _     | _             | _             | _              | _     | _    | _            | _    | _    | _            | _            | _            | _            | _            | _            | 0000          |

| 0590                        | CNSTATF                         | 15:0          | _     | _     | CN<br>STATF13 | CN<br>STATF12 | _              | _     | _    | CN<br>STATF8 | _    | _    | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | 0000          |

|                             |                                 | 31:16         | _     | _     |               |               | _              | _     | _    |              | _    | _    | _            | _            | _            | _            |              | _            | 0000          |

| 05A0                        | CNNEF                           | 15:0          | _     | _     | CNNEF13       | CNNEF12       | _              | _     | _    | CNNEF8       | _    | _    | CNNEF5       | CNNEF4       | CNNEF3       | CNNEF2       | CNNEF1       | CNNEF0       | 0000          |

|                             | 0.1.55                          | 31:16         | _     | _     | _             | _             | _              | _     | _    | _            | _    | _    | _            | -            | -            | _            | _            | _            | 0000          |

| 05B0                        | CNFF                            | 15:0          | _     | _     | CNFF13        | CNFF12        |                |       |      | CNFF8        |      |      | CNFF5        | CNFF4        | CNFF3        | CNFF2        | CNFF1        | CNFF0        | 0000          |

| 05.00                       | SRCON0F                         | 31:16         | —     | —     | —             | —             | _              | —     | —    | —            | —    | _    | —            |              |              | —            | —            |              | 0000          |

| 0500                        | SKUUNUF                         | 15:0          | —     |       | _             | _             | _              |       | _    |              | _    |      | _            |              |              | _            | SR0F1        | SR0F0        | 0000          |

| 05 D0                       | SRCON1F                         | 31:16         | —     |       | —             | —             | —              |       | —    |              | _    |      | —            |              |              | —            | _            |              | 0000          |

| 0500                        | SRUUNTF                         | 15:0          | —     |       | _             | —             | —              |       | —    |              | _    |      | —            |              |              | _            | SR1F1        | SR1F0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

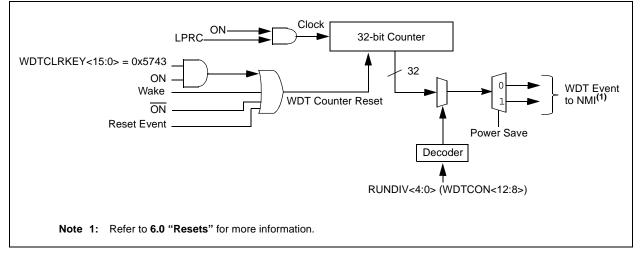

## 16.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). When enabled, the Watchdog Timer (WDT) operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

### FIGURE 16-1: WATCHDOG TIMER BLOCK DIAGRAM

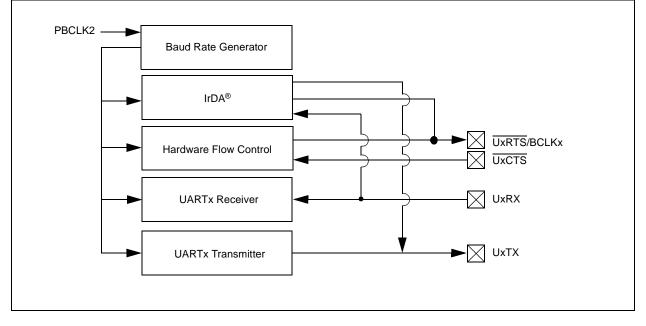

## 22.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The UART module is one of the serial I/O modules available in the PIC32MZ EF family of devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- One or two Stop bits

- Hardware auto-baud feature

- Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 76 bps to 25 Mbps at 100 MHz (PBCLK2)

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- LIN Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 22-1 illustrates a simplified block diagram of the UART module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |  |  |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | ADM_EN           |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |  |  |  |  |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |  |  |  |  |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |  |  |

#### REGISTER 22-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

#### Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

#### bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

- bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

- bit 13 UTXINV: Transmit Polarity Inversion bit

- If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

#### If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

- bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module

#### bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset

- bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only)

- 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

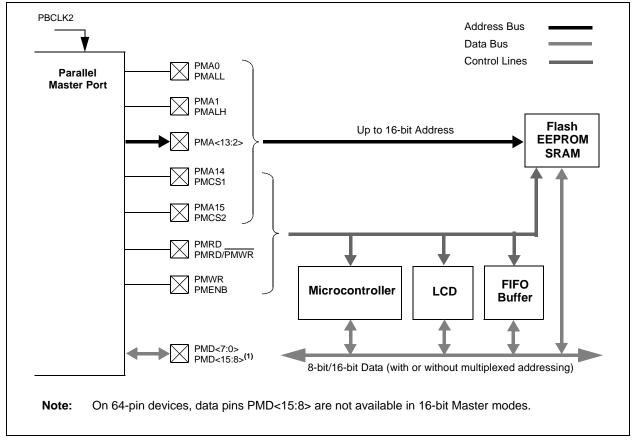

## 23.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features<br>of the PIC32MZ EF family of devices. It is<br>not intended to be a comprehensive refer-<br>ence source. To complement the informa-<br>tion in this data sheet, refer to <b>Section 13</b> . |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | "Parallel Master Port (PMP)"                                                                                                                                                                                                           |

|       | (DS60001128) in the "PIC32 Family Ref-                                                                                                                                                                                                 |

|       | erence Manual", which is available from                                                                                                                                                                                                |

|       | the Microchip web site (www.micro-<br>chip.com/PIC32).                                                                                                                                                                                 |

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. The following are key features of the PMP module:

- 8-bit,16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options:

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- Parallel Slave Port support:

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait states

- Operate during Sleep and Idle modes

- Separate configurable read/write registers or dual buffers for Master mode

- Fast bit manipulation using CLR, SET, and INV registers

Note: On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

| REGISTER | 28-2: ADCCON2: ADC CONTROL REGISTER 2 (CONTINUED)                                                                                                                                                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | REFFLTIEN: Band Gap/VREF Voltage Fault Interrupt Enable bit                                                                                                                                                                                                                            |

|          | 1 = Interrupt will be generated when the REFFLT bit is set                                                                                                                                                                                                                             |

|          | 0 = No interrupt is generated when the REFFLT bit is set                                                                                                                                                                                                                               |

| bit 13   | EOSIEN: End of Scan Interrupt Enable bit                                                                                                                                                                                                                                               |

|          | <ul> <li>1 = Interrupt will be generated when EOSRDY bit is set</li> <li>0 = No interrupt is generated when the EOSRDY bit is set</li> </ul>                                                                                                                                           |

| bit 12   | ADCEIOVR: Early Interrupt Request Override bit                                                                                                                                                                                                                                         |

|          | 1 = Early interrupt generation is not overridden and interrupt generation is controlled by the ADCEIEN1<br>and ADCEIEN2 registers                                                                                                                                                      |

|          | <ul> <li>Early interrupt generation is overridden and interrupt generation is controlled by the ADCGIRQEN1<br/>and ADCGIRQEN2 registers</li> </ul>                                                                                                                                     |

| bit 11   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                             |

| bit 10-8 | ADCEIS<2:0>: Shared ADC (ADC7) Early Interrupt Select bits                                                                                                                                                                                                                             |

|          | These bits select the number of clocks (TAD7) prior to the arrival of valid data that the associated interrupt is generated.                                                                                                                                                           |

|          | 111 = The data ready interrupt is generated 8 ADC clocks prior to end of conversion                                                                                                                                                                                                    |

|          | 110 = The data ready interrupt is generated 7 ADC clocks prior to end of conversion                                                                                                                                                                                                    |

|          | •                                                                                                                                                                                                                                                                                      |

|          | • 001 = The data ready interrupt is generated 2 ADC module clocks prior to end of conversion                                                                                                                                                                                           |

|          | 000 = The data ready interrupt is generated 1 ADC module clock prior to end of conversion                                                                                                                                                                                              |

|          | Note: All options are available when the selected resolution, set by the SELRES<1:0> bits (ADCCON1<22:21>), is 12-bit or 10-bit. For a selected resolution of 8-bit, options from '000' to '101' are valid. For a selected resolution of 6-bit, options from '000' to '011' are valid. |

| bit 7    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                             |

| bit 6-0  | ADCDIV<6:0>: Shared ADC (ADC7) Clock Divider bits                                                                                                                                                                                                                                      |

|          | 1111111 = 254 * TQ = TAD7                                                                                                                                                                                                                                                              |

|          | •                                                                                                                                                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                                                                      |

|          | 0000011 = 6 * TQ = TAD7                                                                                                                                                                                                                                                                |

|          | 0000010 = 4 * TQ = TAD7<br>0000001 = 2 * TQ = TAD7                                                                                                                                                                                                                                     |

|          | 0000000 = Reserved                                                                                                                                                                                                                                                                     |

The ADCDIV<6:0> bits divide the ADC control clock (TQ) to generate the clock for the Shared ADC, ADC7 (TAD7).

#### REGISTER 28-15: ADCCMPx: ADC DIGITAL COMPARATOR 'x' LIMIT VALUE REGISTER ('x' = 1 THROUGH 6)

| Bit Range | Bit<br>31/23/15/7               | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|---------------------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------|

| 24.24     | R/W-0                           | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 31:24     |                                 |                   |                   | DCMPHI<           | 15:8> <sup>(1,2,3)</sup> |                   |                  |                  |

| 00.40     | R/W-0                           | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 23:16     | DCMPHI<7:0> <sup>(1,2,3)</sup>  |                   |                   |                   |                          |                   |                  |                  |

| 45.0      | R/W-0                           | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | DCMPLO<15:8> <sup>(1,2,3)</sup> |                   |                   |                   |                          |                   |                  |                  |

| 7.0       | R/W-0                           | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | DCMPLO<7:0> <sup>(1,2,3)</sup>  |                   |                   |                   |                          |                   |                  |                  |

## Legend:

| Legena:           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 31-16 **DCMPHI<15:0>:** Digital Comparator 'x' High Limit Value bits<sup>(1,2,3)</sup> These bits store the high limit value, which is used by digital comparator for comparisons with ADC converted data.

- bit 15-0 **DCMPLO<15:0>:** Digital Comparator 'x' Low Limit Value bits<sup>(1,2,3)</sup> These bits store the low limit value, which is used by digital comparator for comparisons with ADC converted data.

- **Note 1:** Changing theses bits while the Digital Comparator is enabled (ENDCMP = 1) can result in unpredictable behavior.

- **2:** The format of the limit values should match the format of the ADC converted value in terms of sign and fractional settings.

- **3:** For Digital Comparator 0 used in CVD mode, the DCMPHI<15:0> and DCMPLO<15:0> bits must always be specified in signed format, as the CVD output data is differential and is always signed.

#### REGISTER 29-1: CICON: CAN MODULE CONTROL REGISTER (CONTINUED)

- bit 13 SIDLE: CAN Stop in Idle bit 1 = CAN Stops operation when system enters Idle mode 0 = CAN continues operation when system enters Idle mode bit 12 Unimplemented: Read as '0' bit 11 CANBUSY: CAN Module is Busy bit 1 = The CAN module is active

- 0 = The CAN module is completely disabled

- bit 10-5 Unimplemented: Read as '0'

## bit 4-0 **DNCNT<4:0>:** Device Net Filter Bit Number bits

10011-11111 = Invalid Selection (compare up to 18-bits of data with EID)

- 10010 = Compare up to data byte 2 bit 6 with EID17 (CiRXFn<17>)

- •

- •

- •

00001 = Compare up to data byte 0 bit 7 with EID0 (CiRXFn<0>) 00000 = Do not compare data bytes

**Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

#### **REGISTER 30-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1 (CONTINUED)**

- bit 7 **AUTOFC:** Automatic Flow Control bit

- 1 = Automatic Flow Control enabled

- 0 = Automatic Flow Control disabled

Setting this bit will enable automatic Flow Control. If set, the full and empty watermarks are used to automatically enable and disable the Flow Control, respectively. When the number of received buffers BUFCNT (ETHSTAT<16:23>) rises to the full watermark, Flow Control is automatically enabled. When the BUFCNT falls to the empty watermark, Flow Control is automatically disabled.

This bit is only used for Flow Control operations and affects both TX and RX operations.

#### bit 6-5 Unimplemented: Read as '0'

#### bit 4 MANFC: Manual Flow Control bit

- 1 = Manual Flow Control is enabled

- 0 = Manual Flow Control is disabled

Setting this bit will enable manual Flow Control. If set, the Flow Control logic will send a PAUSE frame using the PAUSE timer value in the PTV register. It will then resend a PAUSE frame every 128 \* PTV<15:0>/2 TX clock cycles until the bit is cleared.

**Note:** For 10 Mbps operation, TX clock runs at 2.5 MHz. For 100 Mbps operation, TX clock runs at 25 MHz.

When this bit is cleared, the Flow Control logic will automatically send a PAUSE frame with a 0x0000 PAUSE timer value to disable Flow Control.

This bit is only used for Flow Control operations and affects both TX and RX operations.

#### bit 3-1 Unimplemented: Read as '0'

bit 0 BUFCDEC: Descriptor Buffer Count Decrement bit

The BUFCDEC bit is a write-1 bit that reads as '0'. When written with a '1', the Descriptor Buffer Counter, BUFCNT, will decrement by one. If BUFCNT is incremented by the RX logic at the same time that this bit is written, the BUFCNT value will remain unchanged. Writing a '0' will have no effect.

This bit is only used for RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

| REGISTI   | ER 34-9: CFGEBIC: EXTERNAL BUS INTERFACE CONTROL PIN CONFIGURATION<br>REGISTER (CONTINUED)                                                          |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 12    | EBIOEEN: EBIOE Pin Enable bit                                                                                                                       |  |

|           | $1 = \overline{\text{EBIOE}}$ pin is enabled for use by the EBI module                                                                              |  |

|           | 0 = EBIOE pin is available for general use                                                                                                          |  |

| bit 11-10 | Unimplemented: Read as '0'                                                                                                                          |  |

| bit 9     | EBIBSEN1: EBIBS1 Pin Enable bit                                                                                                                     |  |

|           | 1 = EBIBS1 pin is enabled for use by the EBI module<br>0 = EBIBS1 pin is available for general use                                                  |  |

| bit 8     | EBIBSEN1: EBIBSO Pin Enable bit                                                                                                                     |  |

| bit 0     | $1 = \overline{\text{EBIBS0}}$ pin is enabled for use by the EBI module                                                                             |  |

|           | 0 = EBIBS0 pin is available for general use                                                                                                         |  |

| bit 7     | EBICSEN3: EBICS3 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{EBICS3}$ pin is enabled for use by the EBI module                                                                                    |  |

|           | 0 = EBICS3 pin is available for general use                                                                                                         |  |

| bit 6     | EBICSEN2: EBICS2 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{\text{EBICS2}}$ pin is enabled for use by the EBI module                                                                             |  |

|           | 0 = EBICS2 pin is available for general use                                                                                                         |  |

| bit 5     | EBICSEN1: EBICS1 Pin Enable bit                                                                                                                     |  |

|           | 1 = EBICS1 pin is enabled for use by the EBI module                                                                                                 |  |

|           | 0 = EBICS1 pin is available for general use                                                                                                         |  |

| bit 4     | EBICSEN0: EBICS0 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{\text{EBICS0}}$ pin is enabled for use by the EBI module                                                                             |  |

| 1         | 0 = EBICS0 pin is available for general use                                                                                                         |  |

| bit 3-2   | Unimplemented: Read as '0'                                                                                                                          |  |

| bit 1     | EBIDEN1: EBI Data Upper Byte Pin Enable bit                                                                                                         |  |

|           | <ul> <li>1 = EBID&lt;15:8&gt; pins are enabled for use by the EBI module</li> <li>0 = EBID&lt;15:8&gt; pins have reverted to general use</li> </ul> |  |

| bit 0     | <b>EBIDEN0:</b> EBI Data Lower Byte Pin Enable bit                                                                                                  |  |

| DIL U     | 1 = EBID<7:0> pins are enabled for use by the EBI module                                                                                            |  |

|           | 0 = EBID < 7:0> pins have reverted to general use                                                                                                   |  |

|           | -                                                                                                                                                   |  |

| Note:     | When EBIMD = 1, the bits in this register are ignored and the pins are available for general use.                                                   |  |

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |                                                   |                       |    |                                                                                                                                                                                                      |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------|-----------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|