Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efh100-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.4 EJTAG Debug Support

The processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the processor core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification specify which registers are selected and how they are used.

# 3.5 MIPS DSP ASE Extension

The MIPS DSP Application-Specific Extension Revision 2 is an extension to the MIPS32 architecture. This extension comprises new integer instructions and states that include new HI/LO accumulator register pairs and a DSP control register. This extension is crucial in a wide range of DSP, multimedia, and DSPlike algorithms covering Audio and Video processing applications. The extension supports native fractional format data type operations, register Single Instruction Multiple Data (SIMD) operations, such as add, subtract, multiply, and shift. In addition, the extension includes the following features that are essential in making DSP algorithms computationally efficient:

- · Support for multiplication of complex operands

- · Variable bit insertion and extraction

- Implementation and use of virtual circular buffers

- Arithmetic saturation and overflow handling support

- Zero cycle overhead saturation and rounding operations

### 3.6 microMIPS ISA

The processor core supports the microMIPS ISA, which contains all MIPS32 ISA instructions (except for branch-likely instructions) in a new 32-bit encoding scheme, with some of the commonly used instructions also available in 16-bit encoded format. This ISA improves code density through the additional 16-bit instructions while maintaining a performance similar to MIPS32 mode. In microMIPS mode, 16-bit or 32-bit instructions will be fetched and recoded to legacy MIPS32 instruction opcodes in the pipeline's I stage, so that the processor core can have the same microAptiv UP microarchitecture. Because the microMIPS instruction stream can be intermixed with 16-bit halfword or 32-bit word size instructions on halfword or word boundaries, additional logic is in place to address the misalignment word issues, thus minimizing performance loss.

# TABLE 4-4: INITIATORS TO TARGETS ACCESS ASSOCIATION

| Torgot      | Initiator ID                                                                                                          | 1 | 2   | 3   | 4      | 5   | 6     | 7   | 8                | 9                 | 10   | 11   | 12   | 13                  | 14     |

|-------------|-----------------------------------------------------------------------------------------------------------------------|---|-----|-----|--------|-----|-------|-----|------------------|-------------------|------|------|------|---------------------|--------|

| Target<br># | Name                                                                                                                  | C | CPU | DMA | A Read | DMA | Write | USB | Ethernet<br>Read | Ethernet<br>Write | CAN1 | CAN2 | SQI1 | Flash<br>Controller | Crypto |

| 1           | Flash Memory:<br>Program Flash<br>Boot Flash<br>Prefetch Module                                                       |   | x   |     | x      |     |       | x   | x                |                   | х    | х    |      |                     | х      |

| 2           | RAM Bank 1 Memory                                                                                                     |   | Х   |     | Х      |     | Х     | Х   | Х                | Х                 | Х    | Х    | Х    | Х                   | Х      |

| 3           | RAM Bank 2 Memory                                                                                                     |   | Х   |     | Х      | 2   | Х     | Х   | Х                | Х                 | Х    | Х    | Х    | Х                   | Х      |

| 4           | External Memory via EBI and EBI Module                                                                                |   | Х   |     | Х      | 2   | Х     | Х   | Х                | Х                 | Х    | Х    | Х    |                     | Х      |

| 5           | Peripheral Set 1:<br>System Control, Flash Control, DMT,<br>RTCC, CVR, PPS Input, PPS Output,<br>Interrupts, DMA, WDT |   | x   |     |        |     |       |     |                  |                   |      |      |      |                     |        |

| 6           | Peripheral Set 2:<br>SPI1-SPI6<br>I2C1-I2C5<br>UART1-UART6<br>PMP                                                     |   | х   |     | x      | :   | x     |     |                  |                   |      |      |      |                     |        |

| 7           | Peripheral Set 3:<br>Timer1-Timer9<br>IC1-IC9<br>OC1-OC9<br>ADC<br>Comparator 1<br>Comparator 2                       |   | x   |     | x      | :   | x     |     |                  |                   |      |      |      |                     |        |

| 8           | Peripheral Set 4:<br>PORTA-PORTK                                                                                      |   | Х   |     | Х      | 2   | х     |     |                  |                   |      |      |      |                     |        |

| 9           | Peripheral Set 5:<br>CAN1<br>CAN2<br>Ethernet Controller                                                              |   | x   |     |        |     |       |     |                  |                   |      |      |      |                     |        |

| 10          | Peripheral Set 6:<br>USB                                                                                              |   | Х   |     |        |     |       |     |                  |                   |      |      |      |                     |        |

| 11          | External Memory via SQI1 and SQI1 Module                                                                              |   | Х   |     |        |     |       |     |                  |                   |      |      |      |                     |        |

| 12          | Peripheral Set 7:<br>Crypto Engine                                                                                    |   | х   |     |        |     |       |     |                  |                   |      |      |      |                     |        |

| 13          | Peripheral Set 8:<br>RNG Module                                                                                       |   | х   |     |        |     |       |     |                  |                   |      |      |      |                     |        |

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MZ EF devices contain an internal Flash program memory for executing user code, which includes the following features:

- Two Flash banks for live update support

- Dual boot support

- Write protection for program and boot Flash

- ECC support

There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 52. "Flash Program Memory with Support for Live Update"** (DS60001193) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which is available for download from the Microchip web site (www.microchip.com).

Note: In PIC32MZ EF devices, the Flash page size is 16 KB (4K IW) and the row size is 2 KB (512 IW).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 | -                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | _                 | -                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 |                   | _                 | EDGEDETECT        | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   |                  |                  |

# REGISTER 12-3: CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A - K)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Change Notice (CN) Control ON bit

1 = CN is enabled

0 = CN is disabled

### bit 14-12 Unimplemented: Read as '0'

- bit 11 EDGEDETECT: Change Notification Style bit

- 1 = Edge Style. Detect edge transitions (CNFx used for CN Event).

- 0 = Mismatch Style. Detect change from last PORTx read (CNSTATx used for CN Event).

- bit 10-0 Unimplemented: Read as '0'

| REGIOTER  |                   | •••••             |                   |                   |                   |                   |                  |                  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 21.24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24     |                   | COUNTER<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16     |                   |                   |                   | COUNTER           | <23:16>           |                   |                  |                  |  |  |  |

| 45-0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8      |                   | COUNTER<15:8>     |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

|           |                   |                   |                   | COUNTE            | R<7:0>            |                   |                  |                  |  |  |  |

### REGISTER 15-5: DMTCNT: DEADMAN TIMER COUNT REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-8 COUNTER<31:0>: Read current contents of DMT counter

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1        | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|------------------|--|--|

| 31:24     | R-0                     | R-0              |  |  |

| 31.24     |                   |                   |                   | PSCNT<            | 31:24>            |                   |                         |                  |  |  |

| 02:16     | R-0                     | R-0              |  |  |

| 23:16     |                   |                   |                   | PSCNT<            | 23:16>            |                   | <b>25/17/9/1</b><br>R-0 |                  |  |  |

| 15:8      | R-0                     | R-0              |  |  |

| 15.6      |                   | PSCNT<15:8>       |                   |                   |                   |                   |                         |                  |  |  |

| 7.0       | R-0               | R-0               | R-0               | R-y               | R-y               | R-y               | R-y                     | R-y              |  |  |

| 7:0       |                   |                   |                   | PSCNT             | <7:0>             |                   |                         |                  |  |  |

#### **REGISTER 15-6: DMTPSCNT: POST STATUS CONFIGURE DMT COUNT STATUS REGISTER**

| Legend:           |                  | y = Value set from Configuration bits on POR |                    |  |  |

|-------------------|------------------|----------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b                          | pit, read as '0'   |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                         | x = Bit is unknown |  |  |

bit 31-8 **PSCNT<31:0>:** DMT Instruction Count Value Configuration Status bits

This is always the value of the DMTCNT<4:0> bits in the DEVCFG1 Configuration register.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|------------------------|------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                      | —                      | —                 | _                 | —                 | -                 |                  | —                |  |  |  |

| 23:16        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                      | —                      | —                 | _                 | —                 | —                 | _                | —                |  |  |  |

|              | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | RCS2 <sup>(1)</sup>    | RCS1 <sup>(3)</sup>    |                   |                   |                   |                   |                  |                  |  |  |  |

|              | RADDR15 <sup>(2)</sup> | RADDR14 <sup>(4)</sup> |                   | RADDR<13:8>       |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              | RADDR<7:0>             |                        |                   |                   |                   |                   |                  |                  |  |  |  |

# REGISTER 23-9: PMRADDR: PARALLEL PORT READ ADDRESS REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

# bit 31-16 **Unimplemented:** Read as '0'

| RCS2: Chip Select 2 bit <sup>(1)</sup>                                                                             |

|--------------------------------------------------------------------------------------------------------------------|

| 1 = Chip Select 2 is active                                                                                        |

| 0 = Chip Select 2 is inactive (RADDR15 function is selected)                                                       |

| RADDR<15>: Target Address bit 15 <sup>(2)</sup>                                                                    |

| RCS1: Chip Select 1 bit <sup>(3)</sup>                                                                             |

| <ul><li>1 = Chip Select 1 is active</li><li>0 = Chip Select 1 is inactive (RADDR14 function is selected)</li></ul> |

|                                                                                                                    |

- bit 14 RADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 RADDR<13:0>: Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

| Bit<br>Range                                                             | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04                                                                    | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24                                                                    |                   | HR10              | <3:0>             |                   |                   | HR01              | <3:0>            |                  |

| 23:16                                                                    | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

|                                                                          |                   | MIN10             | <3:0>             |                   | MIN01<3:0>        |                   |                  |                  |

|                                                                          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8                                                                     |                   | SEC10             | <3:0>             |                   | SEC01<3:0>        |                   |                  |                  |

| 7.0                                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0                                                                      | —                 | —                 | —                 | —                 | —                 | -                 | —                | —                |

|                                                                          |                   |                   |                   |                   |                   |                   |                  |                  |

| Legend:                                                                  |                   |                   |                   |                   |                   |                   |                  |                  |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |                   |                   |                   |                   |                   |                   |                  |                  |

'0' = Bit is cleared

x = Bit is unknown

# REGISTER 25-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10 digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1 digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

'1' = Bit is set

-n = Value at POR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | —                 | —                 | -                 | _                | —                |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   |                   | —                 |                   |                  | -                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   | _                 | _                 |                   | AREIF             | PKTIF             | CBDIF            | PENDIF           |

## REGISTER 26-6: CEINTSRC: CRYPTO ENGINE INTERRUPT SOURCE REGISTER

### Legend:

| 5                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

- bit 3 AREIF: Access Response Error Interrupt bit

- 1 = Error occurred trying to access memory outside the Crypto Engine

- 0 = No error has occurred

- bit 2 **PKTIF:** DMA Packet Completion Interrupt Status bit

- 1 = DMA packet was completed

- 0 = DMA packet was not completed

#### bit 1 CBDIF: BD Transmit Status bit

- 1 = Last BD transmit was processed

- 0 = Last BD transmit has not been processed

- bit 0 PENDIF: Crypto Engine Interrupt Pending Status bit

- 1 = Crypto Engine interrupt is pending (this value is the result of an OR of all interrupts in the Crypto Engine)

- 0 = Crypto Engine interrupt is not pending

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | —                 | —                 | _                 | —                 | —                 | _                 | —                | —                |  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | —                | —                |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | BDPPLCON<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BDPPLCC           | BDPPLCON<7:0>     |                   |                  |                  |  |  |  |  |  |  |

### REGISTER 26-8: CEPOLLCON: CRYPTO ENGINE POLL CONTROL REGISTER

| Legend:           |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15 **BDPPLCON<15:0>:** Buffer Descriptor Processor Poll Control bits

These bits determine the number of SYSCLK cycles that the Crypto DMA would wait before refetching the descriptor control word if the Buffer Descriptor fetched was disabled.

## FIGURE 26-7: FORMAT OF BD\_UPDPTR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31-24        |                   | BD_UPDADDR<31:24> |                   |                   |                   |                   |                  |                  |  |  |

| 23-16        |                   | BD_UPDADDR<23:16> |                   |                   |                   |                   |                  |                  |  |  |

| 15-8         |                   | BD_UPDADDR<15:8>  |                   |                   |                   |                   |                  |                  |  |  |

| 7-0          |                   |                   |                   | BD_UPDA           | DDR<7:0>          |                   |                  |                  |  |  |

bit 31-0 BD\_UPDADDR: UPD Address Location

The update address has the location where the CRDMA results are posted. The updated results are the ICV values, key output values as needed.

## FIGURE 26-8: FORMAT OF BD\_MSG\_LEN

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31-24        |                   | MSG_LENGTH<31:24> |                   |                   |                   |                   |                  |                  |  |

| 23-16        |                   | MSG_LENGTH<23:16> |                   |                   |                   |                   |                  |                  |  |

| 15-8         |                   | MSG_LENGTH<15:8>  |                   |                   |                   |                   |                  |                  |  |

| 7-0          |                   |                   |                   | MSG_LEN           | GTH<7:0>          |                   |                  |                  |  |

bit 31-0 MSG\_LENGTH: Total Message Length

Total message length for the hash and HMAC algorithms in bytes. Total number of crypto bytes in case of GCM algorithm (LEN-C).

# FIGURE 26-9: FORMAT OF BD\_ENC\_OFF

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31-24        |                   | ENCR_OFFSET<31:24> |                   |                   |                   |                   |                  |                  |  |  |

| 23-16        |                   | ENCR_OFFSET<23:16> |                   |                   |                   |                   |                  |                  |  |  |

| 15-8         |                   | ENCR_OFFSET<15:8>  |                   |                   |                   |                   |                  |                  |  |  |

| 7-0          |                   |                    |                   | ENCR_OFF          | SET<7:0>          |                   |                  |                  |  |  |

#### bit 31-0 ENCR\_OFFSET: Encryption Offset

Encryption offset for the multi-task test cases (both encryption and authentication). The number of AAD bytes in the case of GCM algorithm (LEN-A).

### REGISTER 28-3: ADCCON3: ADC CONTROL REGISTER 3 (CONTINUED)

```

bit 6 GSWTRG: Global Software Trigger bit

```

- 1 = Trigger conversion for ADC inputs that have selected the GSWTRG bit as the trigger signal, either through the associated TRGSRC<4:0> bits in the ADCTRGx registers or through the STRGSRC<4:0> bits in the ADCCON1 register

- 0 = Do not trigger an analog-to-digital conversion

- Note: This bit is automatically cleared in the next ADC clock cycle.

### bit 5-0 ADINSEL<5:0>: Analog Input Select bits

These bits select the analog input to be converted when the RQCNVRT bit is set. As a general rule:

```

111111 = Reserved

.

101101 = Reserved

101100 = MAX_AN_INPUT + 2 = IVTEMP

101011 = MAX_AN_INPUT + 1 = IVREF

101010 = MAX_AN_INPUT = AN[MAX_AN_INPUT]

.

.

000001 = AN1

000000 = AN0

```

- **Note 1:** The SAMP bit has the highest priority and setting this bit will keep the S&H circuit in Sample mode until the bit is cleared. Also, usage of the SAMP bit will cause settings of SAMC<9:0> bits (ADCCON2<25:16>) to be ignored.

- 2: The SAMP bit only connects Class 2 and Class 3 analog inputs to the shared ADC, ADC7. All Class 1 analog inputs are not affected by the SAMP bit.

- **3:** The SAMP bit is not a self-clearing bit and it is the responsibility of application software to first clear this bit and only after setting the RQCNVRT bit to start the analog-to-digital conversion.

- 4: Normally, when the SAMP and RQCNVRT bits are used by software routines, all TRGSRCx<4:0> bits and STRGSRC<4:0> bits should be set to '00000' to disable all external hardware triggers and prevent them from interfering with the software-controlled sampling command signal SAMP and with the software-controlled trigger RQCNVRT.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R-0, HS, HC      |  |

| 31:24        | AFEN              | DATA16EN          | DFMODE            | OVRSAM<2:0>       |                   |                   | AFGIEN           | AFRDY            |  |

| 22.16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | _                 | _                 | —                 | CHNLID<4:0>       |                   |                   |                  |                  |  |

| 45.0         | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |

| 15:8         | FLTRDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |

| 7:0          |                   |                   |                   | FLTRDAT           | A<7:0>            |                   |                  |                  |  |

### **REGISTER 28-16:** ADCFLTRx: ADC DIGITAL FILTER 'x' REGISTER ('x' = 1 THROUGH 6)

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                   |

|-------------------|-------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared x = Bit is unknown |

#### bit 31 **AFEN:** Digital Filter 'x' Enable bit

- 1 = Digital filter is enabled

- 0 = Digital filter is disabled and the AFRDY status bit is cleared

- bit 30 DATA16EN: Filter Significant Data Length bit

- 1 = AII 16 bits of the filter output data are significant

- 0 =Only the first 12 bits are significant, followed by four zeros

- **Note:** This bit is significant only if DFMODE = 1 (Averaging Mode) and FRACT (ADCCON1<23>) = 1 (Fractional Output Mode).

#### bit **DFMODE:** ADC Filter Mode bit

- 1 = Filter 'x' works in Averaging mode

- 0 = Filter 'x' works in Oversampling Filter mode (default)

#### bit 28-26 **OVRSAM<2:0>:** Oversampling Filter Ratio bits

If DFMODE is '0':

- 111 = 128 samples (shift sum 3 bits to right, output data is in 15.1 format)

- 110 = 32 samples (shift sum 2 bits to right, output data is in 14.1 format)

- 101 = 8 samples (shift sum 1 bit to right, output data is in 13.1 format)

- 100 = 2 samples (shift sum 0 bits to right, output data is in 12.1 format)

- 011 = 256 samples (shift sum 4 bits to right, output data is 16 bits)

- 010 = 64 samples (shift sum 3 bits to right, output data is 15 bits)

- 001 = 16 samples (shift sum 2 bits to right, output data is 14 bits)

- 000 = 4 samples (shift sum 1 bit to right, output data is 13 bits)

If DFMODE is '1':

- 111 = 256 samples (256 samples to be averaged)

- 110 = 128 samples (128 samples to be averaged)

- 101 = 64 samples (64 samples to be averaged)

- 100 = 32 samples (32 samples to be averaged)

- 011 = 16 samples (16 samples to be averaged)

- 010 = 8 samples (8 samples to be averaged)

- 001 = 4 samples (4 samples to be averaged)

- 000 = 2 samples (2 samples to be averaged)

- bit 25 **AFGIEN:** Digital Filter 'x' Interrupt Enable bit

- 1 = Digital filter interrupt is enabled and is generated by the AFRDY status bit

- 0 = Digital filter is disabled

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6           | Bit<br>29/21/13/5            | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-----------------------------|------------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0                         | U-0                          | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 | —                           | _                            | _                 | —                 | _                 | _                | —                |  |  |  |  |

| 23:16        | U-0               | U-0                         | U-0                          | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        |                   | —                           |                              |                   |                   | _                 |                  | _                |  |  |  |  |

| 15:8         | R/W-0             | R/W-0                       | R/W-0                        | R/W-0             | R/W-0             | R/W-1             | R/W-0            | R/W-1            |  |  |  |  |

| 15.0         |                   |                             | MACMAXF<15:8> <sup>(1)</sup> |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-1             | R/W-1                       | R/W-1                        | R/W-0             | R/W-1             | R/W-1             | R/W-1            | R/W-0            |  |  |  |  |

| 7.0          |                   | MACMAXF<7:0> <sup>(1)</sup> |                              |                   |                   |                   |                  |                  |  |  |  |  |

### REGISTER 30-28: EMAC1MAXF: ETHERNET CONTROLLER MAC MAXIMUM FRAME LENGTH REGISTER

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

### bit 31-16 **Unimplemented:** Read as '0'

bit 15-0 MACMAXF<15:0>: Maximum Frame Length bits<sup>(1)</sup> These bits reset to 0x05EE, which represents a maximum receive frame o

These bits reset to 0x05EE, which represents a maximum receive frame of 1518 octets. An untagged maximum size Ethernet frame is 1518 octets. A tagged frame adds four octets for a total of 1522 octets. If a shorter/longer maximum length restriction is desired, program this 16-bit field.

**Note 1:** If a proprietary header is allowed, this bit should be adjusted accordingly. For example, if 4-byte headers are prepended to frames, MACMAXF could be set to 1527 octets. This would allow the maximum VLAN tagged frame plus the 4-byte header.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| RE | REGISTER 30-31: EMAC1MCFG: ETHERNET CONTROLLER MAC MII MANAGEMENT |     |     |             |     |     |             |     |  |  |  |  |

|----|-------------------------------------------------------------------|-----|-----|-------------|-----|-----|-------------|-----|--|--|--|--|

|    | CONFIGURATION REGISTER                                            |     |     |             |     |     |             |     |  |  |  |  |

|    | Dit                                                               | 5.4 | D'/ | <b>D</b> .' | D'/ | D'1 | <b>D</b> '' | D.1 |  |  |  |  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5          | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                        | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | —                 | _                          | _                 | _                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0                        | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | —                 | _                          | _                 | _                 | _                 | —                | —                |

| 15:8         | R/W-0             | U-0               | U-0                        | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | RESETMGMT         | —                 | _                          | _                 | _                 | _                 | —                | —                |

| 7:0          | U-0               | U-0               | R/W-1                      | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | _                 | CLKSEL<3:0> <sup>(1)</sup> |                   |                   | NOPRE             | SCANINC          |                  |

### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **RESETMGMT:** Test Reset MII Management bit 1 = Reset the MII Management module 0 = Normal Operation

- bit 14-6 Unimplemented: Read as '0'

#### bit 1 NOPRE: Suppress Preamble bit

- 1 = The MII Management will perform read/write cycles without the 32-bit preamble field. Some PHYs support suppressed preamble

- 0 = Normal read/write cycles are performed

#### bit 0 SCANINC: Scan Increment bit

- 1 = The MII Management module will perform read cycles across a range of PHYs. The read cycles will start from address 1 through the value set in EMAC1MADR<PHYADDR>

- 0 = Continuous reads of the same PHY

- **Note 1:** Table 30-7 provides a description of the clock divider encoding.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

### TABLE 30-7: MIIM CLOCK SELECTION

| MIIM Clock Select     | EMAC1MCFG<5:2>        |  |  |  |

|-----------------------|-----------------------|--|--|--|

| TPBCLK5 divided by 4  | 000x                  |  |  |  |

| TPBCLK5 divided by 6  | 0010                  |  |  |  |

| TPBCLK5 divided by 8  | 0011                  |  |  |  |

| TPBCLK5 divided by 10 | 0100                  |  |  |  |

| TPBCLK5 divided by 14 | 0101                  |  |  |  |

| TPBCLK5 divided by 20 | 0110                  |  |  |  |

| TPBCLK5 divided by 28 | 0111                  |  |  |  |

| TPBCLK5 divided by 40 | 1000                  |  |  |  |

| TPBCLK5 divided by 48 | 1001                  |  |  |  |

| TPBCLK5 divided by 50 | 1010                  |  |  |  |

| Undefined             | Any other combination |  |  |  |

bit 5-2 **CLKSEL<3:0>:** MII Management Clock Select 1 bits<sup>(1)</sup> These bits are used by the clock divide logic in creating the MII Management Clock (MDC), which the IEEE 802.3 Specification defines to be no faster than 2.5 MHz. Some PHYs support clock rates up to 12.5 MHz.

NOTES:

| DC CHARACTERISTICS |        | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                                                 |   |                       |    |                                                                                                                                                                                                      |

|--------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---|-----------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                                                                                                                                                                                                                                            | Min. Typical <sup>(1)</sup> Max. Units Conditio |   | Conditions            |    |                                                                                                                                                                                                      |

| DI60a              | licl   | Input Low Injection<br>Current                                                                                                                                                                                                                                             | 0                                               | _ | <sub>-5</sub> (2,5)   | mA | This parameter applies<br>to all pins, with the<br>exception of RB10.<br>Maximum IICH current<br>for this exception is<br>0 mA.                                                                      |

| DI60b              | lich   | Input High Injection<br>Current                                                                                                                                                                                                                                            | 0                                               | _ | +5 <sup>(3,4,5)</sup> | mA | This parameter applies<br>to all pins, with the<br>exception of all 5V toler-<br>ant pins, OSCI, OSCO,<br>SOSCI, SOSCO, D+, D-<br>and RB10. Maximum<br>IICH current for these<br>exceptions is 0 mA. |

| DI60c              | ∑lict  | Total Input Injection<br>Current (sum of all I/O<br>and control pins)                                                                                                                                                                                                      | -20 <sup>(6)</sup>                              | — | +20(6)                | mA | Absolute instantaneous<br>sum of all $\pm$ input<br>injection currents from<br>all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT                                                                |

### TABLE 37-10: DC CHARACTERISTICS: I/O PIN INPUT INJECTION CURRENT SPECIFICATIONS

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: VIL source < (Vss - 0.3). Characterized but not tested.

**3:** VIH source > (VDD + 0.3) for non-5V tolerant pins only.

4: Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS - 0.3)).</li>

6: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 2, IICL = (((Vss - 0.3) - VIL source) / Rs). If Note 3, IICH = ((IICH source - (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss - 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

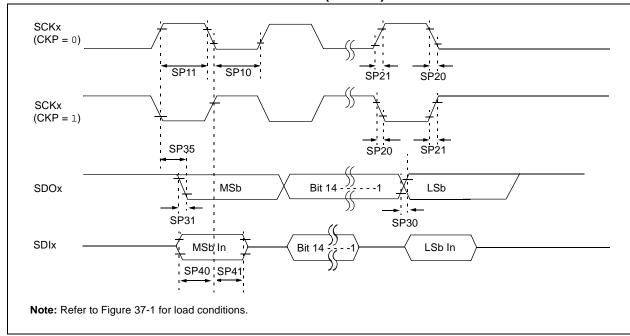

## FIGURE 37-10: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

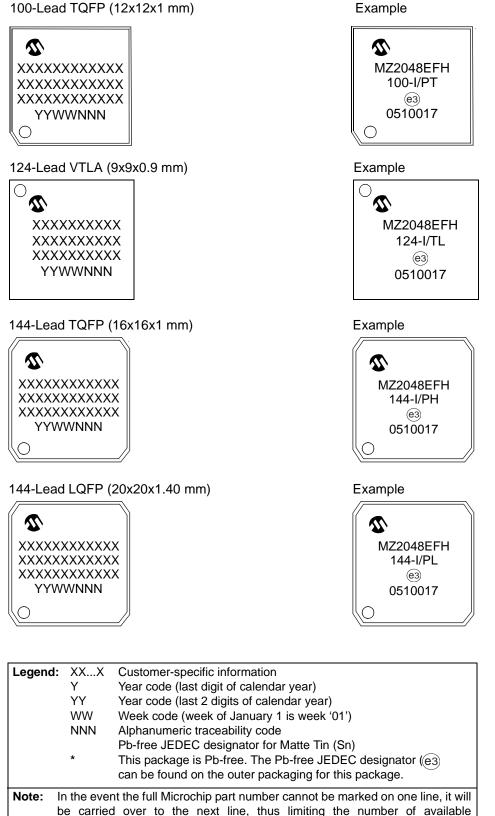

#### 41.1 Package Marking Information (Continued)

100-Lead TQFP (12x12x1 mm)

characters for customer-specific information.

# A.4 Resets

The PIC32MZ EF family of devices has updated the resets modules to incorporate the new handling of NMI resets from the WDT, DMT, and the FSCM. In addition, some bits have been moved, as summarized in Table A-5.

### TABLE A-5: RESET DIFFERENCES

| PIC32MX5XX/6XX/7XX Feature                                                                                                               | PIC32MZ EF Feature                                                                                                                                                                                                                   |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Power Reset                                                                                                                              |                                                                                                                                                                                                                                      |  |  |  |

|                                                                                                                                          | The VREGS bit, which controls whether the internal regulator is<br>enabled in Sleep mode, has been moved from RCON in<br>PIC32MX5XX/6XX/7XX devices to a new PWRCON register in<br>PIC32MZ EF devices.                               |  |  |  |

| VREGS ( <b>RCON&lt;8&gt;</b> )                                                                                                           | VREGS ( <b>PWRCON&lt;0&gt;</b> )                                                                                                                                                                                                     |  |  |  |

| <ul> <li>1 = Regulator is enabled and is on during Sleep mode</li> <li>0 = Regulator is disabled and is off during Sleep mode</li> </ul> | <ul><li>1 = Voltage regulator will remain active during Sleep</li><li>0 = Voltage regulator will go to Stand-by mode during Sleep</li></ul>                                                                                          |  |  |  |

| Watchdog Timer Reset                                                                                                                     |                                                                                                                                                                                                                                      |  |  |  |

| On PIC32MX devices, a WDT expiration immediately triggers a device reset.                                                                | On PIC32MZ EF devices, the WDT expiration now causes a NMI.<br>The WDTO bit in RNMICON indicates that the WDT caused the<br>NMI. A new timer, NMICNT, runs when the WDT NMI is triggered,<br>and if it expires, the device is reset. |  |  |  |

| WDT expiration immediately causes a device reset.                                                                                        | WDT expiration causes a NMI, which can then trigger the<br>device reset.<br>WDTO (RNMICON<24>)<br>1 = WDT time-out has occurred and caused a NMI<br>0 = WDT time-out has not occurred                                                |  |  |  |

|                                                                                                                                          | NMICNT<7:0> (RNMICON<7:0>)                                                                                                                                                                                                           |  |  |  |

### A.5 USB

The PIC32MZ EF family of devices has a new Hi-Speed USB module, which requires the updated USB stack from Microchip. In addition, the USB PLL was also updated. See **A.1** "Oscillator and PLL Configuration" for more information and Table A-6 for a list of additional differences.

### TABLE A-6: USB DIFFERENCES

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                            | PIC32MZ EF Feature                                                                                                |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Debug Mode                                                                                                                                                                            |                                                                                                                   |  |  |  |

| On PIC32MX devices, when stopping on a breakpoint during debugging, the USB module can be configured to stop or continue execution from the Freeze Peripherals dialog in MPLAB X IDE. |                                                                                                                   |  |  |  |

| VBUSON Pin                                                                                                                                                                            |                                                                                                                   |  |  |  |

| PIC32MX devices feature a VBUSON pin for controlling the external transceiver power supply.                                                                                           | On PIC32MZ EF devices, the VBUSON pin is not available. A port pin can be used to achieve the same functionality. |  |  |  |

NOTES: