#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 97                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | •                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

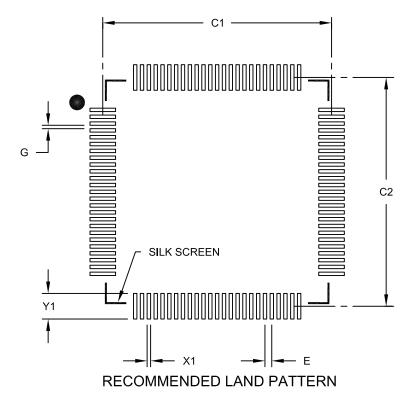

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                 |

| Supplier Device Package    | 124-VTLA (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efh124-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                       | Pin Nu          | mber            |                          |             |                |                                                                            |

|----------|---------------------------------------|-----------------|-----------------|--------------------------|-------------|----------------|----------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP                | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                                                |

|          |                                       |                 |                 |                          | J           | ΓAG            |                                                                            |

| ТСК      | 27                                    | 38              | B21             | 56                       | I           | ST             | JTAG Test Clock Input Pin                                                  |

| TDI      | 28                                    | 39              | A26             | 57                       | I           | ST             | JTAG Test Data Input Pin                                                   |

| TDO      | 24                                    | 40              | B22             | 58                       | 0           | —              | JTAG Test Data Output Pin                                                  |

| TMS      | 23                                    | 17              | A11             | 22                       | I           | ST             | JTAG Test Mode Select Pin                                                  |

|          | •                                     | •               | •               |                          | Tr          | ace            | •                                                                          |

| TRCLK    | 57                                    | 89              | A61             | 129                      | 0           | _              | Trace Clock                                                                |

| TRD0     | 58                                    | 97              | B55             | 141                      | 0           | —              | Trace Data bits 0-3                                                        |

| TRD1     | 61                                    | 96              | A65             | 140                      | 0           | —              |                                                                            |

| TRD2     | 62                                    | 95              | B54             | 139                      | 0           | —              |                                                                            |

| TRD3     | 63                                    | 90              | B51             | 130                      | 0           | —              |                                                                            |

|          |                                       |                 |                 | Pro                      | grammiı     | ng/Debugg      | ing                                                                        |

| PGED1    | 16                                    | 25              | A18             | 36                       | I/O         | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 1          |

| PGEC1    | 15                                    | 24              | A17             | 35                       | Ι           | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 1       |

| PGED2    | 18                                    | 27              | A19             | 38                       | I/O         | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 2          |

| PGEC2    | 17                                    | 26              | B14             | 37                       | Ι           | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 2       |

| MCLR     | 9                                     | 15              | A10             | 20                       | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device. |

| Legend:  | CMOS = CI<br>ST = Schm<br>TTL = Trans | itt Trigger ir  | put with C      | MOS level                |             | O = Outp       | Analog input P = Power<br>ut I = Input<br>eripheral Pin Select             |

#### **TABLE 1-22:** JTAG, TRACE, AND PROGRAMMING/DEBUGGING PINOUT I/O DESCRIPTIONS

The System Bus arbitration scheme implements a nonprogrammable, Least Recently Serviced (LRS) priority, which provides Quality Of Service (QOS) for most initiators. However, some initiators can use Fixed High Priority (HIGH) arbitration to guarantee their access to data.

The arbitration scheme for the available initiators is shown in Table 4-5.

| ID | QOS                                                                     |

|----|-------------------------------------------------------------------------|

| 1  | LRS <sup>(1)</sup>                                                      |

| 2  | HIGH <sup>(1,2)</sup>                                                   |

| 3  | LRS <sup>(1)</sup>                                                      |

| 4  | HIGH <sup>(1,2)</sup>                                                   |

| 5  | LRS <sup>(1)</sup>                                                      |

| 6  | HIGH <sup>(1,2)</sup>                                                   |

| 7  | LRS                                                                     |

| 8  | LRS                                                                     |

| 9  | LRS                                                                     |

| 10 | LRS                                                                     |

| 11 | LRS                                                                     |

| 12 | LRS                                                                     |

| 13 | HIGH <sup>(2)</sup>                                                     |

| 14 | LRS                                                                     |

|    | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>11<br>12<br>13 |

TABLE 4-5:INITIATOR ID AND QOS

- Note 1: When accessing SRAM, the DMAPRI bit (CFGCON<25>) and the CPUPRI bit (CFGCON<24>) provide arbitration control for the DMA and CPU (when servicing an interrupt (i.e., EXL = 1)), respectively, by selecting the use of LRS or HIGH When using HIGH, the DMA and CPU get arbitration preference over all initiators using LRS.

- 2: Using HIGH arbitration can have serious negative effects on other initiators. Therefore, it is recommended to not enable this type of arbitration for an initiator that uses significant system bandwidth. HIGH arbitration is intended to be used for low bandwidth applications that require low latency, such as LCC graphics applications.

## 4.3 Permission Access and System Bus Registers

The System Bus on PIC32MZ EF family of microcontrollers provides access control capabilities for the transaction initiators on the System Bus.

The System Bus divides the entire memory space into fourteen target regions and permits access to each target by initiators via permission groups. Four Permission Groups (0 through 3) can be assigned to each initiator. Each permission group is independent of the others and can have exclusive or shared access to a region.

Using the CFGPG register (see Register 34-10 in **Section 34.0 "Special Features"**), Boot firmware can assign a permission group to each initiator, which can make requests on the System Bus.

The available targets and their regions, as well as the associated control registers to assign protection, are described and listed in Table 4-6.

Register 4-2 through Register 4-10 are used for setting and controlling access permission groups and regions.

To change these registers, they must be unlocked in hardware. The register lock is controlled by the PGLOCK Configuration bit (CFGCON<11>). Setting PGLOCK prevents writes to the control registers; clearing PGLOCK allows writes.

To set or clear the PGLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators with Enhanced PLL"** in the *"PIC32 Family Reference Manual"* for details.

# PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

# REGISTER 4-10: SBTxWRy: SYSTEM BUS TARGET 'x' REGION 'y' WRITE PERMISSIONS REGISTER ('x' = 0-13; 'y' = 0-8)

|              |                   | •                 | ,                 |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 |                   |                   | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 |                   |                   | _                 |                   | _                 |                  | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 |                  | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-1             | R/W-1            | R/W-1            |

| 7:0          |                   |                   | _                 | _                 | GROUP3            | GROUP2            | GROUP1           | GROUP0           |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

#### bit 31-4 Unimplemented: Read as '0'

more information.

|       |      | •·····•                                                                                                    |

|-------|------|------------------------------------------------------------------------------------------------------------|

| bit 3 |      | Group3: Group 3 Write Permissions bits                                                                     |

|       |      | 1 = Privilege Group 3 has write permission                                                                 |

|       |      | 0 = Privilege Group 3 does not have write permission                                                       |

| bit 2 |      | Group2: Group 2 Write Permissions bits                                                                     |

|       |      | 1 = Privilege Group 2 has write permission                                                                 |

|       |      | 0 = Privilege Group 2 does not have write permission                                                       |

| bit 1 |      | Group1: Group 1 Write Permissions bits                                                                     |

|       |      | 1 = Privilege Group 1 has write permission                                                                 |

|       |      | 0 = Privilege Group 1 does not have write permission                                                       |

| bit 0 |      | Group0: Group 0 Write Permissions bits                                                                     |

|       |      | 1 = Privilege Group 0 has write permission                                                                 |

|       |      | 0 = Privilege Group 0 does not have write permission                                                       |

|       |      |                                                                                                            |

| Note  | ə 1: | Refer to Table 4-6 for the list of available targets and their descriptions.                               |

|       | 2:   | For some target regions, certain bits in this register are read-only with preset values. See Table 4-6 for |

DS60001320D-page 98

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>)                   |                                 | e         |       |       |       |               |               |                  |          | Bi                      | its  |      |              |                                |             |                      |                         |                         | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|---------------|---------------|------------------|----------|-------------------------|------|------|--------------|--------------------------------|-------------|----------------------|-------------------------|-------------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12         | 27/11         | 26/10            | 25/9     | 24/8                    | 23/7 | 22/6 | 21/5         | 20/4                           | 19/3        | 18/2                 | 17/1                    | 16/0                    | All Resets |

| 0450                        | 10044                           | 31:16     | _     | _     | —     | A             | ADCDC2IP<2:   | 0>               | ADCDC2   | 2IS<1:0>                | —    | —    | —            | A                              | ADCDC1IP<2  | ::0>                 | ADCDC                   | 1IS<1:0>                | 0000       |

| 01F0                        | IPC11                           | 15:0      | _     | _     | -     | A             | DCFIFOIP<2    | :0>              | ADCFIFC  | DIS<1:0>                | _    | _    | _            |                                | ADCIP<2:0   | >                    | ADCIS                   | S<1:0>                  | 000        |

| 0000                        | 10040                           | 31:16     |       | _     | -     | A             | ADCDC6IP<2:   | 0>               | ADCDC6   | 6IS<1:0>                | —    | _    | —            | A                              | ADCDC5IP<2  | 2:0>                 | ADCDC                   | 5IS<1:0>                | 000        |

| 0200                        | IPC12                           | 15:0      | _     | _     | _     | A             | ADCDC4IP<2:   | 0>               | ADCDC4   | IS<1:0>                 | —    | —    | —            | A                              | ADCDC3IP<2  | 2:0>                 | ADCDC                   | 3IS<1:0>                | 000        |

| 0040                        | 10040                           | 31:16     | _     | _     | -     | A             | ADCDF4IP<2:   | 0>               | ADCDF4   | IS<1:0>                 | _    | _    | _            | Å                              | ADCDF3IP<2  | :0>                  | ADCDF                   | 3IS<1:0>                | 000        |

| 0210                        | IPC13                           | 15:0      |       | _     | -     | A             | ADCDF2IP<2:   | 0>               | ADCDF2   | IS<1:0>                 | —    | _    | —            | Å                              | ADCDF1IP<2  | :0>                  | ADCDF1                  | IIS<1:0>                | 000        |

| 0000                        |                                 | 31:16     |       | _     | _     |               | ADCD0IP<2:0   | )>               | ADCD0    | S<1:0>                  | —    | —    | —            | A                              | DCDFLTIP<   | 2:0>                 | ADCDFL                  | TIS<1:0>                | 000        |

| 0220                        | IPC14                           | 15:0      |       | _     | _     | A             | ADCDF6IP<2:   | 0>               | ADCDF6   | IS<1:0>                 | —    | —    | —            | ļ                              | ADCDF5IP<2  | :0>                  | ADCDF                   | 5IS<1:0>                | 000        |

| 0000                        | IPC15                           | 31:16     | _     | _     | _     |               | ADCD4IP<2:0   | )>               | ADCD4    | S<1:0>                  | _    | _    | _            |                                | ADCD3IP<2:  | 0>                   | ADCD3                   | IS<1:0>                 | 000        |

| 0230                        | IPC 15                          | 15:0      | _     | _     | _     |               | ADCD2IP<2:0   | )>               | ADCD2    | S<1:0>                  | _    | _    | _            |                                | ADCD1IP<2:  | 0>                   | ADCD1                   | IS<1:0>                 | 000        |

| 0240                        | IPC16                           | 31:16     |       | _     | _     |               | ADCD8IP<2:0>  |                  | ADCD8    | S<1:0>                  | —    | —    | —            | ADCD7IP<2:0>                   |             | ADCD7                | IS<1:0>                 | 000                     |            |

| 0240                        | IPC ID                          | 15:0      | _     | _     | _     | ADCD6IP<2:0>  |               | ADCD6            | S<1:0>   | _                       | _    | _    | ADCD5IP<2:0> |                                | ADCD5       | IS<1:0>              | 000                     |                         |            |

| 0250                        | IPC17                           | 31:16     | —     | _     | -     | ADCD12IP<2:0> |               | ADCD12           | IS<1:0>  | —                       | —    | —    | 1            | ADCD11IP<2                     | :0>         | ADCD11               | IS<1:0>                 | 000                     |            |

| 0250                        |                                 | 15:0      | _     | _     | —     | A             | ADCD10IP<2:0> |                  | ADCD10   | IS<1:0>                 | —    | —    | —            |                                | ADCD9IP<2:  | 0>                   | ADCD9                   | IS<1:0>                 | 000        |

| 0260                        | IPC18                           | 31:16     | _     | _     | —     | A             | ADCD16IP<2:   | 0>               | ADCD16   | IS<1:0>                 | _    | —    | —            | ŀ                              | ADCD15IP<2  | :0>                  | ADCD15                  | 5IS<1:0>                | 000        |

| 0260                        | IPC IO                          | 15:0      | —     | _     | -     | A             | ADCD14IP<2:   | 0>               | ADCD14   | IS<1:0>                 | —    | —    | —            | ŀ                              | ADCD13IP<2  | :0>                  | ADCD13                  | 3IS<1:0>                | 000        |

| 0070                        |                                 | 31:16     | _     | _     | —     | A             | DCD20IP<2:0   | >(2)             | ADCD201  | S<1:0> <sup>(2)</sup>   | —    | —    | —            | A                              | DCD19IP<2:  | <sub>)&gt;</sub> (2) | ADCD19I                 | S<1:0> <sup>(2)</sup>   | 000        |

| 0270                        | IPC19                           | 15:0      | _     | —     | -     | A             | ADCD18IP<2:   | 0>               | ADCD18   | IS<1:0>                 | —    | —    | —            | ŀ                              | ADCD17IP<2  | :0>                  | ADCD17                  | 7IS<1:0>                | 000        |

| 0200                        | IPC20                           | 31:16     | _     | —     | -     | A             | DCD24IP<2:0   | > <sup>(2)</sup> | ADCD24   | S<1:0> <sup>(2)</sup>   | —    | —    | —            | A                              | DCD23IP<2:  | )> <sup>(2)</sup>    | ADCD23I                 | S<1:0> <sup>(2)</sup>   | 000        |

| 0260                        | IPC20                           | 15:0      | _     | _     | —     | A             | DCD22IP<2:0   | >(2)             | ADCD22I  | S<1:0> <sup>(2)</sup>   | —    | —    | —            | A                              | DCD21IP<2:  | <sub>)&gt;</sub> (2) | ADCD211                 | S<1:0> <sup>(2)</sup>   | 000        |

| 0200                        | IPC21                           | 31:16     | _     | _     | —     | A             | DCD28IP<2:0   | > <sup>(2)</sup> | ADCD28   | S<1:0> <sup>(2)</sup>   | _    | —    | —            | A                              | DCD27IP<2:  | )> <sup>(2)</sup>    | ADCD27I                 | S<1:0> <sup>(2)</sup>   | 000        |

| 0290                        | IFUZI                           | 15:0      | _     | _     | —     | A             | DCD26IP<2:0   | > <sup>(2)</sup> | ADCD26   | S<1:0> <sup>(2)</sup>   | _    | —    | —            |                                | DCD25IP<2:  |                      | ADCD25I                 |                         | 000        |

| 0240                        | IPC22                           | 31:16     | _     | _     | —     | A             | DCD32IP<2:0   | > <sup>(2)</sup> | ADCD32   | S<1:0> <sup>(2)</sup>   | —    | —    | —            | A                              | DCD31IP<2:  | )> <sup>(2)</sup>    | ADCD311                 | S<1:0> <sup>(2)</sup>   | 000        |

| 02A0                        | 19622                           | 15:0      | _     | _     | —     | A             | DCD30IP<2:0   | > <sup>(2)</sup> | ADCD30   |                         | _    | —    | —            | A                              | DCD29IP<2:  | )> <sup>(2)</sup>    | ADCD29I                 |                         | 000        |

| 0280                        | IPC23                           | 31:16     |       | _     | —     | AD            | CD36IP<2:0>   | (2,4)            | ADCD36IS | S<1:0>(2,4)             | —    | —    | —            | AD                             | DCD35IP<2:0 | >(2,4)               | ADCD3518                | S<1:0> <sup>(2,4)</sup> | 000        |

| 0200                        | 15023                           | 15:0      |       | _     | —     | A             | DCD34IP<2:0   | >(2)             | ADCD341  | S<1:0> <sup>(2)</sup>   | —    | —    | —            | ADCD33IP<2:0> <sup>(2)</sup>   |             | ADCD33I              | S<1:0>(2)               | 000                     |            |

| 0200                        | IPC24                           | 31:16     |       | —     | —     | AD            | CD40IP<2:0>   | (2,4)            | ADCD40IS | S<1:0> <sup>(2,4)</sup> | —    | —    | —            | ADCD39IP<2:0> <sup>(2,4)</sup> |             | ADCD39IS             | S<1:0> <sup>(2,4)</sup> | 000                     |            |

| 0200                        | 1F024                           | 15:0      | _     | —     | -     | AD            | CD38IP<2:0>   | (2,4)            | ADCD38IS | S<1:0> <sup>(2,4)</sup> | —    | _    | _            | ADCD37IP<2:0> <sup>(2,4)</sup> |             | ADCD3718             | S<1:0> <sup>(2,4)</sup> | 000                     |            |

| 0200                        | IDCOF                           | 31:16     |       | —     | —     | A             | ADCD44IP<2:   | 0>               | ADCD44   | IS<1:0>                 | —    | _    | —            | ADCD43IP<2:0>                  |             | ADCD43               | 3IS<1:0>                | 000                     |            |

| 0200                        | IPC25                           | 15:0      |       | _     | _     | AD            | CD42IP<2:0>   | (2,4)            | ADCD42IS | S<1:0> <sup>(2,4)</sup> | _    | _    | _            | AD                             | DCD41IP<2:0 | > <sup>(2,4)</sup>   | ADCD41IS                | S<1:0> <sup>(2,4)</sup> | 000        |

Legend:

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

3: This bit or register is not available on devices without a CAN module.

4: This bit or register is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>f)                  | <b>b</b> -                      | Ð         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |         | ,          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|---------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0    | All Decete |

|                             | 055450                          | 31:16     | _     | -     | _     | —     | -     | _     | _    | —          | _    | —    | _    | —    | —    | —    | VOFF< | :17:16> | 00         |

| J7A4                        | OFF153                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      | •    |      |      | •     | _       | 000        |

| 1749                        | OFF154                          | 31:16     | _     | _     | _     | _     | —     | —     | —    | _          | _    | _    | —    | —    | —    | _    | VOFF< | :17:16> | 00         |

| JIAO                        | UFF154                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 000        |

|                             | OFF155                          | 31:16     | —     | _     | _     | _     | _     | -     |      |            | _    | —    | -    | —    | _    | —    | VOFF< | :17:16> | 000        |

| JIAC                        | 0FF155                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 000        |

|                             | OFF156                          | 31:16     | -     |       | _     | —     |       |       |      | —          | _    | _    |      | —    | —    | —    | VOFF< | :17:16> | 000        |

| 5760                        | OFF 150                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 000        |

| 1784                        | OFF157                          | 31:16     | _     | -     | —     | —     | _     | —     | —    | —          | _    | —    | -    | —    | —    | —    | VOFF< | :17:16> | 000        |

| 57 04                       | 011137                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      | -     | _       | 000        |

| 1788                        | OFF158                          | 31:16     | -     |       | —     | —     |       |       |      | —          | —    | _    |      | -    | _    | —    | VOFF< | :17:16> | 000        |

| 0100                        | 011130                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 000        |

|                             | OFF159                          | 31:16     | _     | _     | —     | —     | _     | _     | _    | _          | _    | —    | _    | —    | —    | _    | VOFF< | :17:16> | 000        |

| льс                         | 011139                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      | -    |      | -    | -    |      |       | —       | 000        |

| 1700                        | OFF160                          | 31:16     | _     | _     | —     | —     | _     | _     | _    | _          | _    | —    | -    | —    | _    | —    | VOFF< | :17:16> | 000        |

| 5700                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 000        |

| 1704                        | OFF161                          | 31:16     | —     | _     | —     | —     |       |       |      | —          | _    | —    |      |      | —    | _    | VOFF< | :17:16> | 000        |

| 5704                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      | -    |      | -    | -    |      |       | —       | 000        |

| 1708                        | OFF162                          | 31:16     | —     | _     | —     | —     | _     | —     | —    | —          | _    | —    | —    | —    | —    | _    | VOFF< | :17:16> | 000        |

| 5700                        | 011102                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 000        |

| 700                         | OFF163                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | _    | _    | —    | —    | —    | VOFF< | :17:16> | 000        |

|                             | 011100                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 000        |

| 0700                        | OFF164                          | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | :17:16> | 000        |

| 5100                        | 011104                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      | -    |      | -    | -    |      |       | —       | 000        |

| 1704                        | OFF165                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | _    | VOFF< | :17:16> | 000        |

| 5704                        | 51105                           | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 000        |

| פחדר                        | OFF166                          | 31:16     | _     | _     | _     | -     | _     | _     | _    | —          | _    | _    | —    | _    | _    | —    | VOFF< | :17:16> | 000        |

| VOFF<15:1>                  |                                 |           |       |       |       |       |       |       |      |            |      |      |      | _    | 000  |      |       |         |            |

|                             | OFF167                          | 31:16     | _     | _     | -     | -     |       | _     | _    | _          | —    | —    | _    | —    | —    | —    | VOFF< | :17:16> | 000        |

|                             |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 000        |

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0                        | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | —                 | _                 | _                 | —                          | —                 | —                | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0                      | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | —                 | —                 | _                 | —                 | SYSDIV<3:0> <sup>(1)</sup> |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0                        | R/W-0             | R/W-1            | R/W-0            |  |

| 15:8         | —                 | —                 | _                 | _                 | —                          | SLWDIV<2:0>       |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                        | R/W-1             | R/W-0            | R-0, HS, HC      |  |

| 7:0          |                   | _                 |                   |                   | _                          | UPEN              | DNEN             | BUSY             |  |

#### REGISTER 8-7: SLEWCON: OSCILLATOR SLEW CONTROL REGISTER

| Legend:           | HC = Hardware Cleared | HS = Hardware Set         |                    |  |  |  |

|-------------------|-----------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, re | ad as '0'          |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

bit 31-20 Unimplemented: Read as '0'

```

bit 19-16 SYSDIV<3:0>: System Clock Divide Control bits<sup>(1)</sup>

```

- bit 15-11 Unimplemented: Read as '0'

- bit 10-8 **SLWDIV<2:0>:** Slew Divisor Steps Control bits

These bits control the maximum division steps used when slewing during a frequency change.

- 111 = Steps are divide by 128, 64, 32, 16, 8, 4, 2, and then no divisor

- 110 = Steps are divide by 64, 32, 16, 8, 4, 2, and then no divisor

- 101 = Steps are divide by 32, 16, 8, 4, 2, and then no divisor

- 100 = Steps are divide by 16, 8, 4, 2, and then no divisor

- 011 = Steps are divide by 8, 4, 2, and then no divisor

- 010 = Steps are divide by 4, 2, and then no divisor

- 001 = Steps are divide by 2, and then no divisor

- 000 = No divisor is used during slewing

Note: The steps apply in reverse order (i.e., 2, 4, 8, etc.) during a downward frequency change.

- bit 7-3 **Unimplemented:** Read as '0'

- bit 2 UPEN: Upward Slew Enable bit

- 1 = Slewing enabled for switching to a higher frequency

- 0 = Slewing disabled for switching to a higher frequency

- bit 1 **DNEN:** Downward Slew Enable bit

- 1 = Slewing enabled for switching to a lower frequency

- 0 = Slewing disabled for switching to a lower frequency

- bit 0 BUSY: Clock Switching Slewing Active Status bit

- 1 = Clock frequency is being actively slewed to the new frequency

- 0 = Clock switch has reached its final value

**Note 1:** The SYSDIV<3:0> bit settings are ignored if both UPEN and DNEN = 0, and SYSCLK will be divided by 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | DMAADD            | R<31:24>          |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | DMAADE            | DR<15:8>          |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 7:0          |                   | •                 | •                 | DMAAD             | DR<7:0>           |                   |                  | •                |  |  |  |

#### **REGISTER 11-22: USBDMAXA: USB DMA CHANNEL 'x' MEMORY ADDRESS REGISTER ('x' = 1-8)**

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DMAADDR<31:0>: DMA Memory Address bits

This register identifies the current memory address of the corresponding DMA channel. The initial memory address written to this register during initialization must have a value such that its modulo 4 value is equal to '0'. The lower two bits of this register are read only and cannot be set by software. As the DMA transfer progresses, the memory address will increment as bytes are transferred.

| REGISTE | ER 11-23: U | USBDMAxN   | : USB DMA  | CHANNEL    | 'x' COUNT  | REGISTER   | ('X' = 1-8) |              |

|---------|-------------|------------|------------|------------|------------|------------|-------------|--------------|

| Bit     | Bit         | Bit        | Bit        | Bit        | Bit        | Bit        | Bit         | Bit          |

| Danaa   | 24/22/4E/7  | 20/22/44/6 | 20/24/42/5 | 20/20/42/4 | 27/40/44/2 | 26/40/40/2 | 25/47/0/4   | 2 A / A C /0 |

| Range                 | 31/23/15/7    | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |  |  |

|-----------------------|---------------|------------|------------|------------|------------|------------|-----------|-----------|--|--|

| 24.24                 | R/W-0         | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0     | R/W-0     |  |  |

| 31:24                 |               |            |            | DMACOUN    | NT<31:24>  |            |           |           |  |  |

| 23:16                 | R/W-0         | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0     | R/W-0     |  |  |

| 23.10 DMACOUNT<23:16> |               |            |            |            |            |            |           |           |  |  |

| 15:8                  | R/W-0         | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0     | R/W-0     |  |  |

| 10.0                  |               |            |            | DMACOU     | NT<15:8>   |            |           |           |  |  |

| 7:0                   | R/W-0         | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0     | R/W-0     |  |  |

| 7.0                   | DMACOUNT<7:0> |            |            |            |            |            |           |           |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-0 DMACOUNT<31:0>: DMA Transfer Count bits

This register identifies the current DMA count of the transfer. Software will set the initial count of the transfer which identifies the entire transfer length. As the count progresses this count is decremented as bytes are transferred.

#### TABLE 12-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| ss                          |                       |           | Bits       |             |       |       |       |       |      |               |      |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|------------|-------------|-------|-------|-------|-------|------|---------------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15      | 30/14       | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8          | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | —     | _      | _    | 0000       |

| 1538                        | RPA14R <sup>(1)</sup> | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPA14 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    | _    | —     | —      | —    | 0000       |

| 153C                        | RPA15R <sup>(1)</sup> | 15:0      | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    |      | RPA15 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    | _    | —     | —      | —    | 0000       |

| 1540                        | RPB0R                 | 15:0      | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    |      | RPB0  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| 1544                        | RPB1R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPB1  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    | _    | —     | —      | —    | 0000       |

| 1548                        | RPB2R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB2  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| 154C                        | RPB3R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB3  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| 1554                        | RPB5R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB5  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          |             | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | _     | _      | _    | 0000       |

| 1558                        | RPB6R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    |      | _    |      | RPB6  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 155C                        | RPB7R                 | 15:0      | _          | _           | _     | _     | _     |       | _    | _             | _    | _    | _    | _    |      | RPB7  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1560                        | RPB8R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB8  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1564                        | RPB9R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB9  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1568                        | RPB10R                | 15:0      | _          | _           | _     | _     | _     |       | _    | _             | _    | _    | _    | _    |      | RPB10 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | _     | _      | _    | 0000       |

| 1578                        | RPB14R                | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPB14 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 157C                        | RPB15R                | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPB15 | R<3:0> |      | 0000       |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    |      | _    | _    | _     | _      | _    | 0000       |

| 1584                        | RPC1R <sup>(1)</sup>  | 15:0      | _          |             | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPC1  | R<3:0> |      | 0000       |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1588                        | RPC2R <sup>(1)</sup>  | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPC2  | R<3:0> |      | 0000       |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 158C                        | RPC3R <sup>(1)</sup>  | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPC3  | R<3:0> |      | 0000       |

|                             | (0)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1590                        | RPC4R <sup>(1)</sup>  | 15:0      | _          |             | _     | _     | _     |       | _    | _             | _    |      | _    | _    |      | RPC4  | R<3:0> |      | 0000       |

| Legen                       | l                     |           | alua an Da | eset: — = u |       |       |       |       |      | h ava da aira |      |      |      |      | l    |       |        |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note** 1: This register is not available on 64-pin devices.

2: This register is not available on 64-pin and 100-pin devices.

NOTES:

# 18.1 Output Compare Control Registers

# TABLE 18-2: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 9 REGISTER MAP

| ess                         |                                 |               |         |            |           |       |       |       |      | Bi    | ts           |      |           |            |             |      |               |      |              |

|-----------------------------|---------------------------------|---------------|---------|------------|-----------|-------|-------|-------|------|-------|--------------|------|-----------|------------|-------------|------|---------------|------|--------------|

| Virtual Address<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14      | 29/13     | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7         | 22/6 | 21/5      | 20/4       | 19/3        | 18/2 | 17/1          | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16<br>15:0 | –<br>ON |            | —<br>SIDL | _     |       |       |      |       |              | _    | —<br>OC32 | —<br>OCFLT | —<br>OCTSEL |      | —<br>OCM<2:0> | —    | 0000         |

| 4010                        | OC1R                            | 31:16<br>15:0 | ÖN      |            | OIDE      |       |       |       |      | OC1R- |              |      | 0002      | 001 EI     | OUTOLL      |      | 00111(2.0)    |      | xxxx         |

| 4020                        | OC1RS                           | 31:16<br>15:0 |         |            |           |       |       |       |      | OC1RS | <31:0>       |      |           |            |             |      |               |      | xxxx<br>xxxx |

| 4200                        | OC2CON                          | 31:16<br>15:0 | —<br>ON |            | —<br>SIDL | —     |       | -     |      |       |              |      | —<br>OC32 | —<br>OCFLT | —<br>OCTSEL |      | —<br>OCM<2:0> | —    | 0000         |

| 4210                        | OC2R                            | 31:16<br>15:0 | -       |            |           |       |       |       |      | OC2R- | <31:0>       |      |           |            |             |      |               |      | xxxx<br>xxxx |

| 4220                        | OC2RS                           | 31:16<br>15:0 |         |            |           |       |       |       |      | OC2RS | <31:0>       |      |           |            |             |      |               |      | xxxx<br>xxxx |

| 4400                        | OC3CON                          | 31:16<br>15:0 | ON      | _          | —<br>SIDL | _     |       | _     | _    | _     | _            |      | —<br>OC32 | —<br>OCFLT | —<br>OCTSEL | _    | —<br>OCM<2:0> | _    | 0000         |

| 4410                        | OC3R                            | 31:16<br>15:0 |         | OC3R<31:0> |           |       |       |       |      |       | xxxx<br>xxxx |      |           |            |             |      |               |      |              |

| 4420                        | OC3RS                           | 31:16<br>15:0 |         |            |           |       |       |       |      | OC3RS | <31:0>       |      |           |            |             |      |               |      | xxxx<br>xxxx |

| 4600                        | OC4CON                          | 31:16<br>15:0 | –<br>ON |            | —<br>SIDL | _     | _     | _     | -    | _     | -            | _    | —<br>OC32 | —<br>OCFLT | —<br>OCTSEL | —    | —<br>OCM<2:0> | _    | 0000         |

| 4610                        | OC4R                            | 31:16<br>15:0 |         |            |           |       |       |       |      | OC4R  | <31:0>       |      |           |            |             |      |               |      | xxxx<br>xxxx |

| 4620                        | OC4RS                           | 31:16<br>15:0 |         |            |           |       |       |       |      | OC4RS | <31:0>       |      |           |            |             |      |               |      | xxxx<br>xxxx |

| 4800                        | OC5CON                          | 31:16<br>15:0 | –<br>ON |            | —<br>SIDL |       |       |       |      |       |              |      | —<br>OC32 | —<br>OCFLT | —<br>OCTSEL | —    | —<br>OCM<2:0> | _    | 0000         |

| 4810                        | OC5R                            | 31:16<br>15:0 |         |            |           |       |       |       |      | OC5R  | <31:0>       |      |           |            |             |      |               |      | xxxx<br>xxxx |

| 4820                        | OC5RS                           | 31:16<br>15:0 |         |            |           |       |       |       |      | OC5RS | <31:0>       |      |           |            |             |      |               |      | xxxx<br>xxxx |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0                   | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   | —                    | -                     |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0                   | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | _                     |                   | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0                   | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | SIDL              | —                    | _                     | -                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0                 | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   | OC32              | OCFLT <sup>(1)</sup> | OCTSEL <sup>(2)</sup> |                   | OCM<2:0>         |                  |

#### REGISTER 18-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(1)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 OCTSEL: Output Compare Timer Select bit<sup>(2)</sup>

- 1 = Timery is the clock source for this Output Compare module

- 0 = Timerx is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin is enabled

- 110 = PWM mode on OCx; Fault pin is disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

- **2:** Refer to Table 18-1 for Timerx and Timery selections.

| Bit<br>Range | Bit<br>31/23/15/7                   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0                               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | TXDATA<31:24>                       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 22.10        | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   |                   |                   |                  |                  |  |  |

| 23:16        | TXDATA<23:16>                       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0                               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                                     |                   |                   | TXDATA            | <15:8>            |                   |                  |                  |  |  |

| 7.0          | R/W-0                               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | TXDATA<7:0>                         |                   |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 20-10: SQI1TXDATA: SQI TRANSMIT DATA BUFFER REGISTER

| L | _egend:          |                  |                          |                    |

|---|------------------|------------------|--------------------------|--------------------|

| F | R = Readable bit | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| - | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 TXDATA<31:0>: Transmit Command Data bits

Data is loaded into this register before being transmitted. Prior to the data transfer, the data in TXDATA is loaded into the shift register (SFDR).

Multiple writes to TXDATA can occur while a transfer is in progress. There can be a maximum of eight commands that can be queued.

#### REGISTER 20-11: SQI1RXDATA: SQI RECEIVE DATA BUFFER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7               | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|---------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R-0                             | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 31:24        | RXDATA<31:24>                   |                   |                   |                   |                   |                   |                  |                  |  |

| 22.10        | R-0                             | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23:16        | RXDATA<23:16>                   |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R-0                             | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         |                                 |                   |                   | RXDATA            | <15:8>            |                   |                  |                  |  |

| 7.0          | R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | RXDATA<7:0>                     |                   |                   |                   |                   |                   |                  |                  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 RXDATA<31:0>: Receive Data Buffer bits

At the end of a data transfer, the data in the shift register is loaded into the RXDATA register. This register works like a FIFO. The depth of the receive buffer is eight words.

| Bit<br>1/23/15/7<br>U-0<br>U-0<br>U-0 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4                        | Bit<br>27/19/11/3<br>U-0                                                                                                        | Bit<br>26/18/10/2                       | Bit<br>25/17/9/1                                                  | Bit<br>24/16/8/0                                                                 |

|---------------------------------------|-------------------|-------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------|

| _                                     | _                 | U-0               | U-0                                      | U-0                                                                                                                             | U-0                                     | U-0                                                               | 11-0                                                                             |

| —<br>U-0                              | -                 | _                 |                                          |                                                                                                                                 |                                         | °                                                                 | 0-0                                                                              |

| U-0                                   | 11.0              |                   |                                          | —                                                                                                                               | —                                       | —                                                                 | —                                                                                |

|                                       | U-0               | U-0               | U-0                                      | U-0                                                                                                                             | U-0                                     | U-0                                                               | U-0                                                                              |

| —                                     | _                 | —                 | —                                        | _                                                                                                                               | —                                       | —                                                                 | —                                                                                |

| U-0                                   | U-0               | U-0               | U-0                                      | R/W-0                                                                                                                           | R/W-0                                   | R/W-0                                                             | R/W-0                                                                            |

| —                                     |                   | —                 | —                                        | DMAEISE                                                                                                                         | PKT<br>DONEISE                          | BD<br>DONEISE                                                     | CON<br>THRISE                                                                    |

| R/W-0                                 | R/W-0             | R/W-0             | R/W-0                                    | R/W-0                                                                                                                           | R/W-0                                   | R/W-0                                                             | R/W-0                                                                            |

| CON<br>MPTYISE                        | CON<br>FULLISE    | RX<br>THRISE      | RX<br>FULLISE                            | RX<br>EMPTYISE                                                                                                                  | TX<br>THRISE                            | TX<br>FULLISE                                                     | TX<br>EMPTYISE                                                                   |

| Ν                                     | R/W-0<br>CON      | R/W-0R/W-0CONCON  | — — —<br>R/W-0 R/W-0 R/W-0<br>CON CON RX | -         -         -           R/W-0         R/W-0         R/W-0         R/W-0           CON         CON         RX         RX | DMAEISER/W-0R/W-0R/W-0R/W-0CONCONRXRXRX | DMAEISEPKT<br>DONEISER/W-0R/W-0R/W-0R/W-0R/W-0R/W-0CONCONRXRXRXRX | DMAEISEPKT<br>DONEISEBD<br>DONEISER/W-0R/W-0R/W-0R/W-0R/W-0R/W-0CONCONRXRXRXTXTX |

## REGISTER 20-22: SQI1INTSIGEN: SQI INTERRUPT SIGNAL ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

|-------------------|------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-12 Unimplemented: Read as '0'

| bit 11 | DMAEISE: DMA Bus Error Interrupt Signal Enable bit                                                       |

|--------|----------------------------------------------------------------------------------------------------------|

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 10 | PKTDONEISE: Receive Error Interrupt Signal Enable bit                                                    |

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 9  | BDDONEISE: Transmit Error Interrupt Signal Enable bit                                                    |

|        | <ol> <li>Interrupt signal is enabled</li> </ol>                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 8  | CONTHRISE: Control Buffer Threshold Interrupt Signal Enable bit                                          |

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 7  | CONEMPTYISE: Control Buffer Empty Interrupt Signal Enable bit                                            |

|        | 1 = Interrupt signal is enabled                                                                          |