Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32 <sup>®</sup> M-Class                                                       |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 120                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 48x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-TFBGA                                                                         |

| Supplier Device Package    | 144-TFBGA (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efh144-i-jwx |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |  |

# REGISTER 10-9: DCHxINT: DMA CHANNEL x INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

# bit 31-24 Unimplemented: Read as '0'

| bit 23   | CHSDIE: Channel Source Done Interrupt Enable bit                                        |

|----------|-----------------------------------------------------------------------------------------|

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 22   | CHSHIE: Channel Source Half Empty Interrupt Enable bit                                  |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 21   | CHDDIE: Channel Destination Done Interrupt Enable bit                                   |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 20   | CHDHIE: Channel Destination Half Full Interrupt Enable bit                              |

|          | 1 = Interrupt is enabled                                                                |

| 1.11.40  | 0 = Interrupt is disabled                                                               |

| bit 19   | CHBCIE: Channel Block Transfer Complete Interrupt Enable bit                            |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>         |

| bit 18   |                                                                                         |

| DIL TO   | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled |

|          | 0 = Interrupt is disabled                                                               |

| bit 17   | CHTAIE: Channel Transfer Abort Interrupt Enable bit                                     |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 16   | CHERIE: Channel Address Error Interrupt Enable bit                                      |

|          | 1 = Interrupt is enabled                                                                |

|          | 0 = Interrupt is disabled                                                               |

| bit 15-8 | Unimplemented: Read as '0'                                                              |

| bit 7    | CHSDIF: Channel Source Done Interrupt Flag bit                                          |

|          | 1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)                  |

|          | 0 = No interrupt is pending                                                             |

| bit 6    | CHSHIF: Channel Source Half Empty Interrupt Flag bit                                    |

|          | 1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)           |

|          | 0 = No interrupt is pending                                                             |

|          |                                                                                         |

REGISTER 11-4: USBCSR3: USB CONTROL STATUS REGISTER 3 (CONTINUED)

bit 19-16 ENDPOINT<3:0>: Endpoint Registers Select bits

- bit 19-11 Unimplemented: Read as 0

- bit 10-0 RFRMNUM<10:0>: Last Received Frame Number bits

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | NRSTX            | NRST             |  |  |

| 00.40        | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-0             | R/W-1            | R/W-0            |  |  |

| 23:16        | LSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-0             | R/W-1             | R/W-1             | R/W-1             | R/W-0             | R.W-1             | R/W-1            | R/W-1            |  |  |

| 15:8         | FSEOF<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R.W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | HSEOF<7:0>        |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 11-17: USBEOFRST: USB END-OF-FRAME/SOFT RESET CONTROL REGISTER

# Legend:

| 3                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-26 Unimplemented: Read as '0'

- bit 25 NRSTX: Reset of XCLK Domain bit

- 1 = Reset the XCLK domain, which is clock recovered from the received data by the PHY 0 = Normal operation

#### bit 24 NRST: Reset of CLK Domain bit

1 = Reset the CLK domain, which is clock recovered from the peripheral bus

0 = Normal operation

bit 23-16 LSEOF<7:0>: Low-Speed EOF bits These bits set the Low-Speed transaction in units of 1.067 μs (default setting is 121.6 μs) prior to the EOF to stop new transactions from beginning.

# bit 15-8 **FSEOF<7:0>:** Full-Speed EOF bits These bits set the Full-Speed transaction in units of 533.3 μs (default setting is 63.46 μs) prior to the EOF to stop new transactions from beginning.

#### bit 7-0 **HSEOF<7:0>:** Hi-Speed EOF bits These bits set the Hi-Speed transaction in units of 133.3 µs (default setting is 17.07µs) prior to the EOF to stop new transactions from beginning.

|              |                   | -                 | -                 | -                 |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | —                 | _                 | _                 | —                 | —                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | -                 | _                 | _                 | _                 | _                 | _                 | -                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 10.0         |                   | -                 |                   |                   | _                 |                   |                  | —                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | ?]R<3:0>         |                  |  |

#### **REGISTER 12-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|---------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 12-2 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

#### REGISTER 12-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | -                 |                   |                   | _                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

# Legend:

| R = Readable bit  | ble bit W = Writable bit |                      | ad as '0'          |

|-------------------|--------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 12-3 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | _                 | TXINTTHR<4:0>     |                   |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   | R                 | XINTTHR<4:0       | >                |                  |

# REGISTER 20-7: SQI1INTTHR: SQI INTERRUPT THRESHOLD REGISTER

# Legend:

| 3                                 |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-13 Unimplemented: Read as '0'

bit 12-8 **TXINTTHR<4:0>:** Transmit Interrupt Threshold bits A transmit interrupt is set when the transmit FIFO has more space than the set number of bytes. For 16-bit mode, the value should be a multiple of 2.

bit 7-5 Unimplemented: Read as '0'

#### bit 4-0 RXINTTHR<4:0>: Receive Interrupt Threshold bits

A receive interrupt is set when the receive FIFO count is larger than or equal to the set number of bytes. For 16-bit mode, the value should be multiple of 2.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | _                 | _                 | -                 | -                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | _                 | _                 | —                 | -                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 | _                 | _                 | START             | POLLEN           | DMAEN            |

#### REGISTER 20-14: SQI1BDCON: SQI BUFFER DESCRIPTOR CONTROL REGISTER

#### Legend:

bit 0

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-3 Unimplemented: Read as '0'

- bit 2 START: Buffer Descriptor Processor Start bit

- 1 = Start the buffer descriptor processor

- 0 = Disable the buffer descriptor processor

- bit 1 **POLLEN:** Buffer Descriptor Poll Enable bit

- 1 = BDP poll is enabled

- 0 = BDP poll is not enabled

- DMAEN: DMA Enable bit

- 1 = DMA is enabled

- 0 = DMA is disabled

#### REGISTER 20-15: SQI1BDCURADD: SQI BUFFER DESCRIPTOR CURRENT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24        | R-0 R-0 R-0 R-0 R-0 R-0 R-0 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 31:24        | BDCURRADDR<31:24>           |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R-0                         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | BDCURRADDR<23:16>           |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0                         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                             |                   |                   | BDCURRAD          | DR<15:8>          |                   |                  |                  |  |  |  |  |

| 7.0          | R-0                         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                             |                   |                   | BDCURRAD          | DDR<7:0>          |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 BDCURRADDR<31:0>: Current Buffer Descriptor Address bits

These bits contain the address of the current descriptor being processed by the Buffer Descriptor Processor.

# 23.1 PMP Control Registers

# TABLE 23-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | ő             |        |              |       |       |           |        |        | В      | its        |        |      |       |        |           |           |         | \$         |

|-----------------------------|---------------------------------|---------------|--------|--------------|-------|-------|-----------|--------|--------|--------|------------|--------|------|-------|--------|-----------|-----------|---------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14        | 29/13 | 28/12 | 27/11     | 26/10  | 25/9   | 24/8   | 23/7       | 22/6   | 21/5 | 20/4  | 19/3   | 18/2      | 17/1      | 16/0    | All Resets |

| E000                        | PMCON                           | 31:16         |        | —            | —     |       | —         | —      | —      |        | RDSTART    |        | —    |       | _      |           | DUALBUF   | _       | 0000       |

| LUUU                        | FINCON                          | 15:0          | ON     | —            | SIDL  | ADRMU | JX<1:0>   | PMPTTL | PTWREN | PTRDEN | CSF        | <1:0>  | ALP  | CS2P  | CS1P   |           | WRSP      | RDSP    | 0000       |

| E010                        | PMMODE                          | 31:16         | _      | —            | —     | _     | —         | —      |        | _      |            | —      | —    | —     | —      | _         | —         | _       | 0000       |

| 2010                        | _                               | 15:0          | BUSY   | IRQM         | <1:0> | INCM  | <1:0>     | MODE16 | MODE   | <1:0>  | WAITE      | 3<1:0> |      | WAITN | /<3:0> |           | WAITE     | <1:0>   | 0000       |

|                             |                                 | 31:16         | _      | —            | —     | —     |           | —      | —      | —      | —          | —      | —    | —     | —      | —         | —         | _       | 0000       |

| E020                        | PMADDR                          | 15:0          | CS2    | CS1          |       |       |           |        |        |        | ADDR       | <13.0> |      |       |        |           |           |         | 0000       |

|                             |                                 |               | ADDR15 | ADDR14       |       |       |           | -      |        |        |            |        |      |       |        |           |           |         | 0000       |

| E030                        | PMDOUT                          | 31:16         | _      | —            | —     | —     | _         | —      | —      | —      |            | —      | —    | —     | _      | —         | —         | _       | 0000       |

|                             |                                 | 15:0          |        |              |       |       |           |        |        | DATAOL | JT<15:0>   |        |      |       |        |           |           |         | 0000       |

| E040                        | PMDIN                           | 31:16<br>15:0 | —      | —            | _     | _     |           | _      | _      |        | -          | —      | _    | —     | —      | —         | —         | _       | 0000       |

|                             |                                 | 31:16         |        |              |       |       |           |        |        | DATAI  | l<15:0>    |        |      |       |        |           |           |         | 0000       |

| E050                        | PMAEN                           | 15:0          | -      | _            | —     | _     | _         | —      | _      |        |            | _      | —    | —     | —      |           | —         | _       |            |

|                             |                                 |               |        |              |       |       |           |        |        |        | <15:0>     |        |      |       |        |           |           |         | 0000       |

| E060                        | PMSTAT                          | 31:16<br>15:0 | IBF    | —<br>IBOV    | _     | _     | IB3F      | IB2F   | IB1F   | IB0F   |            |        |      | _     | OB3E   | —<br>OB2E | —<br>OB1E |         | 0000       |

|                             |                                 | 31:16         |        | <u>іво</u> у |       |       | івэг<br>— |        |        |        |            |        |      |       |        |           |           | <u></u> | 008F       |

| E070                        | PMWADDR                         | 51.10         | WCS2   | WCS1         |       |       |           |        | _      |        | _          |        |      |       |        |           | _         |         | 0000       |

| 2070                        |                                 | 15:0          |        | WADDR14      |       |       |           |        |        |        | WADDF      |        |      |       |        |           |           |         | 0000       |

|                             |                                 | 31:16         |        |              |       | _     |           | _      | _      | _      |            | <13:0> | _    | _     | _      | _         | _         | _       | 0000       |

| E090                        | PMRADDR                         | 51.10         | RCS2   | RCS1         |       |       |           |        |        |        |            |        |      |       |        |           | _         |         | 0000       |

| E080                        | FINIKADDR                       | 15:0          |        | RADDR14      |       |       |           |        |        |        | RADDF      |        |      |       |        |           |           |         | 0000       |

|                             |                                 | 31:16         | 31:16  |              |       | _     | _         |        |        |        |            | <13:0> |      | _     |        | _         |           | _       | 0000       |

| E090                        | PMRDIN                          |               |        |              |       | _     |           | _      |        |        |            | -      |      | _     |        |           | _         | _       | _          |

|                             |                                 | 15:0          | 15:0   |              |       |       |           |        |        | RL     | DATAIN<15: | 0>     |      |       |        |           |           |         | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                 | —                 | —                 | _                 | -                | —                |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        |                   | MONT              | H10<3:0>          |                   | MONTH01<3:0>      |                   |                  |                  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   | DAY               | 10<1:0>           |                   |                   | DAY01             | <3:0>            |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0          |                   |                   | _                 | _                 |                   | WDAY0             | 1<3:0>           |                  |  |

#### REGISTER 25-6: ALRMDATE: ALARM DATE VALUE REGISTER

# Legend:

| Legenu.           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

٦

| <b>TABLE 29-2:</b> | CAN2 REGISTER SUMMARY FOR PIC32MZXXXECF AND PIC32MZXXXECH DEVICES (CONTINUED) |

|--------------------|-------------------------------------------------------------------------------|

|--------------------|-------------------------------------------------------------------------------|

| ess                         |                                 | 6             |         |                                                                 |        |       |       |            |          | Bit       | S                   |        |         | -     |          |                 |          |                |            |

|-----------------------------|---------------------------------|---------------|---------|-----------------------------------------------------------------|--------|-------|-------|------------|----------|-----------|---------------------|--------|---------|-------|----------|-----------------|----------|----------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14                                                           | 29/13  | 28/12 | 27/11 | 26/10      | 25/9     | 24/8      | 23/7                | 22/6   | 21/5    | 20/4  | 19/3     | 18/2            | 17/1     | 16/0           | All Resets |

| 1100                        | C2FLTCON4                       | 31:16         | FLTEN19 | MSEL1                                                           | 9<1:0> |       |       | FSEL19<4:0 | >        |           | FLTEN18             | MSEL1  | 18<1:0> |       | F        | SEL18<4:0       | >        |                | 0000       |

| 1100                        | 021 210014                      | 15:0          | FLTEN17 | MSEL1                                                           | 7<1:0> |       |       | FSEL17<4:0 | >        |           | FLTEN16             | MSEL1  | 16<1:0> |       |          | FSEL16<4:0      | ):       |                | 0000       |

| 1110                        | C2FLTCON5                       | 31:16         | FLTEN23 | MSEL2                                                           |        |       |       | FSEL23<4:0 |          |           | FLTEN22             | -      | 22<1:0> |       |          | SEL22<4:0       |          |                | 0000       |

|                             | 02. 2. 00.10                    | 15:0          | FLTEN21 | MSEL2                                                           | -      |       |       | FSEL21<4:0 |          |           | FLTEN20             | -      | 20<1:0> |       |          | SEL20<4:0       |          |                | 0000       |

| 1120                        | C2FLTCON6                       | 31:16         | FLTEN27 | EN27 MSEL27<1:0> FSEL27<4:0> FLTEN26 MSEL26<1:0> FSEL26<4:0> 00 |        |       |       |            |          |           |                     |        |         | 0000  |          |                 |          |                |            |

|                             |                                 | 15:0          | FLTEN25 |                                                                 |        |       |       |            |          |           |                     |        |         | 0000  |          |                 |          |                |            |

| 1130                        | C2FLTCON7                       | 31:16         |         | MSEL3                                                           |        |       |       | FSEL31<4:0 |          |           | FLTEN30             | MSEL3  |         |       |          | SEL30<4:0       |          |                | 0000       |

|                             |                                 | 15:0          | FLTEN29 | MSEL2                                                           | 9<1:0> |       |       | FSEL29<4:0 | >        |           | FLTEN28             | MSEL2  | 28<1:0> |       | 1        | SEL28<4:0:      | r        |                | 0000       |

| 1140-<br>1330               | C2RXFn<br>(n = 0-31)            | 31:16         |         |                                                                 |        |       |       | SID<10:0>  |          |           | <b>F</b> • <b>O</b> |        |         |       | EXID     |                 | EID<1    | 7:16>          | XXXX       |

| 1000                        |                                 | 15:0<br>31:16 |         | EID<15:0> xxxx 0000                                             |        |       |       |            |          |           |                     |        |         |       |          |                 |          |                |            |

| 1340                        | C2FIFOBA                        | 15:0          |         | C2FIFOBA<31:0>                                                  |        |       |       |            |          |           |                     |        | 0000    |       |          |                 |          |                |            |

|                             | C2FIFOCONn                      | 31:16         |         | _                                                               | _      | _     | _     | _          | _        | _         | _                   | _      | _       |       |          | FSIZE<4:0>      |          |                | 0000       |

| 1350                        | (n = 0)                         | 15:0          |         | FRESET                                                          | UINC   | DONLY | _     | _          | _        | _         | TXEN                | TXABAT | TXLARB  | TXERR | TXREQ    | RTREN           | TXPR     | l<1:0>         | 0000       |

|                             | C2FIFOINTn                      | 31:16         | _       | _                                                               | _      | _     | _     | TXNFULLIE  | TXHALFIE | TXEMPTYIE | _                   | _      | _       | —     | RXOVFLIE | RXFULLIE        | RXHALFIE | RXN<br>EMPTYIE | 0000       |

| 1360                        | (n = 0)                         | 15:0          | _       | _                                                               | _      | _     | _     | TXNFULLIF  | TXHALFIF | TXEMPTYIF | _                   | _      | _       | _     | RXOVFLIF | RXFULLIF        | RXHALFIF | RXN<br>EMPTYIF | 0000       |

| 1370                        | C2FIFOUAn<br>(n = 0)            | 31:16<br>15:0 |         |                                                                 |        |       |       |            |          | C2FIFOU   | A<31:0>             |        |         |       |          |                 |          |                | 0000       |

|                             | . ,                             | 31:16         | _       | _                                                               | _      | _     | _     | _          | _        | _         | _                   | _      | _       |       | _        |                 | _        | _              | 0000       |

| 1380                        | C2FIFOCIn<br>(n = 0)            | 15:0          |         |                                                                 |        |       |       | _          |          |           |                     |        | _       |       |          | <br>2FIFOCI<4:( | 0>       |                | 0000       |

|                             | . ,                             | 31:16         | _       |                                                                 | _      | _     | _     | _          | _        | _         | _                   | _      | _       |       |          | FSIZE<4:0>      |          |                | 0000       |

|                             |                                 | 15:0          | _       | FRESET                                                          | UINC   | DONLY | _     | _          | _        | _         | TXEN                | TXABAT | TXLARB  | TXERR | TXREQ    | RTREN           | TXPR     | l<1:0>         | 0000       |

|                             | C2FIFOCONn                      | 31:16         | _       | _                                                               | —      | _     | _     | TXNFULLIE  | TXHALFIE | TXEMPTYIE | _                   | —      | _       | _     | RXOVFLIE | RXFULLIE        | RXHALFIE | RXN<br>EMPTYIE | 0000       |

| 1390-<br>1B40               | C2FIFOINTn<br>C2FIFOUAn         | 15:0          | -       | _                                                               | -      | -     |       | TXNFULLIF  | TXHALFIF | TXEMPTYIF | -                   | _      | —       | _     | RXOVFLIF | RXFULLIF        | RXHALFIF | RXN<br>EMPTYIF | 0000       |

|                             | C2FIFOCIn<br>(n = 1-31)         | 31:16         |         |                                                                 |        |       |       |            |          | C2FIFOU   | ۵~31.0>             |        |         |       |          |                 |          |                | 0000       |

|                             | ,                               | 15:0          |         |                                                                 |        |       |       |            |          | 021 11 00 |                     |        |         |       |          |                 |          |                | 0000       |

|                             |                                 | 31:16         | _       | —                                                               | _      | _     | _     | _          | —        | —         | _                   | —      | —       | _     | —        | —               | —        | —              | 0000       |

|                             |                                 | 15:0          |         | C2FIFOCI<4:0> 0000                                              |        |       |       |            |          |           |                     |        |         |       |          |                 |          |                |            |

Legend: Note 1:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

# REGISTER 30-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER (CONTINUED)

- bit 6 **TXBUSY:** Transmit Busy bit<sup>(2,6)</sup>

- 1 = TX logic is receiving data

0 = TX logic is idle

This bit indicates that a packet is currently being transmitted. A change in this status bit is not necessarily reflected by the TXDONE interrupt, as TX packets may be aborted or rejected by the MAC.

bit 5 **RXBUSY:** Receive Busy bit<sup>(3,6)</sup>

1 = RX logic is receiving data 0 = RX logic is idle

This bit indicates that a packet is currently being received. A change in this status bit is not necessarily reflected by the RXDONE interrupt, as RX packets may be aborted or rejected by the RX filter.

- bit 4-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for RX operations.

- **2:** This bit is only affected by TX operations.

- **3:** This bit is only affected by RX operations.

- 4: This bit is affected by TX and RX operations.

- **5:** This bit will be set when the ON bit (ETHCON1<15>) = 1.

- 6: This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   | -                 | —                 |                   | -                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | _                 | —                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 |                   | —                 | —                 | -                 | —                | —                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | CVROE             | CVRR              | CVRSS             |                   | CVR<              | <3:0>            |                  |

# REGISTER 32-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| DIL 31-10 | ommplemented. Read as 0                                                                                                              |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> Comparator Voltage Reference On bit<br>1 = Module is enabled                                                              |

|           | Setting this bit does not affect other bits in the register.                                                                         |

|           | 0 = Module is disabled and does not consume current.                                                                                 |

|           | Clearing this bit does not affect the other bits in the register.                                                                    |

| bit 14-7  | Unimplemented: Read as '0'                                                                                                           |

| bit 6     | CVROE: CVREFOUT Enable bit                                                                                                           |

|           | 1 = Voltage level is output on CVREFOUT pin                                                                                          |

|           | 0 = Voltage level is disconnected from CVREFOUT pin                                                                                  |

| bit 5     | CVRR: CVREF Range Selection bit                                                                                                      |

|           | 1 = 0 to 0.67 CVRSRC, with CVRSRC/24 step size                                                                                       |

|           | 0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size                                                                             |

| bit 4     | CVRSS: CVREF Source Selection bit                                                                                                    |

|           | 1 = Comparator voltage reference source, CVRSRC = (VREF+) - (VREF-)<br>0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS |

| bit 3-0   | <b>CVR&lt;3:0&gt;:</b> CVREF Value Selection $0 \le CVR<3:0> \le 15$ bits                                                            |

|           | When CVRR = 1:                                                                                                                       |

|           | $CVREF = (CVR < 3:0 > /24) \bullet (CVRSRC)$                                                                                         |

|           | When CVRR = 0:                                                                                                                       |

|           | $CVREF = 1/4 \bullet (CVRSRC) + (CVR < 3:0 > /32) \bullet (CVRSRC)$                                                                  |

|           |                                                                                                                                      |

# 33.3.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32MZ EF devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- Configuration bit select lock

#### 33.3.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 42.** "**Oscillators with Enhanced PLL**" (DS60001250) in the "*PIC32 Family Reference Manual*" for details.

#### 33.3.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PMDL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|------------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 24.24        | r-x                    | R/P               | r-1               | r-1               | r-1               | r-1                   | r-1              | r-1              |

| 31:24        | —                      | EJTAGBEN          | —                 | —                 | —                 | —                     | —                | —                |

| 00.40        | r-1                    | r-1               | R/P               | R/P               | R/P               | R/P                   | R/P              | R/P              |

| 23:16        | —                      | —                 | POSCBOOST POSCO   |                   | \IN<1:0>          | SOSCBOOST             | SOSCG            | AIN<1:0>         |

| 45.0         | R/P                    | R/P               | R/P               | R/P               | r-y               | R/P                   | R/P              | R/P              |

| 15:8         | 15:8 SMCLR DBGPER<2:0> |                   | —                 | FSLEEP            | FECCCO            | ON<1:0>               |                  |                  |

| 7.0          | r-1                    | R/P               | R/P               | R/P               | R/P               | R/P                   | R/P              | R/P              |

| 7:0          |                        | BOOTISA           | TRCEN             | ICESE             | L<1:0>            | JTAGEN <sup>(1)</sup> | DEBU             | G<1:0>           |

#### REGISTER 34-3: DEVCFG0/ADEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit     | y = Value set from Configu | ration bits on POR |

|-------------------|----------------------|----------------------------|--------------------|

| R = Readable bit  | P = Programmable bit | U = Unimplemented bit, re  | ad as '0'          |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | x = Bit is unknown |

bit 31 Reserved: The reset value of this bit is the same as DEVSIGN0<31>.

- bit 30 EJTAGBEN: EJTAG Boot Enable bit

- 1 = Normal EJTAG functionality

- 0 = Reduced EJTAG functionality

- bit 29-22 Reserved: Write as '1'

- bit 21 POSCBOOST: Primary Oscillator Boost Kick Start Enable bit

- 1 = Boost the kick start of the oscillator

- 0 = Normal start of the oscillator

- bit 20-19 POSCGAIN<1:0>: Primary Oscillator Gain Control bits

- 11 = Gain Level 3 (highest)

- 10 = Gain Level 2

- 01 = Gain Level 1

- 00 = Gain Level 0 (lowest)

- bit 18 SOSCBOOST: Secondary Oscillator Boost Kick Start Enable bit

- 1 = Boost the kick start of the oscillator

- 0 = Normal start of the oscillator

- bit 17-16 SOSCGAIN<1:0>: Secondary Oscillator Gain Control bits

- 11 = Gain Level 3 (highest)

- 10 = Gain Level 2

- 01 = Gain Level 1

- 00 = Gain Level 0 (lowest)

- bit 15 SMCLR: Soft Master Clear Enable bit

#### $1 = \overline{MCLR}$ pin generates a normal system Reset

- 0 = MCLR pin generates a POR Reset

- bit 14-12 DBGPER<2:0>: Debug Mode CPU Access Permission bits

- 1xx = Allow CPU access to Permission Group 2 permission regions

- x1x = Allow CPU access to Permission Group 1 permission regions

- xx1 = Allow CPU access to Permission Group 0 permission regions

- 0xx = Deny CPU access to Permission Group 2 permission regions

- ${\rm x}0{\rm x}$  = Deny CPU access to Permission Group 1 permission regions

- xx0 = Deny CPU access to Permission Group 0 permission regions

When the CPU is in Debug mode and the CPU1PG<1:0> bits (CFGPG<1:0>) are set to a denied permission group as defined by DBGPER<2:0>, the transaction request is assigned Group 3 permissions.

- bit 11 **Reserved:** This bit is controlled by debugger/emulator development tools and should not be modified by the user.

- Note 1: This bit sets the value of the JTAGEN bit in the CFGCON register.

|               |                                |                                         | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3): 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |         |       |       |                                                                                            |

|---------------|--------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|--------------------------------------------------------------------------------------------|

| Param.<br>No. | Symbol Characteristics Min. IV |                                         |                                                                                                                                                                                                                                                                                                  | Typical | Max.  | Units | Comments                                                                                   |

| D300          | VIOFF                          | Input Offset Voltage                    | _                                                                                                                                                                                                                                                                                                | ±10     |       | mV    | AVDD = VDD, AVSS = VSS                                                                     |

| D301          | VICM                           | Input Common Mode Voltage               | 0                                                                                                                                                                                                                                                                                                | —       | Vdd   | V     | AVDD = VDD, AVSS = VSS<br>(Note 2)                                                         |

| D302          | CMRR                           | Common Mode Rejection<br>Ratio          | 55                                                                                                                                                                                                                                                                                               | —       |       | dB    | Max VICM = (VDD - 1)V<br>(Note 2, 4)                                                       |

| D303          | TRESP                          | Response Time                           |                                                                                                                                                                                                                                                                                                  | 150     |       | ns    | AVDD = VDD, AVSS = VSS<br>(Notes 1, 2)                                                     |

| D304          | ON2ov                          | Comparator Enabled to Out-<br>put Valid | —                                                                                                                                                                                                                                                                                                | —       | 10    | μs    | Comparator module is<br>configured before setting the<br>comparator ON bit <b>(Note 2)</b> |

| D305          | IVref                          | Internal Voltage Reference              | 1.194                                                                                                                                                                                                                                                                                            | 1.2     | 1.206 | V     | —                                                                                          |

#### TABLE 37-14: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

- 2: These parameters are characterized but not tested.

- **3:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is guaranteed, but not characterized.

- 4: CMRR measurement characterized with a 1 MΩ resistor in parallel with a 25 pF capacitor to Vss.

| DC CHARACTERISTICS                   |         |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3): 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |                    |       |                                                                 |  |

|--------------------------------------|---------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|

| Param.<br>No. Symbol Characteristics |         |                                                             | Min.                                                                                                                                                                                                                                                                                             | Тур. | Max.               | Units | Comments                                                        |  |

| D312                                 | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                                                                                                                                                                                                                                                                |      | 10                 | μs    | See Note 1                                                      |  |

| D313 DACREFH                         | DACREFH | CVREF Input Voltage<br>Reference Range                      | AVss                                                                                                                                                                                                                                                                                             | _    | AVdd               | V     | CVRSRC with CVRSS = 0                                           |  |

|                                      |         |                                                             | VREF-                                                                                                                                                                                                                                                                                            |      | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |

| D314                                 | DVREF   | CVREF Programmable<br>Output Range                          | 0                                                                                                                                                                                                                                                                                                |      | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |

|                                      |         |                                                             | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                                |      | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/32<br>step size |  |

| D315                                 | DACRES  | CRES Resolution                                             | —                                                                                                                                                                                                                                                                                                |      | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                        |  |

|                                      |         |                                                             |                                                                                                                                                                                                                                                                                                  |      | DACREFH/32         |       | CVRCON <cvrr> = 0</cvrr>                                        |  |

| D316                                 | DACACC  | Absolute Accuracy <sup>(2)</sup>                            | —                                                                                                                                                                                                                                                                                                | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |

|                                      |         |                                                             | —                                                                                                                                                                                                                                                                                                | _    | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

2: These parameters are characterized but not tested.

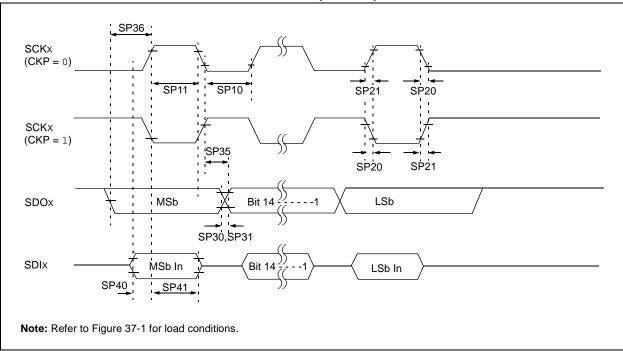

FIGURE 37-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

|                 | I TPBCLK2 I TPBCLK2                          | TPBCLK2        | TPBCLK2 | TPBCLK2 | TPBCLK2         | TPBCLK2  | TPBCLK2  |

|-----------------|----------------------------------------------|----------------|---------|---------|-----------------|----------|----------|

| PBCLK2          |                                              | <br>_//        | ا<br>ہ  | <br>//  |                 | /        |          |

| PMA <x:0></x:0> | <u>                                     </u> | ↓↓<br>         | Address |         |                 |          |          |

|                 |                                              | ⊢ PM2 + PM3    | ·       |         |                 |          | <b> </b> |

| PMD <x:0></x:0> |                                              | Address<7:0>   | >¥      | /<br>\  | Data            | /        |          |

|                 |                                              |                | י<br>ל  | ✓ PM    | 112             | < PM13-► |          |

| PMRD_           |                                              | <b>↓</b>       |         | I       |                 |          |          |

| PMWR _          |                                              | <br>           | ا<br>ا  | ·<br>/  | <u>←</u> PM11-► |          | , I<br>  |

|                 | I I                                          | <b>←</b> PM1 → | ļ       | I       | I               |          |          |

| PMALL/PMALH     |                                              | <u> </u>       |         |         |                 |          |          |

|                 |                                              |                |         |         |                 |          |          |

| PMCSx           | I I/                                         | <u>}</u> }-    |         |         |                 |          |          |

|                 |                                              |                |         |         |                 |          |          |

|                 |                                              |                | •       | •       |                 |          | ·        |

#### FIGURE 37-23: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

# TABLE 37-44: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |           |      |       |            |  |

|--------------------|---------|---------------------------------------------------------------------------|-------------------------------------------------------|-----------|------|-------|------------|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.                                                  | Тур.      | Max. | Units | Conditions |  |

| PM11               | Twr     | PMWR Pulse Width                                                          |                                                       | 1 TPBCLK2 | —    | —     | —          |  |

| PM12               | TDVSU   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) |                                                       | 2 TPBCLK2 | —    | —     | _          |  |

| PM13               | Tdvhold | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             |                                                       | 1 TPBCLK2 | —    | _     | —          |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

#### TABLE 39-3: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACTE                                                    | ERISTICS               |                        | Standard Operating Conditions: 2.1V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |            |  |  |  |  |

|----------------------------------------------------------------|------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Maximum <sup>(4)</sup> | Units                                                                                                                                               | Conditions |  |  |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |                        |                                                                                                                                                     |            |  |  |  |  |

| MDC35                                                          | 41                     | 60                     | mA 252 MHz                                                                                                                                          |            |  |  |  |  |

|                                                                |                        |                        |                                                                                                                                                     |            |  |  |  |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC+PLL with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBPMD = 1), VUSB3V3 is connected to Vss, PBCLKx divisor = 1:128 (' $x' \neq 7$ )

- CPU is in Idle mode (CPU core Halted)

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared (except USBPMD)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: Data in the "Maximum" column is at 3.3V, +85°C at specified operating frequency, unless otherwise stated. Parameters are for design guidance only and are not tested.

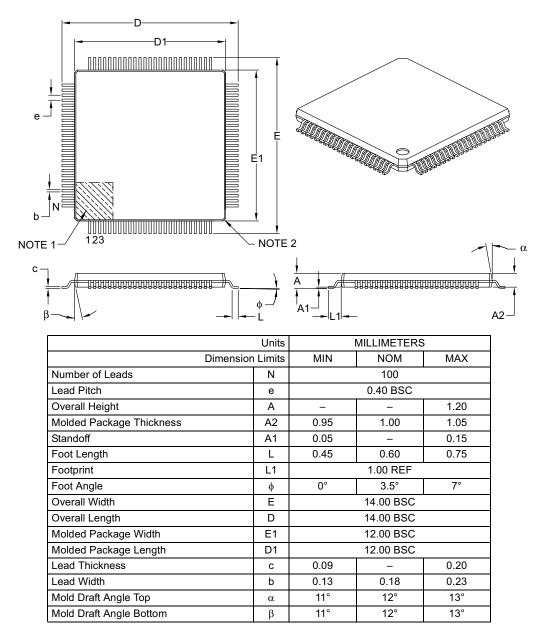

# 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

# A.2 Analog-to-Digital Converter (ADC)

The PIC32MZ EF family of devices has a new 12-bit High-Speed Successive Approximation Register (SAR) ADC module that replaces the 10-bit ADC module in PIC32MX5XX/6XX/7XX devices; therefore, the use of **Bold** type to show differences is *not* used in the following table. Note that not all register differences are described in this section; however, the key feature differences are listed in Table A-3.

# TABLE A-3:ADC DIFFERENCES

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                             | PIC32MZ EF Feature                                                                                                                                                                                                 |  |  |  |  |  |  |