Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | MIPS32 <sup>®</sup> M-Class                                                          |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 252MHz                                                                               |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                         |

| Number of I/O              | 120                                                                                  |

| Program Memory Size        | 2MB (2M x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 512K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                          |

| Data Converters            | A/D 48x12b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LQFP                                                                             |

| Supplier Device Package    | 144-LQFP (20x20)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efh144t-250i-pl |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                   |                        | Pin Nu          | mber                    |     |             |                |                              |

|-------------------|------------------------|-----------------|-------------------------|-----|-------------|----------------|------------------------------|

| Pin Name          | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA<br>LQFP |     | Pin<br>Type | Buffer<br>Type | Description                  |

|                   |                        |                 |                         |     | Output      | Compare        |                              |

| OC1               | PPS                    | PPS             | PPS                     | PPS | 0           | _              | Output Compare Outputs 1-9   |

| OC2               | PPS                    | PPS             | PPS                     | PPS | 0           | —              |                              |

| OC3               | PPS                    | PPS             | PPS                     | PPS | 0           | _              | 1                            |

| OC4               | PPS                    | PPS             | PPS                     | PPS | 0           | _              | 1                            |

| OC5               | PPS                    | PPS             | PPS                     | PPS | 0           | _              | 1                            |

| OC6               | PPS                    | PPS             | PPS                     | PPS | 0           | _              | 1                            |

| OC7               | PPS                    | PPS             | PPS                     | PPS | 0           | _              | 1                            |

| OC8               | PPS                    | PPS             | PPS                     | PPS | 0           | _              | 1                            |

| OC9               | PPS                    | PPS             | PPS                     | PPS | 0           | _              | 1                            |

| OCFA              | PPS                    | PPS             | PPS                     | PPS | I           | ST             | Output Compare Fault A Input |

| DCFB 30 44 B24 62 |                        |                 |                         | 62  | I           | ST             | Output Compare Fault B Input |

| Legend:           | CMOS = CI<br>ST = Schm |                 | •                       | •   | _           | Analog =       | Analog input P = Power       |

#### TABLE 1-4: OC1 THROUGH OC9 PINOUT I/O DESCRIPTIONS

d: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

| Analog = Analog input       | P = Power |

|-----------------------------|-----------|

| O = Output                  | I = Input |

| PPS = Peripheral Pin Select |           |

|                             |           |

#### TABLE 1-5: EXTERNAL INTERRUPTS PINOUT I/O DESCRIPTIONS

|                                          |                        | Pin Nu          | mber            |                          |             |                |                        |  |  |  |  |  |

|------------------------------------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|------------------------|--|--|--|--|--|

| INTO 46<br>INT1 PP<br>INT2 PP<br>INT3 PP | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description            |  |  |  |  |  |

|                                          |                        |                 |                 |                          | External    | Interrupts     |                        |  |  |  |  |  |

| INT0                                     | 46                     | 71              | A48             | 104                      | Ι           | ST             | External Interrupt 0   |  |  |  |  |  |

| INT1                                     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | External Interrupt 1   |  |  |  |  |  |

| INT2                                     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | External Interrupt 2   |  |  |  |  |  |

| INT3                                     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | External Interrupt 3   |  |  |  |  |  |

| INT4                                     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | External Interrupt 4   |  |  |  |  |  |

| Legend:                                  | CMOS = CI              | MOS-comp        | atible input    | or output                | •           | Analog =       | Analog input P = Power |  |  |  |  |  |

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog inputP = PowerO = OutputI = InputPPS = Peripheral Pin Select

#### TABLE 4-20: SYSTEM BUS TARGET 12 REGISTER MAP

|                             |                  |           |       | 000   |       |         |          |       |       |      |                       |       |        |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|---------|----------|-------|-------|------|-----------------------|-------|--------|------|--------|--------|---------|--------|---------------|

| ess                         |                  | 6         |       |       |       |         |          |       |       |      | Bits                  |       |        |      |        |        |         |        |               |

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11    | 26/10 | 25/9  | 24/8 | 23/7                  | 22/6  | 21/5   | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

|                             |                  | 31:16     | MULTI |       | —     |         |          | CODE  | <3:0> |      | —                     | _     |        |      | —      | —      | —       |        | 0000          |

| B020                        | SBT12ELOG1       | 15:0      |       |       |       | INI     | ΓID<7:0> |       |       |      |                       | REGIO | N<3:0> |      | —      | C      | MD<2:0> |        | 0000          |

| D004                        | SBT12ELOG2       | 31:16     | —     | _     | _     | _       | _        | _     | _     | _    | -                     | _     | _      | _    | _      | _      | _       | _      | 0000          |

| D024                        | 3BTT2ELOG2       | 15:0      |       | —     | _     |         | —        |       | —     |      | _                     |       |        |      | —      | _      | GROU    | P<1:0> | 0000          |

| B028                        | SBT12ECON        | 31:16     |       | -     | —     | _       | —        |       | —     | ERRP | _                     | _     |        |      | —      | —      | _       |        | 0000          |

| DU20                        | SBITZECON        | 15:0      |       | —     | _     |         | —        |       | —     |      | _                     |       |        |      | —      | _      | _       |        | 0000          |

| P020                        | SBT12ECLRS       | 31:16     |       | —     | _     |         | —        |       | —     |      | _                     |       |        |      | —      | _      | _       |        | 0000          |

| B030                        | SBI IZECLKS      | 15:0      |       | —     | _     |         | —        |       | —     |      | _                     |       |        |      | —      | _      | _       | CLEAR  | 0000          |

| D020                        | SBT12ECLRM       | 31:16     |       | —     | _     |         | —        |       | —     |      | _                     |       |        |      | —      | _      | _       |        | 0000          |

| B030                        | 3BT 12ECLRIVI    | 15:0      |       | —     | _     |         | —        |       | —     |      | _                     |       |        |      | —      | _      | _       | CLEAR  | 0000          |

| B040                        | SBT12REG0        | 31:16     |       |       |       |         |          |       |       | BA   | SE<21:6>              |       |        |      |        |        |         |        | xxxx          |

| D040                        | SBITZREGU        | 15:0      |       |       | BA    | SE<5:0> |          |       | PRI   |      | SE<21:6><br>SIZE<4:0> |       |        | >    |        | —      | _       |        | xxxx          |

| B050                        | SBT12RD0         | 31:16     |       | —     | _     |         | —        |       | —     |      | _                     |       |        |      | —      | _      | _       |        | xxxx          |

| 6050                        | 3BT12RD0         | 15:0      |       |       | —     |         | _        |       | _     |      | _                     |       |        |      | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| B058                        | SBT12WR0         | 31:16     |       |       | —     |         | _        |       | _     |      | _                     |       |        |      | —      | -      | _       |        | xxxx          |

| 6056                        | 36TT2WR0         | 15:0      |       |       | -     |         | _        | -     | —     |      | _                     |       | _      | -    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

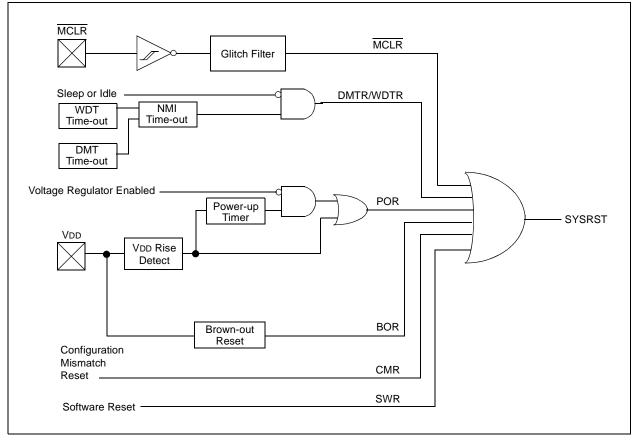

#### 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7**. "**Resets**" (DS60001118) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The device Reset sources are as follows:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

- Deadman Timer Reset (DMTR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

#### FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | —                 | —                 | —                 |                   | IP3<2:0>          |                   | IS3<1:0>         |                  |  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | _                 | —                 | _                 |                   | IP2<2:0>          |                   | IS2<             | :1:0>            |  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.0         | _                 | —                 | _                 |                   | IP1<2:0>          |                   | IS1<             | :1:0>            |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | _                 | —                 | _                 |                   | IP0<2:0>          |                   | IS0<             | :1:0>            |  |  |

#### REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: Interrupt Priority bits                                  |

|-----------|--------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 25-24 | IS3<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1                                    |

|           | 00 = Interrupt subpriority is 0                                    |

| bit 23-21 |                                                                    |

| bit 20-18 | IP2<2:0>: Interrupt Priority bits                                  |

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 17-16 | IS2<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1<br>00 = Interrupt subpriority is 0 |

| hit 15-13 | Unimplemented: Read as '0'                                         |

| 5115-15   | ommplemented. Read as 0                                            |

| Note:     | This register represents a generic defi                            |

|           |                                                                    |

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-2 for the exact bit definitions.

| Bit<br>Range   | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24          |                   | —                 | _                 | —                 |                   | —                 | —                | —                |

| 22.10          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24<br>23:16 |                   | —                 |                   |                   |                   |                   |                  | —                |

| 45.0           | R/W-1             | U-0               | U-0               | U-0               | R-1               | U-0               | U-0              | U-0              |

| 15:8           | 0N <sup>(1)</sup> | —                 | _                 | _                 | PBDIVRDY          | _                 | _                | _                |

| 7.0            | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0            |                   |                   |                   |                   | PBDIV<6:0>        |                   |                  |                  |

#### **REGISTER 8-6: PBxDIV: PERIPHERAL BUS 'x' CLOCK DIVISOR CONTROL REGISTER ('x' = 1-7)**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Peripheral Bus 'x' Output Clock Enable bit<sup>(1)</sup> 1 = Output clock is enabled 0 = Output clock is disabled

#### bit 14-12 Unimplemented: Read as '0'

### bit 11 **PBDIVRDY:** Peripheral Bus 'x' Clock Divisor Ready bit

- 1 = Clock divisor logic is not switching divisors and the PBxDIV<6:0> bits may be written

- 0 = Clock divisor logic is currently switching values and the PBxDIV<6:0> bits cannot be written

#### bit 10-7 Unimplemented: Read as '0'

- bit 6-0 **PBDIV<6:0>:** Peripheral Bus 'x' Clock Divisor Control bits

- 1111111 = PBCLKx is SYSCLK divided by 128

- 1111110 = PBCLKx is SYSCLK divided by 127

- • • 0000011 = PBCLKx is SYSCLK divided by 4

- 0000010 = PBCLKx is SYSCLK divided by 3

- 0000001 = PBCLKx is SYSCLK divided by 2 (default value for  $x \neq 7$ )

- 0000000 = PBCLKx is SYSCLK divided by 1 (default value for x = 7)

- **Note 1:** The clock for peripheral bus 1 cannot be turned off. Therefore, the ON bit in the PB1DIV register cannot be written as a '0'.

Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

#### TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

|                             |                  | 1             |                                                                                                                                                                                                                                                                                                           |                      |       | . (   |       | -,          |               |               | Bits                      |            |              |             |             |             |             |             |            |

|-----------------------------|------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|-------|-------|-------------|---------------|---------------|---------------------------|------------|--------------|-------------|-------------|-------------|-------------|-------------|------------|

| ess                         |                  |               |                                                                                                                                                                                                                                                                                                           | 1                    | 1     |       |       |             |               | 1             | DIIS                      |            | 1            | 1           | 1           | 1           | 1           | 1           |            |

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15                                                                                                                                                                                                                                                                                                     | 30/14                | 29/13 | 28/12 | 27/11 | 26/10       | 25/9          | 24/8          | 23/7                      | 22/6       | 21/5         | 20/4        | 19/3        | 18/2        | 17/1        | 16/0        | All Resets |

| 3170                        | USB<br>E7CSR0    | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             | Inde          | exed by the s | ame bits in U             | SBIE7CSR0  |              |             | •           |             |             |             | 0000       |

| 3174                        | USB<br>E7CSR1    | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             | Inde          | exed by the s | ame bits in U             | SBIE7CSR1  |              |             |             |             |             |             | 0000       |

| 3178                        | USB<br>E7CSR2    | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             | Inde          | exed by the s | ame bits in U             | SBIE7CSR2  |              |             |             |             |             |             | 0000       |

| 317C                        | USB<br>E7CSR3    | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             | Inde          | exed by the s | ame bits in U             | SBIE7CSR3  |              |             |             |             |             |             | 0000       |

| 3200                        | USB<br>DMAINT    | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           | -                    | -     |       |       | -           |               | -             | —<br>DMA8IF               | <br>DMA7IF | —<br>DMA6IF  | —<br>DMA5IF | —<br>DMA4IF | —<br>DMA3IF | —<br>DMA2IF | —<br>DMA1IF | 0000       |

| 3204                        | USB<br>DMA1C     | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           | _                    |       |       |       | —<br>DMABRS | —<br>STM<1:0> | <br>DMAERR    | —                         | —<br>DMA   | —<br>=P<3:0> | —           | —<br>DMAIE  | <br>DMAMODE | —<br>DMADIR | —<br>DMAEN  | 0000       |

| 3208                        | USB<br>DMA1A     | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           | DMAADDR<31:16> 00    |       |       |       |             |               |               |                           |            | 0000         |             |             |             |             |             |            |

| 320C                        | USB<br>DMA1N     | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           | DMACOUNT<31:16> 0000 |       |       |       |             |               |               |                           |            |              |             |             | 0000        |             |             |            |

|                             |                  | 31:16         | _                                                                                                                                                                                                                                                                                                         | _                    | _     | _     | _     |             |               | DIVIA         |                           | >          |              | _           |             |             |             | _           | 0000       |

| 3214                        | USB<br>DMA2C     | 15:0          | _                                                                                                                                                                                                                                                                                                         | _                    |       | _     |       | DMABRS      | <br>GTM<1:0>  | DMAERR        | _                         |            | EP<3:0>      |             | DMAIE       | DMAMODE     | DMADIR      | DMAEN       | 0000       |

| 3218                        | USB<br>DMA2A     | 31:16         |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             |               |               | ADDR<31:16                |            |              |             |             |             |             |             | 0000       |

|                             |                  | 15:0          |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             |               |               | ADDR<15:0>                |            |              |             |             |             |             |             | 0000       |

| 321C                        | USB<br>DMA2N     | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             |               |               | COUNT<31:16<br>COUNT<15:0 |            |              |             |             |             |             |             | 0000       |

| 0004                        | USB              | 31:16         | _                                                                                                                                                                                                                                                                                                         | -                    | _     | _     | _     | _           | _             | _             | _                         | _          | _            | -           | _           | -           | -           | _           | 0000       |

| 3224                        | DMA3C            | 15:0          | _                                                                                                                                                                                                                                                                                                         | _                    |       | _     |       | DMABRS      | STM<1:0>      | DMAERR        |                           | DMA        | EP<3:0>      | •           | DMAIE       | DMAMODE     | DMADIR      | DMAEN       | 0000       |

| 3228                        | USB              | 31:16         |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             |               |               | ADDR<31:16                |            |              |             |             |             |             |             | 0000       |

|                             | DMA3A            | 15:0          |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             |               |               | ADDR<15:0>                |            |              |             |             |             |             |             | 0000       |

| 322C                        | USB<br>DMA3N     | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             |               |               | COUNT<31:16<br>COUNT<15:0 |            |              |             |             |             |             |             | 0000       |

| 3234                        | USB              | 31:16         | _                                                                                                                                                                                                                                                                                                         | _                    | _     | _     | _     | _           | _             | _             | _                         |            | _            | _           | _           | _           | —           | _           | 0000       |

| 0204                        | DMA4C            | 15:0          | —                                                                                                                                                                                                                                                                                                         | _                    | —     | —     | —     | DMABRS      | STM<1:0>      | DMAERR        |                           |            | EP<3:0>      |             | DMAIE       | DMAMODE     | DMADIR      | DMAEN       | 0000       |

| 3238                        | USB<br>DMA4A     | 31:16         |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             |               |               |                           |            |              |             |             |             |             |             | 0000       |

|                             |                  | 15:0          |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             |               |               |                           |            |              |             |             |             |             |             | -          |

| 323C                        | USB<br>DMA4N     | 31:16<br>15:0 |                                                                                                                                                                                                                                                                                                           |                      |       |       |       |             |               |               |                           |            |              |             |             |             |             |             | -          |

|                             | USB              | 31:16         | _                                                                                                                                                                                                                                                                                                         | _                    | _     | _     | _     | _           | _             |               |                           |            | _            | _           | _           | _           | _           | _           | -          |

| 3244                        | DMA5C            | 15:0          | _                                                                                                                                                                                                                                                                                                         | _                    | _     | _     | _     |             | STM<1:0>      | DMAERR        |                           | DMA        | EP<3:0>      |             | DMAIE       | DMAMODE     | DMADIR      | DMAEN       | 0000       |

| Leger                       |                  | 1             | DMAADDR<15:0>       0000         DMACOUNT<31:16>       0000         DMACOUNT<15:0>       0000         OMACOUNT<15:0>       0000         OMACOUNT<15:0>       0000         OMACOUNT<15:0>       0000         OMACOUNT<15:0>       0000         OMACOUNT<15:0>       0000         OMACOUNT<15:0>       0000 |                      |       |       |       |             |               |               |                           |            |              |             |             |             |             |             |            |

Legend: Note x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Device mode.

1:

2: Host mode.

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7). 3: 4:

#### REGISTER 11-5: USBIE0CSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 0) (CONTINUED)

#### bit 21 SENDSTALL: Send Stall Control bit (Device mode)

- 1 = Terminate the current transaction and transmit a STALL handshake. This bit is automatically cleared.

- 0 = Do not send STALL handshake.

**REQPKT:** IN transaction Request Control bit (Host mode)

- 1 = Request an IN transaction. This bit is cleared when the RXPKTRDY bit is set.

- 0 = Do not request an IN transaction

- bit 20 SETUPEND: Early Control Transaction End Status bit (Device mode)

- 1 = A control transaction ended before the DATAEND bit has been set. An interrupt will be generated and the FIFO flushed at this time.

- 0 = Normal operation

This bit is cleared by writing a '1' to the SVCSETEND bit in this register.

#### ERROR: No Response Error Status bit (Host mode)

- 1 = Three attempts have been made to perform a transaction with no response from the peripheral. An interrupt is generated.

- 0 = Clear this flag. Software must write a '0' to this bit to clear it.

#### DATAEND: End of Data Control bit (Device mode)

The software sets this bit when:

bit 19

- Setting TXPKTRDY for the last data packet

- Clearing RXPKTRDY after unloading the last data packet

- Setting TXPKTRDY for a zero length data packet

Hardware clears this bit.

**SETUPPKT:** Send a SETUP token Control bit (*Host mode*)

- 1 = When set at the same time as the TXPKTRDY bit is set, the module sends a SETUP token instead of an OUT token for the transaction

- 0 = Normal OUT token operation

Setting this bit also clears the Data Toggle.

- bit 18 SENTSTALL: STALL sent status bit (Device mode)

- 1 = STALL handshake has been transmitted

- 0 = Software clear of bit

RXSTALL: STALL handshake received Status bit (Host mode)

- 1 = STALL handshake was received

- 0 = Software clear of bit

- bit 17 **TXPKTRDY:** TX Packet Ready Control bit

- 1 = Data packet has been loaded into the FIFO. It is cleared automatically.

- 0 = No data packet is ready for transmit

- bit 16 **RXPKTRDY:** RX Packet Ready Status bit

- 1 = Data packet has been received. Interrupt is generated (when enabled) when this bit is set.

- 0 = No data packet has been received

This bit is cleared by setting the SVCRPR bit.

bit 15-0 Unimplemented: Read as '0'

## REGISTER 11-29: USBLPMR2: USB LINK POWER MANAGEMENT CONTROL REGISTER 2 (CONTINUED)

bit 0 LPMSTIF: LPM STALL Interrupt Flag bit

#### When in Device mode:

- 1 = A LPM transaction was received and the USB Module responded with a STALL

- 0 = No Stall condition

#### When in Host mode:

- 1 = A LPM transaction was transmitted and the device responded with a STALL

- 0 = No Stall condition

#### TABLE 12-18: PORTH REGISTER MAP FOR 144-PIN DEVICES ONLY

| ess                         |                                 | e la |               |               |               |               |                |               |              | Bits         |              |              |              |              |              |              |              |              |     |

|-----------------------------|---------------------------------|------------------------------------------|---------------|---------------|---------------|---------------|----------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-----|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                | 31/15         | 30/14         | 29/13         | 28/12         | 27/11          | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | AII |

|                             | ANSELH                          | 31:16                                    | _             |               | _             | _             |                | —             | _            | _            |              | —            | —            | _            | —            | —            | _            | _            | 0   |

| 100                         | ANOLLII                         | 15:0                                     | —             | _             |               | —             | _              | —             | _            | _            | —            | ANSH6        | ANSH5        | ANSH4        | —            | —            | ANSH1        | ANSH0        | 0   |

| 710                         | TRISH                           | 31:16                                    | —             |               |               | —             |                | —             | —            | _            | —            | —            | —            | —            | —            | —            | —            | —            | 0   |

| // 10                       | -                               | 15:0                                     | TRISH15       | TRISH14       | TRISH13       | TRISH12       | TRISH11        | TRISH10       | TRISH9       | TRISH8       | TRISH7       | TRISH6       | TRISH5       | TRISH4       | TRISH3       | TRISH2       | TRISH1       | TRISH0       | F   |

| 720                         | PORTH                           | 31:16                                    | —             | —             | —             | —             | —              | —             |              | —            | —            | —            | —            | —            | —            | —            | —            | —            | 0   |

|                             | -                               | 15:0                                     | RH15          | RH14          | RH13          | RH12          | RH11           | RH10          | RH9          | RH8          | RH7          | RH6          | RH5          | RH4          | RH3          | RH2          | RH1          | RH0          | х   |

| 730                         | LATH                            | 31:16                                    | _             | -             | —             | —             | _              | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | 0   |

|                             |                                 | 15:0                                     | LATH15        | LATH14        | LATH13        | LATH12        | LATH11         | LATH10        | LATH9        | LATH8        | LATH7        | LATH6        | LATH5        | LATH4        | LATH3        | LATH2        | LATH1        | LATH0        | X   |

| 740                         | 0 ODCH 15                       | 31:16                                    | _             | -             | —             | —             | _              | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | (   |

|                             |                                 | 15:0                                     | ODCH15        | ODCH14        | ODCH13        | ODCH12        | ODCH11         | ODCH10        | ODCH9        | ODCH8        | ODCH7        | ODCH6        | ODCH5        | ODCH4        | ODCH3        | ODCH2        | ODCH1        | ODCH0        | (   |

| 750                         | CNPUH                           | 31:16                                    | _             | -             | —             | —             | _              | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | C   |

|                             | 0.11 0.11                       | 15:0                                     | CNPUH15       | CNPUH14       | CNPUH13       | CNPUH12       | CNPUH11        | CNPUH10       | CNPUH9       | CNPUH8       | CNPUH7       | CNPUH6       | CNPUH5       | CNPUH4       | CNPUH3       | CNPUH2       | CNPUH1       | CNPUH0       | ) ( |

| 760                         | CNPDH                           | 31:16                                    | _             | -             | —             | —             | _              | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | —            | (   |

|                             | -                               | 15:0                                     | CNPDH15       | CNPDH14       | CNPDH13       | CNPDH12       | CNPDH11        | CNPDH10       | CNPDH9       | CNPDH8       | CNPDH7       | CNPDH6       | CNPDH5       | CNPDH4       | CNPDH3       | CNPDH2       | CNPDH1       | CNPDH0       | ) ( |

|                             |                                 | 31:16                                    | _             | -             | —             | —             | _              | —             | —            | _            | —            | —            | —            | —            | —            | —            | —            | —            | (   |

| 0770                        | CNCONH                          | 15:0                                     | ON            | —             | —             | —             | EDGE<br>DETECT | —             | —            | —            | -            | —            | -            | —            | —            | —            | —            | —            | C   |

| 780                         | CNENH                           | 31:16                                    | _             | _             | _             | _             | _              | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | (   |

| 180                         |                                 | 15:0                                     | CNENH15       | CNENH14       | CNENH13       | CNENH12       | CNENH11        | CNENH10       | CNENH9       | CNENH8       | CNENH7       | CNENH6       | CNENH5       | CNENH4       | CNENH3       | CNENH2       | CNENH1       | CNENH0       | ) ( |

|                             |                                 | 31:16                                    | -             | —             | _             | —             | _              | _             | _            | _            | _            | —            | —            | _            | _            | _            | _            | _            | (   |

| 0790                        | CNSTATH                         | 15:0                                     | CN<br>STATH15 | CN<br>STATH14 | CN<br>STATH13 | CN<br>STATH12 | CN<br>STATH11  | CN<br>STATH10 | CN<br>STATH9 | CN<br>STATH8 | CN<br>STATH7 | CN<br>STATH6 | CN<br>STATH5 | CN<br>STATH4 | CN<br>STATH3 | CN<br>STATH2 | CN<br>STATH1 | CN<br>STATH0 | (   |

| 740                         | 0111511                         | 31:16                                    | _             | _             | —             | _             | _              | —             | —            | _            | _            | —            | —            | —            | —            | —            | _            | —            | (   |

| 7A0                         | CNNEH                           | 15:0                                     | CNNEH15       | CNNEH14       | CNNEH13       | CNNEH12       | CNNEH11        | CNNEH10       | CNNEH9       | CNNEH8       | CNNEH7       | CNNEH6       | CNNEH5       | CNNEH4       | CNNEH3       | CNNEH2       | CNNEH1       | CNNEH0       | ) ( |

| 700                         |                                 | 31:16                                    | _             | —             | —             | —             | —              | _             | _            | _            | _            | —            | —            | —            | —            | —            | —            | _            | 1   |

| 7B0                         | CNFH                            | 15:0                                     | CNFH15        | CNFH14        | CNFH13        | CNFH12        | CNFH11         | CNFH10        | CNFH9        | CNFH8        | CNFH7        | CNFH6        | CNFH5        | CNFH4        | CNFH3        | CNFH2        | CNFH1        | CNFH0        | (   |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|           | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 00.10     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 7.0       | R-0, HC, HS       | R-0, HC, HS       | R-0, HC, HS       | U-0               | U-0               | U-0               | U-0              | R-0, HC, HS      |

| 7:0       | BAD1              | BAD2              | DMTEVENT          | _                 |                   | _                 | _                | WINOPN           |

#### REGISTER 15-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:           | HC = Hardware Cleared | HS = Hardware Set                |            |

|-------------------|-----------------------|----------------------------------|------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as   | '0'        |

| -n = Value at POR | '1' = Bit is set      | 0' = Bit is cleared $x = Bit is$ | is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP1<7:0> value was not detected                                                                                     |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer even was not detected                                                                                             |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

#### 16.1 Watchdog Timer Control Registers

#### TABLE 16-1: WATCHDOG TIMER REGISTER MAP

| ess                       |                       | œ.        |       |                      |       |       |       |           |      |      | Bits |      |      |      |      |      |      |          | s         |

|---------------------------|-----------------------|-----------|-------|----------------------|-------|-------|-------|-----------|------|------|------|------|------|------|------|------|------|----------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14                | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0     | All Reset |

| 0000                      | WDTCON <sup>(1)</sup> | 31:16     |       | WDTCLRKEY<15:0> 0000 |       |       |       |           |      |      |      |      |      |      |      |      |      |          |           |

| 0800                      | WD1CON.               | 15:0      | ON    | _                    | _     |       | RI    | UNDIV<4:0 | )>   |      | _    | _    | _    | _    | _    | _    | —    | WDTWINEN | xx00      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See 12.0 "I/O Ports" for more information.

#### TABLE 28-1: ADC REGISTER MAP (CONTINUED)

| ess)                        |                  | e         |                       |                           |                       |                       |                       |                       |                       | Bit                   | S                     |                       |                       |                       |                       |            |        |        | Ś          |

|-----------------------------|------------------|-----------|-----------------------|---------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------------|--------|--------|------------|

| Virtual Address<br>(BF84_#) | Register<br>Name | Bit Range | 31/15                 | 30/14                     | 29/13                 | 28/12                 | 27/11                 | 26/10                 | 25/9                  | 24/8                  | 23/7                  | 22/6                  | 21/5                  | 20/4                  | 19/3                  | 18/2       | 17/1   | 16/0   | All Recets |

| B04C                        | ADCCMP3          | 31:16     |                       | •                         | •                     | •                     |                       |                       |                       | DCMPH                 | <15:0>                | •                     | •                     | •                     | •                     |            |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       |                       |                       |                       |                       | DCMPLC                | )<15:0>               |                       |                       |                       |                       |            |        |        | 000        |

| B050                        | ADCCMPEN4        | 31:16     | CMPE31 <sup>(1)</sup> | CMPE30 <sup>(1)</sup>     | CMPE29 <sup>(1)</sup> | CMPE28 <sup>(1)</sup> | CMPE27 <sup>(1)</sup> | CMPE26 <sup>(1)</sup> | CMPE25 <sup>(1)</sup> | CMPE24 <sup>(1)</sup> | CMPE23 <sup>(1)</sup> | CMPE22 <sup>(1)</sup> | CMPE21 <sup>(1)</sup> | CMPE20 <sup>(1)</sup> | CMPE19 <sup>(1)</sup> | CMPE18     | CMPE17 | CMPE16 | 000        |

|                             |                  | 15:0      | CMPE15                | CMPE14                    | CMPE13                | CMPE12                | CMPE11                | CMPE10                | CMPE9                 | CMPE8                 | CMPE7                 | CMPE6                 | CMPE5                 | CMPE4                 | CMPE3                 | CMPE2      | CMPE1  | CMPE0  | 000        |

| B054                        | ADCCMP4          | 31:16     |                       |                           |                       |                       |                       |                       |                       | DCMPH                 | <15:0>                |                       |                       |                       |                       |            |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       |                       |                       |                       |                       | DCMPLC                | )<15:0>               |                       |                       |                       |                       |            |        |        | 00         |

| B058                        | ADCCMPEN5        | 31:16     | CMPE31 <sup>(1)</sup> | CMPE30 <sup>(1)</sup>     | CMPE29 <sup>(1)</sup> | CMPE28 <sup>(1)</sup> | CMPE27 <sup>(1)</sup> | CMPE26 <sup>(1)</sup> | CMPE25 <sup>(1)</sup> | CMPE24 <sup>(1)</sup> | CMPE23 <sup>(1)</sup> | CMPE22 <sup>(1)</sup> | CMPE21 <sup>(1)</sup> | CMPE20 <sup>(1)</sup> | CMPE19 <sup>(1)</sup> | CMPE18     | CMPE17 | CMPE16 | 000        |

|                             |                  | 15:0      | CMPE15                | CMPE14                    | CMPE13                | CMPE12                | CMPE11                | CMPE10                | CMPE9                 | CMPE8                 | CMPE7                 | CMPE6                 | CMPE5                 | CMPE4                 | CMPE3                 | CMPE2      | CMPE1  | CMPE0  | 000        |

| B05C                        | ADCCMP5          | 31:16     |                       |                           |                       |                       |                       |                       |                       | DCMPH                 | <15:0>                |                       |                       |                       |                       |            |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       |                       |                       |                       |                       | DCMPLC                | )<15:0>               |                       |                       |                       |                       |            |        |        | 000        |

| B060                        | ADCCMPEN6        | 31:16     | CMPE31 <sup>(1)</sup> | CMPE30 <sup>(1)</sup>     | CMPE29 <sup>(1)</sup> | CMPE28 <sup>(1)</sup> | CMPE27 <sup>(1)</sup> | CMPE26 <sup>(1)</sup> | CMPE25 <sup>(1)</sup> | CMPE24 <sup>(1)</sup> | CMPE23 <sup>(1)</sup> | CMPE22 <sup>(1)</sup> | CMPE21 <sup>(1)</sup> | CMPE20 <sup>(1)</sup> | CMPE19 <sup>(1)</sup> | CMPE18     | CMPE17 | CMPE16 | 000        |

|                             |                  | 15:0      | CMPE15                | CMPE14                    | CMPE13                | CMPE12                | CMPE11                | CMPE10                | CMPE9                 | CMPE8                 | CMPE7                 | CMPE6                 | CMPE5                 | CMPE4                 | CMPE3                 | CMPE2      | CMPE1  | CMPE0  | 000        |

| B064                        | ADCCMP6          | 31:16     |                       |                           |                       |                       |                       |                       |                       | DCMPH                 | <15:0>                |                       |                       |                       |                       |            |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       |                       |                       |                       |                       | DCMPLC                | 0<15:0>               |                       |                       |                       |                       |            |        |        | 000        |

| B068                        | ADCFLTR1         | 31:16     | AFEN                  | DATA16EN                  | DFMODE                | (                     | OVRSAM<2:0            | >                     | AFGIEN                | AFRDY                 | _                     | _                     | —                     |                       | C                     | HNLID<4:0> |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       | FLTRDATA<15:0>        |                       |                       |                       |                       |                       |                       | 000                   |                       |                       |            |        |        |            |

| B06C                        | ADCFLTR2         | 31:16     | AFEN                  | DATA16EN                  | DFMODE                | (                     | OVRSAM<2:0            | >                     | AFGIEN                | AFRDY                 | _                     | _                     | —                     |                       | C                     | HNLID<4:0> |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       |                       |                       |                       |                       | FLTRDAT               | A<15:0>               |                       |                       |                       |                       |            |        |        | 000        |

| B070                        | ADCFLTR3         | 31:16     | AFEN                  | DATA16EN                  | DFMODE                | (                     | OVRSAM<2:0            | >                     | AFGIEN                | AFRDY                 | -                     | _                     | _                     |                       | C                     | HNLID<4:0> |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       |                       |                       |                       |                       | FLTRDAT               | A<15:0>               |                       |                       |                       |                       |            |        |        | 000        |

| B074                        | ADCFLTR4         | 31:16     | AFEN                  | DATA16EN                  | DFMODE                | (                     | OVRSAM<2:0            | >                     | AFGIEN                | AFRDY                 |                       | _                     | _                     |                       | C                     | HNLID<4:0> |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       |                       |                       |                       |                       | FLTRDAT               | A<15:0>               |                       |                       |                       |                       |            |        |        | 000        |

| B078                        | ADCFLTR5         | 31:16     | AFEN                  | DATA16EN                  | DFMODE                | (                     | OVRSAM<2:0            | >                     | AFGIEN                | AFRDY                 | _                     | _                     | —                     |                       | C                     | HNLID<4:0> |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       |                       |                       |                       |                       | FLTRDAT               | A<15:0>               |                       |                       |                       |                       |            |        |        | 000        |

| B07C                        | ADCFLTR6         | 31:16     | AFEN                  | DATA16EN                  | DFMODE                | (                     | OVRSAM<2:0            | >                     | AFGIEN                | AFRDY                 | —                     | —                     | —                     |                       | C                     | HNLID<4:0> |        |        | 000        |

|                             |                  | 15:0      |                       |                           |                       |                       |                       |                       |                       | FLTRDAT               | A<15:0>               |                       |                       |                       |                       |            |        |        | 000        |

| B080                        | ADCTRG1          | 31:16     | —                     | —                         | -                     |                       | Т                     | RGSRC3<4:             | 0>                    |                       | _                     | —                     | —                     |                       | TF                    | GSRC2<4:0  | >      |        | 000        |

|                             |                  | 15:0      |                       | _                         | _                     |                       | T                     | RGSRC1<4:             | 0>                    |                       | -                     | _                     | _                     |                       | TF                    | GSRC0<4:0  | >      |        | 000        |

| B084                        | ADCTRG2          | 31:16     | —                     | —                         | -                     |                       | Т                     | RGSRC7<4:             | 0>                    |                       | _                     | —                     | —                     |                       | TF                    | GSRC6<4:0  | >      |        | 000        |

|                             |                  | 15:0      | —                     | —                         | -                     |                       | Т                     | RGSRC5<4:             | 0>                    |                       | _                     | —                     | —                     |                       | TF                    | GSRC4<4:0  | >      |        | 000        |

| B088                        | ADCTRG3          | 31:16     | —                     | —                         |                       |                       |                       |                       |                       | 000                   |                       |                       |                       |                       |                       |            |        |        |            |

|                             |                  | 15:0      | —                     | TRGSRC9<4:0> TRGSRC8<4:0> |                       |                       |                       |                       |                       | 000                   |                       |                       |                       |                       |                       |            |        |        |            |

| B0A0                        | ADCCMPCON1       | 31:16     |                       |                           |                       |                       |                       |                       |                       | CVDDAT                | A<15:0>               |                       |                       |                       |                       |            |        |        | 000        |

|                             |                  | 15:0      |                       | —                         |                       |                       | AINIE                 | )<5:0>                |                       |                       | ENDCMP                | DCMPGIEN              | DCMPED                | IEBTWN                | IEHIHI                | IEHILO     | IELOHI | IELOLO | 000        |

| B0A4                        | ADCCMPCON2       | 31:16     |                       | _                         | _                     | —                     | —                     | _                     | _                     | _                     | _                     | _                     | _                     | _                     | —                     | _          | _      | —      | 000        |

|                             |                  | 15:0      |                       | _                         | _                     |                       |                       | AINID<4:0>            |                       |                       | ENDCMP                | DCMPGIEN              | DCMPED                | IEBTWN                | IEHIHI                | IEHILO     | IELOHI | IELOLO | 000        |

| B0A8                        | ADCCMPCON3       | 31:16     | _                     | _                         | _                     | —                     | —                     | —                     | —                     | —                     | —                     | —                     | —                     | _                     | —                     | —          | —      | —      | 000        |

|                             |                  | 15:0      | _                     | _                         | _                     |                       |                       | AINID<4:0>            |                       |                       | ENDCMP                | DCMPGIEN              | DCMPED                | IEBTWN                | IEHIHI                | IEHILO     | IELOHI | IELOLO | 000        |

1: 2: 3:

This bit or register is not available on 64-pin devices. This bit or register is not available on 64-pin and 100-pin devices. Before enabling the ADC, the user application must initialize the ADC calibration values by copying them from the factory-programmed DEVADCx Flash registers into the corresponding ADCxCFG registers.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |