Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efm064-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              |                   | x = 0-13)         |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | _                 | _                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 7.0          | —                 |                   |                   | —                 |                   |                   |                  | CLEAR            |

|              |                   |                   |                   |                   |                   |                   |                  |                  |

#### REGISTER 4-6: SBTxECLRS: SYSTEM BUS TARGET 'x' SINGLE ERROR CLEAR REGISTER ('x' = 0-13)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-1 Unimplemented: Read as '0'

bit 0 CLEAR: Clear Single Error on Read bit A single error as reported via SBTxELOG1 and SBTxELOG2 is cleared by a read of this register.

**Note:** Refer to Table 4-6 for the list of available targets and their descriptions.

#### REGISTER 4-7: SBTxECLRM: SYSTEM BUS TARGET 'x' MULTIPLE ERROR CLEAR REGISTER ('x' = 0-13)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 |                   |                   | _                 | _                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 |                   |                   | _                 |                   | —                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 7:0          |                   |                   |                   |                   |                   |                   |                  | CLEAR            |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-1 Unimplemented: Read as '0'

bit 0 CLEAR: Clear Multiple Errors on Read bit Multiple errors as reported via SBTxELOG1 and SBTxELOG2 is cleared by a read of this register.

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

© 2015-2016 Microchip Technology Inc.

# **REGISTER 7-2:** PRISS: PRIORITY SHADOW SELECT REGISTER (CONTINUED) bit 15-12 PRI3SS<3:0>: Interrupt with Priority Level 3 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 3 uses Shadow Set 0) 0111 = Interrupt with a priority level of 3 uses Shadow Set 7 0110 = Interrupt with a priority level of 3 uses Shadow Set 6 0001 = Interrupt with a priority level of 3 uses Shadow Set 1 0000 = Interrupt with a priority level of 3 uses Shadow Set 0 bit 11-8 **PRI2SS<3:0>:** Interrupt with Priority Level 2 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 2 uses Shadow Set 0) 0111 = Interrupt with a priority level of 2 uses Shadow Set 7 0110 = Interrupt with a priority level of 2 uses Shadow Set 6 0001 = Interrupt with a priority level of 2 uses Shadow Set 1 0000 = Interrupt with a priority level of 2 uses Shadow Set 0 PRI1SS<3:0>: Interrupt with Priority Level 1 Shadow Set bits<sup>(1)</sup> bit 7-4 1xxx = Reserved (by default, an interrupt with a priority level of 1 uses Shadow Set 0) 0111 = Interrupt with a priority level of 1 uses Shadow Set 7 0110 = Interrupt with a priority level of 1 uses Shadow Set 6 0001 = Interrupt with a priority level of 1 uses Shadow Set 1 0000 = Interrupt with a priority level of 1 uses Shadow Set 0 bit 3-1 Unimplemented: Read as '0' bit 0 SS0: Single Vector Shadow Register Set bit 1 = Single vector is presented with a shadow set 0 = Single vector is not presented with a shadow set

**Note 1:** These bits are ignored if the MVEC bit (INTCON<12>) = 0.

# TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| ss                          |                  |           |                 |                    |        |       |           |       |         |         | Bits    |        |                       |        |                       |          |        |        |            |      |

|-----------------------------|------------------|-----------|-----------------|--------------------|--------|-------|-----------|-------|---------|---------|---------|--------|-----------------------|--------|-----------------------|----------|--------|--------|------------|------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15           | 30/14              | 29/13  | 28/12 | 27/11     | 26/10 | 25/9    | 24/8    | 23/7    | 22/6   | 21/5                  | 20/4   | 19/3                  | 18/2     | 17/1   | 16/0   | All Resets |      |

| 3340                        | USB              | 31:16     | _               | _                  | —      | —     | —         | _     |         | _       | EP7TXD  | EP6TXD | EP5TXD                | EP4TXD | EP3TXD                | EP2TXD   | EP1TXD | _      | 0000       |      |

| 3340                        | DPBFD            | 15:0      | _               | —                  | —      | —     | —         | _     | _       | —       | EP7RXD  | EP6RXD | EP5RXD                | EP4RXD | EP3RXD                | EP2RXD   | EP1RXD | —      | 0000       |      |

| 3344                        |                  | 31:16     |                 | THHSRTN<15:0> 05E6 |        |       |           |       |         |         |         |        |                       |        |                       |          |        |        |            |      |

| 5544                        | TMCON1           | 15:0      | TUCH<15:0> 4074 |                    |        |       |           |       |         |         |         |        |                       |        | 4074                  |          |        |        |            |      |

| 3348                        | 000              | 31:16     | _               |                    | _      | _     | —         | —     | _       | _       | _       | —      | —                     | _      | _                     | _        | -      | _      | 0000       |      |

| 0040                        | TMCON2           | 15:0      | _               | —                  | —      | _     | —         | —     | -       | —       |         | —      | —                     | _      |                       | THSBT<3  | 8:0>   |        | 0000       |      |

|                             |                  | 04.40     | 31:16           |                    | _      | LPM   | LPM       |       | LPMNYIE | LPMSTIE | LPMTOIE |        |                       |        | LPMNAK <sup>(1)</sup> |          | N<1:0> | LPMRES |            | 0000 |

| 3360                        | USB<br>LPMR1     | 51.10     | _               |                    | ERRIE  | RESIE |           |       |         |         |         | _      | _                     | _(2)   | (2)                   | (2)      |        |        | 0000       |      |

|                             | 2                | 15:0      |                 | ENDPOIN            | T<3:0> |       | —         | _     | _       | RMTWAK  |         | HIRI   | D<3:0>                |        |                       | LNKSTATE | <3:0>  |        | 0000       |      |

|                             |                  | 31:16     | _               | —                  | _      | _     | —         | _     | _       | —       | _       | —      | —                     | _      | _                     | _        | —      |        | 0000       |      |

| 3364                        | USB<br>LPMR2     | 15:0      | _               |                    |        | LPI   | MFADDR<6: | 0>    |         |         | _       | _      | LPMERR <sup>(1)</sup> | LPMRES | LPMNC                 | LPMACK   | LPMNY  | LPMST  | 0000       |      |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1: Device mode.

2: Host mode.

3:

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7). 4:

# TABLE 11-2: USB REGISTER MAP 2

| Bits                       |                  |           |       |       |       |       |       |       |               |              |         |               |                |                |               |       |        |               |            |

|----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|---------------|--------------|---------|---------------|----------------|----------------|---------------|-------|--------|---------------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9          | 24/8         | 23/7    | 22/6          | 21/5           | 20/4           | 19/3          | 18/2  | 17/1   | 16/0          | All Resets |

|                            |                  | 31:16     | _     | —     | —     | _     | —     | USBIF | USBRF         | USBWKUP      | _       | —             | —              | —              | _             | —     | —      | _             | 0100       |

| 4000                       | USB<br>CRCON     | 15:0      | _     | _     | _     | _     | _     | _     | USB<br>IDOVEN | USB<br>IDVAL | PHYIDEN | VBUS<br>MONEN | ASVAL<br>MONEN | BSVAL<br>MONEN | SEND<br>MONEN | USBIE | USBRIE | USB<br>WKUPEN | 8000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 21.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116) "PIC32 Family Reference the in Manual", which is available from the Microchip web site (www.microchip.com/ PIC32).

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard.

Each I<sup>2</sup>C module has a 2-pin interface:

- SCLx pin is clock

- SDAx pin is data

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- Provides support for address bit masking

- SMBus support

Figure 21-1 illustrates the I<sup>2</sup>C module block diagram.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        |                   | —                 | —                 | —                 | —                 | —                 | —                | _                |  |  |  |  |  |  |

| 00.40        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | _                 | PCIE              | SCIE              | BOEN              | SDAHT             | SBCDE             | AHEN             | DHEN             |  |  |  |  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | ON                | —                 | SIDL              | SCKREL            | STRICT            | A10M              | DISSLW           | SMEN             |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |  |  |  |  |  |  |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |  |  |  |  |  |  |

# REGISTER 21-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Legend:           | HC = Cleared in Hardware |                          |                    |  |  |  |

|-------------------|--------------------------|--------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, r | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |

#### bit 31-23 Unimplemented: Read as '0'

| DIL 31-23 | Unimplemented: Read as 0                                                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 22    | PCIE: Stop Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                             |

|           | 1 = Enable interrupt on detection of Stop condition                                                                                      |

|           | 0 = Stop detection interrupts are disabled                                                                                               |

| bit 21    | SCIE: Start Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                            |

|           | 1 = Enable interrupt on detection of Start or Restart conditions                                                                         |

|           | 0 = Start detection interrupts are disabled                                                                                              |

| bit 20    | BOEN: Buffer Overwrite Enable bit (I <sup>2</sup> C Slave mode only)                                                                     |

|           | $1 = I2CxRCV$ is updated and $\overline{ACK}$ is generated for a received address/data byte, ignoring the state of the                   |

|           | I2COV bit (I2CxSTAT<6>)only if the RBF bit (I2CxSTAT<2>) = 0<br>0 = I2CxRCV is only updated when the I2COV bit (I2CxSTAT<6>) is clear    |

| bit 19    | <b>SDAHT:</b> SDA Hold Time Selection bit                                                                                                |

| DIL 19    | 1 = Minimum of 300 ns hold time on SDA after the falling edge of SCL                                                                     |

|           | 1 = Minimum of 300 ns hold time on SDA after the falling edge of SCL0 = Minimum of 100 ns hold time on SDA after the falling edge of SCL |

| bit 18    | <b>SBCDE:</b> Slave Mode Bus Collision Detect Enable bit (I <sup>2</sup> C Slave mode only)                                              |

|           | 1 = Enable slave bus collision interrupts                                                                                                |

|           | 0 = Slave bus collision interrupts are disabled                                                                                          |

| bit 18    | AHEN: Address Hold Enable bit (Slave mode only)                                                                                          |

|           | 1 = Following the 8th falling edge of SCL for a matching received address byte; SCKREL bit will be cleared                               |

|           | and the SCL will be held low.                                                                                                            |

| bit 16    | <ul> <li>0 = Address holding is disabled</li> <li>DHEN: Data Hold Enable bit (I<sup>2</sup>C Slave mode only)</li> </ul>                 |

| DIT 16    |                                                                                                                                          |

|           | 1 = Following the 8th falling edge of SCL for a received data byte; slave hardware clears the SCKREL bit<br>and SCL is held low          |

|           | 0 = Data holding is disabled                                                                                                             |

| bit 15    | ON: I <sup>2</sup> C Enable bit                                                                                                          |

|           | 1 = Enables the I <sup>2</sup> C module and configures the SDA and SCL pins as serial port pins                                          |

|           | 0 = Disables the I <sup>2</sup> C module; all I <sup>2</sup> C pins are controlled by PORT functions                                     |

| bit 14    | Unimplemented: Read as '0'                                                                                                               |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                              |

|           | 1 = Discontinue module operation when device enters Idle mode                                                                            |

|           | 0 = Continue module operation in Idle mode                                                                                               |

|           |                                                                                                                                          |

|           |                                                                                                                                          |

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|------------------------|------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                      | _                      | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |

| 22:46        | U-0                    | U-0                    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                      |                        | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |

|              | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | WCS2 <sup>(1)</sup>    | WCS1 <sup>(3)</sup>    |                   |                   |                   |                   |                  |                  |  |  |  |  |

|              | WADDR15 <sup>(2)</sup> | WADDR14 <sup>(4)</sup> | WADDR<13:8>       |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0                  | R/W-0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

|              | WADDR<7:0>             |                        |                   |                   |                   |                   |                  |                  |  |  |  |  |

# REGISTER 23-8: PMWADDR: PARALLEL PORT WRITE ADDRESS REGISTER

#### Legend:

| - 5               |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 WCS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 WADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 WCS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active 0 = Chip Select 1 is inactive

- bit 14 WADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 WADDR<13:0>: Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- 3: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

Note: This register is only used when the DUALBUF bit (PMCON<17>) is set to '1'.

# REGISTER 25-1: RTCCON: REAL-TIME CLOCK AND CALENDAR CONTROL REGISTER (CONTINUED)

bit 10-9 RTCCLKSEL<1:0>: RTCC Clock Select bits

When a new value is written to these bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.

- 11 = Reserved

- 10 = Reserved

- 01 = RTCC uses the external 32.768 kHz Secondary Oscillator (SOSC)

- 00 = RTCC uses the internal 32 kHz oscillator (LPRC)

- bit 8-7 RTCOUTSEL<1:0>: RTCC Output Data Select bits<sup>(2)</sup>

- 11 = Reserved

- 10 = RTCC Clock is presented on the RTCC pin

- 01 = Seconds Clock is presented on the RTCC pin

- 00 = Alarm Pulse is presented on the RTCC pin when the alarm interrupt is triggered

- bit 6 RTCCLKON: RTCC Clock Enable Status bit<sup>(5)</sup>

- 1 = RTCC Clock is actively running

- 0 = RTCC Clock is not running

- bit 5-4 Unimplemented: Read as '0'

- bit 3 RTCWREN: Real-Time Clock Value Registers Write Enable bit<sup>(3)</sup>

- 1 = Real-Time Clock Value registers can be written to by the user

- 0 = Real-Time Clock Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: Real-Time Clock Value Registers Read Synchronization bit

- 1 = Real-time clock value registers can change while reading (due to a rollover ripple that results in an invalid data read). If the register is read twice and results in the same data, the data can be assumed to be valid.

- 0 = Real-time clock value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(4)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 **RTCOE:** RTCC Output Enable bit

- 1 = RTCC output is enabled

- 0 = RTCC output is not enabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- **2:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 3: The RTCWREN bit can be set only when the write sequence is enabled.

- 4: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

- 5: This bit is undefined when RTCCLKSEL<1:0> = 00 (LPRC is the clock source).

Note: This register is reset only on a Power-on Reset (POR).

# PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

| REGIST  | ER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER (CONTINUED)                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-0 | ARPT<7:0>: Alarm Repeat Counter Value bits <sup>(2)</sup>                                                                                        |

|         | 11111111 = Alarm will trigger 256 times                                                                                                          |

|         | •                                                                                                                                                |

|         |                                                                                                                                                  |

|         | 00000000 = Alarm will trigger one time<br>The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1. |

| Note 1: | Hardware clears the ALRMEN bit anytime the alarm event occurs, when $ARPT < 7:0 > = 0.0$ and $CHIME = 0.$                                        |

| 2:      | This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.                                                       |

|         |                                                                                                                                                  |

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 04-04        | R-0, HS, HC            |

| 31:24        | EIRDY31 <sup>(1)</sup> | EIRDY30 <sup>(1)</sup> | EIRDY29 <sup>(1)</sup> | EIRDY28 <sup>(1)</sup> | EIRDY27 <sup>(1)</sup> | EIRDY26 <sup>(1)</sup> | EIRDY25 <sup>(1)</sup> | EIRDY24 <sup>(1)</sup> |

| 00.40        | R-0, HS, HC            |

| 23:16        | EIRDY23 <sup>(1)</sup> | EIRDY22 <sup>(1)</sup> | EIRDY21 <sup>(1)</sup> | EIRDY20 <sup>(1)</sup> | EIRDY19 <sup>(1)</sup> | EIRDY18                | EIRDY17                | EIRDY16                |

| 45.0         | R-0, HS, HC            |

| 15:8         | EIRDY15                | EIRDY14                | EIRDY13                | EIRDY12                | EIRDY11                | EIRDY10                | EIRDY9                 | EIRDY8                 |

| 7.0          | R-0, HS, HC            |

| 7:0          | EIRDY7                 | EIRDY6                 | EIRDY5                 | EIRDY4                 | EIRDY3                 | EIRDY2                 | EIRDY1                 | EIRDY0                 |

|              |                        |                        |                        |                        |                        |                        |                        |                        |

# REGISTER 28-30: ADCEISTAT1: ADC EARLY INTERRUPT STATUS REGISTER 1

| Legend:           | HS = Hardware Set | HC = Hardware Cleared              |                    |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-0 EIRDY31:EIRDY0: Early Interrupt for Corresponding Analog Input Ready bits

- 1 = This bit is set when the early interrupt event occurs for the specified analog input. An interrupt will be generated if early interrupts are enabled in the ADCEIEN1 register. For the Class 1 analog inputs, this bit will set as per the configuration of the ADCEIS<2:0> bits in the ADCXTIME register. For the shared ADC module, this bit will be set as per the configuration of the ADCEIS<2:0> bits in the ADCCIS<2:0> bits in the ADCCON2 register.

- 0 = Interrupts are disabled

- Note 1: This bit is not available on 64-pin devices.

NOTES:

| ess                         |                                                          |               |                |                |         |       |       |            |          | Bits      | 6       |        |         |       |          | -          |          |                |            |

|-----------------------------|----------------------------------------------------------|---------------|----------------|----------------|---------|-------|-------|------------|----------|-----------|---------|--------|---------|-------|----------|------------|----------|----------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                          | Bit Range     | 31/15          | 30/14          | 29/13   | 28/12 | 27/11 | 26/10      | 25/9     | 24/8      | 23/7    | 22/6   | 21/5    | 20/4  | 19/3     | 18/2       | 17/1     | 16/0           | All Resets |

| 0050                        | C1FLTCON3                                                | 31:16         | FLTEN15        | MSEL1          | 15<1:0> |       |       | FSEL15<4:0 | >        |           | FLTEN14 | MSEL1  | 4<1:0>  |       | F        | SEL14<4:0> | >        |                | 0000       |

| 0010                        | CILEICONS                                                | 15:0          | FLTEN13        | MSEL1          | 3<1:0>  |       |       | FSEL13<4:0 | >        |           | FLTEN12 | MSEL1  | 2<1:0>  |       | F        | SEL12<4:0> | >        |                | 0000       |

| 0100                        | C1FLTCON4                                                | 31:16         | FLTEN19        | MSEL1          |         |       |       | FSEL19<4:0 |          |           | FLTEN18 |        | 8<1:0>  |       |          | SEL18<4:0> |          |                | 0000       |

| 0.00                        | 0.1.2.00.1.1                                             | 15:0          | FLTEN17        | MSEL1          | 17<1:0> |       |       | FSEL17<4:0 |          |           | FLTEN16 | MSEL1  | 6<1:0>  |       | F        | SEL16<4:0> | >        |                | 0000       |

| 0110                        | C1FLTCON5                                                | 31:16         | FLTEN23        |                | 23<1:0> |       |       | FSEL23<4:0 |          |           | FLTEN22 |        | 22<1:0> |       |          | SEL22<4:0> |          |                | 0000       |

| 0.110                       | 0.1.2.00.10                                              | 15:0          | FLTEN21        | MSEL2          |         |       |       | FSEL21<4:0 |          |           | FLTEN20 |        | 20<1:0> |       |          | SEL20<4:0> |          |                | 0000       |

| 0120                        | C1FLTCON6                                                | 31:16         | FLTEN27        | MSEL2          |         |       |       | FSEL27<4:0 |          |           | FLTEN26 |        | 26<1:0> |       |          | SEL26<4:0> |          |                | 0000       |

|                             |                                                          | 15:0          | FLTEN25        | MSEL2          |         |       |       | FSEL25<4:0 |          |           | FLTEN24 | MSEL2  | -       |       |          | SEL24<4:0> |          |                | 0000       |

| 0130                        | C1FLTCON7                                                | 31:16         |                | MSEL3          |         |       |       | FSEL31<4:0 |          |           | FLTEN30 | MSEL3  |         |       |          | SEL30<4:0> |          |                | 0000       |

|                             |                                                          | 15:0          | FLTEN29        | MSEL2          | 29<1:0> |       |       | FSEL29<4:0 | >        |           | FLTEN28 | MSEL2  | 28<1:0> |       |          | SEL28<4:0> | r        |                | 0000       |

| 0140-<br>0330               | C1RXFn<br>(n = 0-31)                                     | 31:16         |                |                |         |       |       |            |          | xxxx      |         |        |         |       |          |            |          |                |            |

| 0330                        | (1 = 0-31)                                               | 15:0          |                | EID<15:0> xxxx |         |       |       |            |          |           |         |        |         |       |          |            |          |                |            |

| 0340                        | C1FIFOBA                                                 | 31:16<br>15:0 | C1EIEOBA<31:0> |                |         |       |       |            |          | 0000      |         |        |         |       |          |            |          |                |            |

| 0350                        | C1FIFOCONn                                               | 31:16         | —              | _              | —       | —     | _     |            | —        | _         | _       | _      | —       |       |          | SIZE<4:0>  |          | 0000           |            |

| 0000                        | (n = 0)                                                  | 15:0          | —              | FRESET         | UINC    | DONLY | —     | _          | —        |           | TXEN    | TXABAT | TXLARB  | TXERR | TXREQ    | RTREN      | TXPRI<   | :1:0>          | 0000       |

| 0360                        | C1FIFOINTn                                               | 31:16         | —              | _              | —       | _     | _     | TXNFULLIE  | TXHALFIE | TXEMPTYIE | _       | _      | —       | _     | RXOVFLIE | RXFULLIE   | RXHALFIE | RXN<br>EMPTYIE | 0000       |

| 0000                        | (n = 0)                                                  | 15:0          | _              | -              | —       | —     | _     | TXNFULLIF  | TXHALFIF | TXEMPTYIF | -       | —      | -       | _     | RXOVFLIF | RXFULLIF   | RXHALFIF | RXN<br>EMPTYIF | 0000       |

| 0370                        | $\begin{array}{c} \text{C1FIFOUAn} \\ (n=0) \end{array}$ | 31:16<br>15:0 |                |                |         |       |       |            |          | C1FIFOUA  | <31:0>  |        |         |       |          |            |          |                | 0000       |

| 0380                        | C1FIFOCIn                                                | 31:16         | _              | _              | _       | —     | _     | _          | —        | _         | —       | —      | —       | _     | —        | _          | —        | —              | 0000       |

| 0380                        | (n = 0)                                                  | 15:0          | —              | _              | —       | —     | —     | —          | —        |           | _       | —      | —       |       | C1       | FIFOCI<4:0 | )>       |                | 0000       |

|                             |                                                          | 31:16         | _              | _              | -       | -     | _     | —          | -        | _         | -       | —      | -       |       |          | SIZE<4:0>  |          |                | 0000       |

|                             |                                                          | 15:0          | —              | FRESET         | UINC    | DONLY | _     | _          | —        | _         | TXEN    | TXABAT | TXLARB  | TXERR | TXREQ    | RTREN      | TXPRI<   | <1:0>          | 0000       |

|                             | C1FIFOCONn                                               | 31:16         | —              | _              | —       | _     | _     | TXNFULLIE  | TXHALFIE | TXEMPTYIE | _       | _      | —       | _     | RXOVFLIE | RXFULLIE   | RXHALFIE | RXN<br>EMPTYIE | 0000       |

| 0390-<br>0B40               | C1FIFOINTn<br>C1FIFOUAn<br>C1FIFOCIn                     | 15:0          | _              | _              | —       | —     | _     | TXNFULLIF  | TXHALFIF | TXEMPTYIF | _       | —      | —       | _     | RXOVFLIF | RXFULLIF   | RXHALFIF | RXN<br>EMPTYIF | 0000       |

|                             | (n = 1-31)                                               | 31:16         |                |                |         |       |       |            |          | C1FIFOUA  | ~31.0>  |        |         |       |          |            |          |                | 0000       |

|                             | . ,                                                      | 15:0          |                |                |         |       |       |            |          | UNIFUUF   |         |        |         |       |          |            |          |                | 0000       |

|                             |                                                          | 31:16         | -              | _              | _       | -     | _     | -          | _        | _         | _       | —      | —       | —     | -        | _          | _        | _              | 0000       |

|                             |                                                          | 15:0          | —              | _              | —       | —     | —     | —          | —        | —         | —       | —      | —       |       | C1       | FIFOCI<4:0 | )>       |                | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information. Note 1:

REGISTER 29-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED) bit 15 FLTEN9: Filter 9 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL9<1:0>: Filter 9 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL9<4:0>: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN8: Filter 8 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL8<1:0>: Filter 8 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL8<4:0>: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0 The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. Note:

|           | RE                | GISTER            |                   |                   |                   |                   |                  |                  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10     | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.6      |                   | PMCS<15:8>        |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0       |                   |                   |                   | PMCS              | S<7:0>            |                   |                  |                  |  |  |  |

#### REGISTER 30-9: ETHPMCS: ETHERNET CONTROLLER PATTERN MATCH CHECKSUM REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-8 PMCS<15:8>: Pattern Match Checksum 1 bits

bit 7-0 PMCS<7:0>: Pattern Match Checksum 0 bits

**Note 1:** This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

# REGISTER 30-10: ETHPMO: ETHERNET CONTROLLER PATTERN MATCH OFFSET REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        | —                 | —                 | _                 |                   |                   | _                 |                  | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | —                 | _                 | —                 | —                 | —                | —                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         | PMO<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                   |                   |                   | PMO               | <7:0>             |                   |                  |                  |  |  |

| Le | gend:              |  |

|----|--------------------|--|

|    | Deside to the test |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **PMO<15:0>:** Pattern Match Offset 1 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

| REGISTI | ER 34-3:                   | DEVCFG0/ADEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)                                                            |

|---------|----------------------------|----------------------------------------------------------------------------------------------------------------------|

| bit 10  | FSLEEP: F                  | Flash Sleep Mode bit                                                                                                 |

|         |                            | s powered down when the device is in Sleep mode                                                                      |

|         |                            | emains powered when the device is in Sleep mode                                                                      |

| bit 9-8 |                            | I<1:0>: Dynamic Flash ECC Configuration bits                                                                         |

|         |                            | vice Reset, the value of these bits is copied to the ECCCON<1:0> bits (CFGCON<5:4>).                                 |

|         |                            | and dynamic ECC are disabled (ECCCON<1:0> bits are writable)                                                         |

|         |                            | and dynamic ECC are disabled (ECCCON<1:0> bits are locked)<br>mic Flash ECC is enabled (ECCCON<1:0> bits are locked) |

|         |                            | ECC is enabled (ECCCON<1:0> bits are locked; disables word Flash writes)                                             |

| bit 7   |                            | Write as '1'                                                                                                         |

| bit 6   | BOOTISA:                   | Boot ISA Selection bit                                                                                               |

|         | 1 = Boot c                 | ode and Exception code is MIPS32 <sup>®</sup>                                                                        |

|         | •                          | NEXC bit is set to '0' and the ISA<1:0> bits are set to '10' in the CP0 Config3 register)                            |

|         |                            | ode and Exception code is microMIPS™                                                                                 |

| bit 5   |                            | NEXC bit is set to '1' and the ISA<1:0> bits are set to '11' in the CP0 Config3 register) race Enable bit            |

| C IIC   |                            |                                                                                                                      |

|         |                            | features in the CPU are enabled<br>features in the CPU are disabled                                                  |

| bit 4-3 |                            | :0>: In-Circuit Emulator/Debugger Communication Channel Select bits                                                  |

|         |                            | C1/PGED1 pair is used                                                                                                |

|         |                            | C2/PGED2 pair is used                                                                                                |

|         | 01 = Reser                 |                                                                                                                      |

|         | 00 <b>= Rese</b> i         |                                                                                                                      |

| bit 2   |                            | JTAG Enable bit <sup>(1)</sup>                                                                                       |

|         | 1 = JTAG i:<br>0 = JTAG i: |                                                                                                                      |

| bit 1-0 |                            | :0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled)                                     |

| Dit 1-0 |                            | gger is disabled                                                                                                     |

|         |                            | gger is enabled                                                                                                      |

|         |                            |                                                                                                                      |

Note 1: This bit sets the value of the JTAGEN bit in the CFGCON register.

| DC CHARACTERISTICS                                             |                        | Standard Operating Conditions: 2.1V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |       |                        |  |  |  |

|----------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|--|--|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Maximum <sup>(4)</sup>                                                                                                                                  | Units | Conditions             |  |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |                                                                                                                                                         |       |                        |  |  |  |

| DC30a                                                          | 7                      | 22                                                                                                                                                      | mA    | 4 MHz <b>(Note 3)</b>  |  |  |  |

| DC31a                                                          | 8                      | 24                                                                                                                                                      | mA    | 10 MHz                 |  |  |  |

| DC32a                                                          | 13                     | 32                                                                                                                                                      | mA    | 60 MHz <b>(Note 3)</b> |  |  |  |

| DC33a                                                          | 21                     | 42                                                                                                                                                      | mA    | 130 MHz (Note 3)       |  |  |  |

| DC34                                                           | 26                     | 48                                                                                                                                                      | mA    | 180 MHz (Note 3)       |  |  |  |

| DC35                                                           | 28                     | 52                                                                                                                                                      | mA    | 200 MHz                |  |  |  |

#### TABLE 37-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBPMD = 1), VUSB3V3 is connected to VSS, PBCLKx divisor = 1:128 ('x' ≠ 7)

- CPU is in Idle mode (CPU core Halted)

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared (except USBPMD)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: Data in the "Maximum" column is at 3.3V, +85°C at specified operating frequency, unless otherwise stated. Parameters are for design guidance only and are not tested.

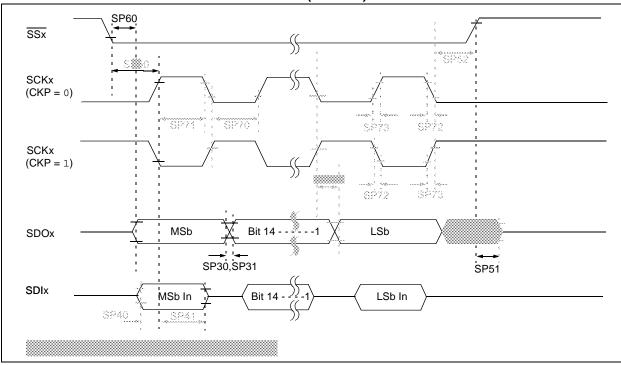

# FIGURE 37-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

# TABLE 37-33: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS         |                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature -40°C $\leq$ TA $\leq$ +85°C for Industrial} \\ \mbox{-40°C $\leq$ TA $\leq$ +125°C for Extended} \\ \end{array}$ |        |                        |      |            |                    |

|----------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|------|------------|--------------------|

| Param.<br>No.              | Symbol                                    | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                            | Min.   | Typical <sup>(2)</sup> | Max. | Units      | Conditions         |

| SP70                       | TscL                                      | SCKx Input Low Time (Note 3)                                                                                                                                                                                                                              | Tsck/2 | _                      | _    | ns         | —                  |

| SP71                       | TscH                                      | SCKx Input High Time (Note 3)                                                                                                                                                                                                                             | TSCK/2 | _                      |      | ns         | —                  |

| SP72                       | TscF                                      | SCKx Input Fall Time                                                                                                                                                                                                                                      |        | _                      | 10   | ns         | —                  |

| SP73                       | TscR                                      | SCKx Input Rise Time                                                                                                                                                                                                                                      | —      | _                      | 10   | ns         | —                  |

| SP30                       | TDOF                                      | SDOx Data Output Fall Time (Note 4)                                                                                                                                                                                                                       | —      | —                      |      | ns         | See parameter DO32 |

| SP31                       | TDOR                                      | SDOx Data Output Rise Time (Note 4)                                                                                                                                                                                                                       | —      | —                      |      | ns         | See parameter DO31 |

| SP35 TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge | —                                                                                                                                                                                                                                                         | _      | 10                     | ns   | VDD > 2.7V |                    |

|                            |                                           |                                                                                                                                                                                                                                                           | _      | 15                     | ns   | Vdd < 2.7V |                    |

| SP40                       | TDIV2scH,<br>TDIV2scL                     | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                | 0      | —                      | _    | ns         | —                  |

| SP41                       | TscH2diL,<br>TscL2diL                     | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                 | 7      | —                      | _    | ns         | —                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 20 ns.

- 4: Assumes 30 pF load on all SPIx pins.

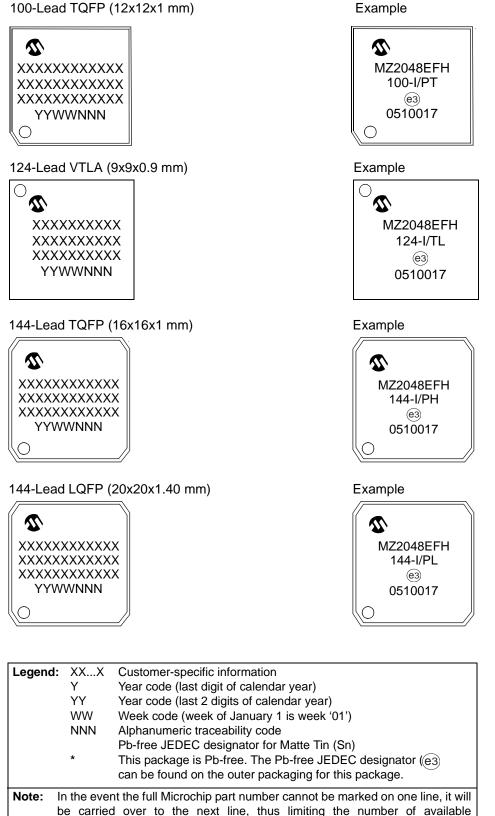

#### 41.1 Package Marking Information (Continued)

100-Lead TQFP (12x12x1 mm)

characters for customer-specific information.

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                                                                                                                | PIC32MZ EF Feature                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Scan Trigg                                                                                                                                                                                                                                                                | Jer Source                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| On PIC32MX devices, there are four sources that can trigger a scan conversion in the ADC module: Auto, Timer3, INT0, and clearing the SAMP bit.<br>SSRC<2:0> (AD1CON1<7:5>)<br>111 = Auto convert<br>110 = Reserved<br>101 = Reserved<br>100 = Reserved<br>011 = Reserved | On PIC32MZ EF devices, the list of sources for triggering a scan<br>conversion has been expanded to include the comparators,<br>Output Compare, and two additional Timers. In addition, trigger<br>sources can be simulated by setting the RQCNVRT<br>(ADCCON3<8>) bit.<br>STRGSRC<4:0> (ADCCON1<20:16>)<br>11111 = Reserved<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |  |  |  |  |

| 010 = Timer3 period match<br>001 = Active transition on INT0 pin<br>000 = Clearing SAMP bit                                                                                                                                                                               | 01011 = Comparator 1 COUT<br>01010 = OCMP5<br>01001 = OCMP3<br>01000 = OCMP1<br>00111 = TMR5 match<br>00101 = TMR3 match<br>00101 = TMR1 match<br>00100 = INT0<br>00011 = Reserved<br>00010 = Global level software trigger (GLSWTRG)<br>00001 = Global software trigger (GSWTRG)<br>00000 = No trigger                                                                             |  |  |  |  |

| Output                                                                                                                                                                                                                                                                    | Format                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| On PIC32MX devices, the output format was decided for all ADC channels based on the setting of the FORM<2:0> bits.                                                                                                                                                        | On PIC32MZ EF devices, the FRACT bit determines whether fractional or integer format is used. Then, each input can have its own setting for input (differential or single-ended) and sign (signed or unsigned) using the DIFFx and SIGNx bits in the ADCIMODx registers.                                                                                                            |  |  |  |  |

| FORM<2:0> (AD1CON1<10:8>)<br>011 = Signed Fractional 16-bit<br>010 = Fractional 16-bit<br>001 = Signed Integer 16-bit<br>000 = Integer 16-bit<br>111 = Signed Fractional 32-bit<br>110 = Fractional 32-bit                                                                | FRACT (ADCCON1<23>)<br>1 = Fractional<br>0 = Integer<br>DIFFx (ADCIMODy)<br>1 = Channel x is using Differential mode<br>0 = Channel x is using Single-ended mode                                                                                                                                                                                                                    |  |  |  |  |

| 101 = Signed Integer 32-bit<br>100 = Integer 32-bit                                                                                                                                                                                                                       | SIGNx (ADCMODy)<br>1 = Channel x is using Signed Data mode<br>0 = Channel x is using Unsigned Data mode                                                                                                                                                                                                                                                                             |  |  |  |  |

| Inter                                                                                                                                                                                                                                                                     | rupts                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| On PIC32MX devices, an interrupt is triggered from the ADC module when a certain number of conversions have taken place, irrespective of which channel was converted.                                                                                                     | On PIC32MZ EF devices, the ADC module can trigger an inter-<br>rupt for each channel when it is converted. Use the Interrupt Con-<br>troller bits, IEC1<31:27>, IEC2<31:0>, and IEC3<7:0>, to enable/<br>disable them.<br>In addition, the ADC support one global interrupt to indicate<br>conversion on any number of channels.                                                    |  |  |  |  |

| SMPI<3:0> (AD1CON2<5:2>)<br>1111 = Interrupt for each 16th sample/convert sequence<br>1110 = Interrupt for each 15th sample/convert sequence                                                                                                                              | AGIENxx (ADCGIRQENx <y>)<br/>1 = Data ready event will generate a Global ADC interrupt<br/>0 = No global interrupt<br/>In addition, interrupts can be generated for filter and comparator</y>                                                                                                                                                                                       |  |  |  |  |

| •<br>0001 = Interrupt for each 2nd sample/convert sequence<br>0000 = Interrupt for each sample/convert sequence                                                                                                                                                           | events.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

# TABLE A-3: ADC DIFFERENCES (CONTINUED)

# B.6 Resets

On PIC32MZ EF devices, the Reset module adds eight bits to the NMICNT field to make the time-out period before device Reset longer, as described in Table B-5.

# TABLE B-5: RESETS DIFFERENCES

| PIC32MZ EC Feature                                                                                                             | PIC32MZ EF Feature                                                                                                                                     |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Countdown to Reset During NMIs                                                                                                 |                                                                                                                                                        |  |  |  |  |

| On PIC32MZ EC devices, the NMICNT<7:0> field is eight bits long, giving a maximum of 256 instructions before the device Reset. | On PIC32MZ EF devices, the NMICNT<15:0> field is now 16 bits long, giving a longer period of time (up to 65,536 instructions) prior to a device Reset. |  |  |  |  |

# B.7 USB

On PIC32MZ EF devices, a new USBCRCON register has been added to assist in controlling the reset of the USB module, and triggering interrupts based on VBUS voltage levels. This register also overcomes an errata on PIC32MZ EC devices that requires a three second start-up on the USB module.

# B.8 I/O Ports

On PIC32MZ EF devices, many of the I/O pins now feature slew rate control bits to control how fast the pin makes a low-to-high or high-to-low transition. The Change Notification feature has also been enhanced to allow detection of level events in addition to edge detection. However, the SIDL bit is not present in the CNCONx registers on PIC32MZ EF devices, as it is on PIC32MZ EC devices.

# B.9 Watchdog Timer

PIC32MZ EF devices use a new Watchdog Timer, although the overall control through the DEVCFGx words remains identical to that of PIC32MZ EC devices. Table B-6 lists two more changes, as well.

# TABLE B-6: WATCHDOG TIMER DIFFERENCES

| PIC32MZ EC Feature                                                                                                     | PIC32MZ EF Feature                                                                        |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Watchdog Timer Postscaler                                                                                              |                                                                                           |  |  |  |  |

| On PIC32MZ EC devices, the SWDTPS<4:0> bits<br>(WDTCON<6:2>) reflect the postscaler setting for the Watchdog<br>Timer. | On PIC32MZ EF devices, the field has been changed to the RUNDIV<4:0> bits (WDTCON<12:8>). |  |  |  |  |