Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

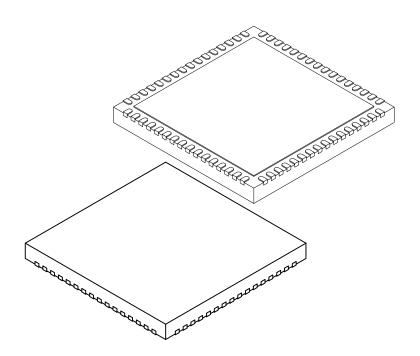

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efm064-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|           |                        | Pin Nu          | mber            |                          |             |                |                                                                                                                                                                                               |

|-----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name  | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                   |

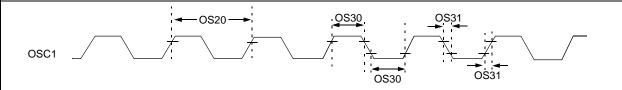

| CLKI      | 31                     | 49              | B28             | 71                       | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                        |

| CLKO      | 32                     | 50              | A33             | 72                       | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1      | 31                     | 49              | B28             | 71                       | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                               |

| OSC2      | 32                     | 50              | A33             | 72                       | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes.                                              |

| SOSCI     | 47                     | 72              | B41             | 105                      | Ι           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                |

| SOSCO     | 48                     | 73              | A49             | 106                      | 0           | — —            | 32.768 low-power oscillator crystal output.                                                                                                                                                   |

| REFCLKI1  | PPS                    | PPS             | PPS             | PPS                      | I           | —              | Reference Clock Generator Inputs 1-4                                                                                                                                                          |

| REFCLKI3  | PPS                    | PPS             | PPS             | PPS                      | I           | _              |                                                                                                                                                                                               |

| REFCLKI4  | PPS                    | PPS             | PPS             | PPS                      | Ι           | -              | 1                                                                                                                                                                                             |

| REFCLKO1  | PPS                    | PPS             | PPS             | PPS                      | 0           | -              | Reference Clock Generator Outputs 1-4                                                                                                                                                         |

| REFCLKO3  | PPS                    | PPS             | PPS             | PPS                      | 0           | —              | ]                                                                                                                                                                                             |

| REFCLKO4  | PPS                    | PPS             | PPS             | PPS                      | 0           | —              | 1                                                                                                                                                                                             |

| Legend: ( | CMOS = CI              | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power                                                                                                                                                                        |

#### TABLE 1-2: OSCILLATOR PINOUT I/O DESCRIPTIONS

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input P O = Output I = PPS = Peripheral Pin Select

I = Input

### TABLE 1-3: IC1 THROUGH IC9 PINOUT I/O DESCRIPTIONS

|          |                        | Pin Nu          | mber            |                          |             |                |                          |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|--------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description              |

|          |                        |                 |                 |                          | Input       | Capture        |                          |

| IC1      | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | Input Capture Inputs 1-9 |

| IC2      | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | 1                        |

| IC3      | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | 1                        |

| IC4      | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | ]                        |

| IC5      | PPS                    | PPS             | PPS             | PPS                      | I           | ST             |                          |

| IC6      | PPS                    | PPS             | PPS             | PPS                      | I           | ST             |                          |

| IC7      | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | 1                        |

| IC8      | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | 1                        |

| IC9      | PPS                    | PPS             | PPS             | PPS                      | Ι           | ST             | 1                        |

| Legend:  | CMOS = CI              | MOS-comp        | atible input    | or output                |             | Analog =       | Analog input P = Power   |

Legend:

CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select P = Power I = Input

| TABLE 1-13: | EBI PINOUT I/O DESCRIPTIONS (CONTINUED) |

|-------------|-----------------------------------------|

|-------------|-----------------------------------------|

|          |                        | Pin Nu          | mber            |                          |             |                                     |                                        |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|-------------------------------------|----------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type                      | Description                            |

| EBIOE    | _                      | 9               | A7              | 13                       | 0           | _                                   | External Bus Interface Output Enable   |

| EBIRDY1  | —                      | <u> </u>        |                 |                          | I           | ST                                  | External Bus Interface Ready Input     |

| EBIRDY2  | —                      | 58              | A39             | 84                       | I           | ST                                  |                                        |

| EBIRDY3  |                        | 57              | B45             | 116                      | Ι           | ST                                  |                                        |

| EBIRP    | _                      | _               | _               | 45                       | 0           | _                                   | External Bus Interface Flash Reset Pin |

| EBIWE    | — 8 B5 12              |                 | 12              | 0                        | _           | External Bus Interface Write Enable |                                        |

| Legend:  | CMOS = CI              | MOS-comp        | atible input    | or output                |             | Analog =                            | Analog input P = Power                 |

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog inputP = PowerO = OutputI = InputPPS = Peripheral Pin Select

| 1            |                   |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 |                   |                  | —                |  |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x            | R/W-x            |  |

| 23:16        |                   |                   |                   |                   |                   |                   | CAUS             | E<5:4>           |  |

|              | —                 | _                 | _                 | _                 | _                 | _                 | E                | V                |  |

|              | R/W-x             | R/W-x             | R/W-x             | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         |                   | CAUSE             | <3:0>             |                   |                   |                   |                  |                  |  |

|              | Z                 | 0                 | U                 | I                 |                   | _                 | _                | _                |  |

|              | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0              | U-0              |  |

| 7:0          |                   |                   |                   | FLAGS<4:0>        |                   |                   |                  |                  |  |

|              |                   | V                 | Z                 | 0                 | U                 | I                 |                  | _                |  |

#### REGISTER 3-8: FEXR: FLOATING POINT EXCEPTIONS STATUS REGISTER; CP1 REGISTER 26

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-18 Unimplemented: Read as '0'

bit 17-12 **CAUSE<5:0>:** FPU Exception Cause bits These bits indicated the exception conditions that arise during execution of an FPU arithmetic instruction.

- bit 17 E: Unimplemented Operation bit

- bit 16 V: Invalid Operation bit

- bit 15 **Z:** Divide-by-Zero bit

- bit 14 **O:** Overflow bit

- bit 13 **U:** Underflow bit

- bit 12 I: Inexact bit

- bit 11-7 Unimplemented: Read as '0'

- bit 6-2 FLAGS<4:0>: FPU Flags bits

These bits show any exception conditions that have occurred for completed instructions since the flag was last reset by software.

- bit 6 V: Invalid Operation bit

- bit 4 **Z:** Divide-by-Zero bit

- bit 4 O: Overflow bit

- bit 3 U: Underflow bit

- bit 2 I: Inexact bit

- bit 1-0 Unimplemented: Read as '0'

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>()                  |                                 | Ð         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

|                             | OFF032                          | 31:16     | _     | _     | -     | —     | -     | _     | -    | _          | _    | _    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0500                        | OFF032                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0504                        | OFF033                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0504                        | 066033                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF034                          | 31:16     | —     |       | —     | _     | _     | -     | _    |            | —    |      | _    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0508                        | 0FF034                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF035                          | 31:16     | —     |       | _     | _     |       |       |      | —          | _    |      | —    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0500                        | 0FF035                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF036                          | 31:16     | —     |       | —     | _     |       |       |      |            | —    |      | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0500                        | 066030                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 05D4                        | OFF037                          | 31:16     | —     |       | —     | _     |       |       |      | —          | —    |      | —    | —    | _    | _    | VOFF< | 17:16> | 0000       |

| 0304                        | 011037                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0508                        | OFF038                          | 31:16     | _     | -     | —     | —     | -     | -     | -    | _          | _    | -    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0300                        | 011030                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     | —      | 0000       |

| 05DC                        | OFF039                          | 31:16     | _     | —     | -     | —     | _     | —     | _    | —          | _    |      | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0300                        | 011039                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0550                        | OFF040                          | 31:16     | _     | _     |       |       |       |       |      | —          | _    |      | —    | _    |      |      | VOFF< | 17:16> | 0000       |

| 0520                        | 011040                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     |        | 0000       |

| 05E4                        | OFF041                          | 31:16     | _     | —     | -     | —     | _     | —     | _    | —          | _    |      | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0564                        | 011041                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 05E8                        | OFF042                          | 31:16     | _     | —     | -     | —     | _     | —     | _    | —          | _    |      | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0520                        | 011042                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     |        | 0000       |

| 05EC                        | OFF043                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0520                        | 011043                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 05E0                        | OFF044                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 001 0                       | 011044                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     | —      | 0000       |

| 05F4                        | OFF045                          | 31:16     | —     | —     | —     | _     | _     | _     | _    | —          | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0014                        | 011040                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      | -    | -     |        | 0000       |

| 0558                        | OFF046                          | 31:16     | —     | _     | -     |       | _     | _     | —    | —          | _    | _    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 05-0                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

© 2015-2016 Microchip Technology Inc.

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

- Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

- Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

<sup>2:</sup>

## TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

| ss                          |                  |               |       |                                                                                                                 |       |       |       |        |              |        | Bits            |          |             |      |            |             |        |       |            |

|-----------------------------|------------------|---------------|-------|-----------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|--------------|--------|-----------------|----------|-------------|------|------------|-------------|--------|-------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                                                                                                           | 29/13 | 28/12 | 27/11 | 26/10  | 25/9         | 24/8   | 23/7            | 22/6     | 21/5        | 20/4 | 19/3       | 18/2        | 17/1   | 16/0  | All Resets |

| 3248                        | USB              | 31:16         |       |                                                                                                                 |       |       |       |        |              | DMA    | ADDR<31:16      | >        |             |      |            |             |        |       | 0000       |

| 3248                        | DMA5A            | 15:0          |       |                                                                                                                 |       |       |       |        |              | DM     | ADDR<15:0       | •        |             |      |            |             |        |       | 0000       |

| 324C                        | USB              | 31:16         |       |                                                                                                                 |       |       |       |        |              | DMA    | COUNT<31:10     | i>       |             |      |            |             |        |       | 0000       |

| 0240                        | DMA5N            | 15:0          |       |                                                                                                                 |       | -     | •     |        |              | DMA    | COUNT<15:0      | >        |             |      |            |             |        |       | 0000       |

| 3254                        | USB              | 31:16         | _     | _                                                                                                               | -     | —     |       | _      | —            | -      | _               | —        | —           | -    | -          | -           | _      | -     | 0000       |

|                             | DMA6C            | 15:0          | —     | —                                                                                                               | —     |       | -     | DMABR  | STM<1:0>     | DMAERR |                 |          | EP<3:0>     |      | DMAIE      | DMAMODE     | DMADIR | DMAEN |            |

| 3258                        | USB<br>DMA6A     | 31:16         |       |                                                                                                                 |       |       |       |        |              |        | ADDR<31:16      |          |             |      |            |             |        |       | 0000       |

|                             |                  | 15:0          |       |                                                                                                                 |       |       |       |        |              |        | ADDR<15:0       |          |             |      |            |             |        |       | 0000       |

| 325C                        | USB<br>DMA6N     | 31:16         |       |                                                                                                                 |       |       |       |        |              |        | COUNT<31:10     |          |             |      |            |             |        |       | 0000       |

| $\vdash$                    |                  | 15:0          |       |                                                                                                                 |       | _     | 1     |        |              |        | COUNT<15:0      |          |             |      |            |             |        |       | 0000       |

| 3264                        | USB<br>DMA7C     | 31:16<br>15:0 | _     |                                                                                                                 | _     |       | _     |        | <br>STM<1:0> |        | —               | -        | <br>EP<3:0> | _    | —<br>DMAIE | <br>DMAMODE |        |       | 0000       |

|                             |                  | 31:16         | —     | _                                                                                                               | —     |       | _     | DIMABR | 51M<1:0>     | DMAERR | ADDR<31:16      |          | EP<3:0>     |      | DIVIAIE    | DMAMODE     | DMADIR | DMAEN | 0000       |

| 3268                        | USB<br>DMA7A     | 15:0          |       | DMAADDR<1150> 0000                                                                                              |       |       |       |        |              |        |                 |          |             |      |            |             |        |       |            |

|                             | USB              | 31:16         |       | DMAADDR<15:0> 0000 DMACOUNT<31:16> 0000                                                                         |       |       |       |        |              |        |                 |          |             |      |            |             |        |       |            |

| 326C                        | DMA7N            | 15:0          |       | DMACOUNT<31:16> 0000 DMACOUNT<15:0> 0000                                                                        |       |       |       |        |              |        |                 |          |             |      |            |             |        |       |            |

|                             | USB              | 31:16         | _     | _                                                                                                               |       | _     | _     | _      | _            | _      | _               | _        | _           | _    | _          | _           | _      | _     | 0000       |

| 3274                        | DMA8C            | 15:0          | _     | _                                                                                                               | _     | _     | _     | DMABR  | STM<1:0>     | DMAERR |                 | DMA      | EP<3:0>     |      | DMAIE      | DMAMODE     | DMADIR | DMAEN | 0000       |

| 0070                        | USB              | 31:16         |       |                                                                                                                 |       |       |       | 1      |              | DMA    | ADDR<31:16      | >        |             |      | 1          |             | 1      | J     | 0000       |

| 3278                        | DMA8A            | 15:0          |       |                                                                                                                 |       |       |       |        |              | DM     | ADDR<15:0       | •        |             |      |            |             |        |       | 0000       |

| 327C                        | USB              | 31:16         |       |                                                                                                                 |       |       |       |        |              | DMA    | COUNT<31:10     | i>       |             |      |            |             |        |       | 0000       |

| 3270                        | DMA8N            | 15:0          |       |                                                                                                                 |       |       |       |        |              | DMA    | COUNT<15:0      | >        |             |      |            |             |        |       | 0000       |

| 3304                        | USB              | 31:16         | —     |                                                                                                                 | —     | _     | —     | _      | —            | —      | _               | —        | _           | -    | —          | _           | _      | —     | 0000       |

| 5504                        | E1RPC            | 15:0          |       |                                                                                                                 |       | -     |       | -      |              | RQP    | KTCNT<15:0      | >        |             | -    |            |             |        |       | 0000       |

| 3308                        | USB              | 31:16         | —     | —                                                                                                               | —     | —     | -     | —      | —            | —      | —               | —        | -           | -    | —          | -           | —      | —     | 0000       |

|                             | E2RPC            | 15:0          |       |                                                                                                                 |       |       |       |        |              | RQP    | KTCNT<15:0      | >        | 1           |      |            |             |        |       | 0000       |

| 330C                        | USB              | 31:16         | _     | _                                                                                                               | —     |       | —     |        | —            | —      |                 |          | _           | _    | _          | _           | _      | —     | 0000       |

|                             | E3RPC            | 15:0          |       |                                                                                                                 |       |       | 1     |        |              |        | KTCNT<15:0      |          |             |      |            |             |        |       | 0000       |

| 3310                        | USB<br>E4RPC     | 31:16         | _     |                                                                                                                 |       |       |       |        |              |        |                 |          |             |      |            |             |        |       |            |

| $\vdash$                    |                  | 15:0          |       |                                                                                                                 |       |       |       |        |              |        | KTCNT<15:0      |          |             |      |            |             |        |       | 0000       |

| 3314                        | USB<br>E5RPC     | 31:16<br>15:0 | —     | _                                                                                                               | —     | _     | —     | _      | —            |        |                 | _        | —           | —    | _          | —           | —      | —     | 0000       |

| $\vdash$                    |                  |               |       |                                                                                                                 |       |       |       |        |              |        | KTCNT<15:0      |          |             |      |            |             |        |       | 0000       |

| 3318                        | USB<br>E6RPC     | 31:16<br>15:0 | —     | _                                                                                                               | —     | _     | _     | _      | _            |        | —<br>KTCNT<15:0 | _        | _           | _    | _          | _           | _      | —     | 0000       |

| $\vdash$                    |                  | 31:16         | _     | _                                                                                                               | _     |       |       | _      |              |        |                 | <u> </u> |             | _    | _          | _           |        | _     | 0000       |

| 331C                        | USB<br>E7RPC     | 15:0          | _     | _                                                                                                               |       |       | _     |        |              | ROP    | <br>KTCNT<15:0  |          | _           | _    |            | _           |        |       | 0000       |

| 1                           |                  | 10.0          |       | RQPKICNI<15:0> 0000<br>n value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |       |       |       |        |              |        |                 |          |             |      |            |             |        |       |            |

Legend: Note x = unknownDevice mode.

Host mode.

1: 2: 3: 4: Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

## TABLE 12-17: PORTH REGISTER MAP FOR 124-PIN DEVICES ONLY

| ess                         | -                               | Ø         |       |       |               |               |                |               |              | Bits         |      |              |              |              |      |      |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|----------------|---------------|--------------|--------------|------|--------------|--------------|--------------|------|------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11          | 26/10         | 25/9         | 24/8         | 23/7 | 22/6         | 21/5         | 20/4         | 19/3 | 18/2 | 17/1         | 16/0         | All<br>Resets |

| 0700                        | ANSELH                          | 31:16     |       |       | _             | —             |                | -             | _            | —            |      | —            | —            | —            | _    | —    | —            |              | 0000          |

| 0100                        | / TOLET                         | 15:0      | —     | _     | _             | —             | —              | -             | -            | —            | _    | ANSH6        | ANSH5        | ANSH4        | -    | —    | ANSH1        | ANSH0        | 0073          |

| 0710                        | TRISH                           | 31:16     | —     | —     | —             | —             | —              | —             | _            | —            | —    |              | —            | —            | —    | —    | —            | —            | 0000          |

| 0710                        | INION                           | 15:0      | —     | —     | TRISH13       | TRISH12       | —              | TRISH10       | TRISH9       | TRISH8       | —    | TRISH6       | TRISH5       | TRISH4       | —    | —    | TRISH1       | TRISH0       | 3773          |

| 0720                        | PORTH                           | 31:16     | —     | —     | _             | —             | _              |               |              | —            | _    |              | —            | —            | _    | —    |              | —            | 0000          |

| 0720                        | 1 OKIII                         | 15:0      | —     | —     | RH13          | RH12          | —              | RH10          | RH9          | RH8          | —    | RH6          | RH5          | RH4          | -    | —    | RH1          | RH0          | xxxx          |

| 0730                        | LATH                            | 31:16     | —     | —     | —             | —             | —              | —             | _            | —            | —    | —            | —            | —            | -    | —    | —            | —            | 0000          |

| 0730                        | LAIN                            | 15:0      | —     | —     | LATH13        | LATH12        | —              | LATH10        | LATH9        | LATH8        | —    | LATH6        | LATH5        | LATH4        | -    | —    | LATH1        | LATH0        | xxxx          |

| 0740                        | ODCH                            | 31:16     | _     | -     |               | _             | _              |               |              | _            | _    | _            | -            | —            |      | _    | _            | _            | 0000          |

| 0740                        | ODCH                            | 15:0      | _     | -     | ODCH13        | ODCH12        | _              | ODCH10        | ODCH9        | ODCH8        | _    | ODCH6        | ODCH5        | ODCH4        |      | _    | ODCH1        | ODCH0        | 0000          |

| 0750                        | CNPUH                           | 31:16     | _     |       | -             | _             | —              |               |              | _            | —    | —            | _            | —            |      | _    | —            | —            | 0000          |

| 0750                        | CINFULL                         | 15:0      | _     |       | CNPUH13       | CNPUH12       | —              | CNPUH10       | CNPUH9       | CNPUH8       | —    | CNPUH6       | CNPUH5       | CNPUH4       |      | _    | CNPUH1       | CNPUH0       | 0000          |

| 0760                        | CNPDH                           | 31:16     | _     |       | -             | _             | —              |               |              | _            | —    | —            | _            | —            |      | _    | —            | —            | 0000          |

| 0700                        | CINEDIT                         | 15:0      | —     |       | CNPDH13       | CNPDH12       | _              | CNPDH10       | CNPDH9       | CNPDH8       | —    | CNPDH6       | CNPDH5       | CNPDH4       |      | —    | CNPDH1       | CNPDH0       | 0000          |

|                             |                                 | 31:16     | _     |       | -             | _             | —              |               |              | _            | —    | —            | _            | —            |      | _    | —            | —            | 0000          |

| 0770                        | CNCONH                          | 15:0      | ON    | Ι     | _             | -             | EDGE<br>DETECT | -             | -            | —            | —    | -            | —            | _            | -    | —    | _            | _            | 0000          |

| 0700                        |                                 | 31:16     | _     | _     | -             | —             | —              |               | -            | _            | _    | —            | _            | _            |      |      | _            | _            | 0000          |

| 0780                        | CNENH                           | 15:0      | _     | _     | CNENH13       | CNENH12       | _              | CNENH10       | CNENH9       | CNENH8       | _    | CNENH6       | CNENH5       | CNENH4       | _    | —    | CNENH1       | CNENH0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _             | _             | _              | _             | _            | _            | _    | —            | —            | —            | _    | —    | —            | _            | 0000          |

| 0790                        | CNSTATH                         | 15:0      | _     | _     | CN<br>STATH13 | CN<br>STATH12 | _              | CN<br>STATH10 | CN<br>STATH9 | CN<br>STATH8 | _    | CN<br>STATH6 | CN<br>STATH5 | CN<br>STATH4 | -    | _    | CN<br>STATH1 | CN<br>STATH0 | 0000          |

| 0740                        |                                 | 31:16     | _     | _     | _             | —             | _              | -             | -            | —            | _    | — —          | —            | —            | _    | —    | _            | _            | 0000          |

| 07A0                        | CNNEH                           | 15:0      | _     | _     | CNNEH13       | CNNEH12       | _              | CNNEH10       | CNNEH9       | CNNEH8       | _    | CNNEH6       | CNNEH5       | CNNEH4       | _    | _    | CNNEH1       | CNNEH0       | 0000          |

|                             | 0.1511                          | 31:16     |       |       |               |               |                |               | _            |              |      |              |              |              |      |      | _            |              | 0000          |

| 07B0                        | CNFH                            | 15:0      | _     | _     | CNFH13        | CNFH12        | _              | CNFH10        | CNFH9        | CNFH8        | _    | CNFH6        | CNFH5        | CNFH4        | _    | _    | CNFH1        | CNFH0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

#### **SQI Control Registers** 20.1

## TABLE 20-1: SERIAL QUADRATURE INTERFACE (SQI) REGISTER MAP

| ess                         |                   |               |       |                            |         |           |        |               |              | В            | its            |               |             |              |                |               |               |               | s          |

|-----------------------------|-------------------|---------------|-------|----------------------------|---------|-----------|--------|---------------|--------------|--------------|----------------|---------------|-------------|--------------|----------------|---------------|---------------|---------------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name  | Bit Range     | 31/15 | 30/14                      | 29/13   | 28/12     | 27/11  | 26/10         | 25/9         | 24/8         | 23/7           | 22/6          | 21/5        | 20/4         | 19/3           | 18/2          | 17/1          | 16/0          | All Resets |

| 2000                        | SQI1              | 31:16         | _     | —                          |         | —         | _      | —             | —            | —            | DUN            | IMYBYTES<     | :2:0>       | AD           | DRBYTES<2      | 2:0>          | READOPC       | CODE<7:6>     | 0000       |

| 2000                        | XCON1             | 15:0          |       |                            | READOPO | CODE<5:0> |        |               | TYPED/       | ATA<1:0>     | TYPEDUN        | /MY<1:0>      | TYPEMC      | DE<1:0>      | TYPEAD         | DR<1:0>       | TYPECI        | MD<1:0>       | 0000       |

| 2004                        | SQI1              | 31:16         | —     | —                          | _       | —         | _      | —             | —            | —            | —              | —             | _           | —            | —              | —             | _             | —             | 0000       |

|                             | XCON2             | 15:0          | _     | _                          | _       | _         | DEVSE  | L<1:0>        | MODEBY       | TES<1:0>     |                |               |             | MODECO       | DDE<7:0>       |               |               |               | 0000       |

| 2008                        | SQI1CFG           | 31:16         | -     | _                          | _       | -         | —      | _             | CSEN         | l<1:0>       | SQIEN          | —             | DATAE       | N<1:0>       | CON<br>FIFORST | RXFIFO<br>RST | TXFIFO<br>RST | RESET         | 0000       |

|                             |                   | 15:0          | _     | —                          | —       | BURSTEN   | _      | HOLD          | WP           | —            | —              | —             | LSBF        | CPOL         | CPHA           |               | MODE<2:0>     | •             | 0000       |

| 200C                        | SQI1CON           | 31:16         | —     | —                          | —       | -         | —      | —             | —            | SCHECK       | —              | DASSERT       | DEVSE       | L<1:0>       | LANEMC         | DE<1:0>       | CMDIN         | IT<1:0>       | 0000       |

|                             |                   | 15:0          |       |                            |         |           |        |               |              | TXRXCOL      | JNT<15:0>      |               |             |              |                |               |               |               | 0000       |

| 2010                        | SQI1              | 31:16         | —     | —                          | —       | -         | —      | —             | —            | —            | _              | _             | _           | _            | _              |               | LKDIV<10:8    |               | 0000       |

|                             | CLKCON            | 15:0          |       | CLKDIV<7:0> STABLE EN 0000 |         |           |        |               |              |              |                |               |             |              |                |               |               |               |            |

| 2014                        | SQI1              | 31:16         | —     | _                          |         | -         | —      | —             | —            | —            | _              | _             | —           | —            | —              | —             | —             | —             | 0000       |

|                             | CMDTHR            | 15:0          | —     | _                          | _       |           | TX     | CMDTHR<4      | :0>          |              | —              | _             | _           |              |                | CMDTHR<4      | 4:0>          |               | 0000       |

| 2018                        | SQI1              | 31:16         |       |                            |         |           |        |               |              |              |                |               |             |              |                |               |               |               |            |

|                             | INTTHR            | 15:0          | —     | -                          | -       |           |        | (INTTHR<4:    |              |              | _              | _             | _           |              |                | (INTTHR<4:    | 1             | 1             | 0000       |

| 201C                        | SQI1              | 31:16         | _     | _                          | _       | _         | _      | -             | -            | -            | -              | -             | —           | -            | -              | -             | -             | —<br>—        | 0000       |

| 2010                        | INTEN             | 15:0          | _     | _                          | _       | _         | DMAEIE | PKT<br>COMPIE | BD<br>DONEIE | CON<br>THRIE | CON<br>EMPTYIE | CON<br>FULLIE | RX<br>THRIE | RX<br>FULLIE | RX<br>EMPTYIE  | TX<br>THRIE   | TX<br>FULLIE  | TX<br>EMPTYIE | 0000       |

| 0000                        | SQI1              | 31:16         | —     | —                          | —       | _         | —      | —             | —            | —            | —              | —             | —           | —            | —              | —             | —             | —             | 0000       |

| 2020                        | INTSTAT           | 15:0          | —     | _                          | —       | -         | DMAEIF | PKT<br>COMPIF | BD<br>DONEIF | CON<br>THRIF | CON<br>EMPTYIF | CON<br>FULLIF | RX<br>THRIF | RX<br>FULLIF | RX<br>EMPTYIF  | TX<br>THRIF   | TX<br>FULLIF  | TX<br>EMPTYIF | 0000       |

| 2024                        | SQI1              | 31:16         |       |                            |         |           |        |               |              | TXDATA       |                |               |             |              |                |               |               |               | 0000       |

|                             | TXDATA            | 15:0          |       |                            |         |           |        |               |              | TXDAT        |                |               |             |              |                |               |               |               | 0000       |

| 2028                        | SQI1              | 31:16         |       |                            |         |           |        |               |              | RXDATA       |                |               |             |              |                |               |               |               | 0000       |

|                             | RXDATA            | 15:0          |       |                            | i       |           |        | i             |              | RXDAT        | A<15:0>        |               |             |              |                |               |               |               | 0000       |

| 202C                        | SQI1<br>STAT1     | 31:16         | _     | _                          | _       |           | _      | _             | _            | _            |                |               |             |              | REE<7:0>       |               |               |               | 0000       |

|                             | -                 | 15:0          | _     | _                          | _       |           | _      | _             | _            | _            |                |               |             |              | CNT<7:0>       |               | 0,4507        |               | 0000       |

| 2030                        | SQI1<br>STAT2     | 31:16         |       |                            |         |           |        |               |              |              |                |               | 0000        |              |                |               |               |               |            |

|                             | -                 | 15:0          | —     | _                          |         | _         |        |               |              |              |                |               | SDID2       | -            |                |               | RXUN          | 1x0v          | 00x0       |

| 2034                        | SQI1<br>BDCON     | 31:16<br>15:0 |       |                            | _       | _         | _      |               |              | _            | _              |               | _           |              |                | —<br>START    | POLLEN        | —<br>DMAEN    | 0000       |

|                             |                   | 31:16         | _     | _                          | _       | _         | _      | _             | _            |              | <br>DDR<31:16> | _             | _           | —            | _              | SIARI         | POLLEN        | DIVIAEN       | 0000       |

| 2038                        | SQI1BD<br>CURADD  | 15:0          |       |                            |         |           |        |               |              |              | DDR<31:16>     |               |             |              |                |               |               |               | 0000       |

|                             |                   | 31:16         |       |                            |         |           |        |               |              |              | R<31:16>       |               |             |              |                |               |               |               | 0000       |

| 2040                        | SQI1BD<br>BASEADD | 15:0          |       |                            |         |           |        |               |              |              |                |               |             |              |                |               |               |               |            |

|                             |                   | 15.0          |       | BDADDR<15:0> 0000          |         |           |        |               |              |              |                |               |             |              |                |               |               |               |            |

|              | 1120-0.03         |                   |                   |                   |                   | <b>_</b>          |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | —                 |                   |                   | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | —                 | _                 |                   | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | —                 | DMAEIE            | PKTCOMPIE         | BDDONEIE         | CONTHRIE         |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CONEMPTYIE        | CONFULLIE         | RXTHRIE           | RXFULLIE          | RXEMPTYIE         | TXTHRIE           | TXFULLIE         | TXEMPTYIE        |

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

HS = Hardware Set

W = Writable bit

'1' = Bit is set

## REGISTER 20-8: SQI1INTEN: SQI INTERRUPT ENABLE REGISTER

| bit 10   | DMAEIE: DMA Bus Error Interrupt Enable bit <ol> <li>Interrupt is enabled</li> <li>Interrupt is disabled</li> <li>PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit</li> <li>Interrupt is enabled</li> <li>Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ol> |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10 I | <ul> <li>0 = Interrupt is disabled</li> <li>PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit</li> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                              |

| bit 10   | <ul> <li>PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit</li> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                                                                 |

| bit 9    | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                                                                                                                                                |

| bit 9    | <ul> <li>Interrupt is disabled</li> <li>BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit</li> </ul>                                                                                                                                                                                                                      |

| bit 9 I  | BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit                                                                                                                                                                                                                                                                         |

| :        |                                                                                                                                                                                                                                                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                                   |

| l        | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

| bit 8    | CONTHRIE: Control Buffer Threshold Interrupt Enable bit                                                                                                                                                                                                                                                                           |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

| bit 7    | CONEMPTYIE: Control Buffer Empty Interrupt Enable bit                                                                                                                                                                                                                                                                             |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | CONFULLIE: Control Buffer Full Interrupt Enable bit                                                                                                                                                                                                                                                                               |

|          | This bit enables an interrupt when the receive FIFO buffer is full.                                                                                                                                                                                                                                                               |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | RXTHRIE: Receive Buffer Threshold Interrupt Enable bit                                                                                                                                                                                                                                                                            |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | RXFULLIE: Receive Buffer Full Interrupt Enable bit                                                                                                                                                                                                                                                                                |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                                   |

|          | RXEMPTYIE: Receive Buffer Empty Interrupt Enable bit                                                                                                                                                                                                                                                                              |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                   |

|          | TXTHRIE: Transmit Threshold Interrupt Enable bit                                                                                                                                                                                                                                                                                  |

|          | -                                                                                                                                                                                                                                                                                                                                 |

|          | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                   |

|          | TXFULLIE: Transmit Buffer Full Interrupt Enable bit                                                                                                                                                                                                                                                                               |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

|          | TXEMPTYIE: Transmit Buffer Empty Interrupt Enable bit                                                                                                                                                                                                                                                                             |

|          | 1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                          |

|          | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                         |

Legend:

R = Readable bit

-n = Value at POR

| REGISTE | R 21-2: I2CxSTAT: I <sup>2</sup> C STATUS REGISTER (CONTINUED)                                                                                                                                                                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <ul> <li>D_A: Data/Address bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Indicates that the last byte received was data</li> <li>0 = Indicates that the last byte received was device address</li> <li>Hardware clear at device address match. Hardware set by reception of slave byte.</li> </ul> |

| bit 4   | P: Stop bit                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                                                                                                               |

| bit 3   | S: Start bit                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                                                                                         |

| bit 2   | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                              |

|         | 1 = Read – indicates data transfer is output from slave<br>0 = Write – indicates data transfer is input to slave<br>Hardware set or clear after reception of $I^2C$ device address byte.                                                                                                                       |

| bit 1   | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul>                                                                                    |

| bit 0   | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                           |