Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efm100-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-7: SYSTEM BUS REGISTER MAP

| sse                        |                  |           | Bits  |       |        |        |        |        |       |       |       |       |       |       |       |       |       |              |               |

|----------------------------|------------------|-----------|-------|-------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|---------------|

| Virtual Addre:<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13  | 28/12  | 27/11  | 26/10  | 25/9  | 24/8  | 23/7  | 22/6  | 21/5  | 20/4  | 19/3  | 18/2  | 17/1  | 16/0         | All<br>Resets |

| 0510                       |                  | 31:16     | —     | —     | _      | —      | —      | _      | _     | _     | _     | —     | _     | —     |       | -     | —     | _            | 0000          |

| 0510                       | SBFLAG           | 15:0      | —     | _     | T13PGV | T12PGV | T11PGV | T10PGV | T9PGV | T8PGV | T7PGV | T6PGV | T5PGV | T4PGV | T3PGV | T2PGV | T1PGV | <b>T0PGV</b> | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-8: SYSTEM BUS TARGET 0 REGISTER MAP

| sse                         |                  |           |       |       |       |          |          |       |       |      | Bits      |       |           |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|----------|----------|-------|-------|------|-----------|-------|-----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7      | 22/6  | 21/5      | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| 8020                        | SBT0ELOG1        | 31:16     | MULTI | —     | -     | —        |          | CODE  | <3:0> |      | —         | -     | —         | _    | —      | —      | —       | _      | 0000          |

| 0020                        | SBIULLOGI        | 15:0      |       |       |       | INIT     | TID<7:0> |       |       |      |           | REGIO | N<3:0>    |      | —      | C      | MD<2:0> |        | 0000          |

| 8024                        | SBT0ELOG2        | 31:16     | _     | —     | -     | —        | -        | _     | -     | —    | —         | —     | —         | _    | —      | —      | —       | _      | 0000          |

| 0024                        | SBIULLOGZ        | 15:0      | _     | —     |       | —        | _        |       | _     | —    | _         | _     | —         |      | —      | _      | GROU    | P<1:0> | 0000          |

| 8028                        | SBT0ECON         | 31:16     | _     | _     | _     | —        | -        | _     | _     | ERRP | _         | _     | _         | _    | —      | _      | —       | -      | 0000          |

| 0020                        | SBIOLOON         | 15:0      | —     | —     |       | —        | _        |       | _     | _    | _         | _     | —         |      | —      | —      |         | _      | 0000          |

| 8030                        | SBT0ECLRS        | 31:16     | _     | —     |       | —        | _        | —     | _     | _    | _         | _     | _         |      | —      | —      |         |        | 0000          |

| 0000                        | SBIULCERG        | 15:0      | —     | —     |       | —        | _        |       | _     | _    | _         | _     | —         |      | —      | —      |         | CLEAR  | 0000          |

| 8038                        | SBT0ECLRM        | 31:16     | _     | —     |       | —        | _        |       | _     | _    | _         | _     | —         |      | —      | _      |         | _      | 0000          |

| 0000                        | OBTOLCER         | 15:0      | —     | —     | _     | —        | —        | —     | —     | _    | —         | —     | —         | —    | —      | —      | —       | CLEAR  | 0000          |

| 8040                        | SBT0REG0         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6>  |       |           |      |        |        |         |        | xxxx          |

| 0040                        | OBTOREGO         | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | —    |           |       | SIZE<4:0: | >    |        | —      | —       | _      | xxxx          |

| 8050                        | SBT0RD0          | 31:16     | _     | —     | -     | —        | -        | —     | _     | —    | _         | —     | —         | —    | —      | —      | —       | _      | xxxx          |

| 0000                        | CETOREO          | 15:0      |       | —     | -     | —        | -        | —     | -     | _    | —         | _     | —         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8058                        | SBT0WR0          | 31:16     | _     | —     | -     | —        | -        | —     | _     | —    | _         | —     | —         | —    | —      | —      | —       | _      | xxxx          |

| 0000                        | <b>OBIONIN</b>   | 15:0      | _     | —     | —     | —        | —        | —     | —     | —    | —         | —     | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8060                        | SBT0REG1         | 31:16     |       |       |       |          |          |       |       | BA   | SE<21:6>  |       |           |      |        |        | •       |        | xxxx          |

| 0000                        |                  | 15:0      |       |       | BA    | \SE<5:0> |          |       | PRI   | _    | SIZE<4:0> |       |           |      |        | _      | xxxx    |        |               |

| 8070                        | SBT0RD1          | 31:16     | _     | —     | _     | —        | —        | —     | _     | _    | _         | _     |           |      | —      | —      | —       | _      | xxxx          |

| 00.0                        | 5010101          | 15:0      | _     | —     | _     | —        | —        | —     | _     | _    | _         | _     |           |      | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 8078                        | SBT0WR1          | 31:16     |       | —     | _     | —        | _        | _     | _     | _    | _         | _     | _         | _    | _      | _      |         | —      | xxxx          |

| 00.0                        | 50101111         | 15:0      | _     | —     | —     | —        | —        | —     |       |      | —         | —     | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   |                   |                   | DATA<             | 31:24>            |                   |                  |                  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23.10        |                   |                   |                   | DATA<             | 23:16>            |                   | R/W-0            |                  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | DATA<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | DATA<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 11-12: USBFIFOX: USB FIFO DATA REGISTER 'x' ('x' = 0-7)

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-0 DATA<31:0>: USB Transmit/Receive FIFO Data bits

Writes to this register loads data into the TxFIFO for the corresponding endpoint. Reading from this register unloads data from the RxFIFO for the corresponding endpoint.

Transfers may be 8-bit, 16-bit or 32-bit as required, and any combination of access is allowed provided the data accessed is contiguous. However, all transfers associated with one packet must be of the same width so that data is consistently byte-, word- or double-word aligned. The last transfer may contain fewer bytes than the previous transfers in order to complete an odd-byte or odd-word transfer.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 | -                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | _                 | -                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 |                   | _                 | EDGEDETECT        | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   |                  |                  |

#### REGISTER 12-3: CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A - K)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Change Notice (CN) Control ON bit

1 = CN is enabled

0 = CN is disabled

#### bit 14-12 Unimplemented: Read as '0'

- bit 11 EDGEDETECT: Change Notification Style bit

- 1 = Edge Style. Detect edge transitions (CNFx used for CN Event).

- 0 = Mismatch Style. Detect change from last PORTx read (CNSTATx used for CN Event).

- bit 10-0 Unimplemented: Read as '0'

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 22:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 7.0       | R-0, HC, HS       | R-0, HC, HS       | R-0, HC, HS       | U-0               | U-0               | U-0               | U-0              | R-0, HC, HS      |

| 7:0       | BAD1              | BAD2              | DMTEVENT          | _                 |                   | _                 | _                | WINOPN           |

#### REGISTER 15-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:           | HC = Hardware Cleared | HS = Hardware Set                |            |  |  |  |

|-------------------|-----------------------|----------------------------------|------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as   | '0'        |  |  |  |

| -n = Value at POR | '1' = Bit is set      | 0' = Bit is cleared $x = Bit is$ | is unknown |  |  |  |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP1<7:0> value was not detected                                                                                     |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer even was not detected                                                                                             |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

NOTES:

#### TABLE 18-2: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 9 REGISTER MAP (CONTINUED)

| ess                         |                                 | 0             |              |                                        |       |       |       |       |      | Bi    |        | -    |              | -     |        |      |          |      |              |

|-----------------------------|---------------------------------|---------------|--------------|----------------------------------------|-------|-------|-------|-------|------|-------|--------|------|--------------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14                                  | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5         | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

| 4A00                        | OC6CON                          | 31:16         | _            | _                                      | _     | _     | _     | _     | _    | _     | _      | _    | —            | —     |        | _    | —        | _    | 0000         |

|                             |                                 | 15:0          | ON           | ON - SIDL OC32 OCFLT OCTSEL OCM<2:0> 0 |       |       |       |       |      |       |        |      | 0000         |       |        |      |          |      |              |

| 4A10                        | OC6R                            | 31:16<br>15:0 |              | OC6R<31:0>                             |       |       |       |       |      |       |        |      | xxxx<br>xxxx |       |        |      |          |      |              |

| 4A20                        | OC6RS                           | 31:16<br>15:0 |              | OC6RS<31:0>                            |       |       |       |       |      |       |        |      |              |       |        |      |          |      |              |

| 4000                        | OC7CON                          | 31:16         | _            |                                        | —     | _     | -     | _     | -    | -     | —      |      | _            |       | —      | -    | _        | _    | 0000         |

| 4000                        |                                 | 15:0          | ON           |                                        | SIDL  | _     | -     | _     | -    | -     | —      |      | OC32         | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 4C10                        | OC7R                            | 31:16<br>15:0 |              |                                        |       |       |       |       |      | OC7R- | <31:0> |      |              |       |        |      |          |      | xxxx<br>xxxx |

| 4C20                        | OC7RS                           | 31:16<br>15:0 |              |                                        |       |       |       |       |      | OC7RS | <31:0> |      |              |       |        |      |          |      | xxxx<br>xxxx |

| 4500                        | 00000                           | 31:16         | _            | _                                      | —     | —     | —     | —     | —    | —     | —      | —    | _            | —     | —      |      | _        | _    | 0000         |

| 4E00                        | OC8CON                          | 15:0          | ON           | -                                      | SIDL  | _     | -     | _     | -    | _     | _      | _    | OC32         | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 4E10                        | OC8R                            | 31:16<br>15:0 |              |                                        |       |       |       |       |      | OC8R  | <31:0> |      |              |       |        |      |          |      | xxxx<br>xxxx |

| 4E20                        | OC8RS                           | 31:16<br>15:0 |              |                                        |       |       |       |       |      | OC8RS | <31:0> |      |              |       |        |      |          |      | xxxx<br>xxxx |

| 5000                        | 00000                           | 31:16         | _            | _                                      | _     | —     | _     | —     | _    | _     | —      | —    | —            | —     | _      | _    | _        | _    | 0000         |

| 5000                        | OC9CON                          | 15:0          | ON           | -                                      | SIDL  | —     | -     | —     | _    | _     | _      |      | OC32         | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 5010                        | OC9R                            | 31:16         | 2000 210 XXX |                                        |       |       |       |       |      |       |        | xxxx |              |       |        |      |          |      |              |

| 5010                        | OCSR                            | 15:0          |              | OC9R<31:0>                             |       |       |       |       |      |       |        |      |              | xxxx  |        |      |          |      |              |

| 5020                        | OC9RS                           | 31:16<br>15:0 |              |                                        |       |       |       |       |      | OC9RS | <31:0> |      |              |       |        |      |          |      | xxxx         |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

|              | IN 20-9. 0        | GIIIIIIOIAI       | . Sel INTER            |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5      | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                      | _                 | _                 | _                 | _                | _                |

| 22.10        | U-0               | U-0               | U-0                    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                      | —                 | _                 | —                 | —                | —                |

|              | U-0               | U-0               | U-0                    | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |

| 15:8         | _                 | —                 | _                      | -                 | DMA<br>EIF        | PKT<br>COMPIF     | BD<br>DONEIF     | CON<br>THRIF     |

|              | R/W-1, HS         | R/W-0, HS         | R/W-1, HS              | R/W-0, HS         | R/W-1, HS         | R/W-1, HS         | R/W-0, HS        | R/W-1, HS        |

| 7:0          | CON<br>EMPTYIF    | CON<br>FULLIF     | RXTHRIF <sup>(1)</sup> | RXFULLIF          | RX<br>EMPTYIF     | TXTHRIF           | TXFULLIF         | TX<br>EMPTYIF    |

#### **REGISTER 20-9:** SQI1INTSTAT: SQI INTERRUPT STATUS REGISTER

| Legend:           | HS = Hardware Set |                          |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

#### b

| hit 21 12 | Unimplemented: Read as '0'                                                             |

|-----------|----------------------------------------------------------------------------------------|

|           | •                                                                                      |

| bit 11    | DMAEIF: DMA Bus Error Interrupt Flag bit                                               |

|           | 1 = DMA bus error has occurred                                                         |

|           | 0 = DMA bus error has not occurred                                                     |

| bit 10    | <b>PKTCOMPIF:</b> DMA Buffer Descriptor Processor Packet Completion Interrupt Flag bit |

|           | 1 = DMA BD packet is complete                                                          |

|           | 0 = DMA BD packet is in progress                                                       |

| bit 9     | BDDONEIF: DMA Buffer Descriptor Done Interrupt Flag bit                                |

|           | 1 = DMA BD process is done                                                             |

|           | 0 = DMA BD process is in progress                                                      |

| bit 8     | CONTHRIF: Control Buffer Threshold Interrupt Flag bit                                  |

|           | 1 = The control buffer has more than THRES words of space available                    |

|           | 0 = The control buffer has less than THRES words of space available                    |

| bit 7     | CONEMPTYIF: Control Buffer Empty Interrupt Flag bit                                    |

|           | 1 = Control buffer is empty                                                            |

|           | 0 = Control buffer is not empty                                                        |

| bit 6     | CONFULLIF: Control Buffer Full Interrupt Flag bit                                      |

|           | 1 = Control buffer is full                                                             |

|           | 0 = Control buffer is not full                                                         |

| bit 5     | RXTHRIF: Receive Buffer Threshold Interrupt Flag bit <sup>(1)</sup>                    |

|           | 1 = Receive buffer has more than RXINTTHR words of space available                     |

|           | 0 = Receive buffer has less than RXINTTHR words of space available                     |

| bit 4     | RXFULLIF: Receive Buffer Full Interrupt Flag bit                                       |

|           | 1 = Receive buffer is full                                                             |

|           | 0 = Receive buffer is not full                                                         |

- b

- bit 3 **RXEMPTYIF:** Receive Buffer Empty Interrupt Flag bit

- 1 = Receive buffer is empty

- 0 = Receive buffer is not empty

- Note 1: In Boot/XIP mode, the POR value of the receive buffer threshold is zero. Therefore, this bit will be set to a '1', immediately after a POR until a read request on the System Bus is received.

Note: The bits in the register are cleared by writing a '1' to the corresponding bit position.

## 23.1 PMP Control Registers

### TABLE 23-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | ő                  |                |                         |       |       |           |        |        | В      | its     |        |      |       |        |           |           |         | \$         |

|-----------------------------|---------------------------------|--------------------|----------------|-------------------------|-------|-------|-----------|--------|--------|--------|---------|--------|------|-------|--------|-----------|-----------|---------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range          | 31/15          | 30/14                   | 29/13 | 28/12 | 27/11     | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5 | 20/4  | 19/3   | 18/2      | 17/1      | 16/0    | All Resets |

| E000                        | PMCON                           | 31:16              |                | —                       | —     |       | —         | —      | —      |        | RDSTART |        | —    |       | _      |           | DUALBUF   | _       | 0000       |

| LUUU                        | FINCON                          | 15:0               | ON             | —                       | SIDL  | ADRMU | JX<1:0>   | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0>  | ALP  | CS2P  | CS1P   |           | WRSP      | RDSP    | 0000       |

| E010                        | PMMODE                          | 31:16              | _              | —                       | —     | _     | —         | —      |        | _      |         | —      | —    | —     | —      | _         | —         | —       | 0000       |

| 2010                        | _                               | 15:0               | BUSY           | IRQM                    | <1:0> | INCM  | <1:0>     | MODE16 | MODE   | <1:0>  | WAITE   | 3<1:0> |      | WAITN | /<3:0> |           | WAITE     | <1:0>   | 0000       |

|                             |                                 | 31:16              | _              | —                       | —     | —     |           | —      | —      | —      | —       | —      | —    | —     | —      | —         | —         | _       | 0000       |

| E020                        | PMADDR                          | 15:0               | CS2            | CS1                     |       |       |           |        |        |        | ADDR    | <13.0> |      |       |        |           |           |         | 0000       |

|                             |                                 |                    | ADDR15         | ADDR14                  |       |       |           | -      |        |        |         |        |      |       |        |           |           |         | 0000       |

| E030                        | PMDOUT                          | 31:16              | _              | —                       | —     | —     | _         | —      | —      | —      |         | —      | —    | —     | _      | —         | —         | _       | 0000       |

|                             |                                 | 15:0               |                |                         |       |       |           |        |        | 0000   |         |        |      |       |        |           |           |         |            |

| E040                        | PMDIN                           | 31:16<br>15:0      | —              | —                       | _     | _     |           | _      | _      |        | -       | —      | _    | —     | —      | —         | —         | _       | 0000       |

|                             |                                 | 31:16              |                |                         |       |       |           |        |        | DATAI  | l<15:0> |        |      |       |        |           |           |         | 0000       |

| E050                        | PMAEN                           | 15:0               | -              | _                       | —     | _     | _         | —      | _      |        |         | _      | —    | —     | —      |           | —         | _       |            |

|                             |                                 |                    |                |                         |       |       |           |        |        |        | <15:0>  |        |      |       |        |           |           |         | 0000       |

| E060                        | PMSTAT                          | 31:16<br>15:0      | IBF            | —<br>IBOV               | _     | _     | IB3F      | IB2F   | IB1F   | IB0F   |         |        |      | _     | OB3E   | —<br>OB2E | —<br>OB1E |         | 0000       |

|                             |                                 | 31:16              |                | <u>іво</u> у            |       |       | івэг<br>— |        |        |        |         |        |      |       |        |           |           | <u></u> | 008F       |

| E070                        | PMWADDR                         | 51.10              | WCS2           | WCS1                    |       |       |           |        | _      |        | _       |        |      |       |        |           | _         |         | 0000       |

| 2070                        |                                 | 15:0               | 15:0 WCS2 WCS1 |                         |       |       |           |        |        |        |         | 0000   |      |       |        |           |           |         |            |

|                             |                                 | 31:16              |                |                         |       | _     |           | _      | _      | _      |         | <13:0> | _    | _     | _      | _         | _         | _       | 0000       |

| E090                        | PMRADDR                         | 51.10              | RCS2           | RCS1                    |       |       |           |        |        |        |         |        |      |       |        |           | _         |         | 0000       |

| E080                        | FINIKADDR                       | DDR 15:0 RCS2 RCS1 |                |                         |       |       |           |        |        | 0000   |         |        |      |       |        |           |           |         |            |

|                             |                                 | 31:16              | 31:16          |                         |       | _     | _         |        |        |        |         | <13:0> |      | _     |        | _         |           | _       | 0000       |

| E090                        | PMRDIN                          |                    |                |                         |       | _     |           | _      |        |        |         | -      |      | _     |        |           | _         | _       |            |

|                             |                                 | 15:0               | 15:0           | 15:0 RDATAIN<15:0> 0000 |       |       |           |        |        |        |         |        |      |       |        |           |           |         |            |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

|                  |                   | -                 |                   |                   |                   |                   |                  |                  |

|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04-04            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24            |                   | HR10              | <3:0>             |                   |                   | HR01              | <3:0>            |                  |

| 00.40            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16 MIN10<3:0> |                   |                   |                   | MIN01<3:0>        |                   |                   |                  |                  |

| 45.0             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8             |                   | SEC10             | <3:0>             |                   | SEC01<3:0>        |                   |                  |                  |

| 7.0              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0              | —                 | —                 | —                 | _                 | —                 | —                 | _                | —                |

|                  |                   |                   |                   |                   |                   |                   |                  |                  |

| Legend:          |                   |                   |                   |                   |                   |                   |                  |                  |

| -                |                   |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |

0' = Bit is cleared

x = Bit is unknown

#### REGISTER 25-3: RTCTIME: REAL-TIME CLOCK TIME VALUE REGISTER

'1' = Bit is set

| bit 31-28 | HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10 digits; contains a value from 0 to 2    |

|-----------|-------------------------------------------------------------------------------------------------|

| bit 27-24 | HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1 digit; contains a value from 0 to 9      |

| bit 23-20 | MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10 digits; contains a value from 0 to 5 |

| bit 19-16 | MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1 digit; contains a value from 0 to 9   |

| bit 15-12 | SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10 digits; contains a value from 0 to 5 |

| bit 11-8  | SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1 digit; contains a value from 0 to 9   |

bit 7-0 Unimplemented: Read as '0'

-n = Value at POR

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Range     31/23/15/7     30/22/14/6     29/21/13/5     28/20/12/4     27/19/11/3     26/18/10/2     25/17/9/1     24/16/       31:24     R-0                                                                                               |       | ( )         | x = 1  OR  2 |     |       |       |     |     |                  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|--------------|-----|-------|-------|-----|-----|------------------|--|--|--|--|--|

| 31:24 SEED<31:24>   23:16 R-0 R                                                                                                                                                                                                                                                                                                                                                                                                                        | _     |             |              |     |       |       |     |     | Bit<br>24/16/8/0 |  |  |  |  |  |

| R-0     R-0 <td>04-04</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> | 04-04 | R-0         | R-0          | R-0 | R-0   | R-0   | R-0 | R-0 | R-0              |  |  |  |  |  |

| 23:16     SEED<23:16>       15:8     R-0     R-0 <t< td=""><td>31:24</td><td></td><td colspan="12">SEED&lt;31:24&gt;</td></t<>                                             | 31:24 |             | SEED<31:24>  |     |       |       |     |     |                  |  |  |  |  |  |

| R-0     R-0 <td>00.40</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> <td>R-0</td> | 00.40 | R-0         | R-0          | R-0 | R-0   | R-0   | R-0 | R-0 | R-0              |  |  |  |  |  |

| 15:8 SEED<15:8>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23:16 | SEED<23:16> |              |     |       |       |     |     |                  |  |  |  |  |  |

| SEED<15:8>       R-0     R-                                                                                                                        | 45.0  | R-0         | R-0          | R-0 | R-0   | R-0   | R-0 | R-0 | R-0              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15:8  |             |              |     | SEED< | 15:8> |     |     |                  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7.0   | R-0         | R-0          | R-0 | R-0   | R-0   | R-0 | R-0 | R-0              |  |  |  |  |  |

| 7:0 SEED<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7:0   |             |              |     | SEED< | <7:0> |     |     |                  |  |  |  |  |  |

# **REGISTER 27-5: RNGSEEDX: TRUE RANDOM NUMBER GENERATOR SEED REGISTER 'x'** ('x' = 1 OR 2)

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **SEED<31:0>:** TRNG MSb/LSb Value bits (RNGSEED1 = LSb, RNGSEED2 = MSb)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 |                   |                   |                   | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 |                   |                   |                   | RCNT<6:0>         |                   |                  |                  |

#### REGISTER 27-6: RNGCNT: TRUE RANDOM NUMBER GENERATOR COUNT REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-7 Unimplemented: Read as '0'

bit 6-0 RCNT<6:0>: Number of Valid TRNG MSB 32 bits

#### REGISTER 28-1: ADCCON1: ADC CONTROL REGISTER 1 (CONTINUED)

bit 3 STRGLVL: Scan Trigger High Level/Positive Edge Sensitivity bit

- 1 = Scan trigger is high level sensitive. Once STRIG mode is selected (TRGSRCx<4:0> in the ADCTRGx register), the scan trigger will continue for all selected analog inputs, until the STRIG option is removed.

- 0 = Scan trigger is positive edge sensitive. Once STRIG mode is selected (TRGSRCx<4:0> in the ADCTRGx register), only a single scan trigger will be generated, which will complete the scan of all selected analog inputs.

- bit 2-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|--|--|

| 24.24        | R/W-0                     | R/W-0            |  |  |  |

| 31:24        | ADCSE             | L<1:0>            |                   | CONCLKDIV<5:0>    |                   |                   |                           |                  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |  |

| 23:16        | DIGEN7            | —                 | _                 | DIGEN4            | DIGEN3            | DIGEN2            | DIGEN1                    | DIGEN0           |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0, HS, HC       | R/W-0                     | R-0, HS, HC      |  |  |  |

| 15:8         | V                 | REFSEL<2:0        | >                 | TRGSUSP           | UPDIEN            | UPDRDY            | SAMP <sup>(1,2,3,4)</sup> | RQCNVRT          |  |  |  |

| 7.0          | R/W-0             | R/W-0, HC         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |  |

| 7:0          | GLSWTRG           | GSWTRG            |                   |                   | ADINS             | SEL<5:0>          |                           |                  |  |  |  |

#### REGISTER 28-3: ADCCON3: ADC CONTROL REGISTER 3

| Legend:           | HC = Hardware Set | HS = Hardware Cleared  |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-30 ADCSEL<1:0>: Analog-to-Digital Clock Source (TCLK) bits

11 = FRC 10 = REFCLK3 01 = System Clock (Tcy) 00 = PBCLK3

#### bit 29-24 CONCLKDIV<5:0>: Analog-to-Digital Control Clock (TQ) Divider bits

|           | 111111 = 64 * TCLK = TQ                  |

|-----------|------------------------------------------|

|           | •                                        |

|           | •                                        |

|           | 000011 = 4 * TCLK = TQ                   |

|           | 000010 = 3 * TCLK = TQ                   |

|           | 000001 = 2 * TCLK = TQ                   |

|           | 000000 = TCLK = TQ                       |

| bit 23    | DIGEN7: Shared ADC (ADC7) Digital Enable |

|           | 1 = ADC7 is digital enabled              |

|           | 0 = ADC7 is digital disabled             |

| 1-1-00 OA | Halman Jamaan (ash. Daashaa (o)          |

### bit 22-21 **Unimplemented:** Read as '0'

#### bit 20 DIGEN4: ADC4 Digital Enable bit

- 1 = ADC4 is digital enabled

- 0 = ADC4 is digital disabled

#### bit 19 **DIGEN3:** ADC3 Digital Enable bit

- 1 = ADC3 is digital enabled

- 0 = ADC3 is digital disabled

- **Note 1:** The SAMP bit has the highest priority and setting this bit will keep the S&H circuit in Sample mode until the bit is cleared. Also, usage of the SAMP bit will cause settings of SAMC<9:0> bits (ADCCON2<25:16>) to be ignored.

bit

- 2: The SAMP bit only connects Class 2 and Class 3 analog inputs to the shared ADC, ADC7. All Class 1 analog inputs are not affected by the SAMP bit.

- **3:** The SAMP bit is not a self-clearing bit and it is the responsibility of application software to first clear this bit and only after setting the RQCNVRT bit to start the analog-to-digital conversion.

- 4: Normally, when the SAMP and RQCNVRT bits are used by software routines, all TRGSRCx<4:0> bits and STRGSRC<4:0> bits should be set to '00000' to disable all external hardware triggers and prevent them from interfering with the software-controlled sampling command signal SAMP and with the software-controlled trigger RQCNVRT.

#### REGISTER 28-7: ADCIMCON3: ADC INPUT MODE CONTROL REGISTER 3 (CONTINUED)

- bit 1 DIFF32: AN32 Mode bit<sup>(1)</sup>

- 1 = AN32 is using Differential mode

- 0 = AN32 is using Single-ended mode

- bit 0 SIGN32: AN32 Signed Data Mode bit<sup>(1)</sup>

- 1 = AN32 is using Signed Data mode

- 0 = AN32 is using Unsigned Data mode

- Note 1: This bit is not available on 64-pin devices.

- 2: This bit is not available on 64-pin and 100-pin devices.

|              |                   | _                 |                   |                       | -                 |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31:24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | —                 | _                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 10.0         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | _                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | _                 | _                 | _                     | MODIF             | CTMRIF            | RBIF             | TBIF             |

#### **REGISTER 29-3: CIINT: CAN INTERRUPT REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | IVRIE: Invalid Message Received Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | WAKIE: CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                             |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                   |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                |

| bit 19    | MODIE: Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                       |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                             |

| bit 15    | IVRIF: Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module off and on by clearing or setting the ON bit (CiCON<15>).                                          |

# PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

REGISTER 29-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED) bit 15 FLTEN5: Filter 17 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL5<1:0>: Filter 5 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL5<4:0>: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN4: Filter 4 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL4<1:0>: Filter 4 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL4<4:0>: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0 The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. Note:

#### TABLE 30-5: ETHERNET CONTROLLER REGISTER SUMMARY (CONTINUED)

| ess                         |                                 | 0         |               |       |       |        |          |            |      | В    | its  |      |      |        |          |          |      |          | ú          |

|-----------------------------|---------------------------------|-----------|---------------|-------|-------|--------|----------|------------|------|------|------|------|------|--------|----------|----------|------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14 | 29/13 | 28/12  | 27/11    | 26/10      | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4   | 19/3     | 18/2     | 17/1 | 16/0     | All Resets |

| 22B0                        |                                 | 31:16     | _             | _     | _     | _      | _        |            |      |      | _    | _    | _    | -      | _        | —        | -    | —        | 0000       |

| 2200                        | MWTD                            | 15:0      | MWTD<15:0> 00 |       |       |        |          |            |      |      |      |      | 0000 |        |          |          |      |          |            |

| 22C0                        | EMAC1                           | 31:16     | _             | —     | _     | —      | —        |            | -    |      | _    | -    | _    | -      | _        | —        | -    | _        | 0000       |

| 2200                        | MRDD                            | 15:0      |               |       |       |        |          | MRDD<15:0> |      |      |      |      |      |        |          |          | 0000 |          |            |

| 22D0                        | EMAC1                           | 31:16     | —             | —     | _     | —      | —        |            |      |      | _    | -    | -    | -      | -        | —        | -    | —        | 0000       |

| 2200                        | MIND                            | 15:0      | -             | _     | —     | _      | —        |            |      |      | _    |      |      |        | LINKFAIL | NOTVALID | SCAN | MIIMBUSY | 0000       |

| 2300                        | EMAC1                           | 31:16     | _             | _     |       | _      | _        |            | _    |      | _    | -    |      | -      |          | _        | _    | _        | xxxx       |

| 2300                        | SA0 <sup>(2)</sup>              | 15:0      |               |       |       | STNADD | 0R6<7:0> |            |      |      |      |      |      | STNADE | )R5<7:0> |          |      |          | xxxx       |

| 2310                        |                                 | 31:16     | -             | -     | —     | -      | _        | -          | -    | -    |      | -    | -    | -      | -        | -        | -    | —        | xxxx       |

| 2310                        | SA1 <sup>(2)</sup>              | 15:0      |               |       |       | STNADD | )R4<7:0> |            |      |      |      |      |      | STNADE | )R3<7:0> |          |      |          | xxxx       |

| 2220                        |                                 | 31:16     | -             | -     | _     | _      | _        | _          | _    | _    | _    | _    | _    | _      | _        | _        | _    | _        | xxxx       |

| 2320                        | SA2 <sup>(2)</sup>              | 15:0      |               |       |       | STNADD | R2<7:0>  |            |      |      |      |      |      | STNADE | )R1<7:0> |          |      |          | xxxx       |

Legend: Note

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and 1: INV Registers" for more information.

2: Reset values default to the factory programmed value.

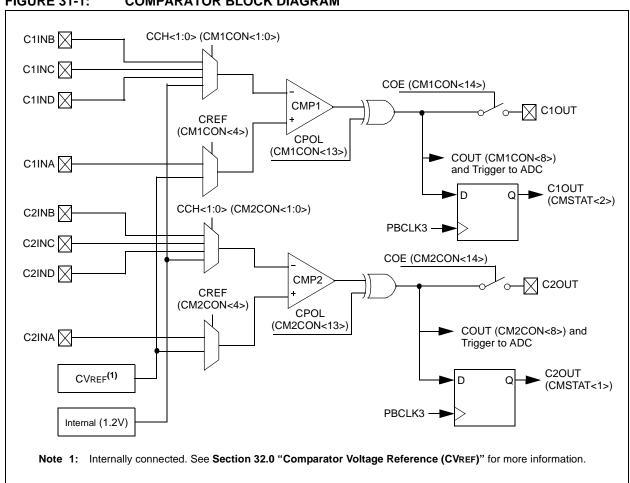

#### 31.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Comparator" (DS60001110) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Analog Comparator module consists of two comparators that can be configured in a variety of ways.

The following are key features of the Analog Comparator module:

- Differential inputs

- Rail-to-rail operation

- Selectable output polarity

- Selectable inputs:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference

- Comparator voltage reference (CVREF)

- Selectable interrupt generation

A block diagram of the comparator module is illustrated in Figure 31-1.

#### **FIGURE 31-1:** COMPARATOR BLOCK DIAGRAM

### 33.3 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 33-1 for more information.

| Note: | Disabling a peripheral module while it's   |

|-------|--------------------------------------------|

|       | ON bit is set, may result in undefined     |

|       | behavior. The ON bit for the associated    |

|       | peripheral module must be cleared prior to |

|       | disable a module via the PMDx bits.        |

| Peripheral                   | PMDx bit Name | Register Name and Bit Location |

|------------------------------|---------------|--------------------------------|

| ADC                          | ADCMD         | PMD1<0>                        |

| Comparator Voltage Reference | CVRMD         | PMD1<12>                       |

| Comparator 1                 | CMP1MD        | PMD2<0>                        |

| Comparator 2                 | CMP2MD        | PMD2<1>                        |

| Input Capture 1              | IC1MD         | PMD3<0>                        |

| Input Capture 2              | IC2MD         | PMD3<1>                        |

| Input Capture 3              | IC3MD         | PMD3<2>                        |

| Input Capture 4              | IC4MD         | PMD3<3>                        |

| Input Capture 5              | IC5MD         | PMD3<4>                        |

| Input Capture 6              | IC6MD         | PMD3<5>                        |

| Input Capture 7              | IC7MD         | PMD3<6>                        |

| Input Capture 8              | IC8MD         | PMD3<7>                        |

| Input Capture 9              | IC9MD         | PMD3<8>                        |

| Output Compare 1             | OC1MD         | PMD3<16>                       |

| Output Compare 2             | OC2MD         | PMD3<17>                       |

| Output Compare 3             | OC3MD         | PMD3<18>                       |

| Output Compare 4             | OC4MD         | PMD3<19>                       |

| Output Compare 5             | OC5MD         | PMD3<20>                       |

| Output Compare 6             | OC6MD         | PMD3<21>                       |

| Output Compare 7             | OC7MD         | PMD3<22>                       |

| Output Compare 8             | OC8MD         | PMD3<23>                       |

| Output Compare 9             | OC9MD         | PMD3<24>                       |

| Timer1                       | T1MD          | PMD4<0>                        |

| Timer2                       | T2MD          | PMD4<1>                        |

| Timer3                       | T3MD          | PMD4<2>                        |

| Timer4                       | T4MD          | PMD4<3>                        |

| Timer5                       | T5MD          | PMD4<4>                        |

| Timer6                       | T6MD          | PMD4<5>                        |

| Timer7                       | T7MD          | PMD4<6>                        |

| Timer8                       | T8MD          | PMD4<7>                        |

| Timer9                       | T9MD          | PMD4<8>                        |

| UART1                        | U1MD          | PMD5<0>                        |

| UART2                        | U2MD          | PMD5<1>                        |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the lists of available peripherals.

2: Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

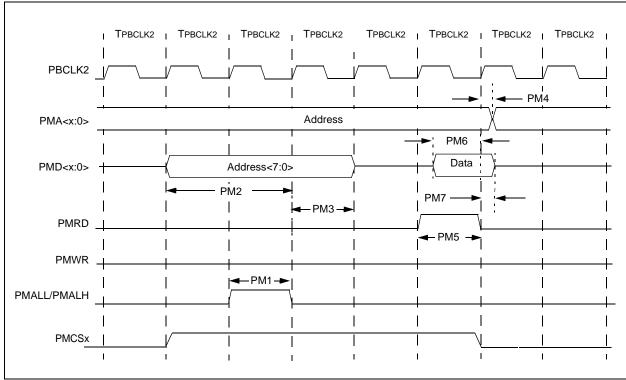

#### FIGURE 37-22: PARALLEL MASTER PORT READ TIMING DIAGRAM

#### TABLE 37-43: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |           |      |       |            |  |  |

|--------------------|---------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-------|------------|--|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                                                    | Тур.      | Max. | Units | Conditions |  |  |

| PM1                | TLAT    | PMALL/PMALH Pulse Width                                              | —                                                                                                                                                                                                                                                                                       | 1 TPBCLK2 | _    | _     |            |  |  |

| PM2                | TADSU   | Address Out Valid to PMALL/<br>PMALH Invalid (address setup time)    | —                                                                                                                                                                                                                                                                                       | 2 TPBCLK2 | —    | —     | _          |  |  |

| PM3                | TADHOLD | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                                                                                                                                                                                                                                                       | 1 TPBCLK2 | —    | _     | _          |  |  |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                                                       | —         | —    | ns    | _          |  |  |

| PM5                | Trd     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                                                       | 1 TPBCLK2 | _    | —     | _          |  |  |

| PM6                | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                                                                                                                                                                                                                                                      | —         | —    | ns    | _          |  |  |