Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efm100-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                       | Pin Nu          | mber            |                          |             |                |                                                                            |

|----------|---------------------------------------|-----------------|-----------------|--------------------------|-------------|----------------|----------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP                | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                                                |

|          |                                       |                 |                 |                          | J           | ΓAG            |                                                                            |

| ТСК      | 27                                    | 38              | B21             | 56                       | I           | ST             | JTAG Test Clock Input Pin                                                  |

| TDI      | 28                                    | 39              | A26             | 57                       | I           | ST             | JTAG Test Data Input Pin                                                   |

| TDO      | 24                                    | 40              | B22             | 58                       | 0           | —              | JTAG Test Data Output Pin                                                  |

| TMS      | 23                                    | 17              | A11             | 22                       | I           | ST             | JTAG Test Mode Select Pin                                                  |

|          | •                                     | •               | •               |                          | Tr          | ace            | •                                                                          |

| TRCLK    | 57                                    | 89              | A61             | 129                      | 0           | _              | Trace Clock                                                                |

| TRD0     | 58                                    | 97              | B55             | 141                      | 0           | —              | Trace Data bits 0-3                                                        |

| TRD1     | 61                                    | 96              | A65             | 140                      | 0           | —              |                                                                            |

| TRD2     | 62                                    | 95              | B54             | 139                      | 0           | —              |                                                                            |

| TRD3     | 63                                    | 90              | B51             | 130                      | 0           | —              |                                                                            |

|          |                                       |                 |                 | Pro                      | grammiı     | ng/Debugg      | ing                                                                        |

| PGED1    | 16                                    | 25              | A18             | 36                       | I/O         | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 1          |

| PGEC1    | 15                                    | 24              | A17             | 35                       | Ι           | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 1       |

| PGED2    | 18                                    | 27              | A19             | 38                       | I/O         | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 2          |

| PGEC2    | 17                                    | 26              | B14             | 37                       | Ι           | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 2       |

| MCLR     | 9                                     | 15              | A10             | 20                       | l/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device. |

| Legend:  | CMOS = CI<br>ST = Schm<br>TTL = Trans | itt Trigger ir  | put with C      | MOS level                |             | O = Outp       | Analog input P = Power<br>ut I = Input<br>eripheral Pin Select             |

#### **TABLE 1-22:** JTAG, TRACE, AND PROGRAMMING/DEBUGGING PINOUT I/O DESCRIPTIONS

# TABLE 4-14: SYSTEM BUS TARGET 6 REGISTER MAP

| ess                         |                  | â         |               |                 |       |         |          |       |       |      | Bits     |           |           |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|---------------|-----------------|-------|---------|----------|-------|-------|------|----------|-----------|-----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15         | 30/14           | 29/13 | 28/12   | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6      | 21/5      | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| 9820                        | SBT6ELOG1        | 31:16     | MULTI         |                 | —     | —       |          | CODE  | <3:0> |      |          |           |           |      | —      |        | _       |        | 0000          |

| 9020                        | SBIOLLOGI        | 15:0      |               |                 |       | INI     | TID<7:0> |       |       |      |          | REGIO     | N<3:0>    |      | —      | С      | MD<2:0> |        | 0000          |

| 9824                        | SBT6ELOG2        | 31:16     | _             | —               | —     | —       | —        | -     | _     | -    | —        | —         | _         | _    | —      | -      | —       | -      | 0000          |

| 9024                        | SBIOLLOGZ        | 15:0      | _             | —               | —     | —       | —        | -     | _     | -    | —        | —         | _         | _    | —      | -      | GROU    | P<1:0> | 0000          |

| 9828                        | SBT6ECON         | 31:16     | _             | —               | —     | —       | —        | -     | _     | ERRP | —        | —         | _         | _    | —      | -      | —       | -      | 0000          |

| 9020                        | SBIOLCON         | 15:0      | —             | _               | —     | —       | —        | _     | _     | _    | _        | _         | —         | _    | —      | _      | —       | _      | 0000          |

| 9830                        | SBT6ECLRS        | 31:16     | —             | —               | —     | —       | —        | _     | _     | _    | _        | —         | —         | _    | —      | _      | —       | -      | 0000          |

| 3030                        | SDIGECERS        | 15:0      | —             | —               | —     | —       | —        | _     | _     | _    | _        | —         | —         | _    | —      | _      | —       | CLEAR  | 0000          |

| 9838                        | SBT6ECLRM        | 31:16     | —             | —               | —     | —       | —        | _     | _     | _    | _        | —         | —         | _    | —      | _      | —       | -      | 0000          |

| 3030                        | SBIOLOCIUM       | 15:0      | —             | —               | —     | —       | —        | _     | _     | _    | —        | _         | —         | _    | —      | _      | —       | CLEAR  | 0000          |

| 9840                        | SBT6REG0         | 31:16     |               |                 |       |         |          |       |       | BA   | SE<21:6> |           |           |      |        |        |         |        | xxxx          |

| 0040                        | OBTORCEOU        | 15:0      |               |                 | BA    | SE<5:0> |          |       | PRI   | _    |          |           | SIZE<4:0: | >    |        | _      | —       | _      | xxxx          |

| 9850                        | SBT6RD0          | 31:16     | —             | —               | —     | —       | —        | —     | —     | —    | —        | —         | —         | —    | —      | —      | —       | —      | xxxx          |

| 0000                        | CETOREO          | 15:0      | _             | —               | —     | —       | —        | —     | —     | —    | —        | —         | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9858                        | SBT6WR0          | 31:16     | _             | —               | —     | —       | —        | —     | —     | —    | —        | —         | —         | —    | —      | —      | —       | —      | xxxx          |

| 0000                        | eb romite        | 15:0      | _             | —               | —     | —       | —        | —     | —     | —    | —        | —         | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9860                        | SBT6REG1         | 31:16     | BASE<21:6> xx |                 |       |         |          |       |       | xxxx |          |           |           |      |        |        |         |        |               |

| 0000                        | OBTOREOT         | 15:0      |               | BASE<5:0> PRI — |       |         |          |       |       |      |          | SIZE<4:0: | >         |      | —      | —      | —       | xxxx   |               |

| 9870                        | SBT6RD1          | 31:16     | —             | —               | —     | —       | —        | _     | _     | _    | —        | _         | _         | _    | —      |        | —       | -      | xxxx          |

|                             | 5010101          | 15:0      | _             | _               | —     | —       | —        | _     | —     | —    | _        | —         | _         | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| 9878                        | SBT6WR1          | 31:16     | _             | _               | —     | —       | —        | _     | —     | —    | _        | —         | _         | _    | —      | —      | —       | —      | xxxx          |

| 0010                        | 02.000           | 15:0      | —             | —               | —     | —       | —        | —     | —     | —    | —        | —         | —         | —    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>)                   | _                               | Ð         |       |       |       |       |                                        |       |          | Bi                     | ts   |      |      |      |                          |                     |         |                       | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------------------------------|-------|----------|------------------------|------|------|------|------|--------------------------|---------------------|---------|-----------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                                  | 26/10 | 25/9     | 24/8                   | 23/7 | 22/6 | 21/5 | 20/4 | 19/3                     | 18/2                | 17/1    | 16/0                  | All Resets |

|                             | BOOG                            | 31:16     | _     | _     | _     |       | CRPTIP<2:0>                            | (7)   | CRPTIS   | <1:0>(7)               | _    | —    | -    |      | SBIP<2:0>                |                     | SBIS    | <1:0>                 | 0000       |

| 02E0                        | PC26                            | 15:0      | _     | _     | _     |       | CFDCIP<2:0                             | >     | CFDCIS   | S<1:0>                 | _    | _    | -    |      | CPCIP<2:0                | >                   | CPCIS   | S<1:0>                | 0000       |

| 02F0                        | 0007                            | 31:16     | _     | _     | _     |       | SPI1TXIP<2:0                           | )>    | SPI1TXI  | S<1:0>                 | _    | _    | _    |      | SPI1RXIP<2:              | 0>                  | SPI1RX  | IS<1:0>               | 0000       |

| 02F0                        | PC27                            | 15:0      | _     | _     | _     |       | SPI1EIP<2:0                            | >     | SPI1EIS  | S<1:0>                 | _    | —    | _    | _    | _                        | _                   | _       | _                     | 0000       |

| 0300                        | 0000                            | 31:16     | _     | _     | _     |       | I2C1BIP<2:0                            | >     | I2C1BIS  | S<1:0>                 | _    | —    | _    |      | U1TXIP<2:0               | >                   | U1TXI   | S<1:0>                | 0000       |

| 0300                        | PC20                            | 15:0      | _     | _     | _     |       | U1RXIP<2:0                             | >     | U1RXIS   | 6<1:0>                 | _    | _    | _    |      | U1EIP<2:0:               | >                   | U1EIS   | S<1:0>                | 0000       |

| 0040                        | DOOD                            | 31:16     | _     | _     | _     |       | CNBIP<2:0>                             |       | CNBIS    | <1:0>                  | _    | —    | _    |      | CNAIP<2:0>               | (2)                 | CNAIS   | <1:0> <b>(2)</b>      | 0000       |

| 0310                        | PC29                            | 15:0      | _     | _     | _     |       | I2C1MIP<2:0                            | >     | I2C1MI   | S<1:0>                 | _    | —    | _    |      | I2C1SIP<2:0              | )>                  | I2C1SI  | S<1:0>                | 0000       |

| 0320                        | BC20                            | 31:16     | —     | —     | _     |       | CNFIP<2:0>                             |       | CNFIS    | <1:0>                  | _    | —    |      |      | CNEIP<2:0                | >                   | CNEIS   | S<1:0>                | 0000       |

| 0320                        | FC30                            | 15:0      | —     | —     | —     |       | CNDIP<2:0>                             |       | CNDIS    | <1:0>                  |      | —    | -    |      | CNCIP<2:0                | >                   | CNCIS   | 6<1:0>                | 0000       |

| 0330                        | DC21                            | 31:16     | —     | _     | _     | C     | 00000000000000000000000000000000000000 | 4,8)  | CNKIS<1  | :0> <sup>(2,4,8)</sup> | —    | —    |      | (    | CNJIP<2:0> <sup>(2</sup> | 2,4)                | CNJIS<  | 1:0> <sup>(2,4)</sup> | 0000       |

| 0330                        | FC31                            | 15:0      | —     | _     | _     | (     | CNHIP<2:0> <sup>(2</sup>               | ,4)   | CNHIS<   | 1:0> <sup>(2,4)</sup>  | _    | —    |      |      | CNGIP<2:0                | >                   | CNGIS   | S<1:0>                | 0000       |

| 0340                        | BC22                            | 31:16     | _     | _     | _     |       | CMP2IP<2:0                             | >     | CMP2IS   | S<1:0>                 | —    | _    |      |      | CMP1IP<2:0               | )>                  | CMP1I   | S<1:0>                | 0000       |

| 0340                        | F032                            | 15:0      | —     | —     | _     |       | PMPEIP<2:0                             | >     | PMPEIS   | S<1:0>                 | _    | —    |      |      | PMPIP<2:0                | >                   | PMPIS   | S<1:0>                | 0000       |

| 0350                        | 0022                            | 31:16     | —     | _     | _     |       | DMA1IP<2:0                             | >     | DMA1IS   | S<1:0>                 | _    | —    |      |      | DMA0IP<2:0               | )>                  | DMA0I   | S<1:0>                | 0000       |

| 0350                        | FC33                            | 15:0      | _     | _     | _     | ι     | JSBDMAIP<2:                            | 0>    | USBDMA   | JS<1:0>                | —    | _    |      |      | USBIP<2:0                | >                   | USBIS   | S<1:0>                | 0000       |

| 0360                        | DC24                            | 31:16     | —     | —     | —     |       | DMA5IP<2:0                             | >     | DMA5IS   | S<1:0>                 | —    | _    |      |      | DMA4IP<2:0               | )>                  | DMA4I   | S<1:0>                | 0000       |

| 0300                        | FC34                            | 15:0      | —     | —     | —     |       | DMA3IP<2:0                             | >     | DMA3IS   | S<1:0>                 | _    | —    | _    |      | DMA2IP<2:0               | )>                  | DMA2I   | S<1:0>                | 0000       |

| 0370                        | DC25                            | 31:16     | —     | _     | _     |       | SPI2RXIP<2:(                           | )>    | SPI2RXI  | S<1:0>                 | _    | —    |      |      | SPI2EIP<2:0              | )>                  | SPI2EI  | S<1:0>                | 0000       |

| 0370                        | FC35                            | 15:0      | —     | —     | _     |       | DMA7IP<2:0                             | >     | DMA7IS   | S<1:0>                 | _    | —    |      |      | DMA6IP<2:0               | )>                  | DMA6I   | S<1:0>                | 0000       |

| 0380                        | DC26                            | 31:16     | —     | —     | —     |       | U2TXIP<2:0:                            | >     | U2TXIS   | S<1:0>                 | _    | —    | _    |      | U2RXIP<2:0               | )>                  | U2RXI   | S<1:0>                | 0000       |

| 0360                        | FC30                            | 15:0      | —     | _     | _     |       | U2EIP<2:0>                             |       | U2EIS    |                        | _    | —    |      | :    | SPI2TXIP<2:              | 0>                  | SPI2TX  | IS<1:0>               | 0000       |

| 0390                        | 0007                            | 31:16     | —     | —     | _     |       | CAN1IP<2:0>                            | (3)   | CAN1IS-  | <1:0> <sup>(3)</sup>   | _    | —    |      | Ľ    | 2C2MIP<2:0:              | >(2)                | I2C2MIS | S<1:0> <b>(2)</b>     | 0000       |

| 0390                        | PC37                            | 15:0      | —     | _     | _     | I     | 2C2SIP<2:0>                            | (2)   | I2C2SIS- | <1:0> <sup>(2)</sup>   | _    | —    |      | I    | 2C2BIP<2:0;              | _(2)                | I2C2BIS | i<1:0> <sup>(2)</sup> | 0000       |

| 03A0                        | 0020                            | 31:16     | _     | _     | _     |       | SPI3RXIP<2:0                           | )>    | SPI3RXI  | S<1:0>                 | —    | _    |      |      | SPI3EIP<2:0              | )>                  | SPI3EI  | S<1:0>                | 0000       |

| 0340                        | FC30                            | 15:0      | _     | _     | _     |       | ETHIP<2:0>                             |       | ETHIS    | <1:0>                  | —    | _    |      | (    | CAN2IP<2:0>              | <sub>&gt;</sub> (3) | CAN2IS  | <1:0> <sup>(3)</sup>  | 0000       |

| 03B0                        | PC 30                           | 31:16     | —     | _     |       |       | U3TXIP<2:0:                            | >     | U3TXIS   | S<1:0>                 | _    | —    |      |      | U3RXIP<2:0               | )>                  | U3RXI   | S<1:0>                | 0000       |

| 0360                        | 1 0 3 9                         | 15:0      | —     | _     | —     |       | U3EIP<2:0>                             |       | U3EIS    | <1:0>                  | _    | —    |      |      | SPI3TXIP<2:              | 0>                  | SPI3TX  | IS<1:0>               | 0000       |

| 0200                        |                                 | 31:16     | —     | _     |       |       | SPI4EIP<2:0                            | >     | SPI4EIS  | S<1:0>                 | _    | _    |      |      | I2C3MIP<2:0              | )>                  | I2C3M   | S<1:0>                | 0000       |

| 03C0                        | F 0 40                          | 15:0      | —     | _     | _     |       | I2C3SIP<2:0                            | >     | 12C3SI   | S<1:0>                 | _    | _    |      |      | I2C3BIP<2:0              | )>                  | I2C3BI  | S<1:0>                | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

- Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

- Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

# REGISTER 11-29: USBLPMR2: USB LINK POWER MANAGEMENT CONTROL REGISTER 2 (CONTINUED)

bit 0 LPMSTIF: LPM STALL Interrupt Flag bit

#### When in Device mode:

- 1 = A LPM transaction was received and the USB Module responded with a STALL

- 0 = No Stall condition

#### When in Host mode:

- 1 = A LPM transaction was transmitted and the device responded with a STALL

- 0 = No Stall condition

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 | -                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | _                 | -                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 |                   | _                 | EDGEDETECT        | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   |                  |                  |

#### REGISTER 12-3: CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A - K)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Change Notice (CN) Control ON bit

1 = CN is enabled

0 = CN is disabled

#### bit 14-12 Unimplemented: Read as '0'

- bit 11 EDGEDETECT: Change Notification Style bit

- 1 = Edge Style. Detect edge transitions (CNFx used for CN Event).

- 0 = Mismatch Style. Detect change from last PORTx read (CNSTATx used for CN Event).

- bit 10-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|--|--|--|--|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |  |

| 31.24        |                      | —                 |                     |                   | —                  |                   |                    | —                |  |  |  |  |

| 00.40        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |  |

| 23:16        |                      | —                 | _                   | —                 | —                  | —                 | —                  | —                |  |  |  |  |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |  |

| 15:8         | ON <sup>(1)</sup>    | —                 | SIDL <sup>(2)</sup> | _                 | —                  | _                 | _                  | —                |  |  |  |  |

| 7:0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |  |  |  |  |

| 7:0          | TGATE <sup>(1)</sup> | Т                 | CKPS<2:0>(          | 1)                | T32 <sup>(3)</sup> | _                 | TCS <sup>(1)</sup> | —                |  |  |  |  |

#### TxCON: TYPE B TIMER CONTROL REGISTER ('x' = 2-9) REGISTER 14-1:

#### Legend:

bit 3

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: Timer On bit<sup>(1)</sup>

- 1 = Module is enabled 0 = Module is disabled

- Unimplemented: Read as '0'

#### bit 14 bit 13 SIDL: Stop in Idle Mode bit<sup>(2)</sup>

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation even in Idle mode

#### Unimplemented: Read as '0' bit 12-8

TGATE: Timer Gated Time Accumulation Enable bit<sup>(1)</sup> bit 7

#### When TCS = 1:

This bit is ignored and is read as '0'.

#### When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 = Gated time accumulation is disabled

#### bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(1)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

# 000 = 1:1 prescale value

## T32: 32-Bit Timer Mode Select bit(3)

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form separate 16-bit timers

- Note 1: While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, Timer5, Timer7, and Timer9). All timer functions are set through the even numbered timers.

- While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer 2: in Idle mode.

- 3: This bit is available only on even numbered timers (Timer2, Timer4, Timer6, and Timer8).

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24     | —                 | —                 | —                 | —                 | —                 | —                 | -                |                  |  |  |  |  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16     | —                 | —                 | —                 | —                 | —                 | —                 | -                |                  |  |  |  |  |

| 15.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8      |                   | —                 | _                 | —                 | —                 | _                 |                  | _                |  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0       |                   | STEP2<7:0>        |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 15-3: DMTCLR: DEADMAN TIMER CLEAR REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 STEP2<7:0>: Clear Timer bits

00001000 = Clears STEP1<7:0>, STEP2<7:0> and the Deadman Timer if, and only if, preceded by correct loading of STEP1<7:0> bits in the correct sequence. The write to these bits may be verified by reading DMTCNT and observing the counter being reset.

All other write patterns = Set BAD2 bit, the value of STEP1<7:0> will remain unchanged, and the new value being written STEP2<7:0> will be captured. These bits are also cleared when a DMT reset event occurs.

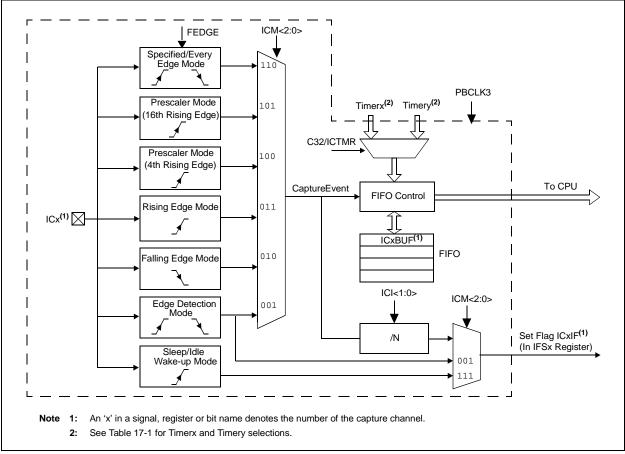

# 17.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin.

Capture events are caused by the following:

• Capture timer value on every edge (rising and falling), specified edge first

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of six 16-bit timers for the time base, or two of six 16-bit timers together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values; Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

## FIGURE 17-1: INPUT CAPTURE BLOCK DIAGRAM

| Bit<br>Range                                                             | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04-04                                                                    | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24                                                                    |                   | HR10              | <3:0>             |                   | HR01<3:0>         |                   |                  |                  |  |  |

| 00.40                                                                    | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16                                                                    |                   | MIN10             | <3:0>             |                   | MIN01<3:0>        |                   |                  |                  |  |  |

| 45.0                                                                     | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8                                                                     |                   | SEC10             | <3:0>             |                   | SEC01<3:0>        |                   |                  |                  |  |  |

| 7.0                                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0                                                                      | —                 | —                 | —                 | —                 | —                 | -                 | —                | —                |  |  |

|                                                                          |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:                                                                  |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 25-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10 digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1 digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

'1' = Bit is set

-n = Value at POR

| REGISTER | 28-2: ADCCON2: ADC CONTROL REGISTER 2 (CONTINUED)                                                                                                                                                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | REFFLTIEN: Band Gap/VREF Voltage Fault Interrupt Enable bit                                                                                                                                                                                                                            |

|          | 1 = Interrupt will be generated when the REFFLT bit is set                                                                                                                                                                                                                             |

|          | 0 = No interrupt is generated when the REFFLT bit is set                                                                                                                                                                                                                               |

| bit 13   | EOSIEN: End of Scan Interrupt Enable bit                                                                                                                                                                                                                                               |

|          | 1 = Interrupt will be generated when EOSRDY bit is set                                                                                                                                                                                                                                 |

|          | 0 = No interrupt is generated when the EOSRDY bit is set                                                                                                                                                                                                                               |

| bit 12   | ADCEIOVR: Early Interrupt Request Override bit                                                                                                                                                                                                                                         |

|          | 1 = Early interrupt generation is not overridden and interrupt generation is controlled by the ADCEIEN1<br>and ADCEIEN2 registers                                                                                                                                                      |

|          | <ul> <li>Early interrupt generation is overridden and interrupt generation is controlled by the ADCGIRQEN1<br/>and ADCGIRQEN2 registers</li> </ul>                                                                                                                                     |

| bit 11   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                             |

| bit 10-8 | ADCEIS<2:0>: Shared ADC (ADC7) Early Interrupt Select bits                                                                                                                                                                                                                             |

|          | These bits select the number of clocks (TAD7) prior to the arrival of valid data that the associated interrupt is generated.                                                                                                                                                           |

|          | 111 = The data ready interrupt is generated 8 ADC clocks prior to end of conversion                                                                                                                                                                                                    |

|          | 110 = The data ready interrupt is generated 7 ADC clocks prior to end of conversion                                                                                                                                                                                                    |

|          | •                                                                                                                                                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                                                                      |

|          | <ul> <li>001 = The data ready interrupt is generated 2 ADC module clocks prior to end of conversion</li> <li>000 = The data ready interrupt is generated 1 ADC module clock prior to end of conversion</li> </ul>                                                                      |

|          | Note: All options are available when the selected resolution, set by the SELRES<1:0> bits (ADCCON1<22:21>), is 12-bit or 10-bit. For a selected resolution of 8-bit, options from '000' to '101' are valid. For a selected resolution of 6-bit, options from '000' to '011' are valid. |

| bit 7    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                             |

| bit 6-0  | ADCDIV<6:0>: Shared ADC (ADC7) Clock Divider bits                                                                                                                                                                                                                                      |

|          | 1111111 = 254 * TQ = TAD7                                                                                                                                                                                                                                                              |

|          | •                                                                                                                                                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                                                                      |

|          | 0000011 = 6 * TQ = TAD7                                                                                                                                                                                                                                                                |

|          | 0000010 = 4 * TQ = TAD7                                                                                                                                                                                                                                                                |

|          | 0000001 = 2 * TQ = TAD7<br>0000000 = Reserved                                                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                                                                                                        |

The ADCDIV<6:0> bits divide the ADC control clock (TQ) to generate the clock for the Shared ADC, ADC7 (TAD7).

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24     | _                 |                   |                   |                   |                   |                   |                  | _                |

| 22.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | _                 | _                 | —                 | _                 | LVL11             | LVL10             | LVL9             | LVL8             |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | LVL7              | LVL6              | LVL5              | LVL4              | LVL3              | LVL2              | LVL1             | LVL0             |

#### REGISTER 28-26: ADCTRGSNS: ADC TRIGGER LEVEL/EDGE SENSITIVITY REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-12 Unimplemented: Read as '0'

- bit 11 LVL11:LVL0: Trigger Level and Edge Sensitivity bits

- 1 = Analog input is sensitive to the high level of its trigger (level sensitivity implies retriggering as long as the trigger signal remains high)

- 0 = Analog input is sensitive to the positive edge of its trigger (this is the value after a reset)

Note 1: This register specifies the trigger level for analog inputs 0 to 31.

2: The higher analog input ID belongs to Class 3, and therefore, is only scan triggered. All Class 3 analog inputs use the Scan Trigger, for which the level/edge is defined by the STRGLVL bit (ADCCON1<3>).

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | R-x                  | R-x               | R-x               | R-x               | R-x               | R-x               | R-x                | R-x                |

| 31.24        |                      |                   |                   | CiFIFOUA          | \n<31:24>         |                   |                    |                    |

| 23:16        | R-x                  | R-x               | R-x               | R-x               | R-x               | R-x               | R-x                | R-x                |

| 23.10        |                      |                   |                   | CiFIFOUA          | n<23:16>          |                   |                    |                    |

| 15.0         | R-x                  | R-x               | R-x               | R-x               | R-x               | R-x               | R-x                | R-x                |

| 15.6         | 15:8 CiFIFOUAn<15:8> |                   |                   |                   |                   |                   |                    |                    |

| 7.0          | R-x                  | R-x               | R-x               | R-x               | R-x               | R-x               | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |

| 7:0          |                      |                   |                   | CiFIFOU           | An<7:0>           |                   |                    |                    |

#### **REGISTER 29-22:** CiFIFOUAn: CAN FIFO USER ADDRESS REGISTER 'n' ('n' = 0-31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 CiFIFOUAn<31:0>: CAN FIFO User Address bits

TXEN = 1: (FIFO configured as a Transmit Buffer)

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0: (FIFO configured as a Receive Buffer)

A read of this register will return the address where the next message is to be read (FIFO tail).

Note 1: This bit will always read '0', which forces byte-alignment of messages.

**Note:** This register is not guaranteed to read correctly in Configuration mode, and should only be accessed when the module is not in Configuration mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | —                 | _                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   | —                 |                   |                   | С                 | iFIFOCIn<4:0      | >                |                  |

#### REGISTER 29-23: CiFIFOCIn: CAN MODULE MESSAGE INDEX REGISTER 'n' ('n' = 0-31)

#### Legend:

| J                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-5 Unimplemented: Read as '0'

bit 4-0 CiFIFOCIn<4:0>: CAN Side FIFO Message Index bits

TXEN = 1: (FIFO configured as a Transmit Buffer)

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0: (FIFO configured as a Receive Buffer)

A read of this register will return an index to the message that the FIFO will use to save the next message.

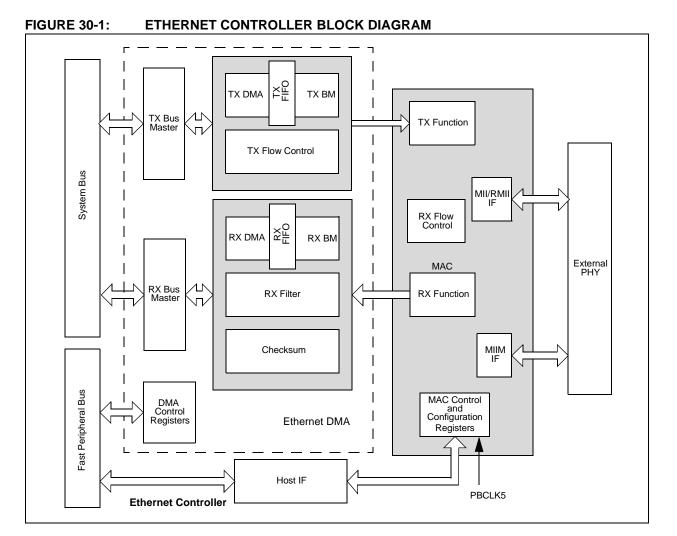

# **30.0 ETHERNET CONTROLLER**

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- · Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- Supports various hardware statistics counters

Figure 30-1 illustrates a block diagram of the Ethernet controller.

| Bit<br>Range            | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24                   | —                 | —                 | _                 | _                 | _                 | —                 | —                | —                |

| 23:16                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10                   |                   | —                 |                   |                   |                   |                   | —                | _                |

| 15:8                    | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |

| 15.8 — NB2BIPKTGP1<6:0> |                   |                   |                   |                   |                   |                   |                  |                  |

| 7:0                     | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

| 7.0                     |                   |                   |                   | NB2E              | BIPKTGP2<6:       | 0>                |                  |                  |

#### REGISTER 30-26: EMAC1IPGR: ETHERNET CONTROLLER MAC NON-BACK-TO-BACK INTERPACKET GAP REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-15 Unimplemented: Read as '0'

#### bit 14-8 NB2BIPKTGP1<6:0>: Non-Back-to-Back Interpacket Gap Part 1 bits

This is a programmable field representing the optional carrierSense window referenced in section 4.2.3.2.1 "Deference" of the IEEE 80.23 Specification. If carrier is detected during the timing of IPGR1, the MAC defers to carrier. If, however, carrier becomes after IPGR1, the MAC continues timing IPGR2 and transmits, knowingly causing a collision, thus ensuring fair access to medium. Its range of values is 0x0 to IPGR2. Its recommend value is 0xC (12d).

#### bit 7 Unimplemented: Read as '0'

#### bit 6-0 NB2BIPKTGP2<6:0>: Non-Back-to-Back Interpacket Gap Part 2 bits This is a programmable field representing the non-back-to-back Inter-Packet-Gap. Its r

This is a programmable field representing the non-back-to-back Inter-Packet-Gap. Its recommended value is 0x12 (18d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps).

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| REGISTI   | ER 34-9: CFGEBIC: EXTERNAL BUS INTERFACE CONTROL PIN CONFIGURATION<br>REGISTER (CONTINUED)                                                          |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 12    | EBIOEEN: EBIOE Pin Enable bit                                                                                                                       |  |

|           | $1 = \overline{\text{EBIOE}}$ pin is enabled for use by the EBI module                                                                              |  |

|           | 0 = EBIOE pin is available for general use                                                                                                          |  |

| bit 11-10 | Unimplemented: Read as '0'                                                                                                                          |  |

| bit 9     | EBIBSEN1: EBIBS1 Pin Enable bit                                                                                                                     |  |

|           | 1 = EBIBS1 pin is enabled for use by the EBI module<br>0 = EBIBS1 pin is available for general use                                                  |  |

| bit 8     | EBIBSEN1: EBIBSO Pin Enable bit                                                                                                                     |  |

| DIT O     | $1 = \overline{\text{EBIBS0}}$ pin is enabled for use by the EBI module                                                                             |  |

|           | 0 = EBIBS0 pin is available for general use                                                                                                         |  |

| bit 7     | EBICSEN3: EBICS3 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{EBICS3}$ pin is enabled for use by the EBI module                                                                                    |  |

|           | 0 = EBICS3 pin is available for general use                                                                                                         |  |

| bit 6     | EBICSEN2: EBICS2 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{\text{EBICS2}}$ pin is enabled for use by the EBI module                                                                             |  |

|           | 0 = EBICS2 pin is available for general use                                                                                                         |  |

| bit 5     | EBICSEN1: EBICS1 Pin Enable bit                                                                                                                     |  |

|           | 1 = EBICS1 pin is enabled for use by the EBI module                                                                                                 |  |

|           | 0 = EBICS1 pin is available for general use                                                                                                         |  |

| bit 4     | EBICSEN0: EBICS0 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{\text{EBICS0}}$ pin is enabled for use by the EBI module                                                                             |  |

| 1         | 0 = EBICS0 pin is available for general use                                                                                                         |  |

| bit 3-2   | Unimplemented: Read as '0'                                                                                                                          |  |

| bit 1     | EBIDEN1: EBI Data Upper Byte Pin Enable bit                                                                                                         |  |

|           | <ul> <li>1 = EBID&lt;15:8&gt; pins are enabled for use by the EBI module</li> <li>0 = EBID&lt;15:8&gt; pins have reverted to general use</li> </ul> |  |

| bit 0     | <b>EBIDEN0:</b> EBI Data Lower Byte Pin Enable bit                                                                                                  |  |

| DILU      | 1 = EBID<7:0> pins are enabled for use by the EBI module                                                                                            |  |

|           | 1 = EBID<7.0> pins are enabled for use by the EBI module<br>0 = EBID<7:0> pins have reverted to general use                                         |  |

|           |                                                                                                                                                     |  |

| Note:     | When EBIMD = 1, the bits in this register are ignored and the pins are available for general use.                                                   |  |

#### 36.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 36.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 36.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 36.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 36.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

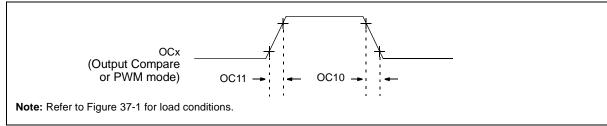

#### FIGURE 37-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 37-28: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

|               |        | Standard Operating Conditions: 2.1V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |                        |      |       |                    |

|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|------|-------|--------------------|

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup>                                                                                                                                                                       | Min. | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| OC10          | TccF   | OCx Output Fall Time                                                                                                                                                                                 | —    | _                      | _    | ns    | See parameter DO32 |

| OC11          | TCCR   | OCx Output Rise Time                                                                                                                                                                                 | —    | —                      | _    | ns    | See parameter DO31 |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

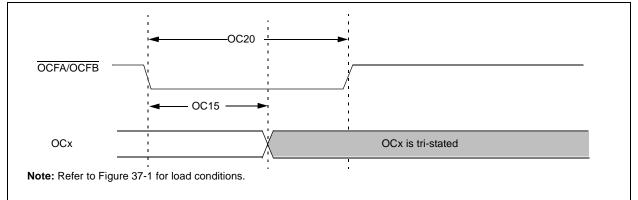

#### FIGURE 37-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 37-29: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |                        |     |       |            |

|--------------------|--------|-------------------------------------------------------|-----|------------------------|-----|-------|------------|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup>                        | Min | Typical <sup>(2)</sup> | Max | Units | Conditions |

| OC15               | Tfd    | Fault Input to PWM I/O Change                         | —   | —                      | 50  | ns    |            |

| OC20               | TFLT   | Fault Input Pulse Width                               | 50  | —                      |     | ns    |            |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

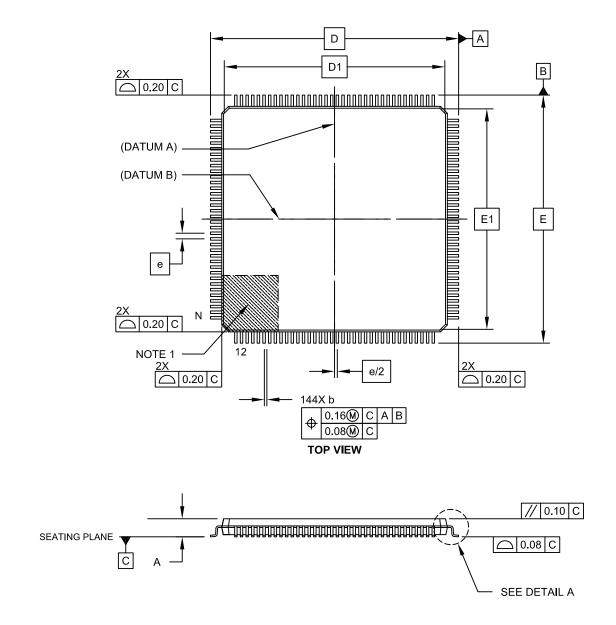

# 144-Lead Plastic Low Profile Quad Flatpack (PL) – 20x20x1.40 mm Body, with 2.00 mm Footprint [LQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-044B Sheet 1 of 2

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                                 | PIC32MZ EF Feature                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Fail-Safe Clock Monitor (FSCM)                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| On PIC32MX devices, the internal FRC became the clock source on a failure of the clock source.                                                                                             | On PIC32MZ EF devices, a separate internal Backup FRC (BFRC) becomes the clock source upon a failure at the clock source.                                                                                                                                                                                                                                           |  |  |  |  |

| On PIC32MX devices, a clock failure resulted in the triggering of a specific interrupt when the switchover was complete.                                                                   | On PIC32MZ EF devices, a NMI is triggered instead, and must be handled by the NMI routine.                                                                                                                                                                                                                                                                          |  |  |  |  |