Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 512K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efm100-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                                                                 |                        | Pin Nu          | mber            |                       |         |                |                                                                            |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|-----------------|-----------------------|---------|----------------|----------------------------------------------------------------------------|--|

| Pin Name                                                                                                                                        | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 4-pin TOFP/ Type Type |         | Buffer<br>Type | Description                                                                |  |

|                                                                                                                                                 |                        |                 |                 |                       | J       | ΓAG            |                                                                            |  |

| ТСК                                                                                                                                             | 27                     | 38              | B21             | 56                    | I       | ST             | JTAG Test Clock Input Pin                                                  |  |

| TDI                                                                                                                                             | 28                     | 39              | A26             | 57                    | I       | ST             | JTAG Test Data Input Pin                                                   |  |

| TDO                                                                                                                                             | 24                     | 40              | B22             | 58                    | 0       | —              | JTAG Test Data Output Pin                                                  |  |

| TMS                                                                                                                                             | 23                     | 17              | A11             | 22                    | I       | ST             | JTAG Test Mode Select Pin                                                  |  |

| Trace                                                                                                                                           |                        |                 |                 |                       |         |                |                                                                            |  |

| TRCLK                                                                                                                                           | 57                     | 89              | A61             | 129                   | 0       | _              | Trace Clock                                                                |  |

| TRD0                                                                                                                                            | 58                     | 97              | B55             | 141                   | 0       | —              | Trace Data bits 0-3                                                        |  |

| TRD1                                                                                                                                            | 61                     | 96              | A65             | 140                   | 0       | —              |                                                                            |  |

| TRD2                                                                                                                                            | 62                     | 95              | B54             | 139                   | 0       | —              |                                                                            |  |

| TRD3                                                                                                                                            | 63                     | 90              | B51             | 130                   | 0       | —              |                                                                            |  |

|                                                                                                                                                 |                        |                 |                 | Pro                   | grammiı | ng/Debugg      | ing                                                                        |  |

| PGED1                                                                                                                                           | 16                     | 25              | A18             | 36                    | I/O     | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 1          |  |

| PGEC1                                                                                                                                           | 15                     | 24              | A17             | 35                    | Ι       | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 1       |  |

| PGED2                                                                                                                                           | 18                     | 27              | A19             | 38                    | I/O     | ST             | Data I/O pin for Programming/Debugging<br>Communication Channel 2          |  |

| PGEC2                                                                                                                                           | 17                     | 26              | B14             | 37                    | Ι       | ST             | Clock input pin for Programming/Debugging<br>Communication Channel 2       |  |

| MCLR                                                                                                                                            | 9                      | 15              | A10             | 20                    | l/P     | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device. |  |

| Legend: CMOS = CMOS-compatible input or output<br>ST = Schmitt Trigger input with CMOS levels<br>TTL = Transistor-transistor Logic input buffer |                        |                 |                 |                       |         | O = Outp       | Analog input P = Power<br>ut I = Input<br>eripheral Pin Select             |  |

#### **TABLE 1-22:** JTAG, TRACE, AND PROGRAMMING/DEBUGGING PINOUT I/O DESCRIPTIONS

| REGISTE | ER 5-8:   | NVMBWP: FLASH BOOT (PAGE) WRITE-PROTECT REGISTER                                                                                               |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | UBWP4:    | Upper Boot Alias Page 4 Write-protect bit <sup>(1)</sup>                                                                                       |

|         |           | protection for physical address 0x01FC30000 through 0x1FC33FFF enabled protection for physical address 0x01FC30000 through 0x1FC33FFF disabled |

| bit 3   | UBWP3:    | Upper Boot Alias Page 3 Write-protect bit <sup>(1)</sup>                                                                                       |

|         | 0 = Write | protection for physical address 0x01FC2C000 through 0x1FC2FFFF enabled protection for physical address 0x01FC2C000 through 0x1FC2FFFF disabled |

| bit 2   | UBWP2:    | Upper Boot Alias Page 2 Write-protect bit <sup>(1)</sup>                                                                                       |

|         |           | protection for physical address 0x01FC28000 through 0x1FC2BFFF enabled protection for physical address 0x01FC28000 through 0x1FC2BFFF disabled |

| bit 1   | UBWP1:    | Upper Boot Alias Page 1 Write-protect bit <sup>(1)</sup>                                                                                       |

|         | 0 = Write | protection for physical address 0x01FC24000 through 0x1FC27FFF enabled protection for physical address 0x01FC24000 through 0x1FC27FFF disabled |

| bit 0   | UBWP0:    | Upper Boot Alias Page 0 Write-protect bit <sup>(1)</sup>                                                                                       |

|         |           | protection for physical address 0x01FC20000 through 0x1FC23FFF enabled protection for physical address 0x01FC20000 through 0x1FC23FFF disabled |

|         |           |                                                                                                                                                |

**Note 1:** These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (LBWPULOCK or UBWPULOCK) is set.

Note: The bits in this register are only writable when the NVMKEY unlock sequence is followed.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | —                 |                   | IP3<2:0>          | IS3<1:0>          |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | —                 | _                 | IP2<2:0>          |                   |                   | IS2<1:0>         |                  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | _                 | —                 | _                 |                   | IP1<2:0>          |                   | IS1<             | :1:0>            |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | _                 |                   | IP0<2:0>          |                   | IS0<             | :1:0>            |

# REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

# bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: Interrupt Priority bits                                  |

|-----------|--------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 25-24 | IS3<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1                                    |

|           | 00 = Interrupt subpriority is 0                                    |

| bit 23-21 |                                                                    |

| bit 20-18 | IP2<2:0>: Interrupt Priority bits                                  |

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 17-16 | IS2<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1<br>00 = Interrupt subpriority is 0 |

| hit 15-13 | Unimplemented: Read as '0'                                         |

| 5115-15   | ommplemented. Read as 0                                            |

| Note:     | This register represents a generic defi                            |

|           |                                                                    |

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-2 for the exact bit definitions.

| REGISTE  | ER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER                                                                                                                           |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10-8 | NOSC<2:0>: New Oscillator Selection bits                                                                                                                              |

|          | 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                                                          |

|          | 110 = Reserved                                                                                                                                                        |

|          | 101 = Internal Low-Power RC (LPRC) Oscillator                                                                                                                         |

|          | 100 = Secondary Oscillator (Sosc)<br>011 = Reserved                                                                                                                   |

|          | 010 = Primary Oscillator (Posc) (HS or EC)                                                                                                                            |

|          | 001 = System PLL (SPLL)                                                                                                                                               |

|          | 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)                                                                                          |

|          | On Reset, these bits are set to the value of the FNOSC<2:0> Configuration bits (DEVCFG1<2:0>).                                                                        |

| bit 7    | CLKLOCK: Clock Selection Lock Enable bit                                                                                                                              |

|          | 1 = Clock and PLL selections are locked                                                                                                                               |

|          | 0 = Clock and PLL selections are not locked and may be modified                                                                                                       |

| bit 6-5  | Unimplemented: Read as '0'                                                                                                                                            |

| bit 4    | SLPEN: Sleep Mode Enable bit                                                                                                                                          |

|          | <ul> <li>1 = Device will enter Sleep mode when a WAIT instruction is executed</li> <li>0 = Device will enter Idle mode when a WAIT instruction is executed</li> </ul> |

| hi+ 0    | <b>CF:</b> Clock Fail Detect bit                                                                                                                                      |

| bit 3    |                                                                                                                                                                       |

|          | <ul> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> </ul>                                                             |

| bit 2    | Unimplemented: Read as '0'                                                                                                                                            |

| bit 1    | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                                                                        |

|          | 1 = Enable Secondary Oscillator                                                                                                                                       |

|          | 0 = Disable Secondary Oscillator                                                                                                                                      |

| bit 0    | OSWEN: Oscillator Switch Enable bit <sup>(1)</sup>                                                                                                                    |

|          | 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits                                                                                            |

|          | 0 = Oscillator switch is complete                                                                                                                                     |

| Note 1:  | The reset value for this bit depends on the setting of the IESO bit (DEVCFG1<7>). When IESO = 1, the                                                                  |

| NOLE I.  | reset value is '1'. When IESO = 0, the reset value is '0'.                                                                                                            |

Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

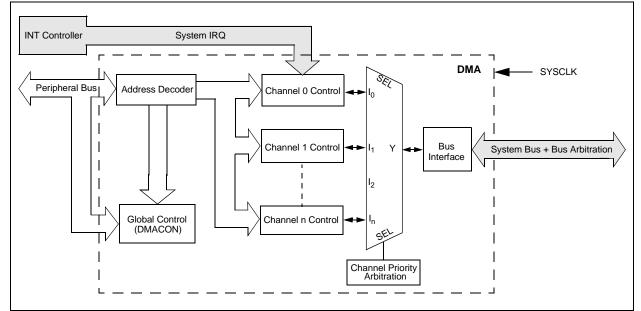

# 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Direct Memory Access (DMA) Controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the device such as SPI, UART, PMP, etc., or memory itself.

The following are key features of the DMA Controller:

- Eight identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

# FIGURE 10-1: DMA BLOCK DIAGRAM

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Up to 2-byte Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent error address accessed by a DMA channel

- Most recent DMA channel to transfer data

- CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                          |                   |                   | —                 | —                 | _                 |                  | —                |  |

| 00.40        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |

| 7:0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN            | _                 | _                | _                |  |

# REGISTER 10-8: DCHxECON: DMA CHANNEL x EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

and set CHAIF flag

#### bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>   |

|-----------|---------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress |

|           | •                                                             |

|           | •                                                             |

|           | •                                                             |

|           |                                                               |

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

# bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits<sup>(1)</sup>

11111111 = Interrupt 255 will initiate a DMA transfer

• 00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

#### bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

#### bit 6 CABORT: DMA Abort Transfer bit

- 1 = A DMA transfer is aborted when this bit is written to a '1'

- 0 = This bit always reads '0'

# bit 5 **PATEN:** Channel Pattern Match Abort Enable bit

- 1 = Abort transfer and clear CHEN on pattern match

- 0 = Pattern match is disabled

- bit 4 SIRQEN: Channel Start IRQ Enable bit

- 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

- 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-2: "Interrupt IRQ, Vector, and Bit Location" for the list of available interrupt IRQ sources.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | _                 |                   | -                 |                   | —                | —                |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          |                   |                   |                   | CHSPTF            | R<7:0>            |                   |                  |                  |  |

#### REGISTER 10-14: DCHxSPTR: DMA CHANNEL x SOURCE POINTER REGISTER

# Legend:

| Logona.           |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

111111111111111 = Points to byte 65,535 of the source

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   |                   | _                 |                   | —                 |                   |                  | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

|              |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |  |  |  |

#### **REGISTER 10-15: DCHxDPTR: DMA CHANNEL x DESTINATION POINTER REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

111111111111111 = Points to byte 65,535 of the destination

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   | _                 | _                 | —                 | _                 | -                 | _                | _                |  |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   |                   |                   |                   | -                 |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHPDAT<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | CHPDAT            | <7:0>             |                   |                  |                  |  |  |

# REGISTER 10-18: DCHxDAT: DMA CHANNEL x PATTERN DATA REGISTER

# Legend:

| 3                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **CHPDAT<15:0>:** Channel Data Register bits <u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

> All other modes: Unused.

# TABLE 12-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                       |           |       | Bits  |       |       |       |       |      |      |      |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 15B4                        | RPC13R                | 31:16     | _     |       | —     |       | _     |       |      | _    |      | —    | —    | —    | —    | —     | _      | -    | 0000       |

| 1364                        | RECISK                | 15:0      | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    |      | RPC13 | R<3:0> |      | 0000       |

| 15B8                        | RPC14R                | 31:16     | _     |       | _     |       | _     |       |      | _    |      | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1300                        | KFC14K                | 15:0      | _     |       | _     |       | —     |       |      | _    |      | -    | _    | _    |      | RPC14 | R<3:0> |      | 0000       |

| 15C0                        | RPD0R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1300                        | REDOR                 | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD0  | R<3:0> |      | 0000       |

| 15C4                        | RPD1R                 | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | _    |      |      | _     | —      | —    | 0000       |

| 1304                        | REDIK                 | 15:0      | —     |       | —     | _     | —     | _     |      | —    | _    | —    | —    | —    |      | RPD1  | R<3:0> |      | 0000       |

| 15C8                        | RPD2R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1300                        | KF D2K                | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | _    |      |      | RPD2  | R<3:0> |      | 0000       |

| 15CC                        | RPD3R                 | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1300                        | KF D3K                | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD3  | R<3:0> |      | 0000       |

| 15D0                        | RPD4R                 | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | _    |      |      | _     | —      | —    | 0000       |

| 1300                        |                       | 15:0      | _     | _     | _     | -     | —     | _     | _    | —    | -    | _    | _    | _    |      | RPD4  | R<3:0> |      | 0000       |

| 15D4                        | RPD5R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1304                        | REDSK                 | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | _    | —    |      | RPD5  | R<3:0> |      | 0000       |

| 15D8                        | RPD6R <sup>(2)</sup>  | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | _    | —    |      | _     | —      | —    | 0000       |

| 1300                        | KFD0K*/               | 15:0      | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | RPD6  | R<3:0> |      | 0000       |

| 15DC                        | RPD7R <sup>(2)</sup>  | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | _    | —    |      | _     | —      | —    | 0000       |

| 1300                        | KFD/K·/               | 15:0      | _     | _     | _     | -     | —     | _     | _    | —    | -    | _    | _    | _    |      | RPD7  | R<3:0> |      | 0000       |

| 15E4                        | RPD9R                 | 31:16     | —     | -     | —     | -     | —     | —     | -    | —    | -    | —    | —    |      |      | —     | —      | —    | 0000       |

| 1324                        | KF D9K                | 15:0      | —     | _     |       | _     | _     | _     | _    | —    | _    |      | _    | —    |      | RPD9  | R<3:0> |      | 0000       |

| 15E8                        | RPD10R                | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | _    | —    |      | _     | —      | —    | 0000       |

| 1020                        | IN DIGIN              | 15:0      | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    |      | RPD10 | R<3:0> |      | 0000       |

| 15EC                        | RPD11R                | 31:16     | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1020                        | KI DIIK               | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD11 | R<3:0> |      | 0000       |

| 15F0                        | RPD12R <sup>(1)</sup> | 31:16     | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1010                        | KI DIZIK <sup>1</sup> | 15:0      | —     | —     | —     | _     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPD12 | R<3:0> |      | 0000       |

| 15F8                        | RPD14R <sup>(1)</sup> | 31:16     | —     | _     |       | _     | _     | _     | _    | —    | _    |      | _    | —    |      | _     | —      | —    | 0000       |

| 101.0                       | IN DI4IN              | 15:0      | —     | _     | —     | _     | —     | _     | _    | —    | _    | —    | —    | —    |      | RPD14 | R<3:0> |      | 0000       |

| 15FC                        | RPD15R <sup>(1)</sup> | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1010                        | N D ION /             | 15:0      | —     | _     |       |       | —     | _     | _    | —    | _    |      | _    |      |      | RPD15 | R<3:0> |      | 0000       |

| 160C                        | RPE3R                 | 31:16     | —     | _     | —     | _     | —     | —     | _    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1000                        | INF LOIN              | 15:0      | —     | -     | —     |       | _     | -     | -    | —    |      | —    | —    | —    |      | RPE3  | R<3:0> |      | 0000       |

| 1614                        | RPE5R                 | 31:16     | _     |       | —     |       | —     |       |      | _    | —    | —    | —    | _    | —    | —     | —      | —    | 0000       |

| 1014                        |                       | 15:0      | —     |       | _     | —     | —     | —     | —    | —    | —    | —    | —    | _    |      | RPE5  | R<3:0> |      | 0000       |

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is not available on 64-pin devices. Note 1:

This register is not available on 64-pin and 100-pin devices. 2:

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        |                      | —                 |                     |                   | —                  |                   |                    | —                |

| 22:46        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23:16        |                      | —                 | _                   | —                 | —                  | —                 | —                  | —                |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1)</sup>    | —                 | SIDL <sup>(2)</sup> | _                 | —                  | _                 | _                  | —                |

| 7:0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(1)</sup> | Т                 | CKPS<2:0>(          | 1)                | T32 <sup>(3)</sup> | _                 | TCS <sup>(1)</sup> | —                |

#### TxCON: TYPE B TIMER CONTROL REGISTER ('x' = 2-9) REGISTER 14-1:

#### Legend:

bit 3

| R = Readable bit  | Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |  |

|-------------------|-------------------------------|----------------------|------------------------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: Timer On bit<sup>(1)</sup>

- 1 = Module is enabled 0 = Module is disabled

- Unimplemented: Read as '0'

#### bit 14 bit 13 SIDL: Stop in Idle Mode bit<sup>(2)</sup>

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation even in Idle mode

#### Unimplemented: Read as '0' bit 12-8

TGATE: Timer Gated Time Accumulation Enable bit<sup>(1)</sup> bit 7

#### When TCS = 1:

This bit is ignored and is read as '0'.

# When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 = Gated time accumulation is disabled

#### bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(1)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

# 000 = 1:1 prescale value

# T32: 32-Bit Timer Mode Select bit(3)

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form separate 16-bit timers

- Note 1: While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, Timer5, Timer7, and Timer9). All timer functions are set through the even numbered timers.

- While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer 2: in Idle mode.

- 3: This bit is available only on even numbered timers (Timer2, Timer4, Timer6, and Timer8).

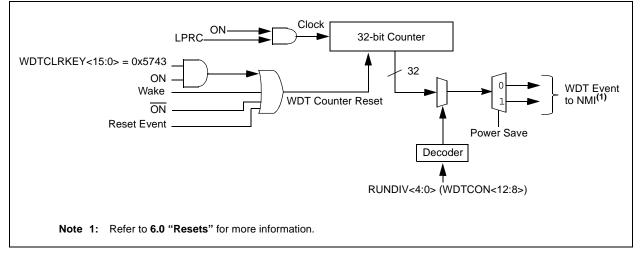

# 16.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). When enabled, the Watchdog Timer (WDT) operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

# FIGURE 16-1: WATCHDOG TIMER BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |  |

|--------------|--------------------------|----------------------|--------------------|-------------------|-------------------|-------------------|----------------------|------------------|--|--|

| 31:24        | U-0                      | U-0                  | U-0                | U-0               | U-0               | U-0               | U-0                  | U-0              |  |  |

|              | —                        |                      | —                  | -                 | —                 |                   | —                    |                  |  |  |

| 00.40        | U-0                      | U-0                  | U-0                | U-0               | U-0               | U-0               | U-0                  | U-0              |  |  |

| 23:16        | —                        | —                    | —                  | —                 | —                 | —                 | —                    | _                |  |  |

| 45.0         | R/W-0                    | R/W-0                | R/W-0              | R-0               | R/W-0             | R/W-0             | R/W-0                | R/W-0            |  |  |

| 15:8         | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC          |                   | AMASK             | <3:0> <sup>(2)</sup> |                  |  |  |

| 7.0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |  |  |

| 7:0          | ARPT<7:0> <sup>(2)</sup> |                      |                    |                   |                   |                   |                      |                  |  |  |

#### REGISTER 25-2: RTCALRM: REAL-TIME CLOCK ALARM CONTROL REGISTER

#### Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

# bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is more than 32 real-time clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved

- 1011 = Reserved

- 11xx = Reserved

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

#### **Note:** This register is reset only on a Power-on Reset (POR).

© 2015-2016 Microchip Technology Inc.

# 26.2 Crypto Engine Buffer Descriptors

Host software creates a linked list of buffer descriptors and the hardware updates them. Table 26-3 provides a list of the Crypto Engine buffer descriptors, followed by format descriptions of each buffer descriptor (see Figure 26-2 through Figure 26-9).

| Name (see No | ote 1) | Bit<br>31/2315/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|--------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| BD_CTRL      | 31:24  | DESC_EN           | —                 | (                 | CRY_MODE<2:0      | >                 | —                 | _                | _                |  |  |  |

|              | 23:16  | _                 | SA_FETCH_EN       | -                 | _                 | LAST_BD           | LIFM              | PKT_INT_EN       | CBD_INT_EN       |  |  |  |

|              | 15:8   |                   |                   |                   | BD_BUFLEN         | <15:8>            | •                 |                  |                  |  |  |  |

|              | 7:0    |                   |                   |                   | BD_BUFLEN         | N<7:0>            |                   |                  |                  |  |  |  |

| BD_SA_ADDR   | 31:24  | BD_SAADDR<31:24>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|              | 23:16  |                   | BD_SAADDR<23:16>  |                   |                   |                   |                   |                  |                  |  |  |  |

|              | 15:8   |                   |                   |                   | BD_SAADDR         | <15:8>            |                   |                  |                  |  |  |  |

|              | 7:0    |                   |                   |                   | BD_SAADR          | <7:0>             |                   |                  |                  |  |  |  |

| BD_SCRADDR   | 31:24  |                   |                   |                   | BD_SRCADDF        | <31:24>           |                   |                  |                  |  |  |  |

|              | 23:16  |                   |                   |                   | BD_SRCADDF        | R<23:16>          |                   |                  |                  |  |  |  |

|              | 15:8   |                   |                   |                   | BD_SRCADD         | R<15:8>           |                   |                  |                  |  |  |  |

|              | 7:0    | BD_SRCADDR<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| BD_DSTADDR   | 31:24  |                   | BD_DSTADDR<31:24> |                   |                   |                   |                   |                  |                  |  |  |  |

|              | 23:16  | BD_DSTADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|              | 15:8   | BD_DSTADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|              | 7:0    |                   |                   |                   | BD_DSTADD         | R<7:0>            |                   |                  |                  |  |  |  |

| BD_NXTPTR    | 31:24  |                   |                   |                   | BD_NXTADDR        | <31:24>           |                   |                  |                  |  |  |  |

|              | 23:16  | BD_NXTADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|              | 15:8   | BD_NXTADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|              | 7:0    | BD_NXTADDR<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| BD_UPDPTR    | 31:24  |                   |                   |                   | BD_UPDADDF        | R<31:24>          |                   |                  |                  |  |  |  |

|              | 23:16  |                   |                   |                   | BD_UPDADDF        | R<23:16>          |                   |                  |                  |  |  |  |

|              | 15:8   |                   |                   |                   | BD_UPDADDI        | R<15:8>           |                   |                  |                  |  |  |  |

|              | 7:0    |                   |                   |                   | BD_UPDADD         | R<7:0>            |                   |                  |                  |  |  |  |

| BD_MSG_LEN   | 31:24  |                   |                   |                   | MSG_LENGTH        | 1<31:24>          |                   |                  |                  |  |  |  |

|              | 23:16  |                   |                   |                   | MSG_LENGTH        | 1<23:16>          |                   |                  |                  |  |  |  |

|              | 15:8   |                   |                   |                   | MSG_LENGT         | H<15:8>           |                   |                  |                  |  |  |  |

|              | 7:0    |                   |                   |                   | MSG_LENGT         | H<7:0>            |                   |                  |                  |  |  |  |

| BD_ENC_OFF   | 31:24  |                   |                   |                   | ENCR_OFFSE        | T<31:24>          |                   |                  |                  |  |  |  |

|              | 23:16  |                   |                   |                   | ENCR_OFFSE        | T<23:16>          |                   |                  |                  |  |  |  |

|              | 15:8   |                   |                   |                   | ENCR_OFFSE        | T<15:8>           |                   |                  |                  |  |  |  |

|              | 7:0    |                   |                   |                   | ENCR_OFFSI        | ET<7:0>           |                   |                  |                  |  |  |  |

#### TABLE 26-3: CRYPTO ENGINE BUFFER DESCRIPTORS

**Note** 1: The buffer descriptor must be allocated in memory on a 64-bit boundary.

# PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

REGISTER 29-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED) bit 15 FLTEN5: Filter 17 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 14-13 MSEL5<1:0>: Filter 5 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL5<4:0>: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN4: Filter 4 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL4<1:0>: Filter 4 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL4<4:0>: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0 The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. Note:

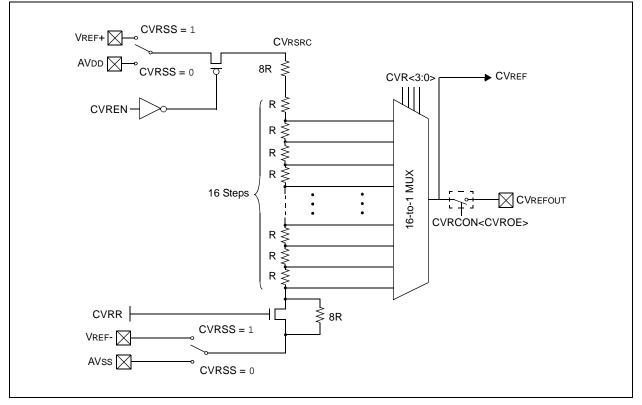

# 32.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

| Note: | This data sheet summarizes the          |

|-------|-----------------------------------------|

|       | features of the PIC32MZ EF family of    |

|       | devices. It is not intended to be a     |

|       | comprehensive reference source. To      |

|       | complement the information in this data |

|       | sheet, refer to Section 20. "Comparator |

|       | Voltage Reference (CVREF)"              |

|       | (DS60001109) in the "PIC32 Family       |

|       | Reference Manual", which is available   |

|       | from the Microchip web site             |

|       | (www.microchip.com/PIC32).              |

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The comparator voltage reference has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

A block diagram of the CVREF module is illustrated in Figure 32-1.

# 33.3 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 33-1 for more information.

| Note: | Disabling a peripheral module while it's   |

|-------|--------------------------------------------|

|       | ON bit is set, may result in undefined     |

|       | behavior. The ON bit for the associated    |

|       | peripheral module must be cleared prior to |

|       | disable a module via the PMDx bits.        |

| Peripheral                   | PMDx bit Name | Register Name and Bit Location PMD1<0> |  |  |

|------------------------------|---------------|----------------------------------------|--|--|

| ADC                          | ADCMD         |                                        |  |  |

| Comparator Voltage Reference | CVRMD         | PMD1<12>                               |  |  |

| Comparator 1                 | CMP1MD        | PMD2<0>                                |  |  |

| Comparator 2                 | CMP2MD        | PMD2<1>                                |  |  |

| Input Capture 1              | IC1MD         | PMD3<0>                                |  |  |

| Input Capture 2              | IC2MD         | PMD3<1>                                |  |  |

| Input Capture 3              | IC3MD         | PMD3<2>                                |  |  |

| Input Capture 4              | IC4MD         | PMD3<3>                                |  |  |

| Input Capture 5              | IC5MD         | PMD3<4>                                |  |  |

| Input Capture 6              | IC6MD         | PMD3<5>                                |  |  |

| Input Capture 7              | IC7MD         | PMD3<6>                                |  |  |

| Input Capture 8              | IC8MD         | PMD3<7>                                |  |  |

| Input Capture 9              | IC9MD         | PMD3<8>                                |  |  |

| Output Compare 1             | OC1MD         | PMD3<16>                               |  |  |

| Output Compare 2             | OC2MD         | PMD3<17>                               |  |  |

| Output Compare 3             | OC3MD         | PMD3<18>                               |  |  |

| Output Compare 4             | OC4MD         | PMD3<19>                               |  |  |

| Output Compare 5             | OC5MD         | PMD3<20>                               |  |  |

| Output Compare 6             | OC6MD         | PMD3<21>                               |  |  |

| Output Compare 7             | OC7MD         | PMD3<22>                               |  |  |

| Output Compare 8             | OC8MD         | PMD3<23>                               |  |  |

| Output Compare 9             | OC9MD         | PMD3<24>                               |  |  |

| Timer1                       | T1MD          | PMD4<0>                                |  |  |

| Timer2                       | T2MD          | PMD4<1>                                |  |  |

| Timer3                       | T3MD          | PMD4<2>                                |  |  |

| Timer4                       | T4MD          | PMD4<3>                                |  |  |

| Timer5                       | T5MD          | PMD4<4>                                |  |  |

| Timer6                       | T6MD          | PMD4<5>                                |  |  |

| Timer7                       | T7MD PMD4<6   |                                        |  |  |

| Timer8                       | T8MD PMD4<7>  |                                        |  |  |

| Timer9                       | T9MD          | PMD4<8>                                |  |  |

| UART1                        | U1MD          | PMD5<0>                                |  |  |

| UART2                        | U2MD          | PMD5<1>                                |  |  |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MZ EF Family Features" for the lists of available peripherals.

2: Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

| DC CHARACTERISTICS |      | SUIPUT SPECIFICATIONSStandard Operating Conditions: 2.1V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended                                                                                 |      |      |      |       |                              |

|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|------------------------------|

| Param.             | Sym. | Characteristic                                                                                                                                                                                                                                                                                            | Min. | Тур. | Max. | Units | Conditions <sup>(1)</sup>    |

| DO10               | Vol  | Output Low Voltage<br>I/O Pins<br>4x Sink Driver Pins -<br>RA3, RA9, RA10, RA14, RA15<br>RB0-RB2, RB4, RB6, RB7, RB11, RB13<br>RC12-RC15<br>RD0, RD6-RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8<br>RG15<br>RH0, RH1, RH4-RH6, RH8-RH13<br>RJ0-RJ2, RJ8, RJ9, RJ11                                       |      | _    | 0.4  | V     | Iol $\leq$ 10 mA, VDD = 3.3V |

|                    |      | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins -<br>RA0-RA2, RA4, RA5<br>RB3, RB5, RB8-RB10, RB12, RB14, RB15<br>RC1-RC4<br>RD1-RD5, RD9, RD10, RD12, RD13, RD15<br>RE4-RE7<br>RF0, RF4, RF5, RF12, RF13<br>RG0, RG1, RG6-RG9<br>RH2, RH3, RH7, RH14, RH15<br>RJ3-RJ7, RJ10, RJ12-RJ15<br>RK0-RK7 | _    | _    | 0.4  | V     | Iol ≤ 15 mA, Vdd = 3.3V      |

|                    |      | Output Low Voltage<br>I/O Pins:<br>12x Sink Driver Pins -<br>RA6, RA7<br>RE0-RE3<br>RF1<br>RG12-RG14                                                                                                                                                                                                      | _    | _    | 0.4  | v     | Iol $\leq$ 20 mA, Vdd = 3.3V |

Note 1: Parameters are characterized, but not tested.

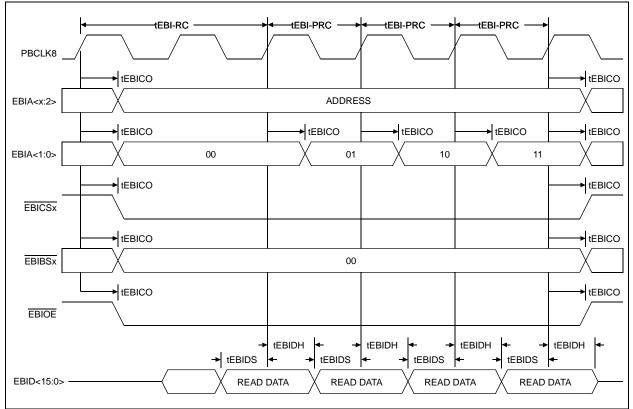

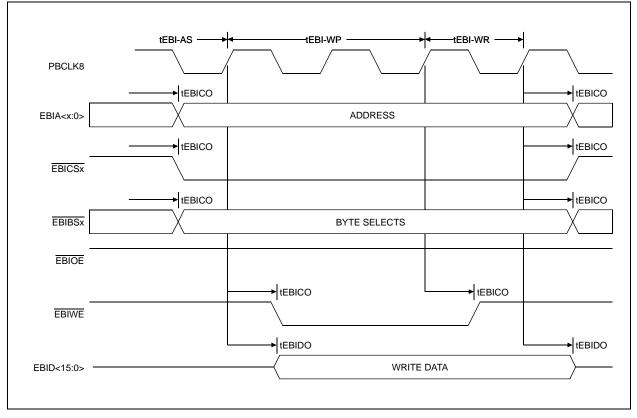

### FIGURE 37-28: EBI PAGE READ TIMING

# FIGURE 37-29: EBI WRITE TIMING

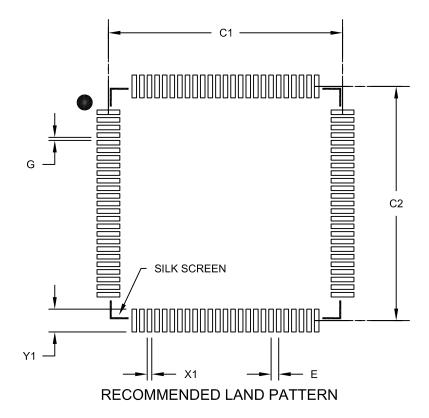

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                     |    | MILLIMETERS |          |      |  |

|---------------------------|----|-------------|----------|------|--|

| Dimension Limits          |    | MIN         | NOM      | MAX  |  |

| Contact Pitch             | E  |             | 0.50 BSC |      |  |

| Contact Pad Spacing       | C1 |             | 15.40    |      |  |

| Contact Pad Spacing       | C2 |             | 15.40    |      |  |

| Contact Pad Width (X100)  | X1 |             |          | 0.30 |  |

| Contact Pad Length (X100) | Y1 |             |          | 1.50 |  |

| Distance Between Pads     | G  | 0.20        |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

# APPENDIX B: MIGRATING FROM PIC32MZ EC TO PIC32MZ EF

This appendix provides an overview of considerations for migrating from PIC32MZ EC devices to the PIC32MZ EF family of devices. The code developed for PIC32MZ EC devices can be ported to PIC32MZ EF devices after making the appropriate changes outlined in the following sections. The PIC32MZ EF devices are similar to PIC32MZ EC devices, with many feature improvements and new capabilities.

# B.1 Oscillator and PLL Configuration

A number of new features have been added to the oscillator and PLL to enhance their ability to work with crystals and to change frequencies.

Table B-1 summarizes the differences (indicated by **Bold** type) between the family differences for the oscillator.

| PIC32MZ EC Feature                                                                                                                                                            | PIC32MZ EF Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Primary Oscillator Crystal Power                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| On PIC32MZ EC devices, the crystal HS Posc mode is only<br>functional with crystals that have certain characteristics, such as<br>very low ESR.                               | On PIC32MZ EF devices, some DEVCFG0 bits have been<br>added to allow control over the strength of the oscillator and to<br>add a kick start boost.<br>POSCBOOST (DEVCFG0<21>)<br>1 = Boost the kick start of the oscillator<br>0 = Normal start of the oscillator<br>POSCGAIN<1:0> (DEVCFG0<20:19>)<br>11 = 2x gain setting<br>10 = 1.5x gain setting<br>01 = 0.5x gain setting<br>00 = 1x gain setting<br>Note that the default for POSCGAIN (2x gain setting) may over-<br>drive crystals and shorten their life. It is the responsibility of the<br>designer to ensure crystals are operated properly. |  |  |  |

| Secondary Oscilla                                                                                                                                                             | ator Crystal Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |