Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 512K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

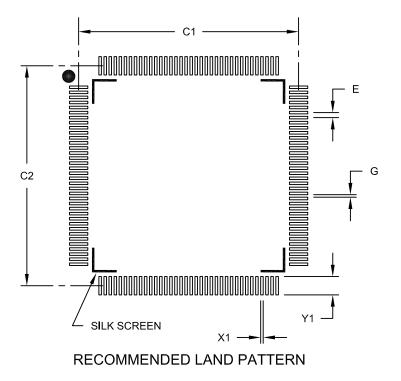

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efm100t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.1.1 BOOT FLASH SEQUENCE AND CONFIGURATION SPACES

Sequence space is used to identify which boot Flash is aliased by aliased regions. If the value programmed into the TSEQ<15:0> bits of the BF1SEQ3 word is equal to or greater than the value programmed into the TSEQ<15:0> bits of the BF2SEQ3 word, boot Flash 1 is aliased by the lower boot alias region, and boot Flash 2 is aliased by the upper boot alias region. If the TSEQ<15:0> bits of the BF2SEQ3 word is greater than the TSEQ<15:0> bits of the BF1SEQ3 word, the opposite is true (see Table 4-2 and Table 4-3 for BFxSEQ3 word memory locations).

The CSEQ<15:0> bits must contain the one's complement value of the TSEQ<15:0> bits; otherwise, the value of the TSEQ<15:0> bits is considered invalid, and an alternate sequence is used. See Section 4.1.2 "Alternate Sequence and Configuration Words" for more information.

Once boot Flash memories are aliased, configuration space located in the lower boot alias region is used as the basis for the Configuration words, DEVSIGNO, DEVCPO, and DEVCFGx (and the associated alternate configuration registers). This means that the boot Flash region to be aliased by lower boot alias region memory must contain configuration values in the appropriate memory locations.

| Note: | Do not use word program operation |  |  |  |  |  |  |

|-------|-----------------------------------|--|--|--|--|--|--|

|       | (NVMOP<3:0> = 0001) when program- |  |  |  |  |  |  |

|       | ming data into the sequence and   |  |  |  |  |  |  |

|       | configuration spaces.             |  |  |  |  |  |  |

# 4.1.2 ALTERNATE SEQUENCE AND CONFIGURATION WORDS

Every word in the configuration space and sequence space has an associated alternate word (designated by the letter A as the first letter in the name of the word). During device start-up, primary words are read and if uncorrectable ECC errors are found, the BCFGERR (RCON<27>) flag is set and alternate words are used. If uncorrectable ECC errors are found in primary and alternate words, the BCFGFAIL (RCON<26>) flag is set and the default configuration is used.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|-------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0                  | U-0                  | U-0                  | U-0                  | U-0                  |  |

| 31:24        | —                 | —                 | _                 | —                    | —                    | —                    | _                    | —                    |  |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0                  | U-0                  | U-0                  | U-0                  |  |

| 23:16        | —                 | —                 | _                 | —                    | _                    |                      | _                    | _                    |  |

| 45.0         | R/W-1             | U-0               | U-0               | R/W-1                | R/W-1                | R/W-1                | R/W-1                | R/W-1                |  |

| 15:8         | LBWPULOCK         | —                 | _                 | LBWP4 <sup>(1)</sup> | LBWP3 <sup>(1)</sup> | LBWP2 <sup>(1)</sup> | LBWP1 <sup>(1)</sup> | LBWP0 <sup>(1)</sup> |  |

| 7.0          | R/W-1             | r-1               | U-0               | R/W-1                | R/W-1                | R/W-1                | R/W-1                | R/W-1                |  |

| 7:0          | UBWPULOCK         | _                 |                   | UBWP4 <sup>(1)</sup> | UBWP3 <sup>(1)</sup> | UBWP2 <sup>(1)</sup> | UBWP1 <sup>(1)</sup> | UBWP0 <sup>(1)</sup> |  |

# REGISTER 5-8: NVMBWP: FLASH BOOT (PAGE) WRITE-PROTECT REGISTER

| Legend:           |                  | r = Reserved                       |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

| bit 15  |     | LBWPULOCK: Lower Boot Alias Write-protect Unlock bit                                                                                                                                                            |

|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |     | 1 = LBWPx bits are not locked and can be modified                                                                                                                                                               |

|         |     | 0 = LBWPx bits are locked and cannot be modified                                                                                                                                                                |

|         |     | This bit is only clearable and cannot be set except by any reset.                                                                                                                                               |

| bit 14- | -13 | Unimplemented: Read as '0'                                                                                                                                                                                      |

| bit 12  |     | LBWP4: Lower Boot Alias Page 4 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC10000 through 0x1FC13FFF enabled</li> <li>0 = Write protection for physical address 0x01FC10000 through 0x1FC13FFF disabled</li> </ul>                 |

| bit 11  |     | LBWP3: Lower Boot Alias Page 3 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC0C000 through 0x1FC0FFFF enabled</li> <li>0 = Write protection for physical address 0x01FC0C000 through 0x1FC0FFFF disabled</li> </ul>                 |

| bit 10  |     | LBWP2: Lower Boot Alias Page 2 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC08000 through 0x1FC0BFFF enabled</li> <li>0 = Write protection for physical address 0x01FC08000 through 0x1FC0BFFF disabled</li> </ul>                 |

| bit 9   |     | LBWP1: Lower Boot Alias Page 1 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC04000 through 0x1FC07FFF enabled</li> <li>0 = Write protection for physical address 0x01FC04000 through 0x1FC07FFF disabled</li> </ul>                 |

| bit 8   |     | LBWP0: Lower Boot Alias Page 0 Write-protect bit <sup>(1)</sup>                                                                                                                                                 |

|         |     | <ul> <li>1 = Write protection for physical address 0x01FC00000 through 0x1FC03FFF enabled</li> <li>0 = Write protection for physical address 0x01FC00000 through 0x1FC03FFF disabled</li> </ul>                 |

| bit 7   |     | UBWPULOCK: Upper Boot Alias Write-protect Unlock bit                                                                                                                                                            |

|         |     | <ul> <li>1 = UBWPx bits are not locked and can be modified</li> <li>0 = UBWPx bits are locked and cannot be modified</li> <li>This bit is only user-clearable and cannot be set except by any reset.</li> </ul> |

| bit 6   |     | Reserved: This bit is reserved for use by development tools                                                                                                                                                     |

| bit 5   |     | Unimplemented: Read as '0'                                                                                                                                                                                      |

|         |     |                                                                                                                                                                                                                 |

| Note    | 1:  | These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (LBWPULOCK or UBWPULOCK) is set.                                                                         |

Note: The bits in this register are only writable when the NVMKEY unlock sequence is followed.

# REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7) (CONTINUED)

#### bit 15-11 MULT<4:0>: Multiplier Control bits

For Isochronous/Interrupt endpoints or of packet splitting on Bulk endpoints, multiplies TXMAXP by MULT+1 for the payload size.

For Bulk endpoints, MULT can be up to 32 and defines the number of "USB" packets of the specified payload into which a single data packet placed in the FIFO should be split, prior to transfer. The data packet is required to be an exact multiple of the payload specified by TXMAXP.

For Isochronous/Interrupts endpoints operating in Hi-Speed mode, MULT may be either 2 or 3 and specifies the maximum number of such transactions that can take place in a single microframe.

### bit 10-0 TXMAXP<10:0>: Maximum TX Payload per transaction Control bits

This field sets the maximum payload (in bytes) transmitted in a single transaction. The value is subject to the constraints placed by the USB Specification on packet sizes for Bulk, Interrupt and Isochronous transfers in Full-Speed and Hi-Speed operations.

TXMAXP must be set to an even number of bytes for proper interrupt generation in DMA Mode 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | DMAADD            | R<31:24>          |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DMAADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| = 0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 7:0          |                   | DMAADDR<7:0>      |                   |                   |                   |                   |                  |                  |  |  |  |

### **REGISTER 11-22: USBDMAXA: USB DMA CHANNEL 'x' MEMORY ADDRESS REGISTER ('x' = 1-8)**

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# bit 31-0 DMAADDR<31:0>: DMA Memory Address bits

This register identifies the current memory address of the corresponding DMA channel. The initial memory address written to this register during initialization must have a value such that its modulo 4 value is equal to '0'. The lower two bits of this register are read only and cannot be set by software. As the DMA transfer progresses, the memory address will increment as bytes are transferred.

| REGISTE | ER 11-23: U | USBDMAxN   | : USB DMA  | CHANNEL    | 'x' COUNT  | REGISTER   | ('X' = 1-8) |              |

|---------|-------------|------------|------------|------------|------------|------------|-------------|--------------|

| Bit     | Bit         | Bit        | Bit        | Bit        | Bit        | Bit        | Bit         | Bit          |

| Danaa   | 24/22/4E/7  | 20/22/44/6 | 20/24/42/5 | 20/20/42/4 | 27/40/44/2 | 26/40/40/2 | 25/47/0/4   | 2 A / A C /0 |

| Range | 31/23/15/7      | 30/22/14/6      | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |  |  |  |

|-------|-----------------|-----------------|------------|------------|------------|------------|-----------|-----------|--|--|--|

| 24.24 | R/W-0           | R/W-0           | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0     | R/W-0     |  |  |  |

| 31:24 |                 | DMACOUNT<31:24> |            |            |            |            |           |           |  |  |  |

| 23:16 | R/W-0           | R/W-0           | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0     | R/W-0     |  |  |  |

| 23.10 | DMACOUNT<23:16> |                 |            |            |            |            |           |           |  |  |  |

| 15:8  | R/W-0           | R/W-0           | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0     | R/W-0     |  |  |  |

| 10.0  | DMACOUNT<15:8>  |                 |            |            |            |            |           |           |  |  |  |

| 7:0   | R/W-0           | R/W-0           | R/W-0      | R/W-0      | R/W-0      | R/W-0      | R/W-0     | R/W-0     |  |  |  |

| 7.0   |                 |                 |            | DMACOL     | JNT<7:0>   |            |           |           |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

## bit 31-0 DMACOUNT<31:0>: DMA Transfer Count bits

This register identifies the current DMA count of the transfer. Software will set the initial count of the transfer which identifies the entire transfer length. As the count progresses this count is decremented as bytes are transferred.

# REGISTER 11-29: USBLPMR2: USB LINK POWER MANAGEMENT CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | _                 |                   | _                 |                   | _                 | —                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | _                 |                   | _                 |                   | _                 | —                | _                |  |  |

| 45.0         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 |                   | LPMFADDR<6:0>     |                   |                   |                   |                  |                  |  |  |

| 7:0          | U-0               | U-0               | R-0               | R-0, HS           | R-0, HS           | R-0, HS           | R-0, HS          | R-0, HS          |  |  |

| 7:0          | _                 |                   | LPMERRIF          | LPMRESIF          | LPMNCIF           | LPMACKIF          | LPMNYIF          | LPMSTIF          |  |  |

| Legend:           | HS = Hardware Set |                                    |                    |  |

|-------------------|-------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-15 Unimplemented: Read as '0'

bit 14-8 LPMFADDR<6:0>: LPM Payload Function Address bits These bits contain the address of the LPM payload function.

bit 7-6 Unimplemented: Read as '0'

### bit 5 LPMERRIF: LPM Error Interrupt Flag bit (Device mode)

1 = An LPM transaction was received that had a LINKSTATE field that is not supported. The response will be a STALL.

0 =No error condition

### bit 4 LPMRESIF: LPM Resume Interrupt Flag bit

- 1 = The USB module has resumed (for any reason)

- 0 = No Resume condition

- bit 3 LPMNCIF: LPM NC Interrupt Flag bit

### When in Device mode:

- 1 = The USB module received a LPM transaction and responded with a NYET due to data pending in the RX FIFOs.

- 0 = No NC interrupt condition

When in Host mode:

- 1 = A LPM transaction is transmitted and the device responded with an ACK

- 0 = No NC interrupt condition

### bit 2 LPMACKIF: LPM ACK Interrupt Flag bit

When in Device mode:

- 1 = A LPM transaction was received and the USB Module responded with an ACK

- 0 = No ACK interrupt condition

### When in Host mode:

1 = The LPM transaction is transmitted and the device responds with an ACK

0 = No ACK interrupt condition

### bit 1 LPMNYIF: LPM NYET Interrupt Flag bit

### When in Device mode:

1 = A LPM transaction is received and the USB Module responded with a NYET

0 = No NYET interrupt flag

When in Host mode:

- 1 = A LPM transaction is transmitted and the device responded with an NYET

- 0 = No NYET interrupt flag

# TABLE 12-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| ss                          |                       |           |            |             |       |       |       |       |      | В             | its  |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|------------|-------------|-------|-------|-------|-------|------|---------------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15      | 30/14       | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8          | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | —     | _      | _    | 0000       |

| 1538                        | RPA14R <sup>(1)</sup> | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPA14 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    | _    | —     | —      | _    | 0000       |

| 153C                        | RPA15R <sup>(1)</sup> | 15:0      | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    |      | RPA15 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    | _    | —     | —      | _    | 0000       |

| 1540                        | RPB0R                 | 15:0      | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    |      | RPB0  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| 1544                        | RPB1R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPB1  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    | _    | —     | —      | _    | 0000       |

| 1548                        | RPB2R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB2  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| 154C                        | RPB3R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB3  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| 1554                        | RPB5R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB5  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          |             | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | _     | _      | _    | 0000       |

| 1558                        | RPB6R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    |      | _    |      | RPB6  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 155C                        | RPB7R                 | 15:0      | _          | _           | _     | _     | _     |       | _    | _             | _    | _    | _    | _    |      | RPB7  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1560                        | RPB8R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB8  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1564                        | RPB9R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB9  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1568                        | RPB10R                | 15:0      | _          | _           | _     | _     | _     |       | _    | _             | _    | _    | _    | _    |      | RPB10 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | _     | _      | _    | 0000       |

| 1578                        | RPB14R                | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPB14 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 157C                        | RPB15R                | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPB15 | R<3:0> |      | 0000       |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    |      | _    | _    | _     | _      | _    | 0000       |

| 1584                        | RPC1R <sup>(1)</sup>  | 15:0      | _          |             | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPC1  | R<3:0> |      | 0000       |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1588                        | RPC2R <sup>(1)</sup>  | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPC2  | R<3:0> |      | 0000       |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 158C                        | RPC3R <sup>(1)</sup>  | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPC3  | R<3:0> |      | 0000       |

|                             | (0)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1590                        | RPC4R <sup>(1)</sup>  | 15:0      | _          |             | _     | _     | _     |       | _    |               | _    |      | _    | _    |      | RPC4  | R<3:0> |      | 0000       |

| Legen                       | l                     |           | alua an Da | eset: — = u |       |       |       |       |      | h ava da aira |      |      |      |      | l    |       |        |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note** 1: This register is not available on 64-pin devices.

2: This register is not available on 64-pin and 100-pin devices.

# 19.1 SPI Control Registers

# TABLE 19-1: SPI1 THROUGH SPI6 REGISTER MAP

| ess                         |                                 | ō             |               |         |        |              |              |              |          | Bi     | ts      |          |        |          |             |          |        |         |            |

|-----------------------------|---------------------------------|---------------|---------------|---------|--------|--------------|--------------|--------------|----------|--------|---------|----------|--------|----------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9     | 24/8   | 23/7    | 22/6     | 21/5   | 20/4     | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 1000                        | SPI1CON                         | 31:16         | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FI           | RMCNT<2: | )>     | MCLKSEL | —        | —      | —        | —           | -        | SPIFE  | ENHBUF  | 0000       |

| 1000                        | SFILCON                         | 15:0          | ON            | -       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP      | CKE    | SSEN    | CKP      | MSTEN  | DISSDI   | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 1010                        | SPI1STAT                        | 31:16         | —             | —       | —      |              |              | BUFELM<4:    | 0>       |        | —       | —        | —      |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| 1010                        |                                 | 15:0          | _             | —       | —      | FRMERR       | SPIBUSY      | —            | —        | SPITUR | SRMT    | SPIROV   | SPIRBE | —        | SPITBE      | —        | SPITBF | SPIRBF  | 0008       |

| 1020                        | SPI1BUF                         | 31:16<br>15:0 |               |         |        |              |              |              |          | DATA<  | :31:0>  |          |        |          |             |          |        |         | 0000       |

| 1030                        | SPI1BRG                         | 31:16         | _             | -       | —      | -            | -            |              | _        | _      | _       |          | _      | -        | _           |          |        |         | 0000       |

| 1030                        | SFIIDKG                         | 15:0          | —             | —       | —      |              |              |              |          |        | В       | RG<12:0> |        |          | -           |          |        |         | 0000       |

|                             |                                 | 31:16         | —             | —       | —      | —            | —            | —            | —        | —      | —       | —        | —      | —        | —           | —        | —      | —       | 0000       |

| 1040                        | SPI1CON2                        | 15:0          | SPI<br>SGNEXT | _       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV   | IGNTUR | AUDEN   | _        | _      | _        | AUD<br>MONO | _        | AUDMO  | )D<1:0> | 0000       |

| 1200                        | SPI2CON                         | 31:16         | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FI           | RMCNT<2: | )>     | MCLKSEL | _        | _      | _        | —           | _        | SPIFE  | ENHBUF  | 0000       |

| 1200                        | 01 120011                       | 15:0          | ON            | —       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP      | CKE    | SSEN    | CKP      | MSTEN  | DISSDI   | STXISE      |          | SRXISE | EL<1:0> | 0000       |

| 1210                        | SPI2STAT                        | 31:16         | _             |         | —      |              |              | BUFELM<4:    | 0>       |        | —       | _        | —      |          |             | BUFELM<4 |        |         | 0000       |

|                             |                                 | 15:0          |               | —       | —      | FRMERR       | SPIBUSY      | _            | —        | SPITUR | SRMT    | SPIROV   | SPIRBE | —        | SPITBE      | —        | SPITBF | SPIRBF  | 0008       |

| 1220                        | SPI2BUF                         | 31:16<br>15:0 |               |         |        |              |              |              |          | DATA<  | 31:0>   |          |        |          |             |          |        |         | 0000       |

| 1230                        | SPI2BRG                         | 31:16         | —             | —       | —      | -            | —            | _            | —        | —      | —       | —        | —      | —        | —           | —        | —      | —       | 0000       |

| 1200                        |                                 | 15:0          | —             | —       | —      | —            | —            | —            | —        |        |         |          |        | BRG<8:0> |             |          |        |         | 0000       |

| 10.40                       |                                 | 31:16         | -             | _       | _      | -            | -            | -            | _        | _      | _       | _        | _      | _        | -           | _        | _      | _       | 0000       |

| 1240                        | SPI2CON2                        | 15:0          | SPI<br>SGNEXT | —       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV   | IGNTUR | AUDEN   | _        | _      | _        | AUD<br>MONO | _        | AUDMO  |         | 0000       |

| 1400                        | SPI3CON                         | 31:16         | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      |              | RMCNT<2: |        | MCLKSEL | —        |        |          | —           | —        | SPIFE  | ENHBUF  |            |

|                             |                                 | 15:0          | ON            | —       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP      | CKE    | SSEN    | CKP      | MSTEN  | DISSDI   | STXISE      |          | SRXISE | EL<1:0> | 0000       |

| 1410                        | <b>SPI3STAT</b>                 | 31:16         |               |         | _      | FRMERR       |              | BUFELM<4:    | 0>       |        | -       |          | -      |          |             | BUFELM<4 |        |         | 0000       |

|                             |                                 | 15:0          |               | —       | —      | FRMERR       | SPIBUSY      | _            | —        | SPITUR | SRMT    | SPIROV   | SPIRBE | —        | SPITBE      | _        | SPITBF | SPIRBF  | 0008       |

| 1420                        | SPI3BUF                         | 31:16<br>15:0 |               |         |        |              | -            |              |          | DATA<  | 31:0>   |          |        |          |             |          | -      |         | 0000       |

| 1430                        | SPI3BRG                         | 31:16         | _             | _       | —      | _            | —            | _            | _        | —      | —       | —        | —      | —        | —           | —        | —      | —       | 0000       |

| 1430                        |                                 | 15:0          | _             | _       | —      | _            | —            | _            | —        |        |         |          |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16         | —             | —       | —      | —            | —            | —            | —        | —      | —       |          | —      | —        | —           |          | —      | —       | 0000       |

| 1440                        | SPI3CON2                        | 15:0          | SPI<br>SGNEXT | —       | -      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV   | IGNTUR | AUDEN   | —        | —      | —        | AUD<br>MONO | —        | AUDMO  | )D<1:0> | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

Legend:

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | —                    | —                 | -                 | —                 | —                        | —                 | _                | —                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | —                    | —                 | -                 | —                 | —                        | —                 | _                | —                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 0.61         | SPISGNEXT            | —                 | -                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

| 7:0          | AUDEN <sup>(1)</sup> | —                 | _                 | —                 | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | <1:0> <sup>(1,2)</sup> |

# REGISTER 19-2: SPIxCON2: SPI CONTROL REGISTER 2

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | SPISGNEXT: Sign Extend Read Data from the RX FIFO bit                                                                                        |

|           | 1 = Data from RX FIFO is sign extended                                                                                                       |

|           | 0 = Data from RX FIFO is not sign extended                                                                                                   |

| bit 14-13 | Unimplemented: Read as '0'                                                                                                                   |

| bit 12    | FRMERREN: Enable Interrupt Events via FRMERR bit                                                                                             |

|           | 1 = Frame Error overflow generates error events                                                                                              |

|           | 0 = Frame Error does not generate error events                                                                                               |

| bit 11    | SPIROVEN: Enable Interrupt Events via SPIROV bit                                                                                             |

|           | 1 = Receive overflow generates error events                                                                                                  |

|           | 0 = Receive overflow does not generate error events                                                                                          |

| bit 10    | SPITUREN: Enable Interrupt Events via SPITUR bit                                                                                             |

|           | 1 = Transmit Underrun Generates Error Events                                                                                                 |

|           | 0 = Transmit Underrun Does Not Generates Error Events                                                                                        |

| bit 9     | IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)                                                                           |

|           | 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data                                            |

|           | 0 = A ROV is a critical error which stop SPI operation                                                                                       |

| bit 8     | IGNTUR: Ignore Transmit Underrun bit (for Audio Data Transmissions)                                                                          |

|           | 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty                                                   |

| 1.1.7     | 0 = A TUR is a critical error which stop SPI operation                                                                                       |

| bit 7     | AUDEN: Enable Audio CODEC Support bit <sup>(1)</sup>                                                                                         |

|           | 1 = Audio protocol is enabled<br>0 = Audio protocol is disabled                                                                              |

| bit 6-5   | ·                                                                                                                                            |

|           | Unimplemented: Read as '0'                                                                                                                   |

| bit 3     | AUDMONO: Transmit Audio Data Format bit <sup>(1,2)</sup>                                                                                     |

|           | <ul> <li>1 = Audio data is mono (Each data word is transmitted on both left and right channels)</li> <li>0 = Audio data is stereo</li> </ul> |

| bit 2     | Unimplemented: Read as '0'                                                                                                                   |

| bit 1-0   | AUDMOD<1:0>: Audio Protocol Mode bit <sup>(1,2)</sup>                                                                                        |

| DIT I U   | 11 = PCM/DSP mode                                                                                                                            |

|           | 10 = Right Justified mode                                                                                                                    |

|           | 01 = Left Justified mode                                                                                                                     |

|           | $00 = I^2 S \text{ mode}$                                                                                                                    |

|           |                                                                                                                                              |

|           |                                                                                                                                              |

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                    | -                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0                  | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | —                 | —                 | —                 | _                 | —                    | CL                | KDIV<10:8>       | (1)              |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CLKDIV<           | :7:0> <sup>(1)</sup> |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | R-0              | R/W-0            |

| 7:0          | _                 | —                 | _                 | _                 | —                    | _                 | STABLE           | EN               |

### REGISTER 20-5: SQI1CLKCON: SQI CLOCK CONTROL REGISTER

# Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-19 Unimplemented: Read as '0'

bit 18-8 CLKDIV<10:0>: SQI Clock TsQI Frequency Select bit<sup>(1)</sup>

|               |      |       |     |    | •       |    |      |

|---------------|------|-------|-----|----|---------|----|------|

| 1000000000 =  | Base | clock | Твс | is | divided | by | 2048 |

| 0100000000 =  | Base | clock | Твс | is | divided | by | 1024 |

| 0010000000 =  | Base | clock | Твс | is | divided | by | 512  |

| 00010000000 = | Base | clock | Твс | is | divided | by | 256  |

| 00001000000 = | Base | clock | Твс | is | divided | by | 128  |

| 00000100000 = |      |       |     |    |         |    |      |

| 00000010000 = | Base | clock | Твс | is | divided | by | 32   |

| 0000001000 =  | Base | clock | Твс | is | divided | by | 16   |

| 0000000100 =  | Base | clock | Твс | is | divided | by | 8    |

| 0000000010 =  | Base | clock | Твс | is | divided | by | 4    |

| 0000000001 =  | Base | clock | Твс | is | divided | by | 2    |

| 00000000000 = | Base | clock | Твс |    |         |    |      |

|               |      |       |     |    |         |    |      |

Setting these bits to '0000000000' specifies the highest frequency of the SQI clock.

### bit 7-2 Unimplemented: Read as '0'

bit 1 STABLE: TSQI Clock Stable Select bit

This bit is set to '1' when the SQI clock, TsQI, is stable after writing a '1' to the EN bit.

- 1 = Tsqi clock is stable

- 0 = Tsql clock is not stable

### bit 0 EN: TSQI Clock Enable Select bit

When clock oscillation is stable, the SQI module will set the STABLE bit to '1'.

- 1 = Enable the SQI clock (TSQI) (when clock oscillation is stable, the SQI module sets the STABLE bit to '1')

- 0 = Disable the SQI clock (TsQI) (the SQI module should stop its clock to enter a low power state); SFRs can still be accessed, as they use PBCLK5

- **Note 1:** Refer to Table 37-34 in **37.0** "Electrical Characteristics" for the maximum clock frequency specifications.

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6    | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0     |

|-----------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| 04.04     | R/W-0                |

| 31:24     | CSS31 <sup>(1)</sup> | CSS30 <sup>(1)</sup> | CSS29 <sup>(1)</sup> | CSS28 <sup>(1)</sup> | CSS27 <sup>(1)</sup> | CSS26 <sup>(1)</sup> | CSS25 <sup>(1)</sup> | CSS24 <sup>(1)</sup> |

| 00.40     | R/W-0                |

| 23:16     | CSS23 <sup>(1)</sup> | CSS22 <sup>(1)</sup> | CSS21 <sup>(1)</sup> | CSS20 <sup>(1)</sup> | CSS19 <sup>(1)</sup> | CSS18                | CSS17                | CSS16                |

| 45.0      | R/W-0                |

| 15:8      | CSS15                | CSS14                | CSS13                | CSS12                | CSS11                | CSS10                | CSS9                 | CSS8                 |

| 7.0       | R/W-0                |

| 7:0       | CSS7                 | CSS6                 | CSS5                 | CSS4                 | CSS3                 | CSS2                 | CSS1                 | CSS0                 |

## REGISTER 28-10: ADCCSS1: ADC COMMON SCAN SELECT REGISTER 1

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CSS31:CSS0: Analog Common Scan Select bits<sup>(2,3)</sup>

1 =Select ANx for input scan

0 =Skip ANx for input scan

**Note 1:** This bit is not available on 64-pin devices.

2: In addition to setting the appropriate bits in this register, Class 1 and Class 2 analog inputs must select the STRIG input as the trigger source if they are to be scanned through the CSS*x* bits. Refer to the bit descriptions in the ADCTRGx registers for selecting the STRIG option.

3: If a Class 1 or Class 2 input is included in the scan by setting the CSSx bit to '1' and by setting the TRGSRCx<4:0> bits to STRIG mode (`0b11), the user application must ensure that no other triggers are generated for that input using the RQCNVRT bit in the ADCCON3 register or the hardware input or any digital filter. Otherwise, the scan behavior is unpredictable.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 01.04        | U-0                    |

| 31:24        | —                      | —                      | —                      | —                      | —                      | —                      | —                      | —                      |

| 22.10        | U-0                    |

| 23:16        |                        | —                      |                        |                        |                        |                        | -                      | —                      |

| 45.0         | U-0                    | U-0                    | U-0                    | R-0, HS, HC            |

| 15:8         | —                      | —                      | _                      | EIRDY44 <sup>(2)</sup> | EIRDY43 <sup>(2)</sup> | EIRDY42 <sup>(2)</sup> | EIRDY41 <sup>(2)</sup> | EIRDY40 <sup>(2)</sup> |

| 7.0          | R-0, HS, HC            |

| 7:0          | EIRDY39 <sup>(2)</sup> | EIRDY38 <sup>(2)</sup> | EIRDY37 <sup>(2)</sup> | EIRDY36 <sup>(2)</sup> | EIRDY35 <sup>(2)</sup> | EIRDY34 <sup>(1)</sup> | EIRDY33 <sup>(1)</sup> | EIRDY32 <sup>(1)</sup> |

# REGISTER 28-31: ADCEISTAT2: ADC EARLY INTERRUPT STATUS REGISTER 2

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                    |

|-------------------|-------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set  | 0' = Bit is cleared $x = Bit is unknown$ |

### bit 31-13 Unimplemented: Read as '0'

bit 31-0 **EIRDY44:EIRDY32:** Early Interrupt for Corresponding Analog Input Ready bits

- 1 = This bit is set when the early interrupt event occurs for the specified analog input. An interrupt will be generated if early interrupts are enabled in the ADCEIEN2 register. For the Class 1 analog inputs, this bit will set as per the configuration of the ADCEIS<2:0> bits in the ADCXTIME register. For the shared ADC module, this bit will be set as per the configuration of the ADCEIS<2:0> bits in the ADCEIS<2:0> bits in the ADCCON2 register.

- 0 = Interrupts are disabled

**Note 1:** This bit is not available on 64-pin devices.

2: This bit is not available on 64-pin and 100-pin devices.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | —                 | _                 | —                 | —                 | —                 | —                | —                |

| 00.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | _                 | —                 | —                 | —                 | —                | —                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0      | —                 | —                 | _                 | —                 | —                 | R                 | XBUFSZ<6:        | 4>               |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 7:0       |                   | RXBUF             | SZ<3:0>           |                   | —                 | _                 | —                | —                |

# REGISTER 30-2: ETHCON2: ETHERNET CONTROLLER CONTROL REGISTER 2

# Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

# bit 31-11 Unimplemented: Read as '0'

| bit 10-4 | RXBUFSZ<6:0>: RX Data Buffer Size for All RX Descriptors (in 16-byte increments) bits<br>1111111 = RX data Buffer size for descriptors is 2032 bytes                                                      |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | •                                                                                                                                                                                                         |

|          | •                                                                                                                                                                                                         |

|          | 1100000 = RX data Buffer size for descriptors is 1536 bytes                                                                                                                                               |

|          | •                                                                                                                                                                                                         |

|          | •                                                                                                                                                                                                         |

|          | •                                                                                                                                                                                                         |

|          | 0000011 = RX data Buffer size for descriptors is 48 bytes<br>0000010 = RX data Buffer size for descriptors is 32 bytes<br>0000001 = RX data Buffer size for descriptors is 16 bytes<br>0000000 = Reserved |

| bit 3-0  | Unimplemented: Read as '0'                                                                                                                                                                                |

| Note 1:  | This register is only used for RX operations.                                                                                                                                                             |

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

NOTES:

NOTES:

# REGISTER 34-9: CFGEBIC: EXTERNAL BUS INTERFACE CONTROL PIN CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 31:24        | EBI<br>RDYINV3    | EBI<br>RDYINV2    | EBI<br>RDYIN1     | _                 | EBI<br>RDYEN3     | EBI<br>RDYEN2     | EBI<br>RDYEN1    | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | EBIRDYLVL        | EBIRPEN          |

| 45-0         | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | -                 | -                 | EBIWEEN           | EBIOEEN           | —                 |                   | EBIBSEN1         | EBIBSEN0         |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | EBICSEN3          | EBICSEN2          | EBICSEN1          | EBICSEN0          | _                 |                   | EBIDEN1          | EBIDEN0          |

| · <b>J</b> · · ·  |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31 | EBIRDYINV3: EBIRDY3 Inversion Control bit            |

|--------|------------------------------------------------------|

|        | 1 = Invert EBIRDY3 pin before use                    |

|        | 0 = Do not invert EBIRDY3 pin before use             |

| bit 30 | EBIRDYINV2: EBIRDY2 Inversion Control bit            |

|        | 1 = Invert EBIRDY2 pin before use                    |

|        | 0 = Do not invert EBIRDY2 pin before use             |

| bit 29 | EBIRDYINV1: EBIRDY1 Inversion Control bit            |

|        | 1 = Invert EBIRDY1 pin before use                    |

|        | 0 = Do not invert EBIRDY1 pin before use             |

| bit 28 | Unimplemented: Read as '0'                           |

| bit 27 | EBIRDYEN3: EBIRDY3 Pin Enable bit                    |

|        | 1 = EBIRDY3 pin is enabled for use by the EBI module |

|        | 0 = EBIRDY3 pin is available for general use         |

| bit 26 | EBIRDYEN2: EBIRDY2 Pin Enable bit                    |

|        | 1 = EBIRDY2 pin is enabled for use by the EBI module |

|        | 0 = EBIRDY2 pin is available for general use         |

| bit 25 | EBIRDYEN1: EBIRDY1 Pin Enable bit                    |

|        | 1 = EBIRDY1 pin is enabled for use by the EBI module |

|        | 0 = EBIRDY1 pin is available for general use         |

|        | Unimplemented: Read as '0'                           |

| bit 17 | EBIRDYLVL: EBIRDYx Pin Sensitivity Control bit       |

|        | 1 = Use level detect for EBIRDYx pins                |

|        | 0 = Use edge detect for EBIRDYx pins                 |

| bit 16 | EBIRPEN: EBIRP Pin Sensitivity Control bit           |

|        | 1 = EBIRP pin is enabled for use by the EBI module   |

|        | 0 = EBIRP pin is available for general use           |

|        | Unimplemented: Read as '0'                           |

| bit 13 | EBIWEEN: EBIWE Pin Enable bit                        |

|        | 1 = EBIWE pin is enabled for use by the EBI module   |

|        | 0 = EBIWE pin is available for general use           |

|        |                                                      |

**Note:** When EBIMD = 1, the bits in this register are ignored and the pins are available for general use.

| REGISTI   | ER 34-9: CFGEBIC: EXTERNAL BUS INTERFACE CONTROL PIN CONFIGURATION<br>REGISTER (CONTINUED)                                                          |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 12    | EBIOEEN: EBIOE Pin Enable bit                                                                                                                       |  |

|           | $1 = \overline{\text{EBIOE}}$ pin is enabled for use by the EBI module                                                                              |  |

|           | 0 = EBIOE pin is available for general use                                                                                                          |  |

| bit 11-10 | Unimplemented: Read as '0'                                                                                                                          |  |

| bit 9     | EBIBSEN1: EBIBS1 Pin Enable bit                                                                                                                     |  |

|           | 1 = EBIBS1 pin is enabled for use by the EBI module<br>0 = EBIBS1 pin is available for general use                                                  |  |

| bit 8     | EBIBSEN1: EBIBSO Pin Enable bit                                                                                                                     |  |

| bit 0     | $1 = \overline{\text{EBIBS0}}$ pin is enabled for use by the EBI module                                                                             |  |

|           | 0 = EBIBS0 pin is available for general use                                                                                                         |  |

| bit 7     | EBICSEN3: EBICS3 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{EBICS3}$ pin is enabled for use by the EBI module                                                                                    |  |

|           | 0 = EBICS3 pin is available for general use                                                                                                         |  |

| bit 6     | EBICSEN2: EBICS2 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{\text{EBICS2}}$ pin is enabled for use by the EBI module                                                                             |  |

|           | 0 = EBICS2 pin is available for general use                                                                                                         |  |

| bit 5     | EBICSEN1: EBICS1 Pin Enable bit                                                                                                                     |  |

|           | 1 = EBICS1 pin is enabled for use by the EBI module                                                                                                 |  |

|           | 0 = EBICS1 pin is available for general use                                                                                                         |  |

| bit 4     | EBICSEN0: EBICS0 Pin Enable bit                                                                                                                     |  |

|           | $1 = \overline{\text{EBICS0}}$ pin is enabled for use by the EBI module                                                                             |  |

| 1         | 0 = EBICS0 pin is available for general use                                                                                                         |  |

| bit 3-2   | Unimplemented: Read as '0'                                                                                                                          |  |

| bit 1     | EBIDEN1: EBI Data Upper Byte Pin Enable bit                                                                                                         |  |

|           | <ul> <li>1 = EBID&lt;15:8&gt; pins are enabled for use by the EBI module</li> <li>0 = EBID&lt;15:8&gt; pins have reverted to general use</li> </ul> |  |

| bit 0     | <b>EBIDEN0:</b> EBI Data Lower Byte Pin Enable bit                                                                                                  |  |

| DIL U     | 1 = EBID<7:0> pins are enabled for use by the EBI module                                                                                            |  |

|           | 0 = EBID < 7:0> pins have reverted to general use                                                                                                   |  |

|           | -                                                                                                                                                   |  |

| Note:     | When EBIMD = 1, the bits in this register are ignored and the pins are available for general use.                                                   |  |

# 36.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 36.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>