Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Obsolete                                                                         |

|                           |                                                                                  |

| Core Processor            | MIPS32® M-Class                                                                  |

| Core Size                 | 32-Bit Single-Core                                                               |

| ipeed                     | 180MHz                                                                           |

| Connectivity              | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| eripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| lumber of I/O             | 97                                                                               |

| rogram Memory Size        | 2MB (2M x 8)                                                                     |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AAM Size                  | 512K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Oata Converters           | A/D 48x12b                                                                       |

| Scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 125°C                                                                    |

| lounting Type             | Surface Mount                                                                    |

| ackage / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                 |

| Supplier Device Package   | 124-VTLA (9x9)                                                                   |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2048efm124-e-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

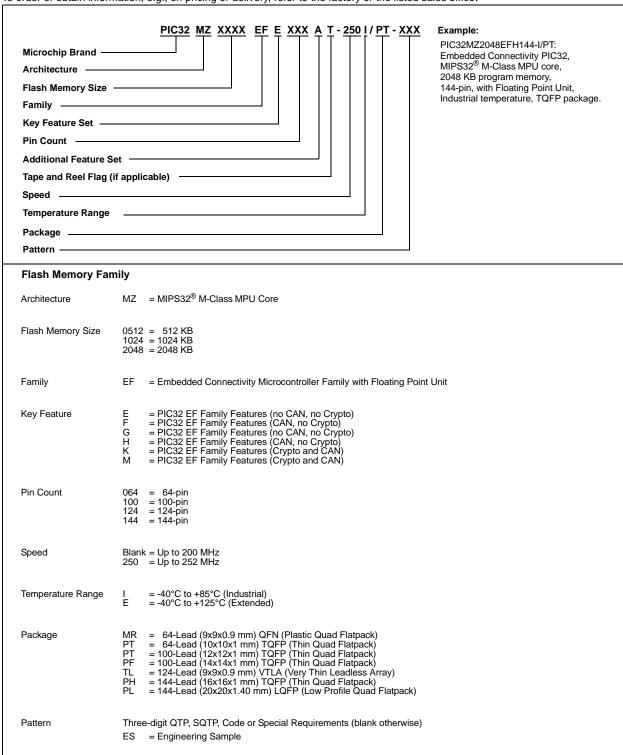

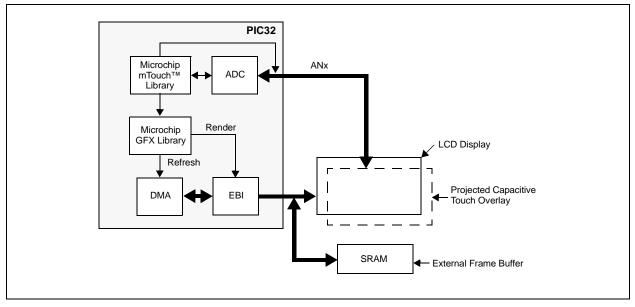

# 2.10 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-6 and Figure 2-7.

FIGURE 2-6: AUDIO PLAYBACK APPLICATION

FIGURE 2-7: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                    |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                      |

| 22,16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                    |

| 23:16        | _                 | _                 | 1                 | _                 | _                 |                   |                  | _                      |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                    |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                      |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC                |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | SWRST <sup>(1,2)</sup> |

Legend: HC = Hardware Cleared

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-1 Unimplemented: Read as '0'

bit 0 **SWRST:** Software Reset Trigger bit<sup>(1,2)</sup>

1 = Enable software Reset event

0 = No effect

Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to **Section**42. "Oscillators with Enhanced PLL" in the "PIC32 Family Reference Manual" for details.

2: Once this bit is set, any read of the RSWRST register will cause a reset to occur.

| <b>TABLE 7-3:</b> | INTERRUPT | REGISTER | MAP | (CONTINUED) |

|-------------------|-----------|----------|-----|-------------|

|                   |           |          |     |             |

| ress<br>f)                  | <b>5</b>                        | ø         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | y,         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

|                             | OFF002                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | -          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0546                        | OFF002                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0540                        | OFF003                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0340                        | 011003                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0550                        | OFF004                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0330                        | 011004                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0554                        | OFF005                          | 31:16     | _     | 1     | _     | _     | _     | _     | -    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0554                        | OFF005                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0558                        | OFF006                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0336                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0550                        | OFF007                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0550                        | 011007                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0560                        | OFF008                          | 31:16     | _     | 1     | _     | _     | _     | _     | -    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0300                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0564                        | OFF009                          | 31:16     | _     | -     | _     | _     | _     | _     | -    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0304                        | 011009                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0568                        | OFF010                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0300                        | 011010                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0560                        | OFF011                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0300                        | 011011                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0570                        | OFF012                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0370                        | 011012                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0574                        | OFF013                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0374                        | 011013                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0578                        | OFF014                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0370                        | 011014                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 057C                        | OFF015                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 3370                        | 011010                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0580                        | OFF016                          | 31:16     | _     | -     | _     | _     | _     | _     | -    | _          |      |      | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0360                        | טו דטוט                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

- Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

This bit or register is not available on 64-pin devices.

- This bit or register is not available on devices without a CAN module.

- 4:

- This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

- 6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

- This bit or register is not available on devices without a Crypto module. This bit or register is not available on 124-pin devices. 7:

| <b>TABLE 7-3</b> : | INTERRUPT REGISTER MAP (CONTINUED | )) |

|--------------------|-----------------------------------|----|

| Ø                  |                                   |    |

| ress<br>()                  |                                 | Φ         |       |       |       |       |       | -     |      | Bit        | ts   |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

|                             | OFF168                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | -          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0720                        | OFF 100                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0754                        | OFF169                          | 31:16     | _     |       | _     | _     | _     |       |      | _          | _    | _    | _    |      | _    |      | VOFF< | 17:16> | 0000       |

| 0714                        | 011109                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 07E8                        | OFF170                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0720                        | 011170                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 07EC                        | OFF171                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| OILO                        | 011171                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 07F0                        | OFF172                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0710                        | 011172                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 07F4                        | OFF173                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 071 4                       | 011173                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 07F8                        | OFF174                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0/10                        | 011174                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 07EC                        | OFF175                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0710                        | 011173                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0800                        | OFF176 <sup>(2)</sup>           | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0000                        | 011170                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0804                        | OFF177 <sup>(2)</sup>           | 31:16     | _     | -     | _     | _     | _     | _     | -    | _          | _    | _    | _    | -    | _    | _    | VOFF< | 17:16> | 0000       |

| 0004                        | OI I III                        | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| กลกล                        | OFF178 <sup>(2)</sup>           | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0000                        | 011170                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0800                        | OFF179                          | 31:16     | _     | _     | _     | _     |       | _     | _    | _          |      |      | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0800                        | OFFITS                          | 15:0      |       |       | •     |       |       |       |      | VOFF<15:1> |      |      | •    |      |      |      | •     | _      | 0000       |

| 0810                        | OFF180                          | 31:16     | _     | 1     | _     | _     | _     | _     | -    | _          | _    | _    | _    | -    | _    | _    | VOFF< | 17:16> | 0000       |

| 0010                        | 011100                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0814                        | OFF181                          | 31:16     | _     | _     | _     |       | _     | _     | _    | _          | _    |      |      |      | _    | _    | VOFF< | 17:16> | 0000       |

| 0014                        | 011101                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0818                        | OFF182                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    |      | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0010                        | OFF102                          | 15:0      |       |       |       |       |       | -     |      | VOFF<15:1> |      |      |      |      |      | -    |       | _      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

Point Unit (EF) Family

- 3: This bit or register is not available on devices without a CAN module.

- This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

- 6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

- 7: This bit or register is not available on devices without a Crypto module.

- This bit or register is not available on 124-pin devices.

#### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL x SOURCE SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 |                   | _                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | -                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHSSIZ-           | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

111111111111111 = 65,535 byte source size

0000000000000001 = 1 byte source size

#### REGISTER 10-13: DCHxDSIZ: DMA CHANNEL x DESTINATION SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSIZ            | ·<7:0>            |                   | •                |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDSIZ<15:0>: Channel Destination Size bits

111111111111111 = 65,535 byte destination size

0000000000000010 = 2 byte destination size

0000000000000001 = 1 byte destination size

# REGISTER 11-6: USBIE0CSR2: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 2 (ENDPOINT 0)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 | -                 | _                 |                   |                   | NAKLIM<4:0>       |                  |                  |

| 23:16        | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | SPEE              | D<1:0>            |                   |                   | _                 | -                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 13.6         | _                 | _                 | _                 | _                 | _                 | -                 |                  | _                |

| 7.0          | U-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   |                   | RXCNT<6:0>        |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-24 NAKLIM<4:0>: Endpoint 0 NAK Limit bits

The number of frames/microframes (Hi-Speed transfers) after which Endpoint 0 should time-out on receiving a stream of NAK responses.

bit 23-22 **SPEED<1:0>:** Operating Speed Control bits

11 = Low-Speed

10 = Full-Speed

01 = Hi-Speed

00 = Reserved

bit 21-7 **Unimplemented:** Read as '0'

bit 6-0 RXCNT<6:0>: Receive Count bits

The number of received data bytes in the Endpoint 0 FIFO. The value returned changes as the contents of the FIFO change and is only valid while RXPKTRDY is set.

## 17.1 Input Capture Control Registers

### TABLE 17-2: INPUT CAPTURE 1 THROUGH INPUT CAPTURE 9 REGISTER MAP

| SS                          |                       |               | Bits       |                   |           |             |            |       |              |        |        |      |      |      |       |      |          |      |            |

|-----------------------------|-----------------------|---------------|------------|-------------------|-----------|-------------|------------|-------|--------------|--------|--------|------|------|------|-------|------|----------|------|------------|

| Virtual Address<br>(BF84_#) | Register<br>Name      | Bit Range     | 31/15      | 30/14             | 29/13     | 28/12       | 27/11      | 26/10 | 25/9         | 24/8   | 23/7   | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1     | 16/0 | All Resets |

|                             | IC1CON <sup>(1)</sup> | 31:16         | _          | _                 | _         | _           | _          | _     | _            | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2000                        | 1010014               | 15:0          | ON         | _                 | SIDL      | _           | _          | -     | FEDGE        | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2010                        | IC1BUF                | 31:16<br>15:0 |            |                   |           |             |            |       |              | IC1BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         | _          | _                 | _         | _           | _          | _     | _            | _      | _      | _    | _    | _    | _     |      | _        | _    | 0000       |

| 2200                        | 1020011               | 15:0          | ON         | _                 | SIDL      | _           |            |       | FEDGE        | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2210                        | IC2BUF                | 31:16<br>15:0 |            | IC2BUF<31:0> 2XXX |           |             |            |       |              |        |        |      |      |      |       |      |          |      |            |

| 2400                        | IC3CON <sup>(1)</sup> | 31:16         | _          | _                 | _         | _           | _          |       | _            | _      | _      | _    | _    | _    | _     |      | _        | _    | 0000       |

| 2400                        | IC3COIN.              | 15:0          | ON         | _                 | SIDL      | _           | _          | -     | FEDGE        | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2410                        | IC3BUF                | 31:16<br>15:0 |            |                   |           |             |            |       |              | IC3BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 2600                        | IC4CON <sup>(1)</sup> | 31:16         | _          | _                 | _         | _           | _          | _     | _            | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2000                        | 1040011               | 15:0          | ON         | _                 | SIDL      | _           | _          | _     | FEDGE        | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2610                        | IC4BUF                | 31:16<br>15:0 |            |                   |           |             |            |       |              | IC4BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 2800                        | IC5CON <sup>(1)</sup> | 31:16         | _          | _                 | _         | _           | _          | -     | _            | _      | _      | _    | _    | _    |       |      | _        | _    | 0000       |

| 2000                        | 1000011               | 15:0          | ON         | _                 | SIDL      | _           | _          | _     | FEDGE        | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2810                        | IC5BUF                | 31:16<br>15:0 |            |                   |           |             |            |       |              | IC5BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 2A00                        | IC6CON <sup>(1)</sup> | 31:16         | _          | _                 | _         | _           | _          | _     | _            | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 27100                       | 1000011               | 15:0          | ON         | _                 | SIDL      | _           | _          | _     | FEDGE        | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2A10                        | IC6BUF                | 31:16<br>15:0 |            |                   |           |             |            |       |              | IC6BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 2000                        | IC7CON <sup>(1)</sup> | 31:16         | _          | _                 | _         | _           | _          | -     | _            | _      | _      | _    | _    | _    | _     | I    | _        | _    | 0000       |

| 2000                        | 1070011               | 15:0          | ON         | _                 | SIDL      | _           | _          | _     | FEDGE        | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2C10                        | IC7BUF                | 31:16<br>15:0 |            |                   |           |             |            |       |              | IC7BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 2F00                        | IC8CON <sup>(1)</sup> | 31:16         | _          | _                 | _         | _           | _          | -     | _            | _      | _      | _    | _    | _    |       |      | _        | _    | 0000       |

| 2200                        | 1000011               | 15:0          | ON         | _                 | SIDL      | _           | _          | _     | FEDGE        | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2E10                        | IC8BUF                | 31:16<br>15:0 |            |                   |           |             |            |       |              | IC8BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 3000                        | IC9CON <sup>(1)</sup> | 31:16         | _          | _                 | _         | _           | _          | _     | _            | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 3000                        | 10900IN.              | 15:0          | ON         | _                 | SIDL      | _           | _          | _     | FEDGE        | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 3010                        | IC9BUF                | 31:16<br>15:0 |            |                   |           |             |            |       |              | IC9BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| Logon                       | ·                     |               | value en l |                   | unimplomo | ntod road o | o 'o' Booo |       | s about in h |        |        |      |      |      |       |      |          |      |            |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

REGISTER 17-1: ICXCON: INPUT CAPTURE x CONTROL REGISTER

| Bit Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | _                    | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40     | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                    | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | R/W-0                | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON                   | _                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0                | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR <sup>(1)</sup> | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

Legend:

bit 7

R = Readable bit W = Writable bit U = Unimplemented bit

-n = Bit Value at POR: ('0', '1', x = unknown) P = Programmable bit r = Reserved bit

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Input Capture Module Enable bit

1 = Module is enabled

0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Control bit

1 = Halt in CPU Idle mode

0 = Continue to operate in CPU Idle mode

bit 12-10 Unimplemented: Read as '0'

bit 9 **FEDGE**: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)

1 = Capture rising edge first0 = Capture falling edge firstC32: 32-bit Capture Select bit

bit 8 **C32:** 32-bit Capture Select bit 1 = 32-bit timer resource capture 0 = 16-bit timer resource capture

ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')(1)

0 = Timery is the counter source for capture 1 = Timerx is the counter source for capture

bit 6-5 ICI<1:0>: Interrupt Control bits

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture overflow is occurred0 = No input capture overflow is occurred

bit 3 ICBNE: Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty; at least one more capture value can be read

0 = Input capture buffer is empty

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

110 = Simple Capture Event mode – every edge, specified edge first and every edge thereafter

101 = Prescaled Capture Event mode – every sixteenth rising edge 100 = Prescaled Capture Event mode – every fourth rising edge

011 = Simple Capture Event mode – every rising edge 010 = Simple Capture Event mode – every falling edge

001 = Edge Detect mode – every edge (rising and falling)

000 = Input Capture module is disabled

**Note 1:** Refer to Table 17-1 for Timerx and Timery selections.

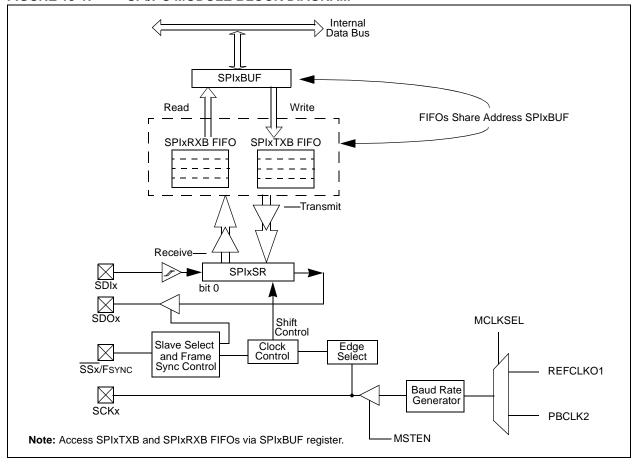

# 19.0 SERIAL PERIPHERAL INTERFACE (SPI) AND INTER-IC SOUND (I<sup>2</sup>S)

Note:

This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 23**. "**Serial Peripheral Interface (SPI)**" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/ PIC32).

The SPI/I<sup>2</sup>S module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices, as well as digital audio devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, and so on.

The SPI/I<sup>2</sup>S module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The following are key features of the SPI module:

- Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- · User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

- FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

FIGURE 19-1: SPI/I<sup>2</sup>S MODULE BLOCK DIAGRAM

#### REGISTER 20-10: SQI1TXDATA: SQI TRANSMIT DATA BUFFER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        |                   |                   |                   | TXDATA<           | :31:24>           |                   |                  |                  |  |  |  |  |  |

| 22.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | TXDATA<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   |                   |                   | TXDATA            | <15:8>            |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | TXDATA            | ·<7:0>            |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 TXDATA<31:0>: Transmit Command Data bits

Data is loaded into this register before being transmitted. Prior to the data transfer, the data in TXDATA is loaded into the shift register (SFDR).

Multiple writes to TXDATA can occur while a transfer is in progress. There can be a maximum of eight commands that can be queued.

#### REGISTER 20-11: SQI1RXDATA: SQI RECEIVE DATA BUFFER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        | RXDATA<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        |                   |                   |                   | RXDATA<           | <23:16>           |                   |                  |                  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | RXDATA<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

|              | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | RXDATA<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 RXDATA<31:0>: Receive Data Buffer bits

At the end of a data transfer, the data in the shift register is loaded into the RXDATA register. This register works like a FIFO. The depth of the receive buffer is eight words.

REGISTER 26-6: CEINTSRC: CRYPTO ENGINE INTERRUPT SOURCE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04:04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 | _                 | _                 | _                 | AREIF             | PKTIF             | CBDIF            | PENDIF           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-4 Unimplemented: Read as '0'

bit 3 AREIF: Access Response Error Interrupt bit

1 = Error occurred trying to access memory outside the Crypto Engine

0 = No error has occurred

bit 2 PKTIF: DMA Packet Completion Interrupt Status bit

1 = DMA packet was completed0 = DMA packet was not completed

bit 1 CBDIF: BD Transmit Status bit

1 = Last BD transmit was processed

0 = Last BD transmit has not been processed

bit 0 PENDIF: Crypto Engine Interrupt Pending Status bit

1 = Crypto Engine interrupt is pending (this value is the result of an OR of all interrupts in the Crypto Engine)

0 = Crypto Engine interrupt is not pending

#### REGISTER 28-6: ADCIMCON2: ADC INPUT MODE CONTROL REGISTER 2 (CONTINUED)

bit 6 SIGN19: AN19 Signed Data Mode bit(1) 1 = AN19 is using Signed Data mode 0 = AN19 is using Unsigned Data mode bit 5 DIFF18: AN18 Mode bit 1 = AN18 is using Differential mode 0 = AN18 is using Single-ended mode bit 4 SIGN18: AN18 Signed Data Mode bit 1 = AN18 is using Signed Data mode 0 = AN18 is using Unsigned Data mode bit 3 DIFF17: AN17 Mode bit 1 = AN17 is using Differential mode 0 = AN17 is using Single-ended mode SIGN17: AN17 Signed Data Mode bit bit 2 1 = AN17 is using Signed Data mode 0 = AN17 is using Unsigned Data mode bit 1 DIFF16: AN16 Mode bit 1 = AN16 is using Differential mode 0 = AN16 is using Single-ended mode bit 0 SIGN16: AN16 Signed Data Mode bit 1 = AN16 is using Signed Data mode

Note 1: This bit is not available on 64-pin devices.

0 = AN16 is using Unsigned Data mode

REGISTER 30-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|----------------------------|-------------------------|-------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0                        | U-0                     | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                          | _                       | _                       | -                 | _                 | _                 |                  |                  |  |  |

| 23:16        | R/W-0                      | R/W-0                   | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | BUFCNT<7:0> <sup>(1)</sup> |                         |                         |                   |                   |                   |                  |                  |  |  |

| 15:8         | U-0                        | U-0                     | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.6         | _                          | _                       |                         | _                 | _                 | _                 |                  | 1                |  |  |

| 7:0          | R/W-0                      | R/W-0                   | R/W-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7.0          | ETHBUSY <sup>(5)</sup>     | TXBUSY <sup>(2,6)</sup> | RXBUSY <sup>(3,6)</sup> | _                 | _                 | _                 | _                | _                |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-24 Unimplemented: Read as '0'

bit 23-16 BUFCNT<7:0>: Packet Buffer Count bits(1)

Number of packet buffers received in memory. Once a packet has been successfully received, this register is incremented by hardware based on the number of descriptors used by the packet. Software decrements the counter (by writing to the BUFCDEC bit (ETHCON1<0>) for each descriptor used) after a packet has been read out of the buffer. The register does not roll over (0xFF to 0x00) when hardware tries to increment the register and the register is already at 0xFF. Conversely, the register does not roll under (0x00 to 0xFF) when software tries to decrement the register and the register is already at 0x0000. When software attempts to decrement the counter at the same time that the hardware attempts to increment the counter, the counter value will remain unchanged.

When this register value reaches 0xFF, the RX logic will halt (only if automatic Flow Control is enabled) awaiting software to write the BUFCDEC bit in order to decrement the register below 0xFF.

If automatic Flow Control is disabled, the RXDMA will continue processing and the BUFCNT will saturate at a value of 0xFF.

When this register is non-zero, the PKTPEND status bit will be set and an interrupt may be generated, depending on the value of the ETHIEN bit <PKTPENDIE> register.

When the ETHRXST register is written, the BUFCNT counter is automatically cleared to 0x00.

**Note:** BUFCNT will not be cleared when ON is set to '0'. This enables software to continue to utilize and decrement this count.

bit 15-8 Unimplemented: Read as '0'

bit 7 **ETHBUSY:** Ethernet Module busy bit<sup>(5)</sup>

- 1 = Ethernet logic has been turned on (ON (ETHCON1<15>) = 1) or is completing a transaction

- 0 = Ethernet logic is idle

This bit indicates that the module has been turned on or is completing a transaction after being turned off.

- **Note 1:** This bit is only used for RX operations.

- 2: This bit is only affected by TX operations.

- **3:** This bit is only affected by RX operations.

- **4:** This bit is affected by TX and RX operations.

- 5: This bit will be set when the ON bit (ETHCON1<15>) = 1.

- **6:** This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

| PIC32MZ Emb | edded Conne | ectivity with | Floating Po | oint Unit (EF | F) Family |

|-------------|-------------|---------------|-------------|---------------|-----------|

| NOTES:      |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

|             |             |               |             |               |           |

TABLE 37-7: DC CHARACTERISTICS: IDLE CURRENT (IDLE)

| IABLE 31-1.       | ABLE 31-1: DC CHARACTERISTICS: IDEE CORRENT (IDEE) |                |                                                                                                                                                                        |                  |  |  |

|-------------------|----------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|

| DC CHARACTI       | ERISTICS                                           |                | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |                  |  |  |

| Parameter<br>No.  | Typical(2)   Maximum(3)                            |                |                                                                                                                                                                        | Conditions       |  |  |

| Idle Current (III | DLE): Core Of                                      | f, Clock on Ba | ase Curren                                                                                                                                                             | t (Note 1)       |  |  |

| DC30a             | 7                                                  | 22             | mA                                                                                                                                                                     | 4 MHz (Note 3)   |  |  |

| DC31a             | 8                                                  | 24             | mA                                                                                                                                                                     | 10 MHz           |  |  |

| DC32a             | 13                                                 | 32             | mA                                                                                                                                                                     | 60 MHz (Note 3)  |  |  |

| DC33a             | 21                                                 | 42             | mA                                                                                                                                                                     | 130 MHz (Note 3) |  |  |

| DC34              | 26                                                 | 48             | mA                                                                                                                                                                     | 180 MHz (Note 3) |  |  |

| DC35              | 28                                                 | 52             | mA                                                                                                                                                                     | 200 MHz          |  |  |

**Note 1:** The test conditions for IDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBPMD = 1), VUSB3V3 is connected to Vss, PBCLKx divisor = 1:128 ('x' ≠ 7)

- CPU is in Idle mode (CPU core Halted)

- L1 Cache and Prefetch modules are disabled

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared (except USBPMD)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** Data in the "Maximum" column is at 3.3V, +85°C at specified operating frequency, unless otherwise stated. Parameters are for design guidance only and are not tested.

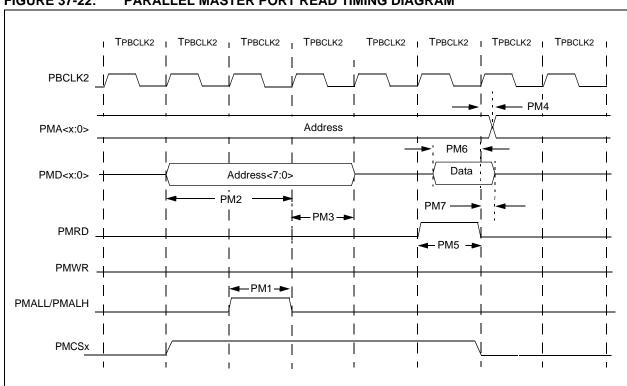

FIGURE 37-22: PARALLEL MASTER PORT READ TIMING DIAGRAM

TABLE 37-43: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                      | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |           |      |       |            |

|--------------------|---------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                             | Тур.      | Max. | Units | Conditions |

| PM1                | TLAT    | PMALL/PMALH Pulse Width                                              | _                                                                                                                                                                                                                                                | 1 TPBCLK2 | _    | _     | _          |

| PM2                | TADSU   | Address Out Valid to PMALL/<br>PMALH Invalid (address setup<br>time) | _                                                                                                                                                                                                                                                | 2 TPBCLK2 | _    | _     | _          |

| РМ3                | TADHOLD | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | _                                                                                                                                                                                                                                                | 1 TPBCLK2 | _    | _     | _          |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                | _         | _    | ns    | _          |

| PM5                | TRD     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                | 1 TPBCLK2 | _    | _     | _          |

| PM6                | Tosu    | PMRD or PMENB Active to Data In Valid (data setup time)              | 15                                                                                                                                                                                                                                               | _         | _    | ns    | _          |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | _                                                                                                                                                                                                                                                | 80        | _    | ns    | _          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

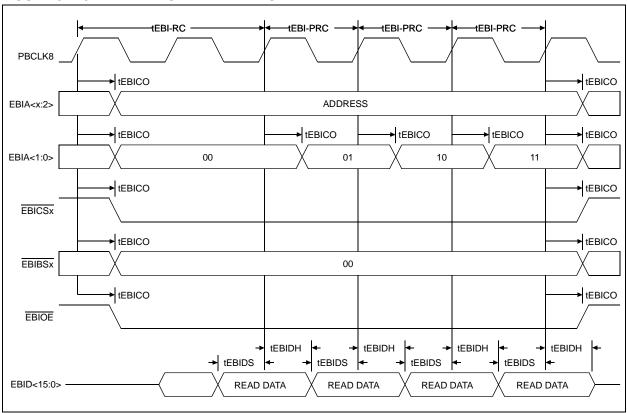

FIGURE 37-28: EBI PAGE READ TIMING

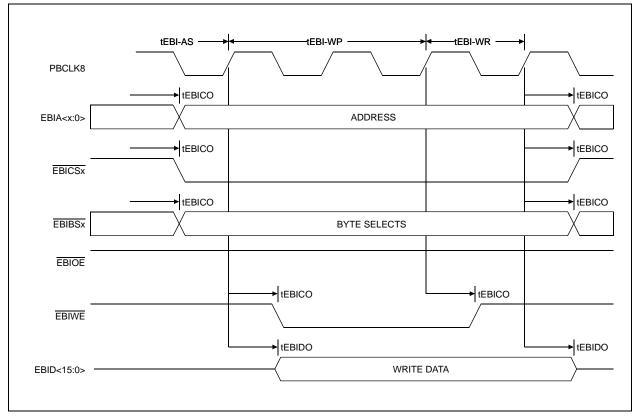

FIGURE 37-29: EBI WRITE TIMING

**TABLE 37-47: EBI TIMING REQUIREMENTS**

| AC CHARACTERISTICS |         |                                         | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |      |      |       |               |

|--------------------|---------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|---------------|

| Param.<br>No.      | Symbol  | Characteristic                          | Min.                                                                                                                                                                                                                                             | Тур. | Max. | Units | Conditions    |

| EB10               | TEBICLK | Internal EBI Clock Period (PBCLK8)      | 10                                                                                                                                                                                                                                               | _    | _    | ns    | _             |

| EB11               | TEBIRC  | EBI Read Cycle Time<br>(TRC<5:0>)       | 20                                                                                                                                                                                                                                               | _    | _    | ns    | _             |

| EB12               | TEBIPRC | EBI Page Read Cycle Time<br>(TPRC<3:0>) | 20                                                                                                                                                                                                                                               | _    | _    | ns    | _             |

| EB13               | TEBIAS  | EBI Write Address Setup (TAS<1:0>)      | 10                                                                                                                                                                                                                                               | _    | _    | ns    | _             |

| EB14               | TEBIWP  | EBI Write Pulse Width (TWP<5:0>)        | 10                                                                                                                                                                                                                                               | _    |      | ns    | _             |

| EB15               | TEBIWR  | EBI Write Recovery Time (TWR<1:0>)      | 10                                                                                                                                                                                                                                               |      |      | ns    | _             |

| EB16               | Тевісо  | EBI Output Control Signal Delay         | _                                                                                                                                                                                                                                                | _    | 5    | ns    | See Note 1    |

| EB17               | TEBIDO  | EBI Output Data Signal Delay            | _                                                                                                                                                                                                                                                | _    | 5    | ns    | See Note 1    |

| EB18               | TEBIDS  | EBI Input Data Setup                    | 5                                                                                                                                                                                                                                                |      |      | ns    | See Note 1    |

| EB19               | TEBIDH  | EBI Input Data Hold                     | 3                                                                                                                                                                                                                                                | _    | _    | ns    | See Note 1, 2 |

**Note 1:** Maximum pin capacitance = 10 pF.

#### **TABLE 37-48: EBI THROUGHPUT REQUIREMENTS**

| AC CHARACTERISTICS |                         | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |      |       |            |  |  |

|--------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|--|

| Param.<br>No.      | Characteristic          | Min.                                                                                                                                                                                                                                             | Тур. | Max. | Units | Conditions |  |  |

| EB20               | Asynchronous SRAM Read  | _                                                                                                                                                                                                                                                | 100  | _    | Mbps  |            |  |  |

| EB21               | Asynchronous SRAM Write | _                                                                                                                                                                                                                                                | 533  | _    | Mbps  | _          |  |  |

**Note 1:** Maximum pin capacitance = 10 pF.

<sup>2:</sup> Hold time from EBI Address change is 0 ns.

<sup>2:</sup> Hold time from EBI Address change is 0 ns.

| DMSTAT (Deadman Timer Status)297                      | sum)534                                             |

|-------------------------------------------------------|-----------------------------------------------------|

| DMTCLR (Deadman Timer Clear)296                       | ETHPMM0 (Ethernet Controller Pattern Match Mask 0). |

| DMTCNT (Deadman Timer Count)298                       |                                                     |

| DMTCON (Deadman Timer Control)295                     | ETHPMM1 (Ethernet Controller Pattern Match Mask 1). |

| DMTPRECLR (Deadman Timer Preclear)295                 | 533                                                 |

| DMTPSINTV (Post Status Configure DMT Interval Sta-    |                                                     |

| tus)299                                               | ,                                                   |

| EBICSx (External Bus Interface Chip Select) 385       | ETHRXOVFLOW (Ethernet Controller Receive Overflow   |

| EBIFTRPDx (External Bus Interface Flash Timing) 388   | Statistics)543                                      |

| EBIMSKx (External Bus Interface Address Mask) 386     | ETHRXST (Ethernet Controller RX Packet Descriptor   |

| EBISMCON (External Bus Interface Static Memory Con-   | Start Address) 531                                  |

| trol)389                                              |                                                     |

| EBISMTx (External Bus Interface Static Memory Timing) | 537                                                 |

| 387                                                   | ETHSCOLFRM (Ethernet Controller Single Collision    |

| EMAC1CFG1 (Ethernet Controller MAC Configuration 1)   | Frames Statistics)545                               |

| 550                                                   | ETHSTAT (Ethernet Controller Status) 541            |

| EMAC1CFG2 (Ethernet Controller MAC Configuration 2)   | ETHTXST (Ethernet Controller TX Packet Descriptor   |

| 551                                                   | Start Address)531                                   |

| EMAC1CLRT (Ethernet Controller MAC Collision Win-     | ,                                                   |

| dow/Retry Limit)555                                   |                                                     |

| EMAC1IPGR (Ethernet Controller MAC Non-Back-to-       |                                                     |

| Back Interpacket Gap)554                              | · · ·                                               |

| EMAC1IPGT (Ethernet Controller MAC Back-to-Back In-   | <b>3</b> ,                                          |

| terpacket Gap)553                                     | ` •                                                 |

| EMAC1MADR (Ethernet Controller MAC MII Manage-        | g ,                                                 |

| ment Address)561                                      | Register 26)57                                      |

| EMAC1MAXF (Ethernet Controller MAC Maximum            |                                                     |

| Frame Length)556                                      |                                                     |

| EMAC1MCFG (Ethernet Controller MAC MII Manage-        | ,                                                   |

| ,                                                     | ,                                                   |

| ment Configuration)                                   |                                                     |

| EMAC1MCMD (Ethernet Controller MAC MII Manage-        | , , , , , , , , , , , , , , , , , , ,               |

| ment Command)                                         | , ,                                                 |